## Nanopackaging: Nanotechnologies and Electronics Packaging

James E. Morris Department of Electrical & Computer Engineering Portland State University, Portland OR 97207-0751, USA j.e.morris@ieee.org

## Abstract

Nanotechnologies are being applied to microelectronics packaging, primarily in the applications of nanoparticle nanocomposites, or in the exploitation of the superior mechanical, electrical, or thermal properties of carbon nanotubes. Composite materials are studied for high-k dielectrics, electrically conductive adhesives, conductive "inks," underfill fillers, and solder enhancement. These trends are demonstrated by paper presentations over the past few years at ECTC and other conferences, which show research to be concentrated in relatively few laboratories, with little work being done on the packaging requirements of the new nanoelectronics technologies. Future needs (predictably) include education and software development.

## Introduction

It may seem that the media hype surrounding the term "nanotechnology" is all too reminiscent of the past promises of cold fusion and high-temperature superconductivity, but nanotechnologies have already yielded everyday consumer benefits beyond stain-resistant clothing and transparent sun-block. So it would not be surprising to discover active research programs in nanotechnology applications to electronics packaging, and amongst the traditional electronics packaging conferences, this trend is most evident in the papers presented at the annual Electronics Component & Technology Conference (ECTC,) the IEEE's flagship event in packaging. The proceedings of recent and forthcoming ECTC events [1-3], and of two more IEEE Components, Packaging, and Manufacturing Technology Society conferences, (i.e. the 5<sup>th</sup> International IEEE Polymers & Adhesives Conference on in Microelectronics & Photonics (Polytronic 2005) [4] and the 10<sup>th</sup> International IEEE Symposium & Exhibition on Advanced Packaging Materials (APM'05) [5],) demonstrate the range and progress of this research.

The definition of nanotechnology is usually taken to be where the size of the functional element falls below 100nm or  $0.1\mu$ m. Of course, according to this definition, and with 90nm CMOS in production, the nanoelectronics era is already here. Furthermore, with metallic grain sizes typically below this limit, one might also argue that solder has always qualified as a nanotechnology, along with many thin film applications. So, the requirement that the specific function depend upon this nanoscale dimension is conventionally added to the definition. According to this *caveat*, MOSFET technology, for example, would not qualify by simple device shrink, but would at dimensions permitting ballistic charge transport.

Nanotechnology drivers are the varied ways in which materials properties change at low dimensions. Electron transport mechanisms at small dimensions include ballistic transport, severe mean free path restrictions in very small nanoparticles, various forms of electron tunneling, electron hopping mechanisms, and more. Other physical property changes include:

• Melting point depression, i.e. the reduction of metal nanoparticle melting points at small sizes [1], although this is unlikely to be a factor in packaging applications with even 10% reductions typically requiring dimensions under 5nm [2]

• Sintering by surface self-diffusion, which is thermally activated, with net diffusion away from convex surfaces of high curvature [3]

• The Coulomb blockade effect, which requires an external field or thermal source of electrostatic energy to charge an individual nanoparticle, and is the basis of single-electron transistor operation [4]

• Theoretical maximum mechanical strengths in single grain material structures [5]

• Unique optical scattering properties by nanoparticles one to two orders smaller than the wavelength of visible light [6]

• The enhanced chemical activities of nanoparticles, which make them effective as

catalysts, and other effects of the high surface-to-volume ratio

## **Computer modeling**

The use of composite materials is well established for many applications. But while overall effective macroscopic properties are satisfactory for computer modeling of automotive body parts, for example, they are clearly inadequate for structures of dimensions similar to the particulate sizes in the composite. The modeling of such microelectronics (or nanoelectronics) packages must include twophase models of the composite structure, and this general principle of inclusion of the nanoscale structural detail in expanded material models must be extended to all aspects of package modeling [7]. The extended computer models can be based on either the known properties of the constituent materials, (and hopefully known at appropriate dimensions,) or the measured nanoscale properties (e.g. by a nano-indenter [8, 9] or atomic-force microscope (AFM) [10].)

# Nanoparticles: Fabrication

Noble metal nanoparticles have been fabricated by an ultrasonic processing technique [11], and Ag/Cu with "polyol" [12]. Alternatively, a precursor may be used, e.g. AgNO<sub>3</sub> for Ag nanoparticles, and there are techniques to control the particle shapes, e.g. spherical, cubic, or wires [14].

## Nanoparticles: High-*k* dielectrics

embedded The move towards passive components at both on-chip and PWB levels has prompted a search for high dielectric constant materials for low area capacitors. High dielectric constants can be achieved by the inclusion of high dielectric constant particulates and minimal thickness. The latter requirement pushes one towards nanoscale particulates, with examples of the former covering ceramic [15-17], silicon [18], and metal [19-23]. The ceramic particles are generally barium titanate, e.g. applied to organic FETs with composite k around 35 [16]; in such materials the particle surface energy must be reduced to avoid aggregation [17].

The target k is 50-200, and while k~150 has been achieved, it is at the expense of high leakage (dielectric loss.) Similar structures have been studied in the past as "cermets," (ceramic-metal composites,) for high resistivity materials for onchip resistors [24], which conduct by electron tunneling between particles. At low fields, the nanoparticles can act as Coulomb blocks to minimize DC leakage if they are sufficiently small [20], but still do not eliminate it at finite temperature [25]. It is the AC performance which is more important, however, and inter-particle capacitance will bypass the block unless pseudo-inductive effects develop at capacitor thicknesses which permit even short nanoparticle chains [26].

An alternative approach to leakage is to use aluminum particles, to take advantage of the native oxide coating [21], with  $k\sim160$  achieved [22]. Ag/Al mixtures have also been studied [23].

# Nanoparticles: Electrically conductive adhesives

The addition of smaller um diameter silver powder to 10µm silver flakes in isotropic conductive adhesives reduces resistance by inserting bridging particles between the flakes. The simple addition of nanoparticles does not improve conductance, due to mean free path restrictions and added interface resistances, and the same principles limit the performance of alumina loaded thermal composites [27]. The addition of silver nanoparticles does achieve dramatic reductions, however, by sintering wide area contacts between flakes [28], a principle also applicable to via fill [29]. Filler nanoparticle sintering can also improve anisotropic conductive adhesive performance [13], aided by contact conductance enhancement by the addition of selfassembly molecular surface treatments [28, 30, 31]. Sintering effects have also been shown to improve contacts in materials with sufficiently low filler content as to be regarded as non-conductive adhesives [32].

# Nanoparticles: Interconnect

Surface electrical interconnect for board and package levels can be achieved by screen-printing nanoscale metal colloids in suspension [33], and there has been recent effort to achieve the same effect by ink-jet printing [34, 35]. Electrical continuity is established by sintering, e.g. of 5-10nm silver particles [36]. As a variation, magnetic composite films, (e.g. of Co/SiO<sub>2</sub> in BCB and Ni/ferrite in epoxy.) have been screen-printed for antennas [37]. Sn/Ni bumps have also been grown on Sn from a nm Ni slurry [38].

## Nanoparticles: Silica filler in underfill

The key advantage of nanoscale silica particles in underfill formulations is that they resist settling [39]. They also scatter light less, permitting UV optical curing, and providing a dual photoresist function from a single material [40], and other advantages of optical transparency [41]. The higher viscosity of the nano-filled material can be reduced by silane surface treatments [42].

## Nanoparticles: Solder

The addition of Pt, Ni, or Co nanoparticles to no-Pb S-Ag-based solders eliminates Kirkendall voids, reduces intermetallic compound (IMC) growth, and reduces IMC grain sizes, significantly improving drop test performance [43]. Similarly, Ni or Mo nanoparticles promote finer grain growth, increased creep resistance, and better contact wetting [44]. Nanoparticles in the grain boundaries also inhibit grain boundary sliding and thermomechanical fatigue, but a similar function can be provided by 1.5nm SiO<sub>1.5</sub> polyhedral oligomeric silsesquioxane structures with surface-active Si-OH groups [45].

## **Carbon Nanotubes: Solder**

The addition of carbon nanotubes (CNTs) to solder can also have beneficial effects, e.g. 30-50% improvements in tensile strength [46].

## **Carbon Nanotubes: Thermal**

The high thermal conductivity of CNTs is being exploited for microelectronics chip cooling both directly in conductive cooling and indirectly in convective cooling systems. For conductive systems, the key is to establish CNT alignment [46], since the thermal conductivities of random arrays (of CNTs and carbon fibers alike) fall far short of expectation, showing no advantages over conventional materials, often also because of CNT fracture at the substrate [47]. In one of the most advanced techniques, vertical CNTs are first grown on both the aluminum heat sink and silicon chip surfaces, which are then positioned ~µm apart in a CVD furnace, enabling the CNTs from the two surfaces to grow further and connect with each other [46]. Composites incorporating CNTs have also been studied for thermal interface materials, e.g. CNT/carbon-black mixtures in epoxy resin [48]. The use of a liquid crystal resin matrix can impose structural order on the CNT alignment to yield a seven-fold improvement in thermal conductivity [49].

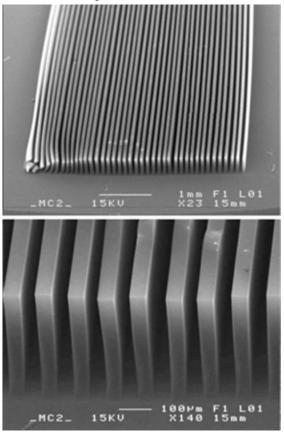

So far, convective CNT cooling has been limited to the use of  $\mu$ m-scale clusters of vertically grown nanotubes [50, 51]. These clusters define microchannels for coolant flow which look very much like the metal or silicon structures they aim to replace, (Figure 1), with similar thermal performances. The problem is that the flowing coolant is only in contact with the outermost CNTs of the clusters, and the internal CNTs are not even in good contact with each other. The system has been modeled [51], and the solution is clearly to spread the CNTs apart by an optimal separation to permit coolant contact with each one [50]. The problem then is whether individual CNTs can withstand the coolant pressure without detaching from the substrate.

#### **Carbon Nanotubes: Electrical**

An important development has been the ability to open CNTs after growth [52], since the open ends permit better wetting by Sn/Pb, (and presumably other metals,) for improved electrical contact. Au and Ag incorporation into CNTs and fullerenes has also been studied for electrical contacts with minimal galvanic corrosion [53]. Metal and carbon loaded polymers have long been used for highfrequency conductors in electromagnetic shielding, and multi-walled CNTs have been studied in polymer matrices for the purpose [54], but CNT replacement of metal filler in isotropic conductive adhesives does not even match the electrical conductivity of standard materials [55]. However, 10-50µm long Ag/Co nanowires of 200nm diameter can be maintained in a parallel vertical orientation by a magnetic field while polymer resin flows around them [56], to form an anisotropic conductive film for z-axis contacts.

## **Carbon Nanotubes: Fabrication**

CNT growth can be accomplished for both electrical and thermal applications by chemical vapor deposition [57], with satisfactory solder wetting of the CNTs for electrical contacts.

## **Nanoscale Structures**

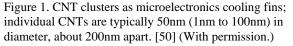

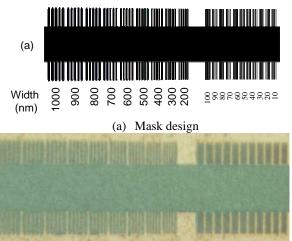

The incorporation of nano- diamond particles into an electroless Ni film coating on an electrothermal actuator [58] can improve cantilever performance by changing the thermal and mechanical properties. In a truly impressive development, the micro-spring contacts originally developed at PARC-Xerox have been down-sized to 10nm wide cantilevers, still 10µm long, for biological sensing [59] (Figure 2.) Nano-imprinting technology is also being used to fabricate optical interconnect waveguides in organic PCBs [60].

(b) e-beam evaporated cantilevers

Figure 2. Nanoscale cantilevers have been made for interconnect and bio-sensor applications, with widths down to 10nm. (a) Mask design; (b) e-beam evaporated cantilevers. [59] (With permission.)

## "Nano-interconnects"

The "nano-interconnect" terminology is applied to interconnect structures which are clearly  $\mu$ mscaled [61-68]. The ITRS Roadmap calls for 20-100 $\mu$ m pitch interconnects for nanoelectronics systems of feature size under 100nm [64], which has prompted studies of nano-grain solders [61] or copper [63], nanocrystalline copper and nickel [64], and nano-scale via fillers [62], all for applications at around 30-35 $\mu$ m pitch [61, 63]. Some nanointerconnect options are reviewed in reference [66]. Other technologies can be included in this group, too, e.g. metal-coated polymer posts on a similar scale [65], and embedded micro- or nano-electrodes for biological flow sensing [67]. Control of the interfacial surface charge on the nano-electrode in contact with the fluid can be used to control the flow [68].

#### Conclusion

The importance of nanoelectronics and "electronanotechnologies" in the future is sufficiently well recognized to have become the subject of industrial and government policy roadmaps [69]. Similarly, the academic world is responding with graduate level courses, (although with few textbooks so far.) As for electronics packaging, the field requires students to be "subject multilingual" [70].

One of the surprising observations to come out of this survey, in full agreement with prior comment [71], has been that there is almost no work reported on the development of packaging for future nanoelectronics technologies. The "nanointerconnect" work [61-66] is directed towards continued Moore's Law shrinkage of silicon, but only one paper specifically addresses the impact of the package on the device [72], specifically of organic flip-chip packaging of 110nm CMOS. next-generation nanoelectronics Candidate technologies, (e.g. single-electron transistors, quantum automata, molecular electronics, etc.,) are generally hyper-sensitive to dimensional change, if based on quantum-mechanical electron tunneling, and this is just one example of how appropriate packaging will be essential to the success or failure of these technologies. Packaging strategies must therefore be developed in parallel with the basic nanoelectronics device technologies in order to make informed decisions as to their commercial viabilities.

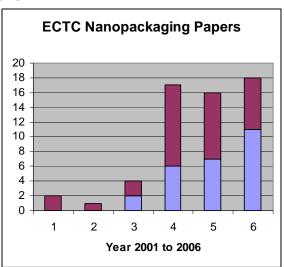

Another observation is that the work, at least as reported at ECTC, is highly concentrated in a few laboratories. This is reflected in Figure 3, where the number of nanotechnology papers presented at ECTC is tracked, with those originating at Georgia Tech highlighted. Other organizations with participation in more than one nanopackaging paper in the conferences referenced include:

University of Arkansas

• Hong Kong University of Science & Technology

• National University of Singapore/Institute of Microelectronics

• Chalmers University of Technology/SMIT Center, Shanghai University

• Industrial Technology Research Institute, Taiwan

• Endicott Interconnect Technologies, Inc

New materials are emerging from small companies and university labs all the time, and with

diverse applications beyond those discussed above [73].

Figure 3. The growth of the nanopackaging field is shown by the number of ECTC papers. The (red) top of each bar represents Georgia Tech papers, (including those with coauthors from elsewhere,) with all others below (in blue.)

#### References

- Hongjin Jiang, Kyoung-sik Moon, Hai Dong; and Fay Hua, "Thermal Properties of Oxide Free Nano Non Noble Metal for Low Temperature Interconnect Technology", Proc. 56th IEEE Electronic Component & technology conference, San Diego CA, (2006) to be published.

- J. R. Sambles, "An electron microscope study of evaporating gold particles: the Kelvin equation for liquid gold and the lowering of the melting point of solid gold particles," Proc. Roy. Soc. Lond. A. 324, (1971), pp. 339-351.

- Milton Ohring, "Materials Science of Thin Films: Deposition & Structure (Second edition)," Academic Press, 2002, pp. 395-397.

- James. E. Morris, "Single-Electron Transistors," in "The Electrical Engineering Handbook Third edition): Electronics, Power Electronics, Optoelectronics, Microwaves, Electromagnetics, and Radar," Richard C. Dorf (editor), CRC/Taylor & Francis, 2006, pp. 3.53-3.64.

- Richard A. Flinn and Paul K. Trojan, "Engineering Materials & their Applications (Second edition)," Houghton-Mifflin (1981), pp. 75-77.

- 6. T. Yamaguchi, M. Sakai, and N. Saito, "Optical properties of well-defined granular metal

systems," Phys. Rev. B, 32(4) 1985, pp. 2126-2130.

- Bernd Michel, Rainer Dudek, and Hans Walter; "Reliability testing of Polytronics Components in the Micro-Nano Region", Proc. 5th International Conference on Polymers and Adhesives in Microelectronics and Photonics, Wroclaw, Poland, (2005), pp. 13-15.

- 8 Sau Koh, Ranjan Rajoo, Rao Tummala, Ashok Saxena and Kuo Tsing Tsai, "Material Characterization for Nano Wafer Level Packaging Application", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 1670-1676.

- 9 S.Bansal, E. Toimil-Molares, A. Saxena, and Rao R. Tummala, "Nanoindentation of Single Crystal and Polycrystalline Copper Nanowires", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 71-76.

- 10 Cell K Y Wong, Hongwei Gu, Bing Xu, and Matthew M Fyuen, "A New Approach in Measuring Cu-EMC Adhesion Strength by AFM", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp 491-495.

- 11 Yamato Hayashi, Hirotsugu Takizawa, Masahiro Inoue, Koichi Niihara and Katsuaki Suganuma, "Ecodesigns and Applications for Noble Metal Nanoparticles by Ultrasound Process", IEEE Transactions on Electronic Packaging Manufacturing, 28(4) October 2005, pp. 338 -343. (Also Proc. Polytronic 2004.)

- 12 Hongjin Jiang, Kyoung-sik Moon and C.P. Wong, "Synthesis of Ag-Cu Alloy nanoparticles for lead-Free Interconnect Materials", Proc.10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine, CA, (2005).

- 13 Kyoung-sik Moon, Suresh Pothukuchi, Yi Li and C.P. Wong, "Nano Metal Particles for Low Temperature Interconnect Technology", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp. 1983-1988.

- 14 Suresh Pothukuchi, Yi Li and C.P. Wong, "Shape Controlled Synthesis of Nanoparticles and Their Incorporation into Polymers", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp. 1965-1967.

- 15 Jianwen Xu, Jianwen Xu, Swapan Bhattacharya, Kyoung-sik Moon, Jiongxin Lu, Brian Englert, and Pranabes Pramanik; Large-Area Processable High k Nanocomposite-Based Embedded Capacitors," Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA (2006) to be published.

- 16 Amjad Rasul, Jie Zhang, and Dan Gamota, "Printed Organic Electronics with a High K Nanocomposite Dielectric Gate Insulator", Proc.56th IEEE Electronic Component & Technology Conference, San Diego, CA (2006), to be published.

- 17 Rabindra Das, Mark Poliks, John Lauffer, and Voya Markovich; "High Capacitance, Large Area, Thin Film, Nanocomposite Based Embedded Capacitors", Proc. 56th IEEE Electronic Component & technology conference, San Diego CA (2006) to be published.

- 18 Ronald Kubacki, "Molecularly Engineered Variable Nanocomposites to Embed Precision Capacitors on-chip", Proc.56th IEEE Electronic Component & Technology Conference, San Diego, CA (2006) to be published.

- 19 Yi Li, Suresh Pothukuchi and C.P. Wong; "Development of a Novel Polymer-Metal Nanocomposite Obtained through the Route of In Situ Reduction and it's Dielectric Properties", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas, NV (2004) pp. 507-513.

- 20 Jiongxin Lu, Kyoung-Sik Moon, Jianwen Xu and C.P. Wong; "Dielectric Loss Control of High-K Polymer Composites by Coulomb Blockade Effects of metal Nanoparticles for embedded Capacitor Applications", Proc. 10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine CA, (2005) to be published.

- 21 Jianwen Xu and C.P. Wong, "High-K Nanocomposites with Core-Shell Structured Nanoparticles for Decoupling Applications", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp.1234 - 1240.

- 22 Jianwen Xu and C.P. Wong, "Effects of the Low Loss Polymers on the Dielectric Behavior of Novel Aluminum-filled High-k Nanocomposites," Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp.496-506.

- 23 Jiongxin Lu, Kyoung-Sik Moon, and C.P. Wong; " Development of Novel Silver Nanoparticles/Polymer Composites as High K Polymer Matrix by In-situ Photochemical Method for Embedded Passives Applications", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006) to be published.

- 24. F. Wu and J. E. Morris, "Characterizations of  $(SiO_xCr_{1-x})N_{1-y}$  thin film resistors for integrated passive applications", 53rd Electronic Components & Technology Conference, New Orleans, (2003), pp.161-166.

- J. E. Morris, "Recent progress in discontinuous thin metal film devices," Vacuum <u>50</u>(1-2), May/June 1998, pp. 107-113.

- 26. J. E. Morris, F. Wu, C. Radehaus, M.Hietschold, A. Henning, K. Hofmann, and A.Kiesow, "Single Electron Transistors: Modeling and Fabrication" Proc. 7<sup>th</sup> Internat. Confer. Solid State & Integrated Circuit Technology (ICSICT), Beijing, Oct, 2004, pp. 634-639.

- 27 Lianhua Fan, Bin Su, Jianmin Qu, C.P. Wong; "Electrical and Thermal Conductivities of Polymer Composites Containing Nano-Sized Particles", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004) pp. 148-154.

- 28 Hongjin Jiang, Kyoung-sik Moon, Lingbo Zhu, Jiongxin Lu and C.P. Wong; "The Role of Self-Assembled Monolayer (SAM) on Ag Nanoparticles for Conductive Nanocomposite", Proc. 10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine, CA. (2005) to be published.

- 29 Rabindra das, John Lauffer, and Frank Egitto; "Electrical Conductivity and Reliability of Naoand Micro-Filled Conducting Adhesives for Zaxis interconnections," Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006) to be published.

- 30 Yi Li, Kyoung-sik Moon and C.P. Wong; "Improvement of Electrical Performance of Anisotropically Conductive Adhesives", Proc. 10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine, CA. (2005).

- 31 Yi Li, Kyoung-sik Moon and C.P. Wong, "Electrical Property of Anisotropically Conductive Adhesive Joints Modified by Self-Assembled Monolayer (SAM)", Proc. 54th IEEE Electronic Component & Technology

Conference, Las Vegas NV, (2004), pp. 1968-1974.

- 32 Yi Li and C.P. Wong; "Novel lead Free Nano Scale Non-Conductive Adhesive (NCA) Interconnect Materials for Ultra-Fine Pitch Electronic Packaging Applications", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006) to be published.

- 33 Sungchul Joo, Daniel F. Baldwin, "Demonstration for Rapid Prototyping of Micro-Systems Packaging by Data-Driven Chip-First Process Using Nano-Particles Metal Colloids," Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 1859-1863.

- 34 Andrzej Moscicki, Jan Felba, Tadeusz Sobierajski, Jozef Kudzia, Andreas Arp, "Electrically Wilhelm Meyer; Conductive Formulations Filled Nano Size Silver Filler for Ink-Jet Technology", Proc. 5th International Conference on Polymers and Adhesives in Microelectronics and Photonics, Wroclaw, Poland, (2005) pp. 40-44.

- 35 Jana Kolbe, Andreas Arp, Francesco Calderone, Edouard Marc Meyer, Wilhelm Meyer, Helmut Schaefer, Manuel Stuve, "Inkjettable conductive adhesive for use in microelectronics and Microsystems technology," Proc. 5th International Conference on Polymers and Adhesives in Microelectronics and Photonics, Wroclaw, Poland, (2005) pp. 160-163.

- 36 W. Peng, V. Hurskainen, K. Hashizume, S. Dunford, S. Quander and R.Vatanparast, "Flexible Circuit Creation with Nano Metal Particles", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 77-82.

- 37 P. Markondeya Raj, Prathap Muthana, T. Danny Xiao, Lixi Wan, Devarajan Balaraman, Isaac Robin Abothu, Swapan Bhattacharya, Madhavan Swaminathan and Rao Tummala; "Magnetic nano-composites for organic compatible miniaturized antennas and inductors", Proc. 10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine, CA. (2005).

- 38 Ravi Doraiswami and Rao Tummala, "Nano-Composite Lead-free Interconnect and Reliability", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 871-873.

- 39 Pradeep Lall, Saiful Islam, Jeff Suhling and Guoyun Tian, "Nano-Underfills for High-Reliability Applications in Extreme Environments", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 212-222.

- 40 Yangyang Sun, Zhuqing Zhang and C.P. Wong, "Photo-Definable Nanocomposite for Wafer Level Packaging", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 179-184.

- 41 Yangyang Sun, C.P. Wong; "Study and Characterization on the Nanocomposite Underfill for Flip Chip Applications", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004) pp. 477-483.

- 42 Yangyang Sun, Zhuqing Zhang and C.P. Wong, "Fundamental Research on Surface Modification of Nano-size Silica for Underfill Applications", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp. 754-760.

- 43 Masazumi Amagai; "A Study of Nano Particles in SnAg-Based Lead Free Solders for Intermetallic Compounds and Drop Test Performance", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006) to be published

- 44 Vaidyanathan Kripesh, Katta Mohankumar and Andrew Tay; "Properties of Solders Reinforced with Nanotubes and Nanoparticles", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006) to be published.

- 45 Andre Lee, K.N. Subramanian, Jong-Gi Lee; "Development of Nanocomposite Lead-Free Electronic Solders", Proc. 10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine, CA, (2005).

- 46 Kai Zhang Matthrew M.F. Yuen, Jian-Ying Miao, Ning Wang, David Guo-Wei Xiao, "Thermal Interface Material with Aligned CNT Growing Directly on the Heat Sink Surface and Its Application in HB-LED Packaging", Proc.56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006), to be published.

- 47 H. Annita Zhong, Slawomir Rubinsztajn, Arun Gowda, david Esler, David Gibson, Don Bucklet, John Osaheni and Sandeep Tonapi; "Utilization of Carbon Fibers in Thermal Management of Microelectronics", Proc. 10th IEEE/CPMT International Symposium on

Advanced Packaging Materials, Irvine CA, (2005).

- 48 Kai Zhang, Guo-Wei Xiao, Cell K Y Wong, Hong-Wei Gu, Matthew M F Yuen, Philip C H Chan and Bing Xu, "Study on Thermal Interface Material With Carbon Nanotubes And Carbon Black in High-Brightness LED Packaging with Flip-Chip Technology", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 60 – 65.

- 49 Tzong-Ming Lee, Kuo-Chan Chiou, Feng-Po Tseng, Chia-Chi Huang, "High Thermal Efficiency Carbon Nanotube-Resin Matrix for Thermal Interface Materials", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 55-59.

- 50 Zhimin Mo, Raluca Morjan, Johan Anderson, Eleanor E.B. Campbell and Johan Liu, "Integrated Nanotube Microcooler for Microelectronics Applications", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 51 - 54.

- 51 Lisa Ekstrand, Zhimin Mo, Yan Zhang and Johan Liu; "Modelling of Carbon Nanotubes as heat Sink Fins in Microchannels for Microelectronics Cooling", Proc. 5th International Conference on Polymers and Adhesives in Microelectronics and Photonics, Wroclaw, Poland, (2005) pp. 185-187.

- 52 Lingbo Zhu, Yonghao Xiu, Dennis Hess and CP Wong, "In-situ Opening Aligned Carbon Nanotube Films/Arrays for Multichannel Ballistic Transport in Electrical Interconnect", Proc.56th IEEE Electronic Component & Technology Conference, San Diego, CA (2006) to be published.

- 53 R.T.Pike, R.Dellmo, J.Wade, S.Newland, G.Hyland and C.M.Newton, "Metallic Fullerene and MWCNT Composite Solutions for Microelectronics Subsystem Electrical Interconnection Enhancement", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp 461-465.

- 54 Jin-Chen Chiu, Chia-Ming Chang and Wood-Hi Cheng, Wern-Shiang Jou, "High-Performance Electromagnetic Susceptibility for a 2.5Gb/s Plastic Transceiver Module Using Mutli-Wall Carbon Nanotubes", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006), to be published.

- 55 A.M. Bondar, A.Bara, D.Patroi, P.M. Svasta; "Carbon Mesophase/Carbon Nanotubes nanocomposite - Functional Filler for

Conductive Pastes", Proc. 5th International Conference on Polymers and Adhesives in Microelectronics and Photonics, Wroclaw, Poland, (2005) pp. 215-218.

- 56 Ren-Jen Lin, Yung-Yu Hsu, Yu-Chih Chen, Syh-Yuh Cheng and Ruoh-Huey Uang, "Fabrication of Nanowire Anisotropic Conductive Film for Ultra-fine Pitch Flip Chip Interconnection", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 66 - 70.

- 57 Lingbo Zhu, Yangyang Sun, Jianwen Xu, Zhuqing Zhang, Dennis W. Hess and C.P. Wong, "Aligned Carbon Nanotubes for Electrical Interconnect an Thermal Management", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp.44 - 50.

- 58 Li-Nuan Tsai, Guang-Ren Shen, Y-T Cheng, Wensyang Hsu; " Power and Reliability Improvement of an Electro-Thermal Microactuator Using Ni-Diamond Nanocomposite", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas, NV (2004) pp. 472-476.

- 59 Kevin M. Klein, Jiantao Zheng, Andrew Gewirtz, Dittakavi S. Sarma, S.Rajalakshmi and Suresh K. Sitaraman, "Array of Nano-Cantilevers as a Bio-Assay for Cancer Diagnosis", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 583-587.

- 60 Bryan Lee, Ramana Pamidigantham, and Premachandran C S; "Development of Polymer waveguide using Nano-Imprint method for chip to chip Optical communication and study the suitability on organic substrates", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA (2006) to be published.

- 61 Pradeep Dixit and Jianmin Miao; "Fabrication of High Aspect Ratio 35 Micron Pitch Nanointerconnects For next Generation 3-D Wafer Level Packaging by Through-wafer Copper Electroplating", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA (2006) to be published.

- 62 Silke Spiesshoefer, Leonard Schaper, Susan Burkett, Gowtham Vangara, Ziaur Rahman, Parthiban Arunasalam; "Z-Axis Interconnects using fine pitch, Nanoscale Through-Silicon Vias: Process Development", Proc. 54th IEEE

Electronic Component & Technology Conference, Las Vegas, NV (2004) pp. 466-471.

- 63 Ankur O. Aggarwal, P. Makondeya Raj, Venky Sundaram, D. Ravi, Sauwee Koh and Rao R. Tummala, "50 Micron Pitch Wafer Level Packaging Testbed with Reworkable IC-Package Nano Interconnects", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp.1139 - 1146.

- 64 S. Bansal, A. Saxena and Rao R. Tummala, "Nanocrystalline Copper and Nickel as Ultra High-Density Chip-to-Package Interconnections", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp. 1647-1651.

- 65 Ankur O. Aggarwal, Kianoush Naeli, P. Makondeya Raj, Farrokh Ayazi, Swapan Bhattacharya and Rao R. Tummala, "MEMS Composite Structures for Tunable Capacitors and IC-Package Nano Interconnects", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp. 835-842.

- Ankur O. Aggarwal, P. Markondeya Raj, Issac R. Abothu, Michael D. Sacks, Andrew A.O Tay, Rao R. Tummala; "New Paradigm in IC-Package Interconnections by Reworkable Nano-Interconnects", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas, NV (2004) pp. 451-460.

- 67 Ravi Doraiswami and Manoharan Muthuswamy,"Nano Bio Embedded Fluidic Substrates: System Level Integration using Nano Electrodes for Food Safety", Proc.56th IEEE Electronic Component & Technology Conference, San Diego, CA (2006) to be published.

- 68 Ravi Doraiswami,"Embedded nano nickel interconnects and electrodes for next generation 15 micron pitch embedded bio fluidic sensors in FR4 substrates", Proc. 56th IEEE Electronic Component & Technology Conference, San Diego CA, (2006) to be published.

- 69 G.Q.(Kouchi) Zhang, Mart Graef and Fred Van Roosmalen, "The Rationale and Paradigm of "More than Moore"", Proc.56th IEEE Electronic Component & Technology Conference, San Diego, CA (2006), to be published.

- 70 Ajay P. Malshe, "Development of a Curriculum in Nano and MEMS Packaging and Manufacturing for Integrated Systems to Prepare Next Generation Workforce", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004), pp. 1706-1711.

- 71 Thomas Zerna and Klaus-Jurgen Wolter, "Developing a Course about Nano-Packaging", Proc. 55th IEEE Electronic Component & Technology Conference, Orlando FL, (2005), pp. 1925-1929.

- 72 Development of Organic Flip Chip Packaging Technology for Nanometer Silicon Incorporating Copper Metallization and Low-k Dielectric", Proc. 54th IEEE Electronic Component & Technology Conference, Las Vegas NV, (2004) pp. 347-351.

- 73 E.Suhir; "New Nano-Particle Material (NPM) for Micro- and Opto-Electronic Packaging Applications," Proc. 10th IEEE/CPMT International Symposium on Advanced Packaging Materials, Irvine, CA. (2005).

This paper will also be presented at the 1<sup>st</sup> IEEE CPMT Electronics Systemintegration Technology Conference (ESTC 2006), Dresden, September 5<sup>th</sup>-7<sup>th</sup>, 2006.