# Nanowire FET Based Neural Element for Robotic Tactile Sensing Skin

William Taube Navaraj<sup>1</sup>, Carlos García Núñez<sup>1</sup>, Dhayalan Shakthivel<sup>1</sup>, Vincenzo Vinciguerra<sup>2</sup>, Fabrice Labeau<sup>3</sup>, Duncan H. Gregory<sup>4</sup> and Ravinder Dahiya<sup>1\*</sup>

<sup>1</sup> Bendable Electronics and Sensing Technologies Group, School of Engineering, University of Glasgow, Glasgow, United Kingdom, <sup>2</sup> ST Microelectronics, Catania, Italy, <sup>3</sup> Department of Electrical and Computer Engineering, McGill University, Montreal, QC, Canada, <sup>4</sup> WestCHEM, School of Chemistry, University of Glasgow, Glasgow, United Kingdom

This paper presents novel Neural Nanowire Field Effect Transistors (v-NWFETs) based hardware-implementable neural network (HNN) approach for tactile data processing in electronic skin (e-skin). The viability of Si nanowires (NWs) as the active material for v-NWFETs in HNN is explored through modeling and demonstrated by fabricating the first device. Using v-NWFETs to realize HNNs is an interesting approach as by printing NWs on large area flexible substrates it will be possible to develop a bendable tactile skin with distributed neural elements (for local data processing, as in biological skin) in the backplane. The modeling and simulation of v-NWFET based devices show that the overlapping areas between individual gates and the floating gate determines the initial synaptic weights of the neural network - thus validating the working of v-NWFETs as the building block for HNN. The simulation has been further extended to v-NWFET based circuits and neuronal computation system and this has been validated by interfacing it with a transparent tactile skin prototype (comprising of  $6 \times 6$  ITO based capacitive tactile sensors array) integrated on the palm of a 3D printed robotic hand. In this regard, a tactile data coding system is presented to detect touch gesture and the direction of touch. Following these simulation studies, a four-gated v-NWFET is fabricated with Pt/Ti metal stack for gates, source and drain, Ni floating gate, and Al<sub>2</sub>O<sub>3</sub> high-k dielectric layer. The current-voltage characteristics of fabricated v-NWFET devices confirm the dependence of turn-off voltages on the (synaptic) weight of each gate. The presented v-NWFET approach is promising for a neuro-robotic tactile sensory system with distributed computing as well as numerous futuristic applications such as prosthetics, and electroceuticals.

Keywords: silicon nanowire, tactile skin, sparse coding, Nanowire Field Effect Transistor, neuro-robotics

# INTRODUCTION: NEURO-MIMICKING TACTILE SENSING

Humans and other biological organisms use tactile feedback to interact with the environment (Dahiya et al., 2010). Inspired by nature, numerous research groups are harnessing the technological advances to develop artificial e-skin with features mimicking human skin (Boland, 2010; Tee et al., 2012; Bauer, 2013; Hammock et al., 2013; Wang et al., 2013; Yogeswaran et al., 2015; Núñez et al., 2017). These works find application in prosthetics, potentially to bestow lost sensory feelings to amputees (Raspopovic et al., 2014) and robotics to provide the touch sensory

### OPEN ACCESS

#### Edited by:

Calogero Maria Oddo, Sant'Anna School of Advanced Studies, Italy

#### Reviewed by:

Martin Ziegler, University of Kiel, Germany Sunil L. Kukreja, National University of Singapore, Singapore Alejandro Linares-Barranco, University of Seville, Spain

\*Correspondence: Ravinder Dahiya ravinder.dahiya@glasgow.ac.uk

#### Specialty section:

This article was submitted to Neuromorphic Engineering, a section of the journal Frontiers in Neuroscience

Received: 18 May 2017 Accepted: 23 August 2017 Published: 20 September 2017

### Citation:

Taube Navaraj W, García Núñez C, Shakthivel D, Vinciguerra V, Labeau F, Gregory DH and Dahiya R (2017) Nanowire FET Based Neural Element for Robotic Tactile Sensing Skin. Front. Neurosci. 11:501. doi: 10.3389/fnins.2017.00501

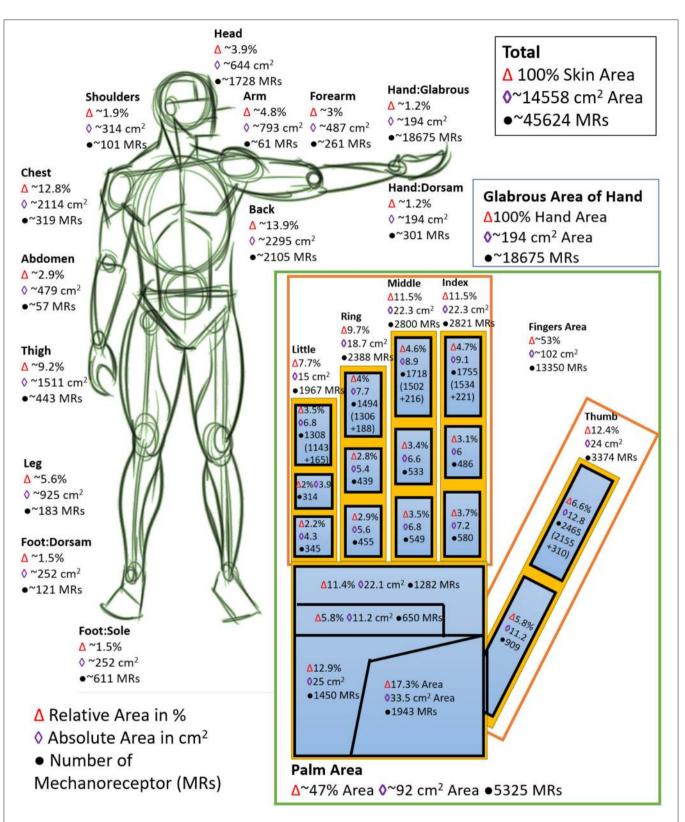

1

capability allowing them to interact physically and safely with real-world objects (Dahiya et al., 2013b). Thus far, the major focus of e-skin research has been on the development of various types of sensors (e.g., contact pressure, temperature, humidity, etc.) and their integration on large-area and flexible/conformable substrates (Dahiya and Valle, 2013; Dahiya et al., 2013a, 2015; Hammock et al., 2013; Lee et al., 2015; Yogeswaran et al., 2015; Polishchuk et al., 2016; Núñez et al., 2017). However, processing of a large amount of data from e-skin has remained a challenge, especially in the case of large area skin where number of touch sensors increase rapidly. As an example, to develop human inspired e-skin for robotic and prosthetic limbs, an estimated 45 K mechanoreceptors (MRs) will be needed in about 1.5 m<sup>2</sup> area, as shown in Figure 1 (details in Supplementary Section 1; Johansson and Vallbo, 1979; Boniol et al., 2008; Mancini et al., 2014; Goldstein and Brockmole, 2016). This number of sensors will be much higher if we consider e-skin to have equivalents of thermo-receptors and nociceptors (Goldstein and Brockmole, 2016). The large number of receptors in the skin indicates that the tactile data will multiply rapidly, and therefore one can understand the challenge associated with its compiling and processing. With the recent shift in the focus of tactile skin research in robotics from hands to whole-body tactile feedback, a need has arisen for new techniques to manage the tactile data. Currently, limited solutions are available to deal with large data generated in tactile skin, let alone for the resulting touch based perception, which is another dimension of tactile data handling. For example, in the case of prosthesis, it is important not only to collect the tactile data for critical feedback, but also to decode the user's intentions in real time (Raspopovic et al., 2014). Perhaps a neuron-like inference to handle the tactile data early on could help as indicated by a significant downstream reduction in the numbers of neurons transmitting stimuli in the early sensory pathways in humans (Barlow, 1981; Buck, 1996; Barranca et al., 2014). Research suggests that distributed computing takes place in the biological tactile sensory system (Barlow, 1981; Dahiya et al., 2010, 2015). For example, the ensemble of tactile data from peripheral neurons is considered to indicate both the contact force and its direction (Johansson and Birznieks, 2004; Johansson and Flanagan, 2009). Such distributed local processing of tactile data is advantageous in practical terms as sending reduced data to higher-perceptual level releases some pressure in terms of complex and bulky sensory hardware. Thus, the hardware implemented neuromorphic tactile data processing along with neural networks like algorithms will be helpful. Currently, the neuromorphic hardware is primarily targeted for vision and hearing related applications. Since, vision and hearing are not as distributed as tactile sensing, the neuromorphic hardware developed for them is not optimal for tactile sensing and dedicated solutions are needed. Few works on tactile sensing have used software based neural networks approaches for tasks such as object recognition via texture or materials (Decherchi et al., 2011; Kaboli et al., 2015). However, due to the lack of large-scale parallel processing, the software-programmed neural networks are slower and less energy-efficient (Ananthanarayanan et al., 2009; Misra and Saha, 2010) and hence the HNN implementations will be interesting.

The hardware neuromorphic architecture implementations reported in literature thus far are based on devices such as memistor (Widrow and Hoff, 1960), spin-logic (Sengupta et al., 2015; Grollier et al., 2016), memristor (Jo et al., 2010), neuron MOSFET (Ishii et al., 1992; Kotani et al., 1998), analog circuit based neurons (Mead and Ismail, 2012), field programmable gate array (FPGA) (Misra and Saha, 2010) and software-programmed neural networks (Cotton and Wilamowski, 2010). So far, these technologies have not been used with tactile skin. But, they could offer alternative to the v-NWFET approach presented here—even if v-NWFET has many inherent advantages such as possibility of printing devices on large area as discussed in the next section. The above alternative technologies have their own advantages and challenges in terms of complexity, scalability, speed, reliability, repeatability, cost, non-bendability, power consumption etc., which limit their use in the emulation of biological systems. For example, the memistor, a 3-terminal electrochemical cell element achieved limited success because of scalability issues (Widrow and Hoff, 1960). Likewise, the spintronic neurons are energy efficient (Grollier et al., 2016) but it is challenging to realize practical large-scale neuromorphic architectures and read-out. Recently, two-terminal memristive devices have gained significant attention as the state of their internal resistance could indicate the history of the voltage across and/or current through the device (Yang et al., 2013). The memristive approach is promising in terms of low-energy, highdensity memories and neuromorphic computing (Courtland, 2016), but as memristors are two terminal devices it may not be possible to simultaneously execute the signal transmission (computation or reading phase) and learning functions (writing phase). Metal NWs finds application mainly as interconnects and junction elements in crossbar memristors. Use of inorganic semiconductor NWs for HNN is an interesting direction.

Addressing the need for tactile HNN in e-skin, this paper presents a novel Neural Nanowire Field Effect Transistor (v-NWFET) structure as the functional building block. The focus of the paper is on modeling, simulation and first validation with fabricated v-NWFET structure prior to practical realization of a large area e-skin. This paper is organized as follows: The v-NWFET device structure, working principle related to a biological neuron, and specific advantages of using NWs for HNN are presented in the Section v-NWFET Based Neuro-Mimicking e-skin. Various modeling and simulation tools, and device fabrication methodology are presented in Section Methods. The results of modeling, simulation and fabrication are presented in Section Results along with experiment of eskin integrated on a 3D printed robotic/prosthetic hand. Section Discussion discusses overall implementation and study of impact of fabrication related variability over HNN performance. The results are summarized in the concluding Section Conclusions.

# *v*-NWFET BASED NEURO-MIMICKING e-SKIN

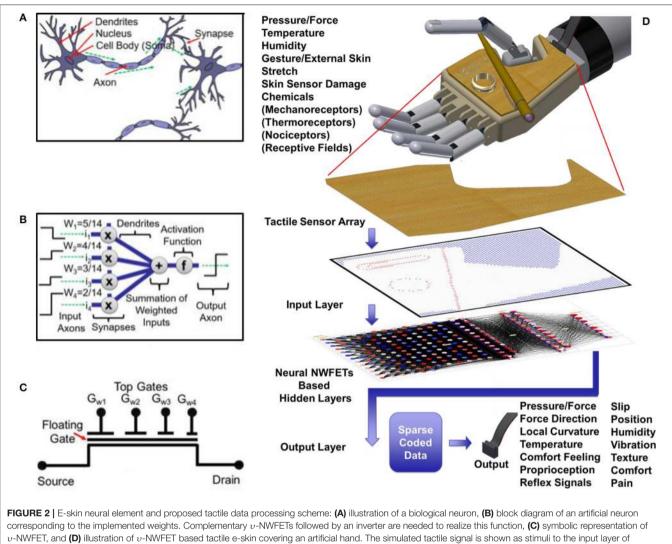

A simplified representation of biological and artificial neurons are shown in Figures 2A,B, respectively (McCulloch and Pitts,

FIGURE 1 | The distribution of mechanoreceptors in various parts of human body. (Inset: 100% glabrous area of hand, which corresponds to 1.2% of the total skin area). The number of mechanoreceptors indicate the typical number of sensors required in various parts to achieve a full body touch/pressure sensing to mimic human body.

v-NWFET based network for coding of tactile information.

1943; Goldstein and Brockmole, 2016). The v-NWFET devices (symbol in Figure 2C and structure in Figure 5A) imitate the working of biological neuron in a simplified manner. The structure of v-NWFET (Figure 5A) is a variant of a neuron MOSFET with NWs providing the functional channel region (Ishii et al., 1992; Shibata and Ohmi, 1992; Taube et al., 2016). The main floating gate, modulating the channel current is capacitively coupled to several gates. The overlap width of the individual gates over the floating gate determines the initial synaptic weight of the neural input on which further schemes of plasticity operates. This imitates the synaptic summation of weighted inputs in the cell body (soma) of the biological neuron or the artificial neuron. The activation function is performed at circuit level as discussed later in Section Circuit Modeling. It may be noted that the biological neural systems also have the plasticity or synaptic modulation, which reflects their ability to strengthen or weaken the synaptic weights over time. This modification of weights results in various forms of memory [namely, Sensory Memory, Short Term Memory (STM) and Long Term Memory (LTM), (Atkinson and Shiffrin, 1968)] at different hierarchical levels of the neural network. The sensory memory lasts for fraction of a second and is associated with local distributed computation involved in the tactile, smell or vision sensory system. Related to tactile perception, sensory memory plays a role in the local distributed computation such as force direction estimation, local curvature estimation, downstream reductions. Sensory memory on further hierarchical levels leads to STM which typically lasts for few seconds to a maximum of 30 s. These STMs gradually get transformed to LTMs at higher perceptual levels of neural network which can last up to lifetime. The v-NWFETs based circuits presented here could exhibit similar behavior as discussed later in Section Circuit Modeling.

The working of v-NWFET can be explained with modulation of the source-drain output curent by the voltage mode weighted summation of all input voltages to individual gates ( $V_{G_{w_i}}$ ). Voltage-mode summation through an insulating dielectric has significant advantage over current-mode summation as the standby power dissipation can ideally be avoided. The voltage in the floating gate ( $V_{FG}$ ) is given by:

$$V_{FG} = \frac{\sum_{i=0}^{3} C_{w_i} V_{G_{w_i}}}{C_{FG} + \sum_{i=0}^{3} C_{w_i}} + V_{Offset}$$

(1)

Where  $C_{w_i}$  corresponds to the capacitance between the individual gate and the floating gate and determines the weighing factor  $w_i$ .  $V_{G_{w_i}}$  corresponds to the voltage at each gate,  $V_{Offset}$  arises from any non-ideal charges such as fixed-oxide or interface trap charges (Shashank et al., 2011; Robinson et al., 2013).

The schematic illustration of proposed biomimetic tactile sensory neuro-system is given in Figure 2D. It consists of a prosthetic hand covered with a tactile e-skin; the simulated/measured tactile signal are read out by the receptive sensors to the input sensory layer of the v-NWFET based neural network for sparse coding of tactile information. In bio-mimicking hardware, the sparse-coded output should comprise of encoded information such as pressure/force and temperature spatial and time distribution, force direction, local curvature, vibration, slip, humidity, comfort feeling, proprioception, reflex signals, pain, gestures. As a demonstration, in this paper, sparse coding of gesture direction has been presented based on v-NWFET array architecture. Modeling was carried out to understand whether NW could be effective as a channel material for a neuron MOSFET as compared to the implementation with bulk material (Shibata and Ohmi, 1992). A combination of p-and n-channel v-NWFET cascaded with a CMOS inverter has been demonstrated to represent a neuronal element. With multiple synaptic inputs and an output, the proposed structure will contribute toward building a computational architecture inspired by biological systems. An integrated hardware-realized neuromorphic tactile system could mimic or simulate biological activity and lead to unidirectional or bidirectional bio-electronic interfaces.

# **METHODS**

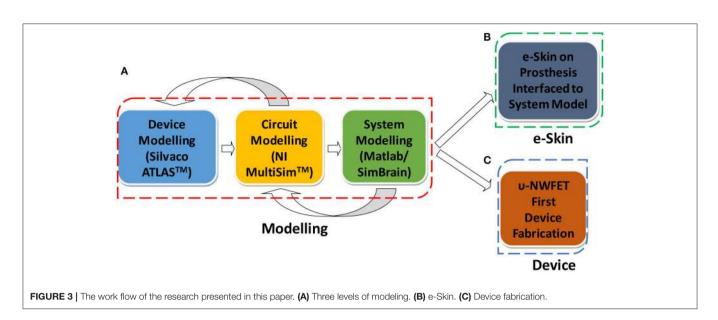

The viability of Si-NWs as an active material for HNN has been investigated through modeling and simulation, followed by the fabrication of first v-NWFET device and tactile eskin interface. The work flow of methodology used in this paper is summarized in **Figure 3** and described below in detail.

# **Modeling and Simulation**

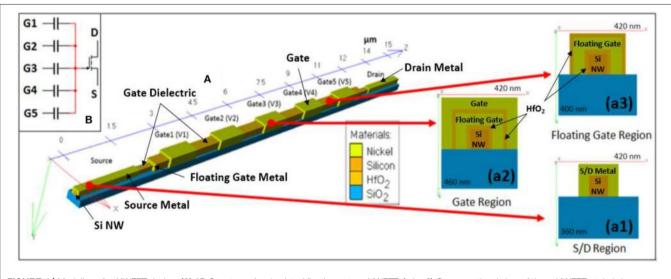

The structure of proposed  $\upsilon$ -NWFET device is shown in **Figure 4**. The modeling and simulation of the proposed approach was carried out at device, circuit and systems levels as shown in **Figure 3A**. The software tools used for this purpose (also shown in **Figure 3A**) include Silvaco ATLAS<sup>TM</sup> for device modeling, National Instruments (NI) Multisim<sup>TM</sup> for circuit modeling and Matlab and SimBrain for training and testing (offline and real-time) of the system model of NN. The implementation of  $\upsilon$ -NWFET at device and circuit levels are illustrated in

Figures 4A,B (top left inset) respectively. As shown in Figure 4A, the active channel region of the v-NWFET consists of a ptype Si-NW with width, height and length ( $w \times h \times l$ ) of 100, 100 nm and 15 µm, respectively. The channel region has ptype doping concentration of 10<sup>14</sup> cm<sup>-3</sup> and n-type source/drain doping concentration of  $10^{20}$  cm<sup>-3</sup>. Ni was used for floating gate, top gate and source/drain contacts in this simulation. Of the total 15 µm length of the NW, the channel length corresponds to 10 µm. The simulated v-NWFET comprises of five gates as input. The cross section of the simulated structure at the drain/source, gate and floating gate area are represented in Figures 4a1-a3, respectively. A 20.5 nm thick high-K dielectric such as HfO2 (or Al2O3), which corresponds to an effective oxide thickness (EOT) of 4 nm, was used between the input gates and floating gate and between the floating gate and the channel. The gates cover the NWs from three sides forming a tri-gated configuration. The individual gates' span is  $1 \mu m$  with  $1 \mu m$  separation gap between them. The v-NWFET device simulation was carried out in ATLAS-3D to solve the fundamental semiconductor physics equations in three dimension. Further, the concentration dependent and the field dependent mobility models, and Shockley-Read-Hall (SRH) recombination model were defined to be solved by the solver. The default material parameters of Si were used in the solver (details given in Supplementary Section 2) while material parameters relevant to the simulation were given as input for user defined materials such as HfO2 (or Al2O3) and Ni. The dielectric permittivity for HfO<sub>2</sub> and work function for Ni used in this work are 20 and 5.01 eV respectively. Fixed oxide charge density of 10<sup>11</sup> cm<sup>-2</sup> was defined between semiconductor/dielectric interface. Newton method was used to solve all the equations related to device simulation. All circuit simulations were carried out in Multisim<sup>TM</sup> with v-NWFET device model implemented as a modified level-3 BSIM NW MOSFET model. This model is similar to the one used by Lee et al. (2009), except that the Schottky contact in source and drain were not considered as we have used heavily-doped source/drain junctions in this work. The parameters such as effective oxide thickness of high-K dielectric, electron and hole mobility, effective width and length etc., which were used in the device simulation, were also used in the circuit simulation (Refer to Supplementary Section 2).

# Fabrication and Characterization of v-NWFET Device

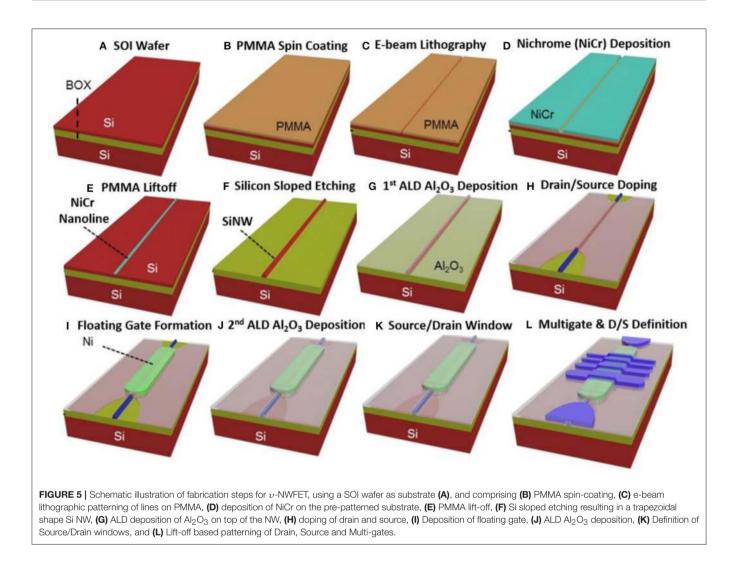

The fabrication steps carried out for realizing the v-NWFET are shown in **Figure 5**. The device was realized on a Silicon-On-Insulator (SOI) wafer using standard top-down fabrication steps. The SOI wafer with the active layer thickness of 100 nm over buried oxide (BOX) of thickness 3  $\mu$ m has been used as a starting material (**Figure 5A**). The supporting bulk Si had a thickness of ~626  $\mu$ m. The active thin layer is p-type doped with boron has a resistivity of 14–22  $\Omega$ -cm. Here, electron beam lithography (EBL) has been used to define the pattern, with a double layer of PMMA2010 4% and PMMA2041 4% as the e-beam resist (**Figure 5B**). After EBL exposure (**Figure 5C**) and development,

**FIGURE 4** | Modeling of *v*-NWFET device. (A) 3D Structure of a simulated floating gate *v*-NWFET. (a1–a3) Cross-sectional view of the *v*-NWFET at drain/source region, floating gate and gate region. (B) Equivalent circuit model of a *v*-NWFET.

NiCr metal film of thickness 50 nm was deposited using an electron beam evaporation technique (**Figure 5D**), followed by a standard lift off process (**Figure 5E**).

The resulting NiCr nanoline (200 nm wide) acted as the hard mask during dry etching to get Si NWs. During dry etching process, a mixture of semiconductor grade SiCl<sub>4</sub> and Ar gas was introduced in Reactive Ion Etching (RIE) system. The etching process used an optimized recipe to obtain a tilted slope of etch with nearly  $45^{\circ}$  angle. A mixture of 7.5 sccm SiCl<sub>4</sub> and 15 sccm Ar was introduced in the etching process. This resulted in a trapezoidal shape which led to conformable coverage during subsequent processes. The hard mask was then removed by using NiCr etchant. A high-k dielectric layer (Al<sub>2</sub>O<sub>3</sub>) of thickness 50 nm was deposited conformably over the Si-NWs (**Figure 5G**) using atomic layer deposition (ALD) to insulate the

forth-deposited Ni floating gate later in step shown in **Figure 5I**. This was followed by source drain doping and actuation. The source and drain were doped into targeted p+ doping concentration of  $\sim 10^{20}$ /cm<sup>3</sup>. Since the starting substrate is p-type the above step resulted in a depletion mode v-NWFET. Although this contrasts with the enhancement mode FET explained in the simulation section, it still serves the purpose when it comes to demonstrating the working of the v-NWFET. The morphology of Si-NW was characterized by using AFM before and after Al<sub>2</sub>O<sub>3</sub> deposition (**Figure 5G**) and doping (**Figure 5H**). Thereafter, a 30-nm thick Ni film was deposited over S1818 photoresist on an Al<sub>2</sub>O<sub>3</sub> layer. This was followed by lift-off to obtain a floating gate for the neural FET (**Figure 5I**). The floating gate was encapsulated with another 30-nm thick Al<sub>2</sub>O<sub>3</sub> layer deposited on top by ALD (**Figure 5J**). This was followed by the definition of

source, drain and multi gate electrodes with 100 nm/10 nm Pt/Ti evaporated over UV lithography patterned photoresist and lift off (**Figures 5K,L**). Finally, the devices were sintered in forming gas (5% H<sub>2</sub> + 95% N<sub>2</sub>) at 400°C for 20 min to conclude the device fabrication process. Since the capacitance plays a crucial role in the  $\upsilon$ -NWFET, the Pt/Ti-Al<sub>2</sub>O<sub>3</sub> (80 nm)-Si stack was studied using Capacitance-Voltage (C-V) characterization with a Keysight 1,520 A capacitance measure unit. The Current-Voltage (I-V) characteristics of  $\upsilon$ -NWFET was also measured using Keysight 1,500 A semiconductor parameter analyzer. Analysis of the I-V characteristics indicates some device induced variation in gate weights, which could potentially lead to variations in the performance of the HNN.

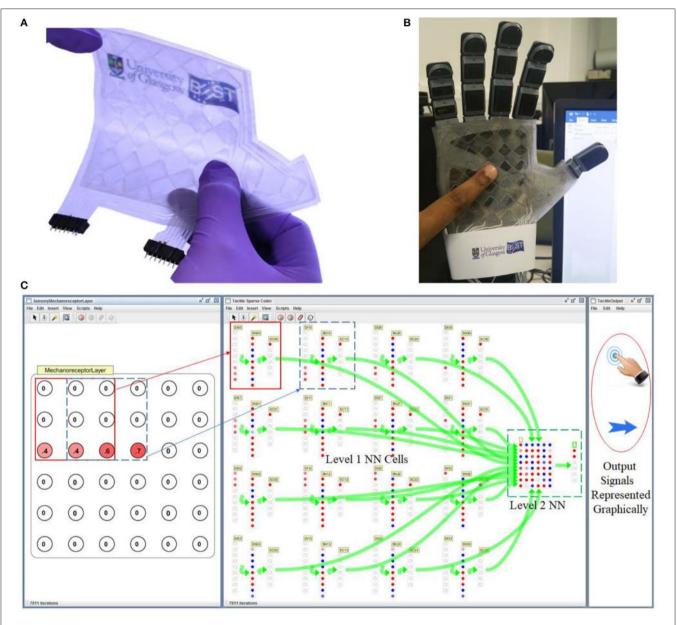

# Fabrication of Tactile Sensitive e-Skin

To demonstrate the real-time working of proposed approach, we fabricated a flexible and transparent e-skin comprising of  $6 \times 6$  capacitive tactile sensor array and integrated over 3D printed hand developed in house. This is a step toward our future goal of obtaining a large scale v-NWFET based printable electronic skin. The skin was interfaced with the SimBrain model

through a capacitive array readout circuitry. The capacitive touch sensor array and the readout circuit was similar to our recently reported work (Núñez et al., 2017). However, in the present case we have used laser-ablation based patterning of indium tin oxide (ITO) on polyethylene terephthalate (PET) substrate instead of blade-cutting based patterning of Graphene on Poly-Vinyl Chloride (PVC) substrate. The touch sensor layer was fabricated using commercial ITO coated PET sheet from Sigma Aldrich, comprising of ITO film of thickness 130 nm and sheet resistance of 60  $\Omega/\Box$  over PET of thickness 200  $\mu$ m. The 6  $\times$ 6 touch sensor array has interlaced diamond patterns of ITO over an area of  $\sim$ 3  $\times$  3 square inches. The sensing structure was designed to cover the palm of 3D printed prosthetic hand. Finally, the tactile sensitive e-skin was interfaced to SimBrain model and was tested in real time. To achieve this, the source code of SimBrain was modified to include a capacitive e-skin readout module programmed in Java. This final model was also used to understand the potential impact on neural function of the resulting network due to the deviation in gate weights arising from the line-edge roughness during fabrication, as described in previous subsection.

RESULTS

# Modeling Results

# Device Modeling

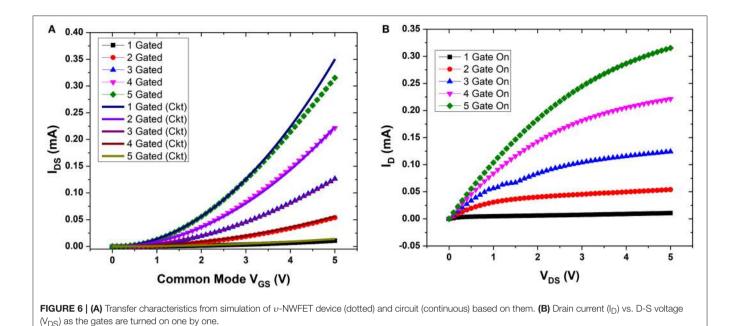

The weighted sum of voltages in the input gates determines the current  $I_{DS}$  between the drain and source. Figures 6A,B show the transfer and output characteristics of v-NWFET respectively as the gates are turned-on one by one. In Figure 6A, the V<sub>GS</sub> sweeps were carried out with common mode V<sub>GS</sub> applied to a single gate and then progressively up to five gates. Working in the enhancement mode, the v-NWFET is normally off. As the common-mode voltage is applied to two or more gates, the effective voltage in the floating gate of the transistor (Equation 1) increases and results in an increased current flow  $I_{DS}$  through the transistor. Figure 6B, shows  $V_{DS}$  vs.  $I_{DS}$  characteristics as 5 V is applied progressively from one gate to five gates.

### **Circuit Modeling**

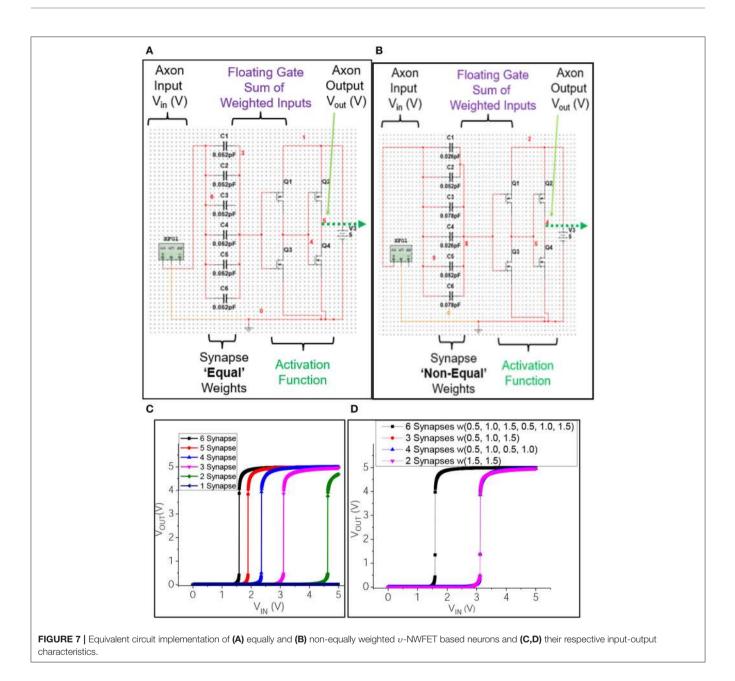

The equivalent circuit of a v-NWFET was also implemented in NI MultiSim with equal weights by connecting capacitances (corresponding to the dimensions of a v-NWFET used in the device simulation) to an n-MOSFET (Figure 4B). To realize the logistic output typical of an artificial neuron, a complementary v-NWFET-based inverter and complementary NWFET-based inverter were connected in series, as shown in Figure 7A to provide the activation function. All weights were kept equal, with a capacitance of 0.052 pF corresponding to a gate span of  $10 \,\mu$ m. Rest of the parameters were unchanged from the simulated device in Figure 7. The output of this circuit (Figure 7A), shown in Figure 7C, shows that as the common mode input passes through more gates the neuron turns on at lower voltages. This indicates that the proposed v-NWFET based neuron can provide a logistic output and could be used directly to realize neural network circuits-with the area of the capacitor's overlap with the channel determining the synaptic weight of the input. **Figure 7B** further highlights this with a circuit such as the one in **Figure 7A**, except that the non-equal gate weighted v-NWFET neuron has been implemented. The common mode input is passed through synaptic weights (1.5, 1.5), (0.5, 1.0, 0.5, 1.0), (0.5, 1.0, 1.5), considering 3 as the maximum weight. The weights were realized with 3 capacitor values (0.026 pF, 0.052 pF, and 0.078 pF) at each of the n-type and p-type v-NWFETs. **Figure 7D** shows that for all these cases (where weight is ~3), the neuron turns on at the same voltage of ~3.12 V. Also **Figure 7D** shows that the doubling of the total weight to ~6, results in the neuron turning on at ~1.59 V. Thus, a neural network implemented with a complementary v-NWFET based inverter will have the weights hard-wired by the area of the gate span over the channel.

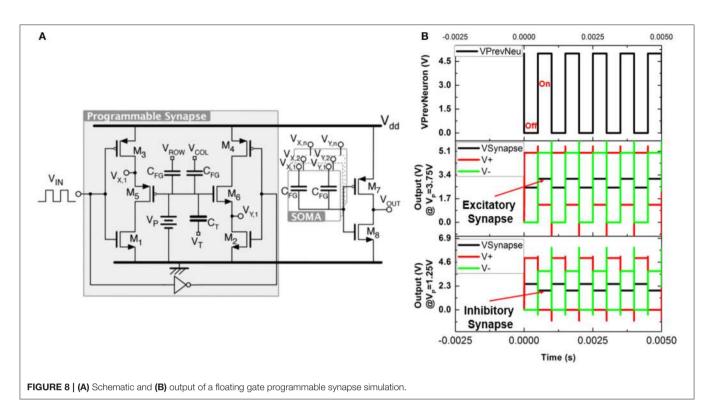

For neuromorphic computing, plasticity or ability to modify the weights of the neurons is also needed. In this regard, the next two circuit level simulations (Figures 8, 9) are relevant as they indicate the steps toward synapses with plasticity using v-NWFET approach. In both these cases, v-NWFET based neurons act as a soma of the neuron while schema proposed for synapses are different. First approach (Figure 8) presents simulation of an EEPROM-like programmable v-NWFET synapse to emulate the long term biological memory (Shibata and Ohmi, 1992; Yan et al., 2011). The second approach (Figure 9) shows simulations that are designed to emulate a sensory memory synapse utilizing passive components such as NW based resistors and capacitive structures along with v-NWFET. Further directions have been proposed for this approach to extend it toward STM and LTM exploiting recent work on nanoionics transistors or memristors (Pillai and De Souza, 2017).

The schematic and the outputs of simulation of a neuron with a programmable synapse are shown in **Figures 8A,B** with complementary v-NWFET and inverter to form a soma. The EEPROM-like programmable v-NWFET forms an element of

the synapse. Programming is carried out by selecting the  $V_{ROW}$  and  $V_{COL}$  and then applying the tunneling voltage  $V_T$  to let electrons tunnel through the tunnel capacitor  $C_T$  and program the floating gate voltage  $V_P$ . This programmed voltage  $V_P$  determines the synapse weight and modulates the output  $V_{Synapse}$  (=  $(V_{X,1} + V_{Y,1})/2$ ). It can be observed from Figure 8B that the gated p-MOS (left) and n-MOS (right) source followers are off whenever the output from the previous layer neuron  $(V_{IN})$  is off. This results in  $V_{X,1}$  (V+) = 5 V (i.e.,  $V_{DD}$ ),  $V_{Y,1}$  (V–) = 0 V (i.e.,  $V_{SS}$ ) and  $V_{Synapse}$  = 2.5 V ( $V_{DD}/2$ ), as shown in the output in Figure 8B. When the output from the previous layer neuron ( $V_{IN}$ ) is on, the  $V_{Synapse}$  results in an excitatory response for  $V_P$  > 2.5 V

and an inhibitory response for  $V_P < 2.5$  V. The graph in **Figure 8B** shows the result for  $V_P$  of values of 3.75 and 1.25 V corresponding to excitatory modulation and inhibitory modulation, respectively. This validates the v-NWFET based circuit through simulation based on NI MultiSim. These neurons could be connected in various configurations to realize systems. However, one drawback of the above approach is that it requires 2 complementary v-NWFETs per neuron, 2 complementary tunnel v-NWFET and 4 NWFET per synapse. The EEPROM programming results in a non-volatile long term storage or long term memory. Further a high field is needed across SiO<sub>2</sub> to achieve the tunneling, which could result in some reliability issues.

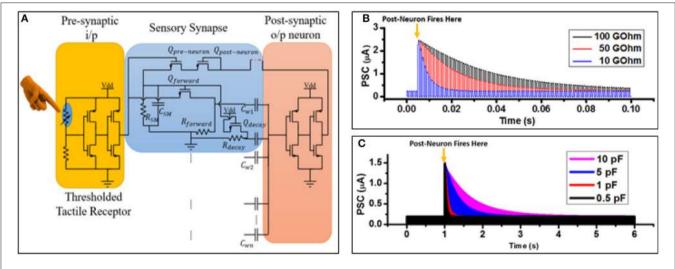

FIGURE 9 | (A) Schematic of a neuron with sensory memory and adaptable toward STM and LTM. (B) Post synaptic current vs. time graph demonstrating sensory memory. (C) Post synaptic current vs. time graph demonstrating short term memory (STM).

For tactile data processing, neurons with sensory memory like biological skin are preferred. In **Figure 9A**, we propose a circuit that takes advantage of NW processing to achieve neurons with sensory memory. The features include processing strategies to obtain a controlled array of NWs (McAlpine et al., 2005, 2007; Wang et al., 2008), the effectiveness of an array architecture (DeHon, 2003) and the inherent length of NWs. By taking advantage of the high aspect ratio of NWs, suitable resistance ( $R_{SM}$ ) and the capacitance ( $C_{SM}$ ) values can be

obtained to realize a pattern designable RC delay operating in non-switched or switched mode. This could be further used to realize both sensory memory and short term memory. For example, a Si-NW with 100  $\Omega$ -cm resistivity, 100  $\mu$ m length and square cross section with a width of 50 nm will have resistance  ${\sim}40~G\Omega.$  A monolithically integrated 20.5 nm thick HfO<sub>2</sub>-based dielectric between two 100  $\mu$ m long and 500 nm wide metal NWs will give a capacitance of  ${\sim}1.7$  pF. Together these two components will lead to a RC delay of  ${\sim}69$  ms, which

is of the order of a typical sensory memory (Atkinson and Shiffrin, 1968). Figure 9A shows the scheme of this approach with a sensory synapse implemented with a thresholder tactile sensory receptor (considered as a presynaptic input). The output of the presynaptic neuron passes through the voltage divider formed by the internal channel resistance of NWFET Qforward and NW resistor  $R_{forward}$ . This, along with the capacitance  $C_{w1}$ , decides the synaptic weight.  $C_{w1} - C_{wn}$  might have equal values acting just as a summing unit (soma) as in Figure 7A or nonequal value as in Figure 7B. To avoid bootstrapping effect, it is best to have a depletion mode NWFET for Qforward. As per Hebbian learning, the correlation between firing of preand post-neuron strengthens the synaptic weight between these two neurons. This is achieved by the feedback path, from the output of post-neuron through Qpost-neuron and Qpre-neuron to sensory memory element  $C_{SM}$ . When the pre- and the postneuron fire together, the latter charges the  $C_{SM}$  and causes the *Q*<sub>forward</sub> NWFET's internal resistance to decrease. This eventually increases the synaptic weight between the pre- and post-neuron. Figure 9B shows a typical output when the sensory memory NW resistor's ( $R_{SM}$ ) value is changed between 100, 50 and 10 G $\Omega$ , for a pulsed pre-synaptic firing of a neuron with a duration of 500  $\mu$ s. As soon as the post neuron fires (500  $\mu$ s) along with pre-neuron, the C<sub>SM</sub> gets charged. The excitatory post synaptic current decays exponentially as the  $C_{SM}$  discharges through  $R_{SM}$ . The neuron will continue to get pre-synaptic input through the voltage divider between  $Q_{decav}$  and  $R_{decav}$ . The actual effective capacitance contributing to the sensory memory is a combination of gate capacitance of Q<sub>forward</sub> as well as C<sub>SM</sub>. Depending on the timing requirement of the sensory memory, C<sub>SM</sub> could even be avoided, thus making use of the internal capacitance of  $Q_{forward}$ . The output of the neuron  $(V_{\upsilon-out})$  is a function of  $V_{FG}$ , which depends on the gate inputs  $(V_{Gn})$  incident on the various capacitors as given by Equation (1).  $V_{Gn}$  is given by the internal resistance  $R_{Q-forward}$  of  $Q_{Forward}$  and the resistance  $R_{Forward}$ :

$$V_{Gn}(t) = V_{\upsilon - in} \frac{R_{Q-forward} \left( V_{MEM} \left( t \right) \right)}{R_{Forward}} \left( 1 - e^{-\frac{t}{\tau 1}} \right)$$

(2)

$R_{O-forward}$  depends on  $V_{MEM}$  (t) across  $C_{SM}$  which is given by:

$$V_{MEM}(t) = V_{\upsilon - in} \frac{R_{SM}}{R_{TotReverse}} \left(1 - e^{-\frac{t}{\tau^2}}\right)$$

(3)

Where,

$$R_{TotReverse} = R_{Q-Pre-neuron} + R_{Q-Post-neuron} + R_{SM}$$

(4)

To demonstrate the effectiveness of the proposed approach and to advance it to system level, a tactile information processing problem was simulated as explained in the next section.

### System Modeling

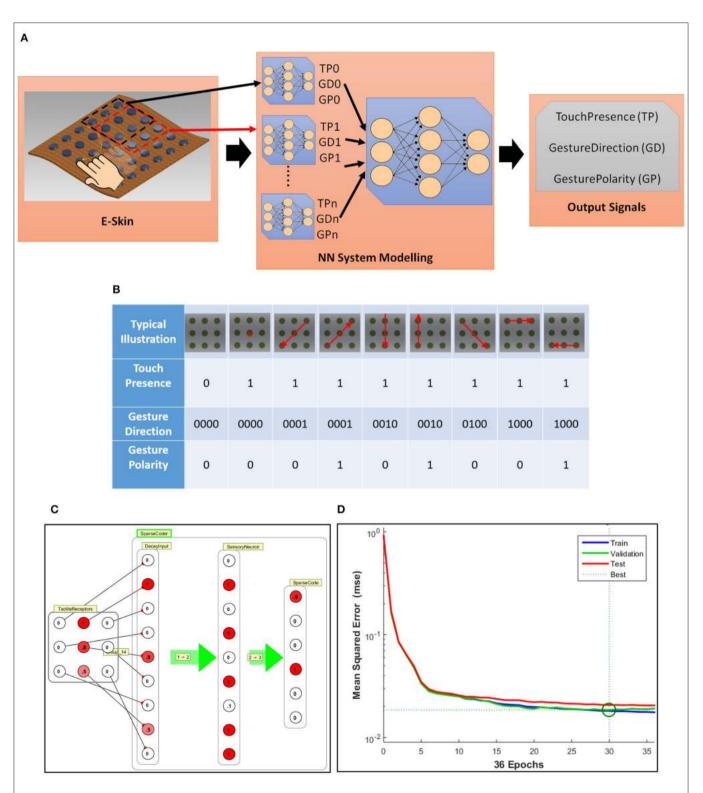

The schema of the sparse coding system shown in **Figure 10A** comprises of an array of tactile sensors  $(6 \times 6)$  which acts as an input to the NN system model. The target of the current sparse coder is to encode the tactile input or gesture into three outputs "TouchPresence," "GestureDirection," and "GesturePolarity." The outputs are considered as bits depending

on whether the neuron is on or off. "TouchPresence" is a single bit output which signifies downstream reduction i.e., whenever one of the tactile sensor (out of the  $6 \times 6$  sensors) is touched, the output should be on, as shown in the second column of Figure 10B. This could be used as an event driven triggering stage for triggering the higher stages of a neural network. "GestureDirection" is a 4-bit data output for which the values 0001, 0010, 0100, 1000 correspond to the directions NE to SW, N to S, NW to SE, and W to E respectively. The reverse direction for each case has the same output value for "GestureDirection" except that "GesturePolarity" is set to 1 instead of 0, as shown in Figure 10B. The model was implemented in two levels. The lower NN level (Simbrain snapshot shown in Figure 10C) acquires input from a  $3 \times 3$  sub-array of the e-skin to a 9 thresholded tactile receptor decay neurons. Since, the feeling of gestures on the skin depends on sensory memory, the above application serves as an effective way of testing the proposed approach. Hence, the sparse coder was modeled as a combination of a Decay Neuron Network forming an input layer followed by a feedforward neural network. The simulations were performed on SimBrain (Tosi and Yoshimi, 2016). The decay time depends on the time of the sensory or short term memory decay in Equation (3). (Supplementary Section 3 shows the snapshot of the time series plot of decay of the simbrain simulation of four neurons with different decay constants). The decay neuron forms the input to a sparse coder. From a system viewpoint, this 3  $\times$  3 sparse coder could be considered as a low-level cell. In a hardware implementation, this could be realized with NWs-based lower level cellular structure in the backplane of 3  $\times$  3 tactile sensors sub-array. This approach enables achieving hierarchical upstream reductions. The level 1 sparse coder was modeled and trained in Matlab using the Levenberg-Marquardt method with 9 logistic hidden layer neurons corresponding to 9 sensory neurons feed forwarded to 6 output neurons. The input and target for training, validation and testing the sparse coder as per Figure 10B was generated using a Matlab code generating various tactile gestures based on a random number generator. A total of 5,000 samples were generated out of which 3,500 samples were used for training, 750 samples for validation and further 750 samples for testing the system. After training, the weight and bias matrices were transferred to SimBrain for testing and visualization. Based on the simulation, training and validation, it was found that the dataset was linearly separable and was implementable with a single layer neural network with the output converged to a mean squared error of 0.02 for linear output neurons-implying a zero error as with the logistic or binary output stage. Figure 10C shows the typical implementation on SimBrain where the output of the receptor is passed to the sensory neuron through the decay inputs. The sensory neuron and the higher level logistic neurons together perform the sparse coding of the input to outputs as in Figure 10B. The first 3 blocks in Figure 10C together mimic the functionality of the sensory neuron of the circuit given in Figures 9A, 10D shows the mean squared error vs. epochs during training of the network. The network converged within 30 epochs, giving a mean squared error of 0.02. In the next section, the interface of a tactile skin to a higher level NN (level 2) through many such level 1 cells to emulate tactile gesture recognition is presented.

FIGURE 10 | (A) Schematic illustration of sparse coding of tactile data from e-skin neural information. (B) Goal of the sparse coding. (C) Typical implementation of one Level 1 sub neural network cell on SimBrain; the output of the decay sensory neuron is passed to the input of the sparse coder which gives the sparse coded output. (D) Mean squared error vs. epochs during training of the network.

# **Experimental Results**

# e-skin on Prosthetic Hand Interfaced to System Model

The fabricated flexible and transparent touch sensitive e-skin is shown in **Figure 11A**. The fabricated passive tactile sensitive e-skin integrated on a 3D printed prosthetic/robotic hand (**Figure 11B**) was interfaced to the system model and tested in real time. **Figure 11C** shows the snapshot of SimBrain model showing mechanoreceptor layer comprising of  $6 \times$ 6 elements. The 3 × 3 overlapping window of receptor elements are connected to individual local processing level 1 NN cells as shown in **Figures 10A**, **11C**. The output of all level 1 NN cells correspond to an array of 96 elements form the input layer for another hierarchical level of the feed forward neural network comprising of 48 neurons in the hidden layer and 6 neurons in the output layer. The value of the output layer of NN shown in **Figure 11C** indicates touch or direction events given in **Figure 10B**. The output signals corresponding to the value of the output layer are graphically represented in the third window of **Figure 11C**. The video of the demonstration is included in Supplementary Video 1.

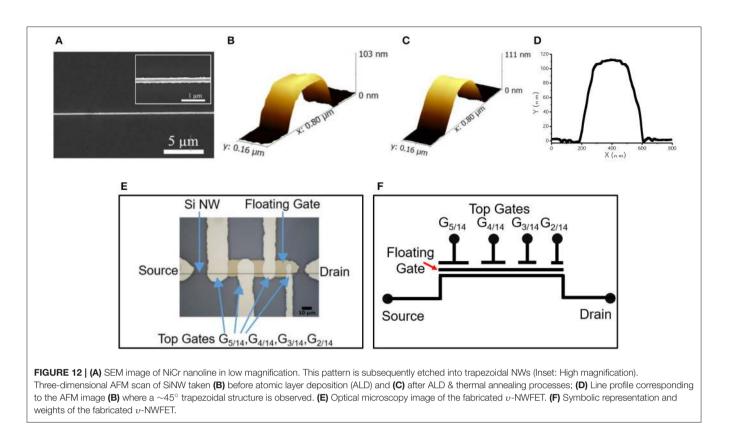

### Characterization of v-NWFET

The structural and electrical characteristics of Si v-NWFET are presented in this section. As shown in the SEM images in Figure 12A, the fabrication process (described in Figure 5A-l) results in a NiCr nanoline of width 200 nm which was used as a hard mask during dry etching for obtaining the Si NWs. After fabrication step shown in Figure 5F, the Si-NW was characterized by using AFM before and after Al<sub>2</sub>O<sub>3</sub> deposition and doping (Figure 12B–D). The Si-NW has a thickness of ~100 nm after etching, as shown in the AFM image in Figure 12B. After ALD processing and doping, the surface is smoothened as depicted in Figure 12C. The optical microscopy image of a fabricated prototypical v-NWFET is shown in Figure 12E. In the fabricated four-gated v-NWFET, the gates spanned 25, 20, 15, and 10 µm over the floating gate electrode, result in synaptic weights of around 5/14, 4/14, 3/14, and 2/14 respectively as illustrated in Figure 12F. Here, C<sub>FG</sub> is not included as the capacitance between the floating gate and the NW is negligible compared to the capacitances formed by the metal gates. Hereafter, the gates are referred, based on their synaptic weights, as G<sub>5/14</sub>, G<sub>4/14</sub>, G<sub>3/14</sub>, and G<sub>2/14</sub>.

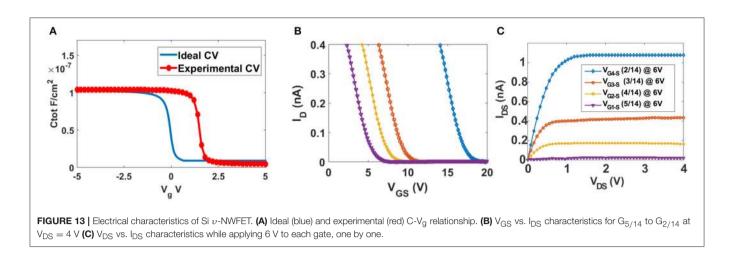

The turn-off voltage of the v-NWFET is influenced by the presence of various charges and interface trap density in the dielectric. The Pt/Ti-Al<sub>2</sub>O<sub>3</sub> (80 nm)-Si stack was studied using Capacitance-Voltage (C-V) characterization with a Keysight 1520A Capacitance Measure Unit. The Capacitance was measured for a gate voltage in the range of -5 to 5 V at 1 MHz frequency with a 50 mV-rms a-c signal. Both the ideal C-V and the experimental C-V curves are plotted in Figure 13A. Here, we used a Matlab code to obtain the ideal C-V curve by solving Poisson's equation (Sze and Ng, 2006). The work function of the electrode (Ti), average doping concentration and the oxide thickness are defined as input parameters in this code. The value of flat band capacitance  $(C_{FB})$  was obtained from the ideal C-V curve at  $V_g = 0$  V. This  $C_{FB}$  was used to get the flat band voltage  $(V_{FB})$  the experimental C-V curve  $(V_{FB} =$ 1.6 V). The fixed oxide charge density was calculated ( $Q_{OX}$  =  $-1.43 \times 10^{12} \text{ e-cm}^{-2}$ ) by finding the flat band voltage shift. The interface trap density  $D_{IT}$ , calculated using the Terman method, was found to be in a range of 1.39–7.89  $\times$  10<sup>12</sup> eV<sup>-1</sup>cm<sup>-2</sup>. The ideal and practical threshold voltages ( $V_{th}$ ) are ~0.6 and  $\sim$ 2.2 V, respectively. In the case of a floating gate structure, the effective voltage needed on the floating gate (50 nm from channel) is less than the inversion voltage observed from the C-V characteristics. Further, the additional charges in the floating gate dielectric interface will result in deviation from the ideal turn off voltage (expected  $\sim$ 1.4 V). Figure 13B shows the V<sub>GS</sub> vs. I<sub>DS</sub> characteristics with voltage sweep applied to the gates of the v-NWFET one at a time, while others kept at 0 V. Since the presented v-NWFET works in depletion mode like a gated resistor, the channel depletes with an increase in the gate voltage, finally inverted, resulting in a decrease in the current. The dependence of the observed turn-off voltage (i.e., 6.1, 7.7, 9.8, and 16.8 V (rounded to 1 decimal point for gates 1-4 respectively) on the synaptic weight of each gates demonstrates the working of the v-NWFET. Figure 13C shows the transfer characteristics

of the v-NWFET as each gate is given 6 V, one at a time. The gate with higher synaptic weight suppresses the current more compared to the gate with the lower synaptic weight in the order  $G_{2/14}$  to  $G_{5/14}$  with current reduced ~54 times from 1.0772  $\pm$  0.01 nA to 19.6  $\pm$  0.1 pA at  $V_{DS}$  = 4 V and  $V_{GS}$  = 6 V. The difference between the trend in the simulation presented in Figures 6A,B and actual data Figures 13B,C could be attributed to the fact that the v-NWFET presented here works as a gated resistor in depletion mode in contrast to the simulation. The gates with non-equal width were given voltage one at a time while the rest were at zero potential in contrast to the simulated device. Further, from the current values, the contacts appear to be Schottky-type, whereas simulation considers a perfect ohmic contact. The early saturation observed in this long channel v-NWFET could also be attributed to the saturation in one of the Schottky mode contacts. Higher performance could be obtained in a sub-50 nm v-NWFET with optimized contacts. The results herein clearly indicate the expected neuronal function from the v-NWFET device.

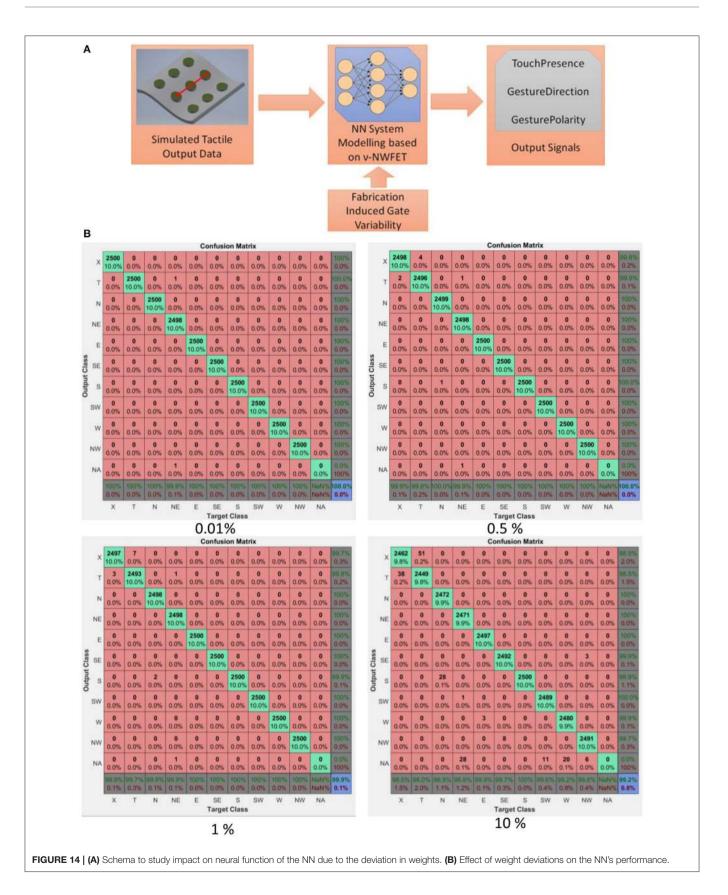

# Effect of Fabrication Induced Gate Weight Variability on the Performance of System Model

The system model given in Section System Modeling were used to understand the potential impact on neural function of the resulting network due to the deviation in gate weights arising from the line-edge ughness during fabrication (seen in Figure 12E). This is schematically illustrated in the Figure 14A. The line-edge roughness results in variation in the capacitances compared to the design value. By fitting the cut-off voltage obtained in the previous section, the experimental capacitances were obtained. The results are compared with the design capacitances in Table 1. A deviation of  $\sim$  <0.1% are observed between design and experimental capacitances. The weights of the system model were changed using a random number generator to maximum of 10% to check its effect on the sparse coder. The results are plotted as confusion matrices in Figure 14B. The class values in the x and y-axis namely, X, T, N, NE, E, SE, S, SW, W, NW, and NA corresponds to No Touch, Touch, North, North East, East, South East, South, South West, West, North West and Not Applicable respectively. With 0.01% weight deviation, only 2 out of 25,000 classifications were misclassified. For 0.5, 1, and 10% deviations the number of samples that were misclassified were 9, 14, and 2,546 samples out of 25,000 were misclassified which shows the inherent robustness in NN.

# DISCUSSION

The v-NWFETs based approach for realizing HNN has several advantages for tactile data processing in electronic skin (eskin). For example, it allows implementation of neural circuits in a compact array architecture (DeHon, 2003). With good subthreshold control of a tri-gated or gate all around NWFETs (Kuhn, 2012), it would also be possible to develop highly power efficient devices or circuits. Further, the possibility of printing NWs (Shakthivel et al., 2015; Yogeswaran et al., 2015; Navaraj et al., 2017) means with v-NWFETs it will be possible to develop bendable or conformable systems, which is much needed for better integration of e-skin on curved surfaces such as the body of a robot or prosthetic hand (Dahiya et al., 2015). Such e-skin could have printed v-NWFETs in the backplane (Yogeswaran et al., 2015; Shakthivel et al., 2016) to communicate with higher perceptual levels. It is possible to have 3D integration or stacking of NWs based circuit (Javey et al., 2007) and if such work is extended for e-skin then we may see more advantages, particularly, in terms of mimicking biological tissues and brain. The integration of v-NWFET based neural processing circuits with NW-based neural recording/mapping and stimulation circuits is another direction that could significantly advance the research in neuro-prosthetics, bio-neuro interfaces and electroceuticals (Patolsky et al., 2006; Qing et al., 2010; Robinson et al., 2013; Thomson et al., 2017).

While the direction is interesting and promising, there are significant challenges associated before realizing a fully biomimicking artificial tactile skin. The tactile data processing in biological e-skin is much complicated and has complex pathways. The notion of neurons being represented as entities performing weighted summation followed by actuation itself is a significant approximation far from a real neuron, and a slightly more

$\ensuremath{\mathsf{TABLE 1}}\xspace$  ] Comparison of designed capacitances with experimental capacitance for various gates.

| Capacitance        | G <sub>5/14</sub> | G <sub>4/14</sub> | G <sub>3/14</sub> | G <sub>2/14</sub> |

|--------------------|-------------------|-------------------|-------------------|-------------------|

| Design             | 1.3812pF          | 1.1050pF          | 0.8287pF          | 0.5525pF          |

| Experimental (Fit) | 1.3932pF          | 1.1037pF          | 0.8672pF          | 0.5059pF          |

| Deviation (%)      | 0.00869           | 0.00118           | 0.04887           | 0.08434           |

closer approximation uses time-domain differential equations to explain biological neuron's membrane dynamics and interaction (Marder and Taylor, 2011).

Biological neurons are highly energy efficient compared to most artificial implementation of neurons (Boahen, 2017). To achieve energy efficiency and better performance, a v-NWFET should have lower leakage current, higher drive current and higher on-to-off ratio. High-K dielectric used as a gate dielectric to avoid gate leakage while still having lower EOT ensures better coupling and control of gates over the channel. Further, the gates formed in a trigate configuration around the NW offers better subthreshold performance. On-to-off ratio of up to 2.6  $\times$  10<sup>4</sup> was achieved for the simulated device structure with all gates ON vs. all gates OFF. For packing more neurons per unit area and improving performance further, the v-NWFET must be scaled in all dimensions such as the width, length of the NW, the gate span of each gates.

When such intense scaling is carried out, the process variations such as variations in doping concentration, NW dimension, gate width, line edge roughness may influence the synaptic weights and performance of the neural network. However, neural networks are known to be inherently fault tolerant and robust. In the presented work, comparison of designed capacitances with experimental capacitance shows a maximum fabrication induced weight variation  $\sim 0.1\%$ . Allowing up to 1% change in the weights of the system model lead to misclassification of the data set by only  $\sim 0.06\%$  which shows the robustness of NN for such applications.

The various circuit approaches presented could be used as sub-components for neuro-mimicking tactile e-skin and based on system requirement, choice can be made between hardwiredneuron with no plasticity (as in Figure 7), neuron with plasticity having sensory memory or STM (as in Figure 9) or LTM (as in Figure 8) to be used at different hierarchical levels of the tactile sensing NN. Synaptic plasticity finds application both in data storage/memory as well as neural computation. In the first approach, i.e., hardwired-neurons, learning and circuit/layout synthesis will be through software tools which will be followed by practical fabrication forming a hardwired neural network. By introducing additional plastic synapse schemes (as in Figures 8, 9), the weight could be modulated over the initial value set by the capacitances. In this case the synaptic weight initially set by the capacitances could be considered as a phyletic memory (Fuster, 1997) because it is hardwired over which further schemes of plasticity operates. Such an approach

could be considered as a semi-plastic neural network. For such a network, the quantization arising from layout synthesis (For example rounding-off the weight equivalent capacitance dimensions to 1 µm) followed by lithography process for fabricating the capacitors will lead to k-levels of possible discrete synaptic weights (Obradovic and Parberry, 1992; Obradović and Parberry, 1994). The approach proposed in Figure 9 results in a programmable synapse, which could be used to implement hardware-in-the-loop learning. It is to be noted that in the initial stage of tactile sensing the sensory data need to be stored only for a short time and hence a neural circuit with sensory memory is sufficient for earlier tactile data handling as in Figure 9. This circuit could be further modified for higher hierarchical levels to have STM and LTM associated plasticity. A transitionary circuit from sensory memory to STM can be achieved either by replacing the  $C_{SM}$  with an element of higher value (as in **Figure 9C**) or by replacing  $Q_{forward}$  with a nanoionic-like transistor (Pillai and De Souza, 2017) for use in higher hierarchical level of neural network beyond tactile skin. Beyond that, increasing  $C_{SM}$  may not be a practical option as it becomes bulkier in the process of realizing longer times. Possible strategies for transition from STM to LTM at different stages of the network include replacing Qforward by a nanoioniclike transistor (Pillai and De Souza, 2017), or with a NWbased programmable floating gate transistor (Yan et al., 2011), or replacing R<sub>forward</sub> with a memristive device (Yang et al., 2013).

The system model interfaced with a flexible and transparent touch sensitive e-skin with  $6 \times 6$  tactile elements and tested in real-time demonstrates the working of the proposed approach. However, since the SimBrain model involves software NN programmed in java to mimic the HNN, a delay of ~1.12-1.54 s was observed per cycle for the implementation with Intel® Core<sup>TM</sup> i7-4500U CPU @ 2.4 GHz with 8GB RAM and a delay per cycle of ~0.394-0.470 s was observed for implementation in Intel<sup>®</sup> Core<sup>TM</sup> i7-4790K CPU @ 4 GHz with 32GB RAM. While this could be improved by approaches such as use of GPU, dedicated HNN such as the proposed approach will be optimal for real-time tactile data processing. The delay with software NN will be much substantial if the number of tactile elements are increased for example to a human palm ~18,675 MRs as shown in Figure 1. Further advancements in the system model is required toward advanced tactile perception tasks such as schematically shown in Figure 2D.

One of the potential application of this technology could be in an industrial task such as fruit or object sorting, where the biomimicking neural networks in the skin of robotic hands could classify and held objects based on the physical parameters such as pressure, temperature etc. as well as optical parameters from special optical sensors from tactile e-skin (Dahiya and Valle, 2013; Dahiya et al., 2015).

# CONCLUSIONS

A novel v-NWFET based approach for realizing hardware neural networks has been presented and validated through device,

circuit and system-level modeling and simulation. Two different approaches, STM and LTM, have been simulated to implement the memory or neuroplasticity. Fabrication of a v-NWFET has been carried out with a Si-NW as the channel material. The I-V characteristics of the v-NWFET demonstrates the neuronal function of the device with synaptic weights modulating the output current. For example, for a given drain ( $V_{DS} = 4 V$ ) and gate voltage ( $V_{GS} = 6$  V), the drain current at output was reduced by  $\sim$ 54 times with a gate weight of 5/14 as compared to 2/14. The proposed structure is a step toward realizing flexible power-efficient bio-inspired neural sensing and circuit architectures as a backplane for tactile e-skin in robotics or prosthetics. To this end, the system model interfaced with a flexible and transparent touch sensitive e-skin (having 6  $\times$ 6 tactile elements) and tested in real-time demonstrates the working of the proposed approach. Up to 1% change in the weights of the system model lead to misclassification of the data set by <0.06% which shows the robustness of NN for tactile sensing application. In principle, the approach could be adapted for spiking neural networks and further exploration in that direction should be extremely interesting. Multilayer or deep learning hardware neural networks could be used for further additional sparse coding to enable advanced tactile perception tasks such as schematically shown in Figure 2D. Future work will include large area fabrication of the proposed e-skin system in a flexible form factor and its subsequent testing.

# REFERENCES

- Ananthanarayanan, R., Esser, S. K., Simon, H. D., and Modha, D. S. (2009). "The cat is out of the bag: cortical simulations with 109 neurons, 1013 synapses," in *Proceedings of the Conference on High Performance Computing Networking*, *Storage and Analysis* (Denver, CO), 1–12.

- Atkinson, R. C., and Shiffrin, R. M. (1968). Human memory: a proposed system and its control processes. *Psychol. Learn. Motiv.* 2, 89–195. doi: 10.1016/S0079-7421(08)60422-3

- Barlow, H. B. (1981). The ferrier lecture, 1980: critical limiting factors in the design of the eye and visual cortex. Proc. R. Soc. Lond. B Biol. Sci. 212, 1–34. doi: 10.1098/rspb.1981.0022

- Barranca, V. J., Kovacic, G., Zhou, D., and Cai, D. (2014). Sparsity and compressed coding in sensory systems. *PLoS Comput. Biol.* 10:e1003793. doi: 10.1371/journal.pcbi.1003793

- Bauer, S. (2013). Flexible electronics: sophisticated skin. Nat. Mater. 12, 871–872. doi: 10.1038/nmat3759

- Boahen, K. (2017). A Neuromorph's Prospectus. Comput. Sci. Eng. 19, 14–28. doi: 10.1109/MCSE.2017.33

- Boland, J. J. (2010). Flexible electronics: within touch of artificial skin. *Nat. Mater.* 9, 790–792. doi: 10.1038/nmat2861

- Boniol, M., Verriest, J.-P., Pedeux, R., and Doré, J.-F. (2008). Proportion of skin surface area of children and young adults from 2 to 18 years old. J. Investig. Dermatol. 128, 461–464. doi: 10.1038/sj.jid.5701032

- Buck, L. B. (1996). Information coding in the vertebrate olfactory system. Annu. Rev. Neurosci. 19, 517–544. doi: 10.1146/annurev.ne.19.030196. 002505

- Cotton, N. J., and Wilamowski, B. M. (2010). "Compensation of sensors nonlinearity with neural networks," in 2010 24th IEEE International Conference on Advanced Information Networking and Applications (Perth, WA), 1210–1217.

- Courtland, R. (2016). Can HPE's "The Machine" deliver? *IEEE Spectrum* 53, 34–35. doi: 10.1109/MSPEC.2016.7367460

# **AUTHOR CONTRIBUTIONS**

WT and RD conceptualized the idea. WT, FL, and VV contributed to the simulation. WT, CG, and DS contributed to the fabrication and analysis of device. All the authors were involved in the manuscript preparation. RD provided overall supervision of this research.

# FUNDING

This work was supported in part by the EPSRC Fellowship for Growth–Printable Tactile Skin (EP/M002527/1) and the Principal's mobility programme of the University of Glasgow.

# ACKNOWLEDGMENTS

The authors are thankful to James Watt Nanofabrication Center (JWNC) and Electronic Systems Design Centre (ESDC) at University of Glasgow for support related to fabrication and characterization of the prototype device respectively.

## SUPPLEMENTARY MATERIAL

The Supplementary Material for this article can be found online at: http://journal.frontiersin.org/article/10.3389/fnins. 2017.00501/full#supplementary-material

- Dahiya, R., Adami, A., Collini, C., and Lorenzelli, L. (2013a). POSFET tactile sensing arrays using CMOS technology. Sens. Actuat. A 202, 226–232. doi: 10.1016/j.sna.2013.02.007

- Dahiya, R., and Valle, M. (2013). *Robotic Tactile Sensing Technologies and System*. Dordrecht: Springer.

- Dahiya, R., Metta, G., Valle, M., and Sandini, G. (2010). Tactile sensing - from humans to humanoids. *IEEE Trans. Robot.* 26, 1–20. doi: 10.1109/TRO.2009.2033627

- Dahiya, R., Mittendorfer, P., Valle, M., Cheng, G., and Lumelsky, V. J. (2013b). Directions toward effective utilization of tactile skin: a review. *IEEE Sens. J.* 13, 4121–4138. doi: 10.1109/JSEN.2013.22 79056

- Dahiya, R., Navaraj, W. T., Khan, S., and Polat, E. O. (2015). Developing electronic skin with the sense of touch. *Inform. Display* 31:5. Available online at: http:// informationdisplay.org/Portals/InformationDisplay/IssuePDF/04\_15.pdf

- Decherchi, S., Gastaldo, P., Dahiya, R., Valle, M., and Zunino, R. (2011). Tactile-data classification of contact materials using computational intelligence. *IEEE Trans. Robot.* 27, 635–639. doi: 10.1109/TRO.2011.21 30030

- DeHon, A. (2003). Array-based architecture for FET-based, nanoscale electronics. *IEEE Trans. Nanotechnol.* 2, 23–32. doi: 10.1109/TNANO.2003.808508

- Fuster, J. N. M. (1997). Network memory. Trends Neurosci. 20, 451–459. doi: 10.1016/S0166-2236(97)01128-4

- Goldstein, E. B., and Brockmole, J. (2016). Sensation and Perception. Cengage Learning.

- Grollier, J., Querlioz, D., and Stiles, M. D. (2016). Spintronic nanodevices for bioinspired computing. *Proc. IEEE* 104, 2024–2039. doi: 10.1109/JPROC.2016.2597152

- Hammock, M. L., Chortos, A., Tee, B. C., Tok, J. B., and Bao, Z. (2013). 25th anniversary article: the evolution of electronic skin (eskin): a brief history, design considerations, and recent progress. *Adv. Mater. Weinheim.* 25, 5997–6038. doi: 10.1002/adma.201 302240

- Ishii, H., Shibata, T., Kosaka, H., and Ohmi, T. (1992). "Hardwarebackpropagation learning of neuron MOS neural networks," in *Electron Devices Meeting*, 1992. IEDM '92. Technical Digest, International (San Francisco, CA), 435–438.

- Javey, A., Nam, S., Friedman, R. S., Yan, H., and Lieber, C. M. (2007). Layer-by-Layer Assembly of nanowires for three-dimensional, multifunctional electronics. *Nano Lett.* 7, 773–777. doi: 10.1021/nl0630561

- Jo, S. H., Chang, T., Ebong, I., Bhadviya, B. B., Mazumder, P., and Lu, W. (2010). Nanoscale memristor device as synapse in neuromorphic systems. *Nano Lett.* 10, 1297–1301. doi: 10.1021/nl904092h

- Johansson, R. S., and Birznieks, I. (2004). First spikes in ensembles of human tactile afferents code complex spatial fingertip events. *Nat. Neurosci.* 7, 170–177. doi: 10.1038/nn1177

- Johansson, R. S., and Flanagan, J. R. (2009). Coding and use of tactile signals from the fingertips in object manipulation tasks. *Nat. Rev. Neurosci.* 10, 345–359. doi: 10.1038/nrn2621

- Johansson, R. S., and Vallbo, Å. B. (1979). Tactile sensibility in the human hand: relative and absolute densities of four types of mechanoreceptive units in glabrous skin. J. Physiol. (Lond). 286, 283–300. doi: 10.1113/jphysiol.1979.sp012619

- Kaboli, M., De La Rosa, T., Walker, R., and Cheng, G. (2015). "In-hand object recognition via texture properties with robotic hands, artificial skin, and novel tactile descriptors," in 2015 IEEE-RAS 15th International Conference on Humanoid Robots (Seoul), 1155–1160.

- Kotani, K., Shibata, T., Imai, M., and Ohmi, T. (1998). Clock-controlled neuron-MOS logic gates. *IEEE Trans. Circ. Sys. II Anal. Dig. Sig. Process.* 45, 518–522. doi: 10.1109/82.663810

- Kuhn, K. J. (2012). Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59, 1813–1828. doi: 10.1109/TED.2012.219 3129

- Lee, S. H., Yu, Y. S., Hwang, S. W., and Ahn, D. (2009). A SPICE-Compatible New Silicon Nanowire Field-Effect Transistors (SNWFETs) Model. *IEEE Trans. Nanotechnol.* 8, 643–649. doi: 10.1109/TNANO.2009.2019724

- Lee, W. W., Kukreja, S. L., and Thakor, N. V. (2015). "A kilohertz kilotaxel tactile sensor array for investigating spatiotemporal in neuromorphic touch," in 2015 IEEE Biomedical features Circuits Conference (BioCAS) (Atlanta, and Systems GA), 1 - 4.

- Mancini, F., Bauleo, A., Cole, J., Lui, F., Porro, C. A., Haggard, P., et al., (2014). Whole-body mapping of spatial acuity for pain and touch. *Ann. Neurol.* 75, 917–924. doi: 10.1002/ana.24179

- Marder, E., and Taylor, A. L. (2011). Multiple models to capture the variability in biological neurons and networks. *Nat. Neurosci.* 14, 133–138. doi: 10.1038/nn.2735

- McAlpine, M. C., Ahmad, H., Wang, D., and Heath, J. R. (2007). Highly ordered nanowire arrays on plastic substrates for ultrasensitive flexible chemical sensors. *Nat. Mater.* 6, 379–384. doi: 10.1038/ nmat1891

- McAlpine, M. C., Friedman, R. S., and Lieber, C. M. (2005). High-Performance Nanowire Electronics and Photonics and Nanoscale Patterning on Flexible Plastic Substrates. *Proceed. IEEE* 93, 1357–1363. doi: 10.1109/JPROC.2005.850308

- McCulloch, W. S., and Pitts, W. (1943). A logical calculus of the ideas immanent in nervous activity. *Bull. Math. Biophys.* 5, 115–133. doi: 10.1007/BF02 478259

- Mead, C., and Ismail, M. (2012). Analog VLSI Implementation of Neural Systems. Portland, OR: Springer Science & Business Media.

- Misra, J., and Saha, I. (2010). Artificial neural networks in hardware A survey of two decades of progress. *Neurocomputing* 74, 239–255. doi: 10.1016/j.neucom.2010.03.021

- Navaraj, W. T., Shakthivel, D., García Núñez, C., Liu, F., Gregory, D., and Dahiya, R. (2017). "Metal-assisted chemical etched Si nanowires for high-performance large area flexible electronics," in *Innovations in Large Area Electronics (InnoLAE 2017) Conference* (Cambridge).

- Núñez, C. G., Navaraj, W. T., Polat, E. O., and Dahiya, R. (2017). Energy autonomous flexible and transparent tactile skin. Adv. Funct. Mater. 27:1606287. doi: 10.1002/adfm.201606287

- Obradović, Z., and Parberry, I. (1994). Learning with discrete multivalued neurons. J. Comput. Sys. Sci. 49, 375–390. doi: 10.1016/S0022-0000(05) 80055-8

- Obradovic, Z., and Parberry, I. (1992). Computing with discrete multi-valued neurons. J. Comput. Sys. Sci. 45, 471–492. doi: 10.1016/0022-0000(92) 90035-H

- Patolsky, F., Timko, B. P., Yu, G., Fang, Y., Greytak, A. B., Zheng, G., et al., (2006). Detection, stimulation, and inhibition of neuronal signals with high-density nanowire transistor arrays. *Science* 313, 1100–1104. doi: 10.1126/science.1128640

- Pillai, P. B., and De Souza, M. M. (2017). A nanoionics-based three-terminal synaptic device using zinc oxide. ACS Appl. Mater. Interfaces 9, 1609–1618. doi: 10.1021/acsami.6b13746

- Polishchuk, A., Navaraj, W., Heidari, H., and Dahiya, R. (2016). "Multisensory smart glove for tactile feedback in prosthetic hand," in *Procedia Engineering* (*Eurosensors 2016*) (Budapest), 1605–1608.

- Qing, Q., Pal, S. K., Tian, B., Duan, X., Timko, B. P., Cohen-Karni, T., et al., (2010). Nanowire transistor arrays for mapping neural circuits in acute brain slices. *Proc. Natl. Acad. Sci.* 107, 1882–1887. doi: 10.1073/pnas.0914737107

- Raspopovic, S., Capogrosso, M., Petrini, F. M., Bonizzato, M., Rigosa, J., Di Pino, G., et al., (2014). Restoring natural sensory feedback in real-time bidirectional hand prostheses. *Sci. Transl. Med.* 6:222ra219. doi: 10.1126/scitranslmed.3006820

- Robinson, J., Jorgolli, M., and Park, H. (2013). Nanowire electrodes for highdensity stimulation and measurement of neural circuits. *Front. Neural Circuits* 7:38. doi: 10.3389/fncir.2013.00038

- Sengupta, A., Choday, S. H., Kim, Y., and Roy, K. (2015). Spin orbit torque based electronic neuron. *Appl. Phys. Lett.* 106:143701. doi: 10.1063/1. 4917011

- Shakthivel, D., Navaraj, W. T., García Núñez, C., Liu, F., and Dahiya, R. (2016). "Transfer printing si nanowires for flexible large area electronics," in *Innovations in Large Area Electronics (InnoLAE) Conference* (Cambridge).

- Shakthivel, D., Taube, W., Raghavan, S., and Dahiya, R. (2015). "VLS growth mechanism of Si-nanowires for flexible electronics," in 2015 11th IEEE Conference on Ph. D. Research in Microelectronics and Electronics (PRIME) (Glasgow, UK), 349–352.

- Shashank, N., Singh, V., Taube, W., and Nahar, R. (2011). Role of Interface Charges on High-k Based Poly-Si and Metal Gate Nano-Scale MOSFETs. J. Nano Electr. Phys. 3:937.

- Shibata, T., and Ohmi, T. (1992). A functional MOS transistor featuring gatelevel weighted sum and threshold operations. *IEEE Trans. Electron Dev.* 39, 1444–1455. doi: 10.1109/16.137325

- Sze, S. M., and Ng, K. K. (2006). *Physics of Semiconductor Devices*. Hoboken, NJ: John Wiley & Sons.

- Taube, W., Liu, F., Vilouras, A., Shaktivel, D., Nunez, C. G., Heidari, H., et al., (2016). "Modelling of nanowire FETs based Neural Network for Tactile Pattern Recognition in E-Skin," in *Proceedings of IEEE-Biomedical Circuits and Systems* (*BioCAS*) Conference (Shanghai).

- Tee, B. C. K., Wang, C., Allen, R., and Bao, Z. N. (2012). An electrically and mechanically self-healing composite with pressure- and flexion-sensitive properties for electronic skin applications. *Nat. Nanotechnol.* 7, 825–832. doi: 10.1038/nnano.2012.192

- Thomson, S. E., Ng, N. Y. B., Riehle, M. O., Kingham, P. J., Dahlin, L. B., Wiberg, M., et al., (2017). Bioengineered nerve conduits and wraps for peripheral nerve repair of the upper limb. *Cochrane Datab. Systemat. Rev.* CD012574. doi: 10.1002/14651858.CD012574

- Tosi, Z., and Yoshimi, J. (2016). Simbrain 3.0: a flexible, visually-oriented neural network simulator. *Neural Netw.* 83, 1–10. doi: 10.1016/j.neunet.2016.07.005

- Wang, C., Hwang, D., Yu, Z., Takei, K., Park, J., Chen, T., et al., (2013). Userinteractive electronic skin for instantaneous pressure visualization. *Nat. Mater.* 12, 899–904. doi: 10.1038/nmat3711

- Wang, D. W., Sheriff, B. A., McAlpine, M., and Heath, J. R. (2008). Development of Ultra-High Density Silicon Nanowire Arrays for Electronics Applications. *Nano Res.* 1, 9–21. doi: 10.1007/s12274-008-8005-8

- Widrow, B., and Hoff, M. E. (1960). "Adaptive switching circuits," in *IRE WESCON* Convention Record (New York, NY), 96–104.

- Yan, H., Choe, H. S., Nam, S., Hu, Y., Das, S., Klemic, J. F., et al., (2011). Programmable nanowire circuits for nanoprocessors. *Nature* 470, 240–244. doi: 10.1038/nature09749

- Yang, J. J., Strukov, D. B., and Stewart, D. R. (2013). Memristive devices for computing. *Nat. Nanotechnol.* 8, 13–24. doi: 10.1038/nnano. 2012.240

- Yogeswaran, N., Dang, W., Navaraj, W. T., Shakthivel, D., Khan, S., Polat, E. O., et al., (2015). New materials and advances in making electronic skin for interactive robots. *Advanced Robotics* 29, 1359–1373. doi: 10.1080/01691864.2015.10 95653

**Conflict of Interest Statement:** The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Copyright © 2017 Taube Navaraj, García Núñez, Shakthivel, Vinciguerra, Labeau, Gregory and Dahiya. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) or licensor are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.