## SAND79-0641C

NEUTRON IRRADIATION FOR PREVENTION OF LATCH-UP IN MOS INTEGRATED CIRCUITS\*

# MASTER

J. R. Adams and R. J. Sokel Integrated Circuit Technology Division Sandia Laboratories Albuquerque, NM 87185 This report was prepared as an account of most speakers by the United States Generators. Needer the United States Generators. Needer the United States the United States the United States not be United States the United States not any of the opposite of the United States have been as any of the United States of the United S

### I. Introduction

Bulk silicon integrated circuits can exhibit latch-up effects arising from regenerative switching in the parasitic bipolar transistors inherent in the complex circuit configurations. This is especially true for bulk CMOS integrated circuits in which a vertical NPN and lateral PNP connected in an SCR fashion occur. An extensive amount of work has been done in characterizing and preventing the latch-up which occurs from either transient ionizing radiation or from exceeding the breakdown voltage of the circuits. (See for example Refs. 1-4.) The purposes of this work were 1) to characterize the long-term annealing of neutron irradiation induced changes in the parasitic bipolar gains of MOS/LSI integrated circuits, and 2) to establish a procedure for neutron irradiation of LSI integrated circuits which would guarantee that latch-up would not occur during the normal lifetime of the circuits.

#### II. Discussion

The success of the neutron irradiation method for eliminating latch-up effects in integrated circuits rests on the fact that the minority carrier lifetime and, thus, the parasitic bipolar gain  $(\beta)$ , is

<sup>4</sup>A. Ochos "Latch-up Control in CMOS Integrated Circuits," This Conference.

<sup>\*</sup>This work supported by the U. S. Department of Energy (DOE).

<sup>&</sup>lt;sup>1</sup>B. L. Gregory and B. D. Shafer, "Latch-up in CMOS Integrated Circuits," IEEE Trans. on Nuc. Sci. NS20, 6, p. 293, December 1973

<sup>&</sup>lt;sup>2</sup>L. L. Sivo, J. Rosen, L. C. Jeffers," Latch-up Screening of LSI Devices," IEEE Trans. on Nuc. Sci NS25, 6, December 1978.

<sup>&</sup>lt;sup>3</sup>W. R. Dawes and G. F. Derbenwick, "Frevention of CMOS Latch-up by Gold Doping," IEEE Trans. on Nuc. Sci., NS23, 6, December 1976.

extremely sensitive to neutron damage. Ideally we would like to know how the structural damage introduced by the neutron irradiation affects the bipolar gains and how this damage anneals as a function of temperature and time in order to predict the long-term annealing characteristics of the parasitic bipolar gains. T. R. Waite<sup>5,6</sup> developed a model to describe the annealing of radiation damage in solids. The model assumes that the annealing mechanism is the recombination of defects with defect sinks, and ignores multiply activated processes. For recombination to occur, the defect must diffuse to within a distance ro, the reaction radius of defect sink. Therefore, the annealing process is diffusion-limited. We recognize that the general behavior of the annealing of neutron damage in silicon is too complex to be described by this simple model. However, within the temperature range and time scales of interest, the kinetics of these processes appear to be relatively insensitive to these complexities and may therefore be described in terms of this diffusion limited model.

The transport equations for this model are derived by considering the time dependence of various probability distributions. These distributions describe the spatial distribution of the defects. There are two particularly important distributions. The first is the probability per unit volume that a defect is to be found in a certain volume element and that a defect sink is to be found in another volume element. It is assumed that these defect complexes are uniformly distributed. The second distribution relates the arrangement of defect complexes which can be associated with a particular defect sink. A distribution of the form

$$\rho(r)dr = \left[c \exp \left(-\frac{r}{\lambda r_o}\right)^2\right] 4\pi r^2 dr \tag{1}$$

is assumed where C is a normalization factor and  $\lambda$  is a parameter.

The initial annealing is dominated by the correlated defect complexes and sinks which are described by the probability distribution function given in Eq. (1). The uncorrelated defects and defect sinks are uniformly distributed, and they control annealing at long times. The consequence of this model which makes it useful for the purpose of this paper is that the fraction of defects annealed,  $\phi$ , is a function of a normalized time, z, where

$$z = (4Dt/r_0^2)^{\frac{1}{2}}$$

, - (2)

<sup>5</sup>T. R. Waite, "Theoretical Treatment of the Kinetics of Diffusion Limited Reactions," Phys. Rev. 107, 463, 1957.

<sup>6</sup>T. R. Waite, "Diffusion Limited Annealing of Radiation Damage in Germanium," Phys. Rev. 107, 471, 1957.

where D is an effective diffusion coefficient given by D =  $D_0$ exp (-E<sub>A</sub>/kT). Because  $\phi$  is a function of the dimensionless quantity, z, all annealing data should lie on a single universal curve once it has been properly normalized according to Eq. (2).

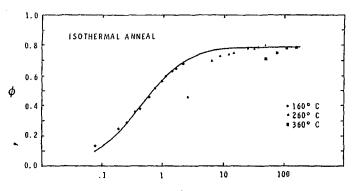

Shown in Figure (1) is  $\phi(z)$  which has been fit with experimental data obtained by measuring bipolar transistor gains on a CMOS structure. To translate bipolar gains into fraction of defects annealed, we have assumed that

$$\frac{1}{\tau(t)} = \frac{1}{\tau_0} + \alpha N(t) \quad , \text{ and } \phi(t) = \frac{\frac{1}{\tau_{post}} - \frac{1}{\tau(t)}}{\frac{1}{\tau_{post}} - \frac{1}{\tau_0}}$$

(3)

where  $au_0$  is the intrinsic minority carrier lifetime, N(t) is the density of defects as a function of time, au is a constant,  $\phi(t)$  is the fraction of defects annealed, and  $au_{\rm post}$  is the minority carrier lifetime after neutron irradiation. The lifetime is calculated from the measured bipolar gains according to the relationships given in Ref. 7.

Admittedly, the procedure for calculating fraction of defects annealed from bipolar gains is an approximate one. Nevertheless, the data, so analyzed, fit the theory rather well. The best fit of the data is obtained with an activation energy of 1.40 eV which is in good agreement with the activation energy for the annealing of divacancies. This is a "worst case" value for the data. Therefore, at high temperature the actual amount of annealing will be less than predicted by this value of the activation energy.

## III. Experimental

Three MOS circuit technologies which are known to exhibit latch-up without some form of 1 fetime control to lower parasitic bipolar gains were investigated. These were (1) metal gate CMOS technology typified by the RCA CD-4000 series, (2) closed geometry silicon gate technology represented by the RCA CDP-1802 microprocessor, and (3) a p-channel MNOS nonvolatile memory technology.

<sup>7</sup>A. S. Grove, "Physics and Technology of Semiconductor Devices," Wiley, New York, p. 220, 1967.

<sup>8</sup>B. L. Gregory and C. W. Gwyn, "Radiation Damage in Semiconductor Devices," SC-M-710887, Vol. 1, Sandia Laboratories, Albuquerque, NM, March 1972.

Devices from these three technologies were neutron irradiated in a bare critical reactor 9 (E > 10KeV) to neutron fluences between 1 x  $10^{13}$  n/cm² and 2 x  $10^{14}$  n/cm². This type of reactor is preferred since the "hard" neutron spectrum is quite effective in reducing lifetime and the neutron-to-gamma ratio is inherently high. A 10 cm-thick lead wall and a boron shield were used between the reactor and the integrated circuit wafers to increase the neutron-to-gamma ratio and attenuate the low-energy thermal neutrons.

The annealing characteristics of the parasitic bipolar transistor gains were determined using both isothermal and isochronal annealing techniques up to  $400^{\rm PC}$  and were found to fit the model for annealing of defect complexes discussed above. Using this model, a procedure has been established for neutron irradiation of circuits which guarantees that latch-up will not occur. This procedure is applicable to a wide range of technologies and design rules. For the three technologies described above, a neutron fluence of  $1 \times 10^{14} \rm n/cm^2$  followed by a suitable anneal to remove ionizing radiation effects and the fast annealing correlated defects, is sufficient to guarantee a latch-up free lifetime of greater than  $10^3$  years at  $125^{\rm PC}$ . This procedure is being used on a routine basis on both wafer and packaged devices to prevent latch-up and to improve the transient upset level of many types of MOS integrated circuits.

Figure 1

Fraction of lifetime annealed as a function of normalized time, 1. Annealing data are fit to the theoretical curve (soild line) using the procdure described in the text with an activation energy, b<sub>0</sub> = 1.4 eV.

<sup>9</sup>L. M. Choate and T. R. Schmidt, "New Neutron Simulation Capabilities Provided by the Sandia Pulse Reactor-III (SPR-III) and the Upgraded Annular Core Pulse Reactor (ACPR)," IEEE Trans. on Nuc. Sci. NS25, 6, December 1978.