Open access • Proceedings Article • DOI:10.23919/ISPSD.2017.7988914

## New calorimetrie power transistor soft-switching loss measurement based on accurate temperature rise monitoring — Source link $\square$

Dominik Neumayr, Mattia Guacci, Dominik Bortis, Johann W. Kolar

Institutions: ETH Zurich

Published on: 01 May 2017 - International Symposium on Power Semiconductor Devices and IC's

Topics: Power semiconductor device, Measuring principle and Heat sink

Related papers:

- Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10-kV SiC mosfets and Diodes

- Accuracy Study of Calorimetric Switching Loss Energy Measurements for Wide Bandgap Power Transistors

- · Heat flux sensor for power loss measurements of switching devices

- Optimization of the Driver of GaN Power Transistors Through Measurement of Their Thermal Behavior

- · Heat flux-based sensor for the measurement of the power dissipated by switching devices

Share this paper: 🚯 🄰 🛅 🗠

## **ETH** zürich

# New Calorimetric Power Transistor Soft-Switching Loss Measurement Based on Accurate Temperature Rise Monitoring

**Conference Paper**

Author(s): Neumayr, Dominik; Guacci, Mattia; Bortis, Dominik (D; Kolar, Johann W.

Publication date: 2017

Permanent link: https://doi.org/10.3929/ethz-b-000187520

Rights / license: In Copyright - Non-Commercial Use Permitted

Originally published in: https://doi.org/10.23919/ISPSD.2017.7988914

### New Calorimetric Power Transistor Soft-Switching Loss Measurement Based on Accurate Temperature Rise Monitoring

D. Neumayr, M. Guacci, D. Bortis, and J. W. Kolar

Power Electronic Systems Laboratory, ETH Zurich, Switzerland. Email: neumayr@lem.ee.ethz.ch

Abstract—Modern GaN and SiC power semiconductors require new experimental methods for determining switching losses as the widely accepted double-pulse-test (DPT) fails to accurately capture the dissipated energy during a switching transition because of electrical measurement limitations imposed by the very fast switching of WBG devices. In this paper, a new calorimetric measurement principle which relies on temperature rise monitoring of an aluminum heat sink during continuous operation of the attached power semiconductor is presented. Unlike traditional calorimetric methods, a single measurement can be performed in minutes. Using the proposed measurement principle, a soft-switching performance evaluation of selected  $600 \vee$  GaN, SiC and Si power transistors is provided.

Index Terms—WBG Power Semiconductor, Soft-Switching Losses, ZVS Losses, Calorimetric Measurement

#### I. INTRODUCTION

Targeting maximal power density in kW-scale 400 V dc/ac converter systems and pushing the switching frequency above 1 MHz, a good knowledge of soft-switching losses is crucial for an optimal design of the power electronic system. Since power semiconductor soft-switching losses are challenging to model mathematically [1] and very much depend on the employed gate-driver and PCB layout, typically empirical loss data obtained from experimental measurements with prototype hardware is used. A well known and widely accepted technique is the double-pulse test (DPT, [2]), where switching losses are calculated from electrical voltage and current measurements of the device during a turn-on and turn-off transient. Unfortunately, for fast switching transients in the ns-range which are typically achieved with WBG devices, the accuracy of the measured soft-switching losses is not satisfying [3]. Instead of measuring individual switching transients, the switching losses can be determined by measuring the average losses provided to the experimental setup during continuous operation without load and then subtract conduction losses and losses in the inductor, where the latter can be calculated [4] or measured calorimetrically [5]. Advantageously, the losses generated in the power semiconductors can also be measured directly as presented in [3], [6], where the temperature excursion of a heat sink attached to the power transistor is monitored. This calorimetric measurement principle is adopted and refined in this paper to characterize soft-switching losses of 600 V WBG power transistors and to compare them to the latest generation of 600 V Si superjunction MOSFETs.

Since this study is motivated by the optimization of a high power density 400 V DC/AC converter system, solely power transistors which are available in a very low-inductance and compact surface-mount package were selected and both power transistors of a half-brdige are connected to a common heat sink to achieve a low-inductance layout.

#### II. CALORIMETRIC MEASUREMENT SETUP

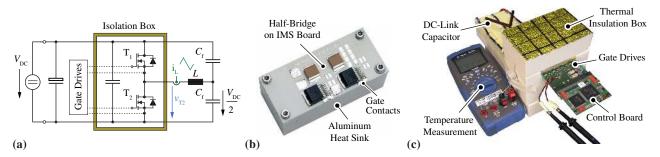

The experimental setup consists of two power devices under test (DUT,  $T_1$  &  $T_2$ ) in half-bridge configuration and a LC output filter with filter capacitors connected to negative and positive DC rail as shown in Fig. 1 (a). The half-bridge is operated continuously with 50 % duty-cycle with symmetrical triangular current in the inductor (cf. Fig. 3 (c)). For given DClink voltage, the switched current can be varied by means of altering the value of  $L (2 \mu H - 20 \mu H)$ , keeping the switching frequency in the range of 0.8 MHz - 1.2 MHz) for a high ratio of switching to total semiconductor loss,  $P_{sw}/(P_{sw}+P_{c})$ . In order to achieve a low-inductance layout of the half-bridge, both power devices are attached to a common aluminum heat sink to extract the losses during continuous operation. Knowing the thermal behavior and parameters of the setup, the total power loss can be determined through monitoring the heat sink temperature. In order to minimize the thermal resistance between the DUT and the aluminum heat sink, the half-bridge is realized with an Insulated Metal Substrate (IMS) board as depicted in Fig. 1 (b). Since the temperature rise of the heat sink characterizes the total impressed losses, it is essential to minimize any transfer of heat to the ambient by means of thermal insulation of the power stage and the aluminum heat sink as illustrated in Fig. 1 (c). Since (i) the gate drive and digital control board are located outside of the insulation box and (ii) power board (IMS) and gate drive PCB are physically separated except for short copper wires connecting the gate contacts (cf. Fig. 1 (b)), the contribution of gate drive and auxiliary power loss to the temperature rise of the heat sink is negligible.

#### A. Transient Calorimetric Measurement

Although calorimetric approaches offer several advantages over electrical switching loss measurements, often temperature readings at thermal equilibrium are needed. This results in (i) a long total measurement time and (ii) deflects the operating temperature of the DUT over a wide range during the

Fig. 1. (a) Circuit diagram of the experimental setup with two power devices under test  $(T_1, T_2)$  in half-bridge arrangement and connected LC output filter. Both power devices are attached to a common aluminum heat sink to extract the losses. (b) The power PCB is realized with a single-layer Insulated Metal Substrate (IMS) board to achieve a low thermal resistance between the DUT and the heat sink. (c) The power stage and the attached aluminum block (heat sink) are thermally insulated to the ambient. Gate drive and digital control board are located outside of the insulation box.

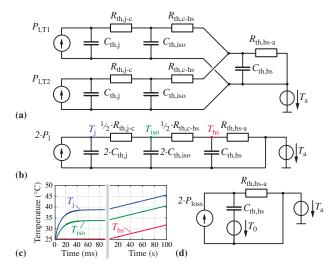

Fig. 2. (a) Thermal equivalent circuit (Cauer RC network) of the experimental setup assuming a 1-D heat flux. (b) Simplification due to symmetry of the setup. (c)-(d) Further simplification of the thermal network by neglecting the RC filter stages with comparably small time constant.

measurements. On the contrary, in the transient calorimetric measurment approach proposed in this paper, the heat sink temperature excursion is always kept between 30 °C to 40 °C and the elapsed time to reach 40 °C differs depending on the impressed power losses. Neglecting lateral heat spreading (1-D heat flow) and assuming uniform heat sink temperature, the circuit shown in Fig. 2 (a) models the thermal behavior of the experimental setup. The thermal properties of the power transistor are approximated with  $C_{th,j}$  and  $R_{th,j-c}$ . The prepreg insulation layer of the IMS board between top-side copper layer and aluminum substrate is taken into consideration with  $C_{\rm th,iso}$  and  $R_{\rm th,c-hs}$ . The thermal capacitance of the aluminum substrate and the attached large aluminum block are modeled with  $C_{\rm th,hs}$ . The thermal resistance to the ambient, kept as large as possible by means of the insulation box, is represented with  $R_{\rm th,hs-a}$ . The thermal interface formed by solder and copper layer is neglected, assuming that the temperature of the copper layer and the prepreg layer are identical  $(T_{iso})$ . Due to the symmetry of the setup, the thermal circuit can be simplified as shown Fig. 2 (b). The thermal time constants

of the first two filter stages (power transistor and prepreg layer) are much smaller compared to the filter stage formed by the aluminum block and thermal resistance to ambient as listed in Tab. II-A. The simulated temperature response as a function of time at the respective thermal interfaces due to a power step of  $2 \cdot P_1 = 20$  W at t = 0 s is illustrated in Fig. 2 (c), showing a settling of  $T_{\rm j}$  and  $T_{\rm iso}$  already after  $t \approx 80 \,\mathrm{ms}$ , whereas  $T_{\mathrm{hs}}$  has virtually not changed. Hence, if the continuous operation of the half-bridge is initiated prior to the beginning of the temperature recording such that the fast thermal transients have already settled, then the thermal behavior of the experimental system can be simplified to a first order system as shown in Fig. 2 (d) with initial heat sink temperature  $T_{\rm hs}(t=0) = T_0$ . Now, for a stepwise increase of the impressed power,  $p(t) = \sigma(t) \cdot P_1$ , the heat sink temperature increases according to

$$T_{\rm hs}(t) = R_{\rm th} P_{\rm l} + (T_0 - R_{\rm th} P_{\rm l}) \cdot e^{-\frac{t}{R_{\rm th} C_{\rm th}}}.$$

(1)

The thermal parameters of the experimental setup,  $C_{\rm th} = C_{\rm th,hs}$  and  $R_{\rm th} = R_{\rm th,h-a}$ , are identified by means of a least-mean-square (LMS) regression,

$$\min_{R,C} \sum_{k=1}^{N} \left\| \left( RP_{l,k} + (T_{0,k} - RP_{l,k}) \cdot e^{-\frac{t}{RC}} \right) - T_{hs,k} \right\|^{2}, (2)$$

with experimental data obtained from N distinct calibration measurements with known power dissipation  $P_{l,k}$  as illustrated in Fig. 3 (a). During a calibration measurement, both power transistors are kept in the on-state and a constant current  $I_s$ is forced through the transistors (DUT) and the connecting PCB tracks by means of a laboratory power supply operating in constant current mode. Varying  $I_s$  allows to adjust the dissipated power,

$$p(t) = v_{cal}(t)I_s = 2(R_{DS,on}(T_j) + R_{PCB}(T_{iso}))I_S^2$$

, (3)

with the instantaneous voltage drop  $v_{\rm cal}(t)$  across the conduction path as indicated in Fig. 3 (b). Since the on-state resistance of the DUT is strongly dependent on the operating temperature, the dissipated power is slightly increasing throughout the calibration measurements although current  $I_{\rm s}$  (cf. Fig. 3 (b)) is kept constant. For the LMS regression (2), the average power

TABLE I

Technical specifications and thermal parameters of the experimental setup

| Aluminum Block (Heat Sink) |                                         | IMS Board         |                                           | Thermal Parameters |                                    |                  |                                     |

|----------------------------|-----------------------------------------|-------------------|-------------------------------------------|--------------------|------------------------------------|------------------|-------------------------------------|

| Dimension                  | $(30 \times 70 \times 50) \text{ mm}^3$ | Dimension         | $(30 \times 70 \times 1.65) \text{ mm}^3$ | $R_{\rm th,j-c}$   | $0.49$ K/W $^{\rm i}$              | $C_{\rm th,j}$   | $0.0035$ J/K $^{\rm i}$             |

| Weight                     | 0.28 kg                                 | Alu/Prepreg thk.  | $1.5/0.1{ m mm}$                          | $R_{\rm th,c-hs}$  | $0.88$ K/W $^{\rm ii}$             | $C_{\rm th,iso}$ | $0.01 $ J/K $^{\rm ii}$             |

| $C_{\rm th, block}$        | 262 J/K                                 | $C_{\rm th,core}$ | 7.6 J/K                                   | $R_{\rm th,hs-a}$  | $18.8\mathrm{K/W}$ $^\mathrm{iii}$ | $C_{\rm th,hs}$  | $292.6\mathrm{J/K}$ $^\mathrm{iii}$ |

<sup>i</sup> Approximation of the thermal properties of power transistor specimen B (cf. Tab. II)

<sup>ii</sup> Considering chip size are of specimen B (10.05 mm × 8.68 mm) and thermal properties of the prepreg layer (FR4,  $\lambda = 1.3$  W K/m,  $\rho = 1.91$  g/cm<sup>3</sup>,  $c_{\rm th} = 0.6$  J K/g)

<sup>iii</sup> Empirically determined by means of LMS regression to measurement data (cf. Fig. 3)

over the course of the  $k^{\text{th}}$  calibration measurement,

$$P_{l,k} = \overline{p_k(t)} = \frac{1}{T_{cal,k}} \int_{t|_{T_{hs,k}=30\,^{\circ}C}}^{t|_{T_{hs,k}=40\,^{\circ}C}} v_{cal,k} \cdot I_{s,k} \, dt, \quad (4)$$

$$T_{\rm cal,k} = t|_{T_{\rm hs,k} = 40\,^{\circ}{\rm C}} - t|_{T_{\rm hs,k} = 30\,^{\circ}{\rm C}},\tag{5}$$

is considered. Moreover, the average resistance of the conduction path, valid for a heat sink temperature excursion between  $30 \text{ }^{\circ}\text{C} - 40 \text{ }^{\circ}\text{C}$  is given by

$$R_{\rm c,tot,k}(P_{\rm l,k}) = \frac{P_{\rm l,k}}{I_{\rm S,k}^2},$$

(6)

and will be needed to deduct conduction losses as discussed in the section below. Once the thermal system has been identified, the total power dissipation in the half-bridge, i. e. the sum of conduction and switching losses, during regular operation of the setup, can then be obtained by solving the LMS regression,

$$\min_{P} \left\| \left( R_{\mathrm{th}} \cdot P + (T_0 - R_{\mathrm{th}} \cdot P) \cdot \mathrm{e}^{-\frac{t}{R_{\mathrm{th}}C_{\mathrm{th}}}} \right) - T_{\mathrm{hs}} \right\|^2. (7)$$

#### B. Switching Loss Extraction

By means of the presented transient temperature measurement approach, the total power loss in the half-bridge i. e. DUT, can be determined with high accuracy. In order to extract the switching losses of the DUT, the conduction losses must be subtracted from the total power loss. In this paper, the conduction losses are calculated numerically according to,

$$P_{\rm l,c} = R_{\rm c,tot}(P_{\rm l})I_{\rm DUT}^2.$$

(8)

The total resistance of the conduction path as a function of power,  $R_{c,tot}$ , is obtained from a polynomial fit to  $\{R_{c,tot,1}, \ldots R_{c,tot,N}\}$ , the result of (4) for the N preceding calibration measurements. The RMS value of the power transistor current,  $I_{DUT} = I_{T,1} = I_{T,2}$  due to symmetry, is given by

$$I_{\rm DUT} = \sqrt{\left(\frac{1}{2} - \frac{t_{\rm d}}{T_{\rm s}}\right) \frac{I_{\rm sw}^2}{3}},\tag{9}$$

wherein the prevailing current in the inductor at the instant of switching  $I_{sw}$ , the adjusted dead-time  $t_d$  and PWM period  $T_s$ , illustrated in Fig. 3 (c), are obtained from measurement of  $i_L$  and the applied gate signals. Depending on the operating point defined by the applied DC-link voltage and the switched current level, the dead-time of the half-bridge  $t_d$ , is adjusted

Fig. 3. (a) Change of the heat sink temperature over time due to the impressed power loss of the half-bridge i. e. DUT. (b) Impressed power during calibration measurements and extraction of the temperature dependent conduction path resistance  $R_{\rm c,tot}$ . (c) RMS calculation of the transistor current from  $i_{\rm L}$  and gate-control timings.

such that the resonant transition for Zero Voltage Switching (ZVS) is completed but the conduction time of the antiparallel diode is kept at a minimum. Typically,  $t_d$  is just a small fraction of the PWM period and the conduction losses caused by the copper tracks of the IMS board during the deadtime interval are negligible compared to the switching losses (cf.  $i_{T1,c}$  and  $i_{T1}$  in Fig. 3 (c)).

#### **III. SOFT-SWITCHING BENCHMARK**

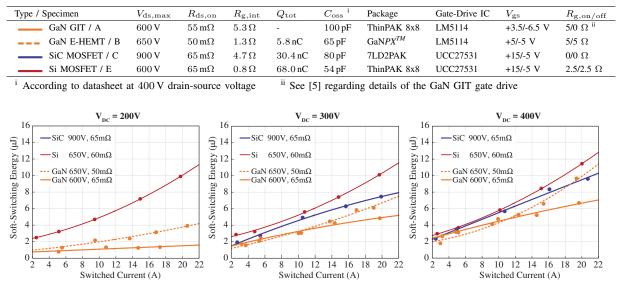

The proposed measurement technique was applied for a soft-switching performance evaluation of selected GaN and SiC power transistors and a comparison of the WBG devices to the latest generation of superjunction Si MOSFETs. As listed in Tab. II, 600 V devices (except for SiC specimen C) with an on-state resistance in the range of  $50 \text{ m}\Omega - 65 \text{ m}\Omega$  were selected for the benchmark. The employed gate drive circuits have been designed according to the specific driving requirements of the individual power devices and technical details are listed in Tab. II. Additional free-wheeling SiC diodes (C3D1P7060Q) were connected in parallel to the selected

TABLE II Selected Power Semiconductors and Technical Details

Fig. 4. Soft-switching energy dissipation ( $\mu$ J) per transistor of selected SiC, GaN and Si power semiconductors in half-bridge arrangement for switched currents in the range of 2 A – 22 A and DC-link voltages of 200 V, 300 V and 400 V. The measurement error is less than  $\pm 15$  %.

GaN power transistors. The experimental results obtained for the considered power devices in half-bridge arrangement are given in Fig. 4, showing the energy dissipation in µJ per power transistor caused by a soft-switching transition (ZVS) for a device current  $I_{sw}$ . The expected measurement error was calculated to be less than  $\pm 15\,\%$  in a worst case consideration. It can be clearly seen that the selected GaN power devices are leading the benchmark. In particular specimen A features the lowest energy dissipation of  $2\,\mu\text{J}$  –  $7\,\mu\text{J}$  at  $400\,\text{V}$  DC-link voltage. The 900 V SiC device, specimen C, exhibits a slightly higher energy dissipation close to 10 µJ at the max. switched current. Interestingly, the performance of the tested 600 V, 7<sup>th</sup>generation Si MOSFET, specimen E, exhibits a soft-switching performance very similar to the tested WBG devices. In case of the Si MOSFET, the remaining soft-switching losses can be attributed to a distinctive hysteresis in the output capacitance, i. e. a lossy charging of  $C_{\rm oss}$ , as described in [7]. However, for the GaN and SiC power transistors further investigations are needed to identify the physical origin of the remaining soft-switching losses.

#### IV. CONCLUSION

In this paper a new transient calorimetric measurement technique to accurately determine the soft-switching losses of fast switching power semiconductors is presented. The method, based on heat sink temperature rise monitoring, allows to quickly (1 min - 15 min per measurement depending on operating point) and accurately  $(\pm 15\% \text{ error})$  determine the soft-switching losses of power transistors in half-bridge arrangement. Applying the proposed measurement principle, a soft-switching benchmark of selected 600 V GaN, SiC and superjunction Si devices with low-inductacne SMD packages and similar on-state resistance was performed. The experi-

mental results revealed that at 400 V DC-link voltage and switched currents in the range of 2 A - 20 A, the selected power transistors exhibit an energy dissipation in the range of  $2 \mu \text{J} - 12 \mu \text{J}$ , whereby the tested GaN GIT showed the best performance. The tested 600 V Si superjunction MOSFET showed a soft-switching performance comparable to the 900 V SiC MOSFET. It is the topic of ongoing research to identify the origin of this remaining switching losses, as simulation results confirm that they can not be attributed to deficiencies in the gate driving of the power transistors or circuit layout.

#### REFERENCES

- M. R. Ahmed, R. Todd, and A. J. Forsyth, "Analysis of SiC MOSFETs Under Hard and Soft-Switching," in *Proc. of the IEEE Energy Convers. Congr. Expo. (ECCE USA)*, 2015.

- [2] Z. Zhang, B. Guo, F. Wang, L. M. Tolbert, B. J. Blalock, Z. Liang, and P. Ning, "Methodology for Switching Characterization Evaluation of Wide Band-Gap Devices in a Phase-Leg Configuration," in *Proc. of the* 29th IEEE Appl. Power Electron. Conf. Expo. (APEC), 2014.

- [3] D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10kV SiC MOSFETs," in *Proc. of the 7th Intern. Symposium on Power Electron. for Distributed Gen. Systems (PEDG)*, 2016.

- [4] J. Brandelero, B. Cougo, T. Meynard, and N. Videau, "A Non-Intrusive Method for Measuring Switching Losses of GaN Power Transistors," in Proc. of the 39th Annual Conf. of the IEEE Industrial Electron. Society (IECON), 2013.

- [5] D. Bortis, D. Neumayr, O. Knecht, and J. W. Kolar, "Comprehensive Evaluation of GaN GIT in Low- and High-Frequency Bridge Leg Applications," in *Proc. of the IEEE Energy Convers. Congr. Expo. (ECCE* ASIA), 2016.

- [6] L. Hoffmann, C. Gautier, S. Lefebvre, and F. Costa, "Optimization of the Driver of GaN Power Transistors through Measurement of their Thermal Behavior," *IEEE Trans. on Power Electron.*, vol. 29, no. 5, pp. 2359– 2366, 2014.

- [7] J. B. Fedison, M. Fornage, M. J. Harrison, and D. R. Zimmanck, "Coss Related Energy Loss in Power MOSFETs Used in Zero-Voltage-Switched Applications," in *Proc. of the 29th IEEE Appl. Power Electron. Conf. Expo. (APEC)*, 2014.