## New fundamental insights into capacitance modeling of laterally non-uniform MOS devices

*Citation for published version (APA):* Aarts, A. C. T., Hout, van der, R., Paasschens, J. C. J., Scholten, A. J., Willemsen, M. B., & Klaassen, D. B. M. (2006). New fundamental insights into capacitance modeling of laterally non-uniform MOS devices. (CASAreport; Vol. 0620). Technische Universiteit Eindhoven.

Document status and date: Published: 01/01/2006

### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# New fundamental insights into capacitance modeling of laterally non-uniform MOS devices

A.C.T. Aarts, R. van der Hout, J.C.J. Paasschens, A.J. Scholten, M.B. Willemsen, and D.B.M. Klaassen, *Member, IEEE*

Abstract-In compact transistor modeling for circuit simulation, the capacitances of conventional MOS devices are commonly determined as the derivatives of terminal charges, which in their turn are obtained from the so-called Ward-Dutton charge partitioning scheme. For devices with a laterally non-uniform channel doping profile, however, it is shown in this paper that no terminal charges exist from which the capacitances can be derived. Instead, for such devices a new model is presented for the capacitances themselves. Furthermore, a method is given to incorporate such a capacitance model into circuit simulators, which are traditionally based on terminal charge models. Comparison with 2-D device simulations and a segmentation model shows that for a constant mobility the new capacitance model provides an accurate description for a MOSFET with a laterally diffused channel doping profile. Through a comparison with high-frequency measurements the agreement between model and experimental results is discussed.

*Index Terms*—Diffused Doping, LDMOS, Modeling, Charge Partitioning, Integrated Circuit Design.

#### I. INTRODUCTION

DMOS devices are well-known examples of MOS devices with a laterally non-uniform channel doping profile. Accurate modeling of the capacitances in high-voltage LDMOS devices is a prerequisite for integrated RF-design of, for instance, switched-mode power supplies and power amplifiers. For high-voltage devices often the sub-circuit model approach is followed, but the effect of the lateral non-uniformity in the channel is usually neglected [1]-[4]. In the sub-circuit models of [5] and [6], the lateral non-uniformity is taken into account, but results have been limited to the dc-behavior and its conductances. For capacitance modeling, efforts have been taken to incorporate the lateral channel non-uniformity in a terminal charge model [7]-[9]. However, we have shown [10] that incorporation of the lateral channel non-uniformity via a terminal charge model is incorrect. Instead, we have developed a new capacitance model, which takes into account the lateral non-uniformity. Furthermore, we have provided a method to incorporate such a capacitance model into circuit simulators which are traditionally based on terminal charge models.

A.C.T. Aarts was with Philips Research Laboratories, Eindhoven, 5656 AA Eindhoven, The Netherlands. She is now with the Department of Mathematics and Computer Science, Eindhoven University of Technology, Eindhoven 5600 MB, The Netherlands (e-mail: a.c.t.aarts@tue.nl).

In this paper, the results of [10] are elaborated, and the new capacitance model is derived in detail. Furthermore, we show additional, experimental results by comparing this capacitance model with high-frequency measurements performed on a MOSFET with a laterally diffused channel doping profile. In Sec. II the typical capacitance behavior of laterally nonuniform MOS devices, like an LDMOS transistor, is shown, and in Sec. III the charge and capacitance modeling of uniform MOSFETs is recalled. In Sec. IV it is shown that a terminal charge model does not exist for the description of the capacitances of laterally non-uniform devices. Next, in Sec. V the new capacitance model for laterally non-uniform MOS devices is derived. In Sec. VI the method for incorporation of the capacitance model into a circuit simulator (traditionally based on charge models) is demonstrated. Finally, in Sec. VII the new capacitance model is verified by comparison with high-frequency measurements, 2-D device simulations, and circuit simulations using a segmentation approach [11].

#### II. LDMOS DEVICES

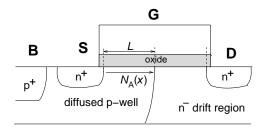

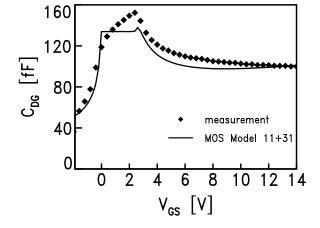

In Fig. 1 a cross-section of an LDMOS device is given. Due to diffusion from the source-side, the p-well doping of the LDMOS device decreases from source (S) to drain (D). In this way, a laterally non-uniform inversion channel region is formed with its doping concentration  $N_A(x)$  being dependent on the lateral position x along the channel. The n<sup>-</sup>-drift region is needed to withstand high voltages applied between source and drain. In the specific LDMOS device of Fig. 1, the gate (G) extends over the drift region. In Fig. 2 a typical capacitance measurement on such an LDMOS device is shown, together with the simulation result of a sub-circuit model comprising MOS Model 11 (MM11; [12]) for the channel region and MOS Model 31 (MM31; [12]) for the drift region. Notice that the oxide of an LDMOS device is sufficiently thick to have no gate leakage.

Fig. 1. Cross-section of an LDMOS device with a diffused p-well MOS channel region and an  $n^-$ -type drift region.

R. van der Hout is with the University of Leiden, Leiden, The Netherlands, and also with Philips Research Laboratories, Eindhoven, 5656 AA, The Netherlands.

J.C.J. Paasschens is with Philips Semiconductors, Nijmegen, The Netherlands.

A.J. Scholten, M.B. Willemsen, and D.B.M. Klaassen are with Philips Research Laboratories, Eindhoven 5656 AA The Netherlands.

Fig. 2. Drain-gate capacitance of an LDMOS device at  $V_{\rm DS} = 0$  V: symbols represent measurements and the solid line represents sub-circuit model simulations. The device has a total oxide capacitance of 180fF and a threshold voltage of 2.8 V. Note that the threshold voltage in the sub-circuit model is dictated by the *I*-V characteristics, which is determined by the threshold voltage of the channel region at the source side.

The discrepancy between measurements and the sub-circuit model seen in Fig. 2 around the threshold voltage, triggered device simulations of a MOSFET with a non-uniform channel doping profile but without a drift region. For the non-uniform channel doping profile an exponential decay according to

$$N_A(x) = N_{A0} \exp\left[-D\left(\frac{x}{L}\right)^2\right] \tag{1}$$

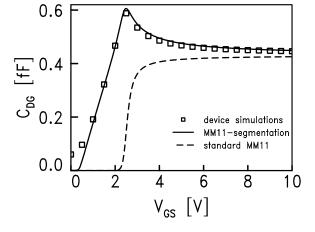

is taken, where  $N_{A0}$  represents the doping concentration at the source (x = 0), and D (D > 0) represents the decay towards the drain (x = L). For such a MOSFET, the drain-gate capacitance obtained by device simulations using MEDICI is plotted in Fig. 3. In this figure we observe that a standard MOS model, like MM11, is not capable of describing the typical capacitance behavior of a laterally non-uniform MOS device. By comparison with a segmentation model [11] using 20 segments each modeled by MM11 with parameters varying according to the doping profile, we conclude that the peak in the capacitance behavior is caused by the non-uniform channel doping profile. Although the capacitance behavior of the laterally non-uniform device is accurately described by the segmentation model, the use of such model with many segments has been found to be limited because of the chance of non-convergence during simulation if no additional measures are taken.

#### **III. LATERALLY UNIFORM MOSFETS**

Before turning to laterally non-uniform MOSFETs, we recall the charge- and capacitance modeling of *uniform* MOSFETs (see also [10]). As shown by [13], the total current  $I_i$  through terminal i of a uniform MOSFET is given by

$$I_i(t) = I_{\rm T}(t) + \frac{\mathrm{d}Q_i}{\mathrm{d}t},\tag{2}$$

where  $I_{\rm T}$  is the transport current and  $Q_i$  is the terminal charge in terms of the terminal voltages  $V_j$ . The source- and drain charge are obtained from the inversion charge using the wellknown Ward-Dutton charge partitioning scheme. From the

Fig. 3. Drain-gate capacitance of a MOSFET ( $C_{\rm ox} = 0.86$  fF) with a laterally non-uniform channel doping profile (D = 2.78) at  $V_{\rm DS} = 0$  V: symbols represent device simulations with MEDICI; the dashed line represents a compact model simulation with MM11; the solid line represents a circuit simulation with 20 segments each modeled by MM11 with parameters varying according to the doping profile (see also [11]).

terminal charges  $Q_i$  the capacitances  $C_{ij}$ , which are defined in terms of the Y-parameters as  $C_{ij} \equiv \text{Im}[Y_{ij}]/(2\pi f)$ , can be written as

$$C_{ij} = (2\delta_{ij} - 1)\frac{\partial Q_i}{\partial V_j}, \quad i, j = S, G, D, B$$

(3)

(see also [16]), where  $\delta_{ij}$  is the Kronecker delta, i.e.  $\delta_{ij} = 1$ , i = j and  $\delta_{ij} = 0$ ,  $i \neq j$ . Thus, the existence of a terminal charge  $Q_i$  implies

$$(2\delta_{ik} - 1)\frac{\partial C_{ij}}{\partial V_k} = (2\delta_{ij} - 1)\frac{\partial C_{ik}}{\partial V_j} \tag{4}$$

and the integral  $q_{c,i}$  of the charging current through terminal *i*, given by

$$q_{\mathrm{c},i}(t) \equiv \int_0^t \left[ I_i(\tau) - I_{\mathrm{T}}(\tau) \right] \mathrm{d}\tau,\tag{5}$$

equals zero for a closed voltage cycle in time, i.e.  $q_{c,i}(t_{cycle}) = 0$ , where  $t_{cycle}$  is the period of the cycle.

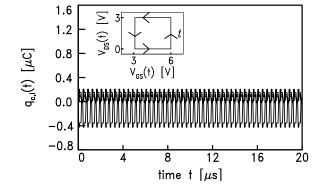

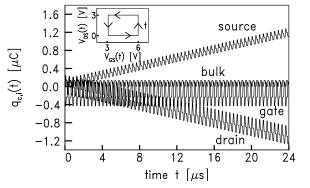

In Fig. 4 we have plotted the integral of the charging current through the drain-, gate-, source- and bulk terminal of a uniform MOSFET, described by MM11 (without gate leakage). We observe that indeed all the integrals are exactly equal to zero after a closed voltage cycle in time.

#### **IV. LATERALLY NON-UNIFORM MOSFETS**

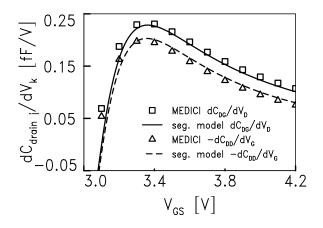

We have tested both implications (4) and (5) of the existence of terminal charges for a laterally non-uniform MOSFET, using device simulations as well as circuit simulations with the segmentation approach mentioned above (see also [10]). Again, we do not consider gate leakage, since LDMOS devices have an oxide that is sufficiently thick. In Fig. 5, we observe that  $\partial C_{\rm DG}/\partial V_{\rm D} \neq -\partial C_{\rm DD}/\partial V_{\rm G}$ , which implies that (4) does not hold for the drain-related capacitances. In Fig. 6, on the other hand, we observe that the integrals of the charging current for several closed voltage cycles in time through the bulk- and gate terminal exactly equal zero. The integrals of

Fig. 4. Integral of the charging current through the drain- source-, gateand bulk terminal of a uniform MOSFET, described by MM11, for 50 closed voltage cycles in time according to the inset ( $t_{\rm cycle} = 0.4 \ \mu s$ ).

Fig. 5. Partial derivatives of drain-related capacitances for a laterally non-uniform MOSFET with a diffused doping profile according to (1) with D = 2.78, at  $V_{\rm DS} = 0.5$  V.

the charging current through the drain- and source terminal, however, are not equal to zero.

Thus, (4) and (5) do *not* hold for the drain- and source terminal of a laterally non-uniform MOSFET. As a result, *no* terminal drain- and source charge exists for these devices. A terminal gate- and bulk charge, on the other hand, does exist (provided that there are no gate leakage currents). The above is in line with the general observations on non-linear dissipative systems [14] and with the terminal charge conservation constraints in [15]. Consequently, for a compact model of laterally non-uniform MOSFETs, instead of a terminal drain- and source charge, expressions for the capacitances have to be derived directly.

#### V. NEW CAPACITANCE MODEL FOR LATERALLY NON-UNIFORM DEVICES

The electron drain-to-source current I = I(x, t) at position x and time t is given by the transport equation and the continuity equation, according to (see [16])

$$\begin{cases} I = -W \,\mu \,Q_{\rm inv} \frac{\partial V}{\partial x}, \\ \frac{\partial I}{\partial x} = W \frac{\partial Q_{\rm inv}}{\partial t}, \end{cases}$$

(6)

Fig. 6. Integral of the charging current through the drain- source-, gateand bulk terminal of a laterally non-uniform MOSFET with a diffused doping profile according to (1) with D = 2.78, for 60 closed voltage cycles in time according to the inset ( $t_{\rm cycle} = 0.4 \ \mu s$ ), obtained using the segmentation model.

valid for 0 < x < L, where W is the width of the device, L is its length,  $\mu$  the electron mobility,  $Q_{inv}$  the inversion charge per unit area, and V = V(x,t) is the quasi-Fermi potential. With the source terminal positioned at x = 0 and the drain terminal at x = L, the boundary conditions for the quasi-Fermi potential are

$$V(0,t) = V_{\rm SB}(t),$$

$V(L,t) = V_{\rm DB}(t).$  (7)

Under the assumption of no leakage currents, the gate current  $I_{\rm G} = I_{\rm G}(t)$  is given by

$$I_{\rm G} = -W \frac{\mathrm{d}}{\mathrm{d}t} \left\{ \int_0^L Q_{\rm tot} \,\mathrm{d}x \right\},\tag{8}$$

where  $Q_{\text{tot}} = Q_{\text{inv}} + Q_{\text{bulk}}$  represents the total charge per unit area underneath the oxide, with  $Q_{\text{bulk}}$  the sum of the depletion- and accumulation charge per unit area. In the model a charge-sheet approach based on surface-potential formulations is taken. The surface potential  $\psi_{\text{s}}$  is determined in terms of the gate-bulk bias  $V_{\text{GB}}$  and the quasi-Fermi potential V from Poisson's equation and Gauss' law according to [17].

In case the MOSFET has a diffused doping profile, the doping concentration  $N_A$  is dependent on the lateral position x along the channel; see (1). As a result, the inversion charge and the total charge can be written as

$$Q_{\rm inv} = Q_{\rm inv} (V, V_{\rm GB}, x), \quad Q_{\rm tot} = Q_{\rm tot} (V, V_{\rm GB}, x),$$

(9)

i.e., with an *explicit* dependence on the lateral position x. For reasons of simplicity, we assume that the electron mobility does not depend on the doping concentration, and we neglect mobility reduction due to the longitudinal- and transversal electrical field. We remark that the approach can be extended to also include the mobility effects. For instance, the electron mobility can be taken dependent on the doping concentration  $N_A$  [18], so that it also becomes explicitly dependent on the lateral position x. Furthermore, mobility reduction due to the electrical fields can be incorporated through a dependence on the effective, global longitudinal- and transversal electrical field [12], so that it becomes explicitly dependent on the terminal voltages. Subsequently, the small-signal analysis for

determination of the capacitances can be elaborated analogously as has been done here for a uniform and constant mobility.

To determine the capacitances, we apply small-signal voltages to the terminals of the device according to

$$V_{\rm GB}(t) = \overline{V}_{\rm GB} + \overline{v}_{\rm GB} e^{j\omega t},$$

$$V_{\rm DB}(t) = \overline{V}_{\rm DB} + \overline{v}_{\rm DB} e^{j\omega t},$$

$$V_{\rm SB}(t) = \overline{V}_{\rm SB} + \overline{v}_{\rm SB} e^{j\omega t},$$

(10)

for given stationary gate-bulk bias  $\overline{V}_{\rm GB}$ , drain-bulk bias  $\overline{V}_{\rm DB}$ and source-bulk bias  $\overline{V}_{\rm SB}$ , and small-signal amplitudes  $\overline{v}_{\rm GB}$ ,  $\overline{v}_{\rm DB}$  and  $\overline{v}_{\rm SB}$ . Here,  $\omega = 2\pi f$  is the angular frequency. Due to the perturbation, the drain-to-source current, the gate current and the quasi-Fermi potential are perturbed according to

$$I(x,t) = \overline{I}(x) + [i_1(x) + j\omega i_2(x)] e^{j\omega t},$$

$$V(x,t) = \overline{V}(x) + [v_1(x) + j\omega v_2(x)] e^{j\omega t},$$

$$i_G(t) = \overline{I}_G + [i_{G1} + j\omega i_{G2}] e^{j\omega t},$$

(11)

where the variables with a bar correspond to the dc-solution. This dc-solution is given by

$$\left( \begin{array}{c} \overline{I} = -W \,\mu \,Q_{\rm inv} \left( \overline{V}(x), \overline{V}_{\rm GB}, x \right) \, \frac{\mathrm{d}\overline{V}(x)}{\mathrm{d}x}, \\ \frac{\mathrm{d}\overline{I}(x)}{\mathrm{d}x} = 0, \end{array} \right)$$

(12)

with boundary conditions  $\overline{V}(0) = \overline{V}_{SB}$  and  $\overline{V}(L) = \overline{V}_{DB}$ , and the dc-gate current equal to zero, i.e.

$$\overline{I}_{\rm G} = 0. \tag{13}$$

Substitution of (11) into (6) and (8) yields, after subtraction of the dc-solution and under neglect of the higher-order terms in  $v_1$ ,  $v_2$  and  $\overline{v}_{GB}$ , the following 6 equations for the 6 unknowns  $i_1$ ,  $i_2$ ,  $v_1$ ,  $v_2$ ,  $i_{G1}$  and  $i_{G2}$ ,

$$\begin{pmatrix}

i_1(x) = -W \mu \left[ Q_{\text{inv}} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) \frac{\mathrm{d}v_1(x)}{\mathrm{d}x} + v_1(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) \frac{\mathrm{d}\overline{V}(x)}{\mathrm{d}x} + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) \frac{\mathrm{d}\overline{V}(x)}{\mathrm{d}x} \right], \\

\left( \frac{\mathrm{d}i_1(x)}{\mathrm{d}x} = 0, \right)$$

(14)

$$i_{2}(x) = -W \mu \left[ Q_{\text{inv}} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) \frac{\mathrm{d}v_{2}(x)}{\mathrm{d}x} + v_{2}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) \frac{\mathrm{d}\overline{V}(x)}{\mathrm{d}x} \right],$$

(15)

$$\frac{\mathrm{d}i_{2}(x)}{\mathrm{d}x} = W \left[ v_{1}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) \right].$$

$$\begin{cases} i_{\rm G1} = 0, \\ i_{\rm G2} = -W \int_0^L \left[ v_1(x) \frac{\partial Q_{\rm tot}}{\partial V} \left( \overline{V}(x), \overline{V}_{\rm GB}, x \right) + \overline{v}_{\rm GB} \frac{\partial Q_{\rm tot}}{\partial \overline{V}_{\rm GB}} \left( \overline{V}(x), \overline{V}_{\rm GB}, x \right) \right] dx. \end{cases}$$

(16)

Notice that  $O(\omega^2)$ -terms have been neglected, which corresponds to the quasi-static approximation. Thus, the small-signal currents are dependent on the dc-solution. The boundary condition (7) transfers into

$$v_1(0) = \overline{v}_{SB},$$

$v_1(L) = \overline{v}_{DB},$

$v_2(0) = 0,$   $v_2(L) = 0.$  (17)

In the Appendix the solution of (14)-(16) for  $i_1$ ,  $i_2$ ,  $v_1$ ,  $v_2$ ,  $i_{G1}$  and  $i_{G2}$ , under boundary condition (17) is given.

The real part  $i_1$  of the small-signal current represents the conductances. From the imaginary parts of the small-signal currents, the capacitances are determined, as follows: For  $C_{iG}$ , i = D, G, S, B:  $\overline{v}_{DB} = \overline{v}_{SB} = 0$ :

$$C_{\rm DG} = -\frac{i_2(L)}{\overline{v}_{\rm GB}}, \quad C_{\rm SG} = \frac{i_2(0)}{\overline{v}_{\rm GB}}, \quad C_{\rm GG} = \frac{i_{\rm G2}}{\overline{v}_{\rm GB}},$$

$$C_{\rm BG} = C_{\rm GG} - C_{\rm DG} - C_{\rm SG}.$$

(18)

For  $C_{iD}$ , i = D, G, S, B:  $\overline{v}_{GB} = \overline{v}_{SB} = 0$

$$C_{\rm DD} = \frac{i_2(L)}{\overline{v}_{\rm DB}}, \quad C_{\rm SD} = \frac{i_2(0)}{\overline{v}_{\rm DB}}, \quad C_{\rm GD} = -\frac{i_{\rm G2}}{\overline{v}_{\rm DB}}, \quad (19)$$

$$C_{\rm BD} = C_{\rm DD} - C_{\rm SD} - C_{\rm GD}$$

For  $C_{iS}$ , i = D, G, S, B:  $\overline{v}_{GB} = \overline{v}_{DB} = 0$

$$C_{\rm DS} = -\frac{i_2(L)}{\overline{v}_{\rm SB}}, \quad C_{\rm SS} = -\frac{i_2(0)}{\overline{v}_{\rm SB}}, \quad C_{\rm GS} = -\frac{i_{\rm G2}}{\overline{v}_{\rm SB}},$$

$$C_{\rm BS} = C_{\rm SS} - C_{\rm DS} - C_{\rm GS}$$

(20)

For

$$C_{iB}$$

,  $i = D, G, S, B$ :

$C_{DB} = C_{DD} - C_{DG} - C_{DS}$ ,  $C_{SB} = C_{SS} - C_{SG} - C_{SD}$ ,

$C_{GB} = C_{GG} - C_{GD} - C_{GS}$ ,  $C_{BB} = C_{BS} + C_{BG} + C_{BD}$ .

(21)

Finally, we show how the lateral non-uniformity influences the capacitances in comparison to those obtained via the classical Ward-Dutton charge partitioning scheme. To that end, we consider, without loss of generality, a perturbation at the gate terminal. Since the perturbation is in time, the term between square brackets in (32) satisfies

$$v_{1}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right) + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left( \overline{V}(x), \overline{V}_{\text{GB}}, x \right)$$

$$= \frac{\mathrm{d}}{\mathrm{d} e^{j \, \omega \, t}} \left\{ Q_{\text{inv}} \left( V(x, t), V_{\text{GB}}(t), x \right) \right\}$$

$$= \overline{v}_{\text{GB}} \frac{\mathrm{d}}{\mathrm{d} V_{\text{GB}}(t)} \left\{ Q_{\text{inv}} \left( V(x, t), V_{\text{GB}}(t), x \right) \right\},$$

(22)

under neglect of higher-order terms. Substitution of (22) into (32), with the time-dependent potentials replaced by the stationary ones, yields by use of (18) for the source- and drain

related capacitances

$$C_{\rm SG} = \frac{W\mu}{L} \int_0^L \frac{v_2(x)}{\overline{v}_{\rm GB}} \frac{\partial Q_{\rm inv}}{\partial x} \left(\overline{V}_{\rm dc}, \overline{V}_{\rm GB}, x\right) dx$$

$$- \frac{d}{d\overline{V}_{\rm GB}} \left\{ W \int_0^L \left(1 - \frac{x}{L}\right) Q_{\rm inv} \left(\overline{V}_{\rm dc}, \overline{V}_{\rm GB}, x\right) dx \right\}$$

$$C_{\rm DG} = - \frac{W\mu}{L} \int_0^L \frac{v_2(x)}{\overline{v}_{\rm GB}} \frac{\partial Q_{\rm inv}}{\partial x} \left(\overline{V}_{\rm dc}, \overline{V}_{\rm GB}, x\right) dx$$

$$- \frac{d}{d\overline{V}_{\rm GB}} \left\{ W \int_0^L \frac{x}{L} Q_{\rm inv} \left(\overline{V}_{\rm dc}, \overline{V}_{\rm GB}, x\right) dx \right\},$$

(23)

where we have written  $\overline{V}_{dc} = \overline{V}_{dc} (x, \overline{V}_{GB}) = \overline{V}(x)$  to refer to the dependency of  $\overline{V}(x)$  on  $\overline{V}_{GB}$ . Since for a laterally nonuniform MOS device  $\partial Q_{inv}/\partial x \neq 0$ , the first term in the right-hand side of (23) thus represents the correction to the capacitances obtained from the classical Ward-Dutton charge partitioning scheme.

To determine the gate- and bulk related capacitances for a perturbation at the gate terminal, we notice that (22) also holds for the depletion and accumulation charge  $Q_{\text{bulk}}$  as well as for the total charge  $Q_{\text{tot}}$ . As a result, by use of (16) and (18) we obtain for the gate- and bulk related capacitances

$$C_{\rm GG} = \frac{\mathrm{d}}{\mathrm{d}\overline{V}_{\rm GB}} \left\{ -W \int_0^L Q_{\rm tot} \left(\overline{V}_{\rm dc}, \overline{V}_{\rm GB}, x\right) \mathrm{d}x \right\},$$

$$C_{\rm BG} = -\frac{\mathrm{d}}{\mathrm{d}\overline{V}_{\rm GB}} \left\{ W \int_0^L Q_{\rm bulk} \left(\overline{V}_{\rm dc}, \overline{V}_{\rm GB}, x\right) \mathrm{d}x \right\}.$$

(24)

Thus, the terms between brackets in (24) are the terminal gateand bulk charge  $Q_{\rm G}$  and  $Q_{\rm B}$ , respectively, from which the corresponding capacitances can be derived. Notice that the lateral non-uniformity is included via the dependence on the lateral position.

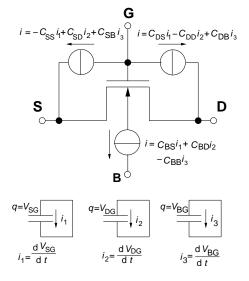

#### VI. INCORPORATION OF A CAPACITANCE MODEL INTO CIRCUIT SIMULATORS

Conventional circuit simulators are based on terminal charge models. However, in Sec. IV we have shown that for laterally non-uniform MOS devices no terminal charge model exists. Therefore, we have developed a method to implement the capacitance model directly into these circuit simulators; see Fig. 7. In [10] we have shown for a three-terminal device with a laterally diffused doping profile that this method indeed yields for a closed voltage cycle in time a non-zero charging current through the source- and drain terminal and a zero charging current through the gate terminal. Furthermore, we have shown in [10] that this method yields exactly the same results as a circuit simulation using the segmentation approach. Thus, capacitance models can be successfully implemented into conventional charge-based circuit simulators.

#### VII. RESULTS

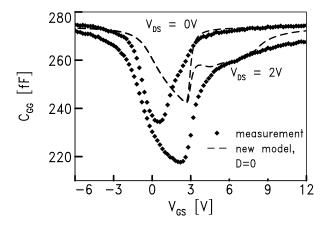

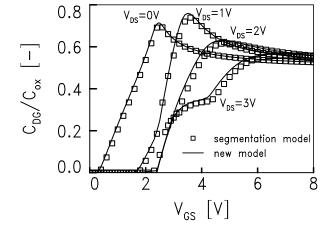

In this section the capacitances calculated from the model equations of Sec. V are shown in comparison to those obtained from high-frequency measurements (Figs. 8 and 9), 2-D device

Fig. 7. Equivalent circuit for a MOS device illustrating the method to implement a capacitance model into circuit simulators.

simulations (Figs. 10 and 11), and circuit simulations using the segmentation approach (Figs. 12 and 13). For more plots showing the comparison with 2-D device simulations and circuit simulations using the segmentation approach we refer to [10]. In the model, a diffused doping profile according to (1) is taken. In this way, D = 0 corresponds to the uniform case, while D > 0 represents a device with a laterally diffused doping profile decreasing from source to drain.

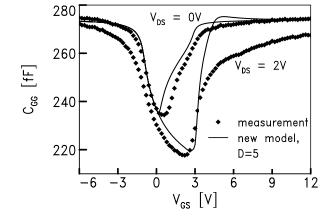

Fig. 8. Measured (symbols) gate-gate capacitance of a MOSFET with a diffused doping profile, for  $V_{\rm DS} = 0$  and 2 V. The dashed line represents the simulated capacitance of a uniform MOSFET (D = 0), using the new model.

In Figs. 8 and 9 measurements are shown of a conventional MOSFET (thus without drift region) but with a diffused doping profile. The measurements were performed on dedicated test structures, by use of an S-parameter analyzer at a frequency of f = 1 GHz. The device has an oxide thickness of 40 nm, and a threshold voltage of about 3 V. In Fig. 8 we observe that the model with a uniform doping (D = 0) does not adequately predict the measured capacitance values. The plot reveals that especially in depletion the diffused doping profile has a strong impact on these capacitance values. In Fig. 9, on the other hand, we observe that the new model for a laterally

Fig. 9. Comparison of the gate-gate capacitance of a MOSFET with a diffused doping profile, between measurements (symbols) and the new model (solid lines) with D = 5.

non-uniform MOSFET with D = 5 accurately describes the effect of the diffused doping profile. In strong inversion for  $V_{\rm DS} = 2$  V, however, the model over-estimates the measured capacitance. Possible reasons are the neglect of mobility reduction due to the longitudinal and transversal fields, and the assumption that the electron mobility is independent of the doping concentration.

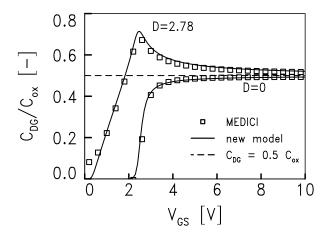

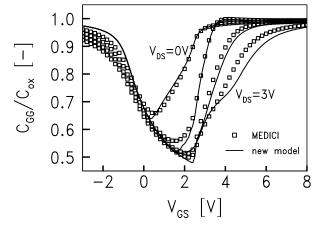

To omit the mobility effects, we compare the new capacitance model with 2D-device simulations (using MEDICI) in which we take a constant and uniform mobility. In Figs. 10 and 11 we observe that the capacitances obtained from the new model compare very well to the ones obtained from the device simulations, for both a laterally non-uniform device and a uniform device. Furthermore, in Fig. 10 the influence of the diffused doping profile is clearly seen: With the maximum value of  $C_{\rm DG}$  equal to  $0.5 \times C_{\rm ox}$  for the uniform device, but equal to  $0.7 \times C_{\rm ox}$  for the laterally non-uniform device, an increase of about 40% in maximum drain-gate capacitance is obtained due to the lateral non-uniformity.

Fig. 10. Comparison of the normalized drain-gate capacitance between MEDICI device simulations (symbols) and the new model (solid lines), for  $V_{\rm DS}=0$  V. Results are shown for a laterally diffused doping profile (D=2.78) and a uniform doping profile (D=0).

To exclude possible 2D-effects and make a one-to-one comparison, we finally compare the new capacitance model

Fig. 11. Normalised gate-gate capacitance of the new model (solid lines) compared to device simulations (symbols), for  $V_{\rm DS} = 0$ , 1, 2 and 3 V. The device has a laterally diffused doping profile with D = 2.78.

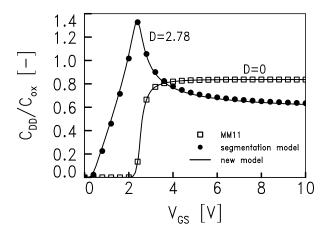

with circuit simulations using the segmentation approach. In Figs. 12 and 13 we observe that the capacitances obtained from the new model compare very well to the ones obtained from the segmentation model, for both a laterally non-uniform device and a uniform device. Furthermore, in Fig. 12 the influence of the diffused doping profile is clearly seen: The lateral non-uniformity causes the maximum value of  $C_{\rm DD}$  to exceed above the total oxide capacitance, up to a value of  $1.3 \times C_{\rm ox}$ .

Fig. 12. Normalised drain-drain capacitance for  $V_{\rm DS} = 0$  V, obtained by the new model (solid lines) in comparison to MOS Model 11 for the uniform case (D = 0), and to the segmentation model for a laterally diffused doping profile (D = 2.78), both represented by the symbols.

#### VIII. CONCLUSIONS

In this paper, we have shown that laterally non-uniform channel doping profiles in, for instance, LDMOS devices lead to a capacitance behavior that is fundamentally different from that of MOSFETs with uniform channels. Furthermore, we have demonstrated that for these devices as a consequence of the lateral non-uniformity, no terminal source- and drain charge exists. Therefore, we have derived for MOS devices with a laterally non-uniform channel doping profile a capacitance model. This model is based on surface-potential

Fig. 13. Normalised drain-gate capacitance of the new model (solid lines) compared to segmentation model (symbols), for a diffused doping profile according to (1) with D = 2.78.

formulations. Next, we have presented a method to implement the capacitance model into standard charge-based circuit simulators. Finally, a comparison with 2-D device simulations and a segmentation model demonstrates that for a constant mobility the typical capacitance behavior of laterally non-uniform MOS devices is accurately predicted by the capacitance model. A comparison with high-frequency measurements shows for low drain-source bias conditions a good agreement in all regimes ranging from accumulation and depletion to strong inversion. At elevated drain-source voltages, however, the model agrees less in strong inversion, which is is ascribed to the simplifications made in the model for the electron mobility.

#### APPENDIX

The solution of (14) for  $v_1$  and  $i_1$  is given by

$$i_1(x) = \frac{W \,\mu \, C'_{\text{ox}}}{L} \, C,$$

$$v_1(x) = e^{\Gamma(x)} \left( \overline{v}_{\text{SB}} + C \, T(x) - \overline{v}_{\text{GB}} \, S(x) \right),$$

(25)

where the functions  $\Gamma$ , T and S are given by

$$\Gamma(x) = -\int_{0}^{x} \frac{\frac{\partial Q_{\text{inv}}}{\partial V} \left(\overline{V}(s), \overline{V}_{\text{GB}}, s\right)}{Q_{\text{inv}} \left(\overline{V}(s), \overline{V}_{\text{GB}}, s\right)} \frac{d\overline{V}(s)}{ds} \, \mathrm{d}s,$$

$$T(x) = -\frac{C'_{\text{ox}}}{L} \int_{0}^{x} \frac{\mathrm{e}^{-\Gamma(s)}}{Q_{\text{inv}} \left(\overline{V}(s), \overline{V}_{\text{GB}}, s\right)} \, \mathrm{d}s,$$

$$S(x) = \int_{0}^{x} \frac{\frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left(\overline{V}(s), \overline{V}_{\text{GB}}, s\right)}{Q_{\text{inv}} \left(\overline{V}(s), \overline{V}_{\text{GB}}, s\right)} \frac{d\overline{V}(s)}{\mathrm{d}s} \, \mathrm{e}^{-\Gamma(s)} \, \mathrm{d}s.$$

(26)

and the constant C is determined from the boundary condition  $v_1(L) = \overline{v}_{\rm DB}$ , i.e.

$$C = \frac{1}{T(L)} \left( \overline{v}_{\rm DB} \,\mathrm{e}^{-\Gamma(L)} - \overline{v}_{\rm SB} + \overline{v}_{\rm GB} \,S(L) \right). \tag{27}$$

The solution of (15) for  $v_2$  is given by

$$v_2(x) = e^{\Gamma(x)} u_2(x),$$

(28)

where  $u_2$ , under boundary condition  $u_2(0) = 0$ , is given by

$$-\frac{C_{\rm ox}'}{L}u_2(x) = Q_{\rm inv}\left(\overline{V}(0), \overline{V}_{\rm GB}, 0\right) u_2'(0) T(x) -\frac{T(x)}{\mu} \int_0^x \left[v_1(s) \frac{\partial Q_{\rm inv}}{\partial V} \left(\overline{V}(s), \overline{V}_{\rm GB}, s\right) + \overline{v}_{\rm GB} \frac{\partial Q_{\rm inv}}{\partial V_{\rm GB}} \left(\overline{V}(s), \overline{V}_{\rm GB}, s\right)\right] \left(1 - \frac{T(s)}{T(x)}\right) {\rm d}s.$$

(29)

The value  $u'_{2}(0)$  is determined from the boundary condition  $u_{2}(L) = 0$ . Thus, by combining (25)-(29) with (15) and (16), we have determined the small-signal quasi-Fermi potentials  $v_{1}$  and  $v_{2}$ , and the small-signal currents  $i_{1}$ ,  $i_{2}$ ,  $i_{G1}$  and  $i_{G2}$ .

For the derivation of the capacitances we determine the imaginary parts  $i_2(0)$  and  $i_2(L)$  of the small-signal currents at the source- and drain side. To that end, we integrate the second equation of (15) twice with respect to x, and obtain

$$i_{2}(0) = \frac{1}{L} \int_{0}^{L} i_{2}(x) dx$$

$$-W \int_{0}^{L} \left(1 - \frac{x}{L}\right) \left[v_{1}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right) + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right)\right] dx,$$

$$i_{2}(L) = \frac{1}{L} \int_{0}^{L} i_{2}(x) dx$$

$$+W \int_{0}^{L} \frac{x}{L} \left[v_{1}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right) + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right)\right] dx.$$

(30)

Subsequently, with the first equation of (15) rewritten as

$$i_{2}(x) = -W \mu \left[ \frac{\mathrm{d}}{\mathrm{d}x} \left\{ v_{2}(x) Q_{\mathrm{inv}} \left( \overline{V}(x), \overline{V}_{\mathrm{GB}}, x \right) \right\} - v_{2}(x) \frac{\partial Q_{\mathrm{inv}}}{\partial x} \left( \overline{V}(x), \overline{V}_{\mathrm{GB}}, x \right) \right],$$

(31)

substitution of (31) into (30) yields, under the boundary condition  $v_2(0) = v_2(L) = 0$ ,

$$i_{2}(0) = \frac{W \mu}{L} \int_{0}^{L} v_{2}(x) \frac{\partial Q_{\text{inv}}}{\partial x} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right) dx$$

$$- W \int_{0}^{L} \left(1 - \frac{x}{L}\right) \left[v_{1}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right) + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right)\right] dx$$

$$i_{2}(L) = \frac{W \mu}{L} \int_{0}^{L} v_{2}(x) \frac{\partial Q_{\text{inv}}}{\partial x} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right) dx$$

$$+ W \int_{0}^{L} \frac{x}{L} \left[v_{1}(x) \frac{\partial Q_{\text{inv}}}{\partial V} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right) + \overline{v}_{\text{GB}} \frac{\partial Q_{\text{inv}}}{\partial V_{\text{GB}}} \left(\overline{V}(x), \overline{V}_{\text{GB}}, x\right)\right] dx.$$

(32)

Notice that in a laterally non-uniform MOS device  $\partial Q_{\text{inv}}/\partial x \neq 0$ , so that the first terms of (32) do not vanish.

#### References

- Y. Subramanian, P.O. Lauritzen and K.R. Green, "A compact Model for an IC Lateral Diffused MOSFET Using the Lumped-Charge Methodology", in *Proc. Modeling and Simulation of Microsystems*, pp. 284-288, 1999.

- [2] S.F. Frere, J. Rhayem, H.O. Adawe, R. Gillon, M. Tack and A.J. Walton, "LDMOS Capacitance Analysis versus Gate and Drain Biases, Based on Comparison Between TCAD Simulations and Measurements", in *Proc. ESSDERC*, pp. 219-222, 2001.

- [3] E.C. Griffith, S.C. Kelly, J. A. Power, D. Bain, S. Whiston, P. Elebert and M. O'Neill, in *Proc. ESSDERC*, pp. 624-627, 2000.

- [4] C. Liu and J.B. Kuo, "Quasi-Saturation Capacitance Behavior of a DMOS Device", *Trans. Electron Devices*, Vol. 44, No. 7, pp. 1117-1123, 1997.

- [5] J. Jang, O. Tornblad, T. Arnborg, Q. Chen, K. Banerjee, Z. Yu and R.W. Dutton, "RF-LDMOS Characterization and Its Compact Modeling", in *Proc. IEEE MTT-S International*, pp. 967-970, 2001.

- [6] J. Victory, C.C. Mc Andrew, R. Thoma, K. Joardar, M. Kniffin, S. Merchant and D. Moncoqut, "A Physically-Based Compact Model for LDMOS Transistors", in *Proc. SISPAD*, pp. 271-274, 1998.

- [7] N. D'Halleweyn, L. Tiemeijer, J. Benson and W. Redman-White, "Charge Model for SOI-LDMOST with Lateral Doping Gradient", in *Proc. ISPSD*, pp. 291-294, 2001.

- [8] Y. Kim, J.G. Fossum and R.K. Williams, "New Physical Insights and Models for High-Voltage LDMOST IC CAD", *IEEE Trans. Electron Devices*, Vol. 38, No. 7, pp. 1641-1649, 1991.

- [9] Y. Chung, "LADISPICE-1.2: A Nonplanar-Drift Lateral DMOS Transistor Model and its Application to Power IC TCAD", *IEE Proc. Circuits Devices Syst.*, Vol. 147, No. 4, pp. 219-227, 2000.

- [10] A.C.T. Aarts, R. van der Hout, J.C.J. Paasschens, A.J. Scholten, M. Willemsen, and D.B.M. Klaassen, "Capacitance modeling of laterally non-uniform MOS devices", in *IEDM Tech. Digest*, pp. 751-754, 2004.

- [11] A.J. Scholten, L.F. Tiemeijer, P.W.H. de Vreede and D.B.M. Klaassen, "A Large Signal Non-Quasi-Static MOS Model for RF Circuit Simulation, in *IEDM Tech. Digest*, pp. 163-166, 1999.

- [12] Internet: www.semiconductors.philips.com/Philips\_Models.

- [13] D.E. Ward, "Charge-Based modeling of capacitance in MOS transistors", *Ph.D. Thesis*, Stanford University, 1981.

- [14] H.K. Dirks, "Kapazitätskoeffizienten Nichtlinearer Dissipativer Systeme", ", Habilitationsschrift, Aachen University of Technology, 1988.

- [15] D.E. Root, "Nonlinear Charge Modeling for FET Large-Signal Simulation and its Importance for IP3 and ACPR in Communication Circuits", in *Proc. MWSCAS*, Vol. 2, pp. 768-772, 2001.

- [16] Y. Tsividis, Operation and Modeling of The MOS Transistor, 2nd ed., Mc. Graw-Hill, 1999.

- [17] C.C. McAndrew and J.J. Victory, "Accuracy of Approximations in MOSFET Charge Models", *IEEE Trans. Electron Devices*, Vol. 49, No. 1, pp. 72-81, 2002.

- [18] D.B.M. Klaassen, "A Unified Mobility Model for Device Simulation - I. Model Equations and Concentration Dependence", *Solid-State Electronics*, Vol. 35, No. 7, pp. 953-959, 1992.

**Rein van der Hout** After his Ph.D. in algebra (Utrecht University, 1975), Rein van der Hout (born 1948) joined Akzo Nobel as an applied mathematician. He specialized in differential equations and he was appointed Professor of Applied Mathematics at the University of Leiden in 1998. As from January 2003, he has been a consultant with Philips Research. During the academic year 2003/2004 he was a Visiting Professor at the International University Bremen, Germany. His main fields of interest are partial differential equations and geometric analysis.

Jeroen C.J. Paasschens was born in Valkenswaard, The Netherlands, in 1970. He received the M.Sc. degree in physics from the University of Nijmegen, The Netherlands in 1994, and the Ph.D. degree from the University of Leiden, The Netherlands in 1997. In 1998 he joined Philips Research Laboratories, Eindhoven, where he worked on bipolar device modeling for circuit simulation. Recently, he joined Philips Semiconductors, Nijmegen, where he works on device characterisation and modeling.

He is currently a member of the modeling and characterisation program committee of the Bipolar/BiCMOS Circuits and Technology Meeting (BCTM).

Andries J. Scholten received the M.Sc. and Ph.D. degrees in experimental physics from the University of Utrecht, The Netherlands, in 1991 and 1995, respectively. In 1996, he joined Philips Research Laboratories, Eindhoven, The Netherlands, where he works on compact MOS models for circuit simulation, with a focus on RF and noise modeling.

Marnix B. Willemsen was born in Leiden, The Netherlands, in 1975. He received the M.Sc. degree in physics in 1997 and the Ph.D. degree in 2001, both from Leiden University, The Netherlands. He is currently working on high-voltage RF-LDMOS modeling at Philips Research Laboratories, Eindhoven, The Netherlands.

Annemarie C.T. Aarts received the M.Sc. degree in Technical Mathematics in 1992 and the Ph.D. degree for her research in instabilities in the extrusion of polymers in 1997, both from the Eindhoven University of Technology, Eindhoven, The Netherlands. In 1997 she joined Shell International Exploration and Production, Rijswijk, The Netherlands, where she worked in reservoir engineering. In 1999 she joined Philips Research Laboratories, Eindhoven, The Netherlands, where she worked on high-voltage LDMOS modeling and characterization. Recently,

she has become an Assistant Professor at the Eindhoven University of Technology, where she works on industrial problems through mathematical modeling.

**Dirk B.M. Klaassen** received the Ph.D. degree in experimental physics from the Catholic University of Nijmegen, The Netherlands, in 1982. He then joined Philips Research Laboratories, Eindhoven, The Netherlands, where he has worked on various subjects in the field of luminescence from the solid state and modeling for silicon device simulation, most notably the Philips Unified Mobility Model. After that he switched to compact modeling for circuit simulation. He has co-developed and industrialised well-known compact models such as

Mextram, MOS Model 9, and MOS Model 11. He holds several patents, has authored and co-authored over 80 papers in scientific journals and conferences and was Short-Course Chair of the International Electron Devices Meeting (IEDM) 1999.