# New salicidation technology with Ni(Pt) alloy for MOSFETs

Mangelinck, D.; Chan, L.; Lee, Pooi See; Pey, Kin Leong; Ding, Jun; Chi, Dong Zhi

2001

Lee, P. S., Pey, K. L., Mangelick, D., Ding, J., Chi, D. Z., & Chan, L. (2001). New Salicidation Technology with Ni(Pt) Alloy for MOSFETs. IEEE Electron Device Letters, 22(12), 568-570.

https://hdl.handle.net/10356/91823

### https://doi.org/10.1109/55.974579

© 2001 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. The published version is available at: http://dx.doi.org/10.1109/55.974579.

Downloaded on 23 Aug 2022 14:07:03 SGT

## New Salicidation Technology With Ni(Pt) Alloy for MOSFETs

P. S. Lee, Member, IEEE, K. L. Pey, Member, IEEE, D. Mangelinck, J. Ding, D. Z. Chi, and L. Chan

Abstract—A novel salicide technology to improve the thermal stability of the conventional Ni silicide has been developed by employing Ni(Pt) alloy salicidation. This technique provides an effective avenue to overcome the low thermal budget (<700 °C) of the conventional Ni salicidation by forming Ni(Pt)Si. The addition of Pt has enhanced the thermal stability of NiSi. Improved sheet resistance of the salicided narrow poly-Si and active lines was achieved up to 750 °C and 700 °C for as-deposited Ni(Pt) thickness of 30 nm and 15 nm, respectively. This successfully extends the rapid thermal processing (RTP) window by delaying the nucleation of NiSi<sub>2</sub> and agglomeration. Implementation of Ni(Pt) alloyed silicidation was demonstrated on PMOSFETs with high drive current and low junction leakage.

Index Terms-Ni(Pt)Si, NiSi, salicidation.

#### I. INTRODUCTION

▼ URRENTLY, the self-aligned silicide (salicide) process is widely used to lower the gate resistance (and therefore RC delay), to reduce the source/drain parasitic resistance, and increase the drive current of MOS transistors. Scaling of the VLSI technology has caused TiSi2 to encounter incomplete phase transformation from C49 to C54 phase, resulting in higher sheet resistance on very narrow lines. CoSi<sub>2</sub> is currently being used due to the absence of sheet resistance degradation on deep submicron lines. However, high Si consumption and junction spiking may limit its applications. NiSi is a silicide material which is of much interest due to the low temperature one step annealing, lower Si consumption, and low sheet resistance which shows no linewidth dependence. Nevertheless, NiSi has been reported to agglomerate at temperatures as low as 600 °C [1], [2] and phase transformation to the high resistivity NiSi2 occurs at temperatures of 750 °C and above [3]. Recently, we have reported the enhanced thermal stability of NiSi by alloying with Pt [4]. In this letter, we report on the implementation of Ni(Pt) alloyed silicide onto device structures to realize the potential of Ni(Pt) alloy silicides in achieving a larger processing window for future silicidation applications. The improved electrical per-

K. L. Pey is with the Department of Electrical and Computing Engineering, National University of Singapore, Singapore 119670.

D. Mangelinck is with L2MP-CNRS, 13397 Marseille cedex 20, France.

D. Z. Chi is with the Institute of Materials Research and Engineering, National University of Singapore, Singapore 119670.

L. Chan is with Chartered Semiconductor Manufacturing, Ltd., Singapore 738406.

formance of the Ni(Pt) alloyed salicide scheme is reported for PMOSFETs.

#### II. EXPERIMENT

After the growth of a 6.5-nm gate oxide on (100)-p-type Si substrate, 255-nm poly-Si was deposited using LPCVD. This is followed by gate patterning and source/drain formation. The n<sup>+</sup> and p<sup>+</sup> dopings were carried out by As implant of  $2 \times 10^{15}$  cm<sup>-2</sup>, 50 keV, and BF<sub>2</sub> implant of  $2 \times 10^{15}$  cm<sup>-2</sup>, 40 keV, respectively. After thermal activation of the dopants, pure Ni and Ni(Pt) films of thickness 30 nm were sputter deposited on narrow width structures (ranging from 1  $\mu$ m to 0.23  $\mu$ m) after a dilute HF dip. In addition, 15 nm of Ni(Pt) was sputtered and salicided on patterned wafers optimized for 0.13  $\mu$ m technology with sub-0.18  $\mu$ m structures. The amount of Pt in the alloy is about 5 atomic % from the measurements using RBS (Rutherford Backscattering). Silicidation was carried out at 500 to 800 °C by rapid thermal annealing in N<sub>2</sub> ambient. Unreacted metal was removed using H<sub>2</sub>SO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub> etchants. Sheet resistance of pure Ni and Ni(Pt) salicided poly-Si and active regions was measured as a function of linewidths using Kelvin structures. Electrical characterization was performed on PMOSFETs after salicidation.

#### **III. RESULTS AND DISCUSSION**

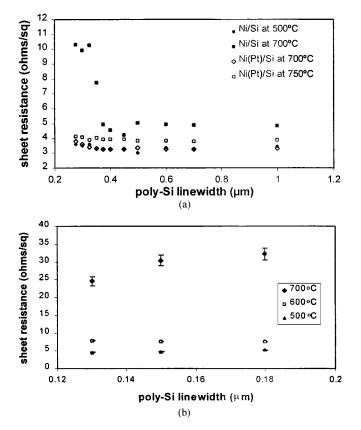

Fig. 1(a) compares the sheet resistance of Ni and Ni(Pt) salicided poly-Si lines as a function of linewidth after various silicidation temperatures. The sheet resistance of the 30 nm Ni and Ni(Pt) salicided poly-Si lines is low and uniform at low silicidation temperature of 500 °C. However, at a higher silicidation temperature of 700 °C, the sheet resistance starts to degrade on the pure Ni salicided narrow poly-Si lines due to agglomeration. On the other hand, the Ni(Pt) salicided poly-Si lines do not exhibit degradation at 700 °C. There is only a small increment in the sheet resistance on the Ni(Pt) salicided lines at 750 °C, above which severe degradation began to start. This is due to the effect of agglomeration, which has detrimental effects on narrow lines. The formation of Ni(Pt)Si at silicidation temperatures above 750 °C has been shown using micro-Raman spectroscopy on these poly-Si lines [5]. Fig. 1(b) shows the sheet resistance of the 15 nm Ni(Pt) on sub-0.18  $\mu$ m n<sup>+</sup> poly-Si lines. The sheet resistance starts to degrade at 700 °C due to agglomeration. For pure Ni with thickness of 15 nm, the sheet resistance degradation occurs at 600 °C (not shown), in accordance to the results reported by Das et al. [1] and Xu et al. [2]. The sheet resistance of Ni(Pt)Si at 700 °C is still five to six times lower than that of silicides formed using 15-nm pure Ni ( $\sim 100\Omega/sq$ ) in [6]. The Ni(Pt)Si

P. S. Lee and J. Ding are with the Department of Materials Science, National University of Singapore, Singapore 119670 (e-mail: scip8028@nus.edu.sg).

Fig. 1. (a) Sheet resistance of 30 nm of Ni and Ni(Pt) salicided poly-Si as a function of poly-Si linewidth at various salicidation temperatures. (b) Sheet resistance of 15 nm of Ni(Pt) salicided poly-Si lines of sub-0.18  $\mu$  m at various salicidation temperatures.

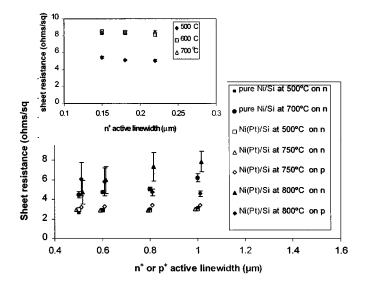

Fig. 2. Sheet resistance of Ni and Ni(Pt) salicided  $n^+$  and  $p^+$  active regions as a function of active linewidth at various salicidation temperatures. Insert plot shows the active resistance of 15 nm of Ni(Pt) on sub-0.25  $\mu$ m narrow  $n^+$  active lines.

salicided poly-Si lines has retarded agglomeration to a higher temperature than that of pure NiSi when compared at a silicidation temperature of 600-700 °C.

Fig. 2 shows the 30-nm Ni and Ni(Pt) salicided active sheet resistance of various active linewidths at different salicidation temperatures. The Ni(Pt)Si shows low sheet resistance even up

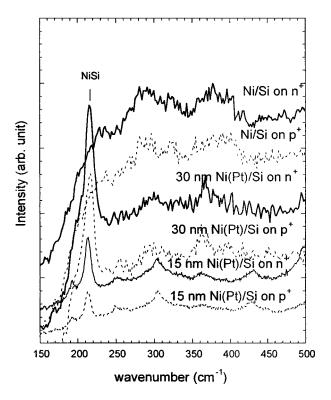

Fig. 3. Micro-Raman spectroscopy on  $n^+$  and  $p^+$  salicided device active regions using Ni and Ni(Pt) at 800  $^\circ C.$

to annealing temperature of 750 °C on both n<sup>+</sup> and p<sup>+</sup> active lines. Agglomeration started to occur at 800 °C, which is higher than that of pure Ni silicides. Low sheet resistance was also demonstrated using the 15-nm Ni(Pt) on sub-0.25  $\mu$ m n<sup>+</sup> active lines up to 700 °C as shown in the inserted plot. The phase formation on the n<sup>+</sup> and p<sup>+</sup> active regions was studied using micro-Raman as shown in Fig. 3. A strong Raman peak at 215  $cm^{-1}$  was observed on both  $n^+$  and  $p^+$  active after annealing at temperatures of 800 °C, corroborating the enhanced stability of Ni(Pt)Si even with 15-nm thin Ni(Pt) [7]. On pure Ni salicided active regions, absence of the NiSi Raman peak at 800 °C is due to the formation of NiSi<sub>2</sub>. It was previously claimed that NiSi<sub>2</sub> forms at low temperatures (~600 °C) especially on the active regions with thin Ni film [2]. The conclusion was drawn merely from the sheet resistance data without phase analysis. This deduction may have neglected the effect of agglomeration on the sheet resistance degradation, especially thin NiSi can agglomeration at such low temperatures. Despite this, we have demonstrated that the addition of Pt has delayed the NiSi2 nucleation on both narrow poly-Si and active regions even for 15-nm thin Ni(Pt) film.

The formation of NiSi<sub>2</sub> occurs through a nucleation-controlled process. Nucleation controlled reactions occurred when the change in free energy ( $\Delta G$ ) of a reaction (NiSi + Si  $\rightarrow$ NiSi<sub>2</sub>) can hardly balance the increase in interfacial energy associated with the creation of new phase ( $\Delta \sigma = \sigma$  NiSi<sub>2</sub>/Si + $\sigma$ NiSi<sub>2</sub>/NiSi  $-\sigma$  NiSi/Si). The activation energy for nucleation,  $\Delta G^*$  is related to  $\Delta \sigma^3 / \Delta G^2$  during the reaction of NiSi + Si  $\rightarrow$  NiSi<sub>2</sub>. The addition of alloying element may influence both  $\Delta \sigma$  and  $\Delta G$ . A decrease in the free energy ( $\Delta G$ ) term is due to the formation of a pseudobinary silicide solution

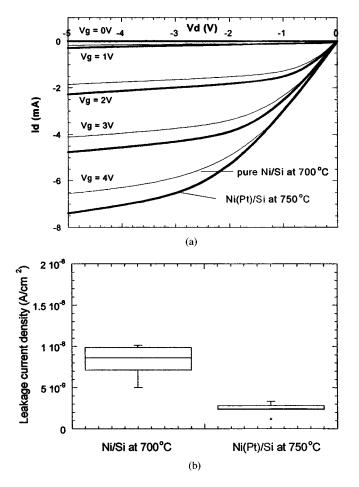

Fig. 4. (a) $I_d$ – $V_d$  characteristics for 0.35  $\mu$ m PMOS transistors with Ni monosilicide salicidation using Ni- and Ni(Pt) at 700 °C and 750 °C, respectively. (b) Leakage current density for Ni- and Ni(Pt)-salicided junctions at 700 ° and 750 °C, respectively.

Ni(Pt)Si which has a lower free energy (NiSi and PtSi are both orthorhombic silicides). The strong tendency of Ni(Pt)Si to be in texture on Si(100) was ascribed to lower the interfacial energy of Ni(Pt)Si on Si and therefore increases the  $\Delta \sigma$  [4], [8].

The Ni(Pt) salicidation scheme was integrated onto PMOS-FETs. Fig. 4(a) shows the  $I_d$ - $V_d$  characteristics of a 0.35  $\mu$ m gate length and 25  $\mu$ m width PMOSFET after salicidation using pure Ni at 700 °C and compared to Ni(Pt) salicidation at 750 °C. Both devices with monosilicide have similar  $V_{th}$ . The higher drain current of the device with Ni(Pt)Si is due to the lower sheet resistance of the source and drain region. Fig. 4(b) compares the p<sup>+</sup>/n junction leakage current density at reverse bias of 3.6 V at high silicidation temperatures. At 700 °C anneal for pure Ni-salicided junctions, the leakage current density is higher and has a wider distribution than that of Ni(Pt) salicided junctions at 750 °C. The mechanism of  $p^+/n$  junction degradation for pure NiSi at 700 °C has been attributed to the formation of some small area Schottky contacts arising from silicide spikes [9]. This provides evidence of the enhanced stability of Ni(Pt)Si with the addition of Pt.

#### IV. CONCLUSION

Ni(Pt) alloy silicide was demonstrated to improve the stability Ni(Pt)Si by delaying the NiSi<sub>2</sub> nucleation and agglomeration. PMOSFETs have shown improved drive current at high silicidation temperature of 750 °C when compared to pure Ni–salicide anneal at 700 °C. Low junction leakage can be achieved on Ni(Pt)Si junctions even at high processing temperatures. The Ni(Pt) alloy salicidation scheme has been introduced for CMOS applications, the large salicide processing window revealed its great potential for implementation onto a newly merged device (e.g., logic and DRAM) which requires large thermal budget.

#### ACKNOWLEDGMENT

The authors would like to thank R. Lee and W. D. Wang for technical assistance.

#### REFERENCES

- S. R. Das, D.-X. Xu, M. Nourmia, L. Lebrun, and A. Naem, "Thermal stability of nickel silicide films," in *Mater. Soc. Symp. Proc.*, vol. 427, 1996, p. 54.

- [2] D.-X. Xu, S. R. Das, C. J. Peters, and L. E. Erickson, "Materials aspects of nickel silcide for ULSI applications," *Thin Solid Films*, vol. 326, p. 143, 1998.

- [3] F. M d'Heurle, "Nucleation of a new phase from the interaction of two adjacent phases: some silicides," J. Mater. Res., vol. 3, p. 167, 1988.

- [4] D. Mangelinck, J. Y. Dai, J. S. Pan, and S. K. Lahiri, "Enhancement of thermal stability of NiSi films on (100)Si and (111)Si by Pt addition," *Appl. Phys. Lett.*, vol. 75, no. 12, p. 1736, 1999.

- [5] P. S. Lee, D. Mangelinck, K. L. Pey, J. Ding, T. Osipowicz, C. S. H, G. L. Chen, and L. Chan, "Characterization of Ni- and Ni(Pt)-silicides formation on narrow polycrystalline Si lines by Raman spectroscopy," in *Mater. Soc. Symp. Proc.*, vol. 591, 2000, p. 269.

- [6] T. Ohguro, M. Saito, E. Morifuji, T. Yoshitomi, T. Morimoto, H. S. Momose, Y. Katsumata, and H. Iwai, "Thermal stability of CoSi<sub>2</sub> film for CMOS salicide," *IEEE Trans. Electron Devices*, vol. 47, p. 2208, Nov. 2000.

- [7] P. S. Lee, D. Mangelinck, K. L. Pey, Z. X. Shen, J. Ding, T. Osipowicz, and A. See, "Micro-Raman spectroscopy investigations of nickel silicides and nickel (platinum) silicides," *Electrochem. Solid State Lett.*, vol. 3, no. 3, p. 153, 2000.

- [8] D. Mangelinck, J. Y. Dai, S. K. Lahiri, C. S. Ho, K. L. Pey, and T. Osipowicz, "Formation and stability of Ni(Pt) silicide on (100)Si and (111)Si," *Mater. Soc. Symp. Proc.*, vol. 564, p. 163, 1999.

- [9] D. Z. Chi, D. Mangelinck, S. K. Lahiri, P. S. Lee, and K. L. Pey, "A comparative study of current–voltage characteristics of Ni and Ni(Pt)alloy silicided p<sup>+</sup>/n diodes," *Appl. Phys. Lett.*, vol. 78, no. 21, p. 3256, 2001.