iccess Journal

Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# New type single-supply four-switch five-level inverter with frequency multiplication capability

# QINGDONG CHEN<sup>1</sup>, JIAN PAN<sup>1</sup>, SONGLIN LIU<sup>1</sup>, GUANGYI CHEN<sup>1</sup>, AND JIAXING XIONG<sup>1</sup>

<sup>1</sup>Hubei Key Laboratory for High-efficiency Utilization of Solar Energy and Operation Control of Energy Storage System, School of Electrical and Electronic Engineering, Hubei University of Technology, Wuhan 430068, China

Corresponding author: Jian Pan (e-mail: jpan@163.com )

This work was supported by the Key Laboratory Open Foundation of Hubei Province for Solar Power Generation and Energy Storage Control (HBSEES201902).

**ABSTRACT** This paper focuses on the problems of a large number of components and complex structure for traditional five-level inverters. In order to solve the problem, a novel single-supply four-switch five-level inverter topology is proposed. Based on the H4 two-level full bridge inverter, one coupling inductor and two diodes are added to constitute the proposed topology. By means of the LPS-PWM modulation strategy with frequency doubling ability, one pair of complementary power switches operate at power frequency, and the other pair of high-frequency switches operate at the half of the output sine wave modulation frequency, which effectively reduces the switching loss and electromagnetic interference resulting from high switching frequency. In addition, three kinds of extended circuits of four-switch five-levels are proposed. A comprehensive comparison against the state-of-the-art topologies in terms of the required number of components is performed to attest the outperforming merits of the proposed topology. Finally, various experimental results are presented to validate the feasibility and operability of the proposed topology.

INDEX TERMS Four-switch five-level inverter, reduce switch count, frequency doubling, THD

# I. INTRODUCTION

Inverter is the key to realize DC-AC. Multilevel inverter has the advantages of low Total Harmonic Distortion (THD) rate, low switching voltage stress and small output filter over the various types of sine wave inverter [1]-[3]. Thus, it is widely used in new energy generation, HVDC transmission, active power filter, high-power motor drive, flexible AC transmission and other fields [4]-[6]. The classical multilevel inverter (MLI) topologies include cascaded H-bridge (CHB) multilevel inverter [7], Neutral Point Clamped (NPC) multilevel inverter [8] and flying capacitor (FC) multilevel inverter [9]. However, at least eight power switches are required in the classic five-level inverter, which also needs more power components and auxiliary drive circuits. With the number of MLI levels increases, the number of components will also increase, which makes the MLI system bigger, more complex and less efficient. At the same time, it is difficult to solve the capacitor voltage balance problem existed in NPC and FC topologies [10-11].

Researchers are trying to increase the number of output voltage levels and reduce the number of switches to further

improve the efficiency and the quality of output voltage waveform [12]-[22]. An ANPC topology and decoupling algorithm are introduced in [12], which solve the problem of unbalanced neutral point potential of NPC topology capacitor. Moreover, the clamping capacitances required by traditional NPC topology are also reduced, only three capacitors and eight power switching devices are needed to realize five-level output. However, it is noted that the input DC voltage of this topology should be twice as high as the peak output voltage, which limits its application. Recently, the topology which is combined FC and NPC in [13] can realize NPC capacitor neutral point potential balance and output larger voltage with less switches. However, six switches and three capacitors are still needed in this topology. A MLI topology based on switched capacitor (SC) is proposed in [14]-[16], whose number of components is reduced by outputting a higher voltage than the input in a charge pump like manner [23]. The five-level topology based on SC introduced in [14] has twice the output voltage gain, and the voltage stress of some power switches are declined to reduce the switching loss. With a large number of components, the topology consists of two capacitors,

QD.CHEN et al.: New type single-supply four-switch five-level inverter with frequency multiplication capability

seven power switching devices and four independent diodes. The number of independent diodes is further reduced in [15]. The switched capacitor five-level topology proposed in [16] with only one capacitor as auxiliary component has twice the output voltage gain, and the voltage stress of all power switches does not exceed the input voltage. However, more power switches are needed in this topology, and it does not have the ability of frequency doubling. At the same time, the switching frequency of the power switch is high and the switching loss is serious. In [19], a five-level inverter using coupling inductors is proposed, which can achieve five-level output using only four-switches. However, four independent diodes and two reverse polarity coupled inductors are also needed in this topology. As a result, the volume and cost of the inverter system are increased.

In this paper, a novel four-switch five-level inverter and its modulation strategy are proposed. Only one coupling inductor and two diodes are added to the proposed topology which is based on the H4 full bridge inverter. It is conducive to the reduction of inverter system volume and the improvement of efficiency that the number of components and gate driving circuit are reduced. A double frequency LPS-PWM modulation strategy combined level shift and phase shift modulation is designed. The strategy is easy to implement, and the equivalent switching frequency is doubled.

This paper is organized as follows: in the second part, the topology of the proposed four-switch five-level inverter is discussed in detail, the current ripple on the coupling inductor is calculated, and the multi-carrier level pulse width modulation technology for pulse generation by gate driving circuit is discussed. In the third section, three kinds of extended circuits are given. The comparisons between the proposed topologies and advanced topology are given in the fourth part. In the fifth part, the results and analysis are given. On the experimental platform based on STM32H750VBT6, the experiments are carried out to verify its performance. Finally, the conclusion is given in the sixth part.

# II. FOUR-SWITCH FIVE-LEVEL INVERTER TOUPOLOGY

### A. OPERATION PRINCIPLES

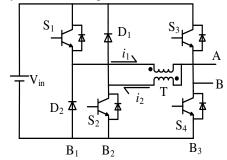

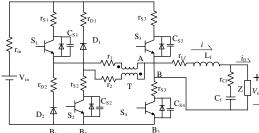

The topology of four-switch five-level inverter consisted of three legs  $B_1$ - $B_3$  is shown in Fig. 1. The switches  $S_1$  on the leg  $B_1$  and  $S_2$  on the leg  $B_2$  work at high-frequency PWM, and the switches  $S_3$  and  $S_4$  on the leg  $B_3$  work at the fundamental frequency for voltage polarity reversal. The switching frequency of  $S_1$  and  $S_2$  is only half of the modulation frequency of the output sine wave. The end points of the upper and lower windings of the reverse polarity coupling inductor are respectively connected to the midpoint of the leg  $B_1$  and leg  $B_2$ , and the freewheeling path is formed by diodes. It does not need to set the dead time for the high frequency leg, so that the reliability of the inverter system can be improved.

**IEEE**Access

FIGURE 1. Main circuit of coupled inductance five-level inverter.

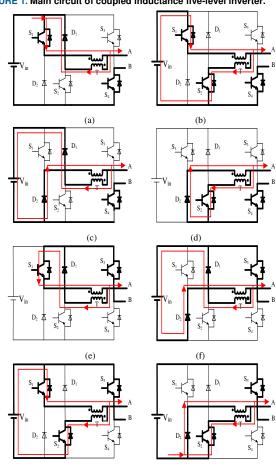

(g) (h) (h) FIGURE 2 Operation modes. (a) State A, (b) State B, (c) State C, (d) State D, (e) State E, (f) State F, (g) State G, (h) State H.

As shown in Fig. 2, all kinds of operation states of the four-switch five-level inverter are given.

State A: when the circuit is in the state shown in Fig. 2(a), the switches  $S_1$  and  $S_4$  are on, the upper winding current of the reverse polarity coupling inductor flows in through  $S_1$ , while the current of the lower winding flows out through  $D_1$ . Ignoring the forward voltage drop of diode  $D_1$ , the bus differential mode voltage  $V_{AB}$  is

$$V_{AB} = V_{in} \tag{1}$$

At this time, the voltage stress of switches  $S_2$ ,  $S_3$  and diode  $D_2$  are  $V_{in}$ .

IEEEACCESS Multidisciplinary : Rapid Review : Open Access Journal

State B: when the circuit is in the second working state shown in Fig. 2(b),  $S_1$ ,  $S_2$  and  $S_4$  are on, the upper winding current of the reverse polarity coupling inductor flows in through  $S_1$ , and the lower winding current of the reverse polarity coupling inductor flows out through  $S_2$ . The bus voltage  $V_{AB}$  is

$$V_{AB} = \frac{V_{in}}{2} \tag{2}$$

In this state, the voltage stress of switch  $S_3$  and diodes  $D_1$  and  $D_2$  are  $V_{in}$ .

State C: when the circuit is in the third working state shown in Fig. 2(c).  $S_4$  is on, the upper winding current of the reverse polarity coupling inductor flows in through  $D_2$ , and the winding current under the reverse polarity coupling inductor flows out through  $D_1$ . Without considering the forward voltage drop of diodes, the bus voltage  $V_{AB}$  is

$$V_{AB} = \frac{V_{in}}{2} \tag{3}$$

At this time, the voltage stress of switches  $S_1$ ,  $S_2$  and  $S_3$  are  $V_{in}$ .

State D: when the circuit is in the fourth working state shown in Fig. 2(d).  $S_2$  and  $S_4$  are on, the upper winding current of the reverse polarity coupling inductor flows in through  $D_1$ , and the winding current under the reverse polarity coupling inductor flows out through  $S_2$ . The bus voltage  $V_{AB}$  is

$$V_{AB} = 0 \tag{4}$$

At this time, the voltage stress of switches  $S_1,\,S_3$  and diode  $D_1$  are  $V_{\text{in.}}$

States E, F, G and H are the four working states of the proposed topology when the output voltage level is in negative half cycle, corresponding to the four working states D, C, B and A respectively. TABLE I

| SWITCHING STATES OF THR FIVE-LEVEL INVERTOR |             |                |       |       |       |  |  |

|---------------------------------------------|-------------|----------------|-------|-------|-------|--|--|

| State                                       | $V_{AB}$    | $\mathbf{S}_1$ | $S_2$ | $S_3$ | $S_4$ |  |  |

| А                                           | $V_{in}$    | 1              | 0     | 0     | 1     |  |  |

| В                                           | $V_{in}/2$  | 1              | 1     | 0     | 1     |  |  |

| С                                           | $V_{in}/2$  | 0              | 0     | 0     | 1     |  |  |

| D                                           | +0          | 0              | 1     | 0     | 1     |  |  |

| Е                                           | -0          | 1              | 0     | 1     | 0     |  |  |

| F                                           | $-V_{in}/2$ | 0              | 0     | 1     | 0     |  |  |

| G                                           | $-V_{in}/2$ | 1              | 1     | 1     | 0     |  |  |

| Н                                           | $-V_{in}$   | 0              | 1     | 1     | 0     |  |  |

The corresponding relationship between the working state of four-switch five-level inverter and the switches is shown in Table I. The switching frequency of  $S_1$  and  $S_2$  is half of the operating frequency of voltage level  $V_{AB}$ . Switches  $S_3$  and  $S_4$  used for symbol reversal work at the fundamental frequency, and the switching losses are neglected. Therefore, the total switching loss can be reduced. In the table, "1" indicates on and "0" indicates off.

## B. Current ripple on coupled inductor

The duty cycle of  $S_1$  is  $d_1$  and the duty cycle of  $S_2$  is  $d_2$ . The input voltage  $V_{in}$  and the sinusoidal voltage  $V_0$  output to the load can be regarded as ordinary step-down inverter when the inverter operates in continuous conduction mode. There are the following equations.

$d_{1} = \begin{cases} \frac{V_{0}}{V_{in}} & V_{0} \ge 0\\ 1 + \frac{V_{0}}{V_{in}} & V_{0} < 0 \\ d_{2} = 1 - d_{1} \end{cases}$ (5)

When the switches  $S_1$  and  $S_2$  are on at the same time, the voltage on the upper and lower sides of the coupling inductor both are  $V_{in}/2$ , and the current ripple is positive. When the switches  $S_1$  and  $S_2$  are off, the voltage on upper and lower sides of the coupling inductor are  $-V_{in}/2$ , and the current ripple is negative, so:

$$L\frac{\Delta i}{\Delta t} = \frac{1}{2}V_{\rm in} \tag{7}$$

$$\Delta i_{1} = \begin{cases} \frac{V_{in}d_{2}}{2Lf_{s}} & d_{2} < 0.5 \le d_{1} \\ \frac{V_{in}d_{1}}{2Lf_{s}} & d_{1} < 0.5 \le d_{2} \end{cases}$$

(8)

$$\Delta i_1 = \Delta i_2 \tag{9}$$

Where L is the coupling inductance,  $\Delta i_1$  and  $\Delta i_2$  are the ripple current of  $i_1$  and  $i_2$  at the upper and lower sides of the coupling inductor, respectively.  $f_s$  is the switching frequency.

# C. Modulation strategy

There are two kinds of multi-carrier PWM modulation methods: level shift pulse width modulation (LS-PWM) [24]-[25] and phase shift pulse width modulation (PS-PWM) [26]. However, the inverter with redundant switching states cannot be modulated by these two modulation strategies. In [27], the LPS-PWM modulation method combining LS-PWM and PS-PWM is proposed, which is applied to a seven-level inverter. A kind of LPS-PWM modulation which is suitable for the proposed five-level inverter topology is designed in this paper.

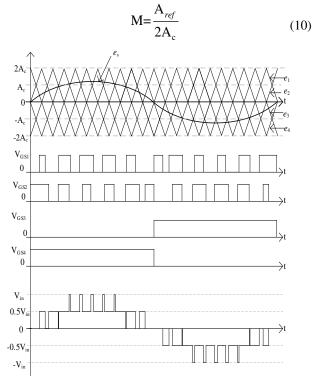

The modulation strategy for the proposed five-level inverter is shown in Fig. 3. The voltage levels of carrier  $e_1$ and  $e_3$  are the same as the voltage levels of  $e_2$  and  $e_4$ , respectively, but the phases of the two carriers at the same voltage level differ by  $\pi$ . The sinusoidal modulated signal waveform  $e_s=A_{ref}\sin 2\pi f_{ref}t$  shares the same axis with these carriers.  $A_{ref}$  is the amplitude of the sinusoidal signal waveform  $|A| < 2A_c$ , and  $f_{ref}$  is the frequency of the sinusoidal signal waveform. According to the relationship between  $e_s$  and  $e_k(k=1,2,3,4)$ , the process of five-level modulation is divided into four sectors: $R_1 \sim R_4$ , the state of two levels appears alternately in each sector.

In Fig. 3, when  $e_s \ge e_2$ , the switch  $S_1$  is ON, when  $e_s \le e_1$ , the switch  $S_2$  is ON, when  $e_s \ge e_4$ , the switch  $S_1$  is ON, when

QD.CHEN et al.: New type single-supply four-switch five-level inverter with frequency multiplication capability

**IEEE**Access

$e_s \le e_3$ , the switch S<sub>2</sub> is ON. The driving signals of switches S<sub>3</sub> and S<sub>4</sub> are fundamental wave.

The amplitude of the output voltage waveform  $V_0$  is determined by the ratio of the amplitude of the reference sinusoidal signal waveform  $e_s$  and the amplitude of the carrier. Therefore, the modulation index M is defined as:

FIGURE 3. The modulation scheme of the proposed five-level inverter.

## **III. EXTENDED TOPOLOGY**

The basic unit of the four switch five level inverter topology shown in Fig. 1 can be extended in three different ways, which will be discussed below.

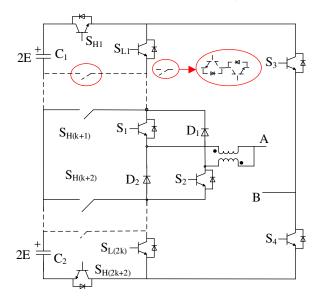

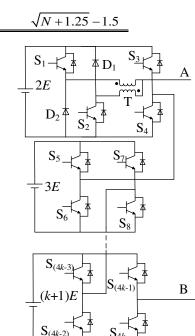

*Extension I*: As shown in Fig. 4, symmetrical capacitors and switches are added in the basic unit in this method. When a group of symmetrical capacitors and switches are added in the topology, the inclusion of a DC power supply increases the output voltage level by eight.

The total rated voltage of switching semiconductor devices in the topology can be reflected by the total standing voltage (TSV), it can be defined as

$$TSV = \frac{\sum_{i=1}^{n} V_{b_{sw,i}} + \sum_{j=1}^{m} V_{b_{sd,j}}}{V_{0_{max}}}$$

(11)

Where  $V_{b_{sw,i}}$  and  $V_{b_{d,j}}$  represents the maximum shielding voltage of each switch and diode in the topology, respectively.  $V_{o_{max}}$  is the maximum output peak voltage.

The equation of switch number  $(N_{SW})$ , the number of drive circuits  $(N_{gd})$ , the number of capacitors  $(N_C)$  and the number of levels (N) expressions of multilevel topology are

given, where k is a positive integer variable and the voltage at both ends of each capacitor is 2E.

$$N_{sw} = (6k + 6)$$

$$N_{gd} = (4k + 6)$$

$$N_{c} = (2k)$$

$$N = (8k + 1)$$

(12)

The TSV of each switch in the extended topology in Fig.4 can be calculated as

$$V_{S3} = 4kE$$

$$V_{S1} = V_{D1} = 2kE$$

$$V_{SH(k+1)} = 2kE$$

$$V_{SH_k} = V_{SL_k} = 2E$$

(13)

Therefore, the total TSV of extension I is given as

$$TSV = (2k^{2} + 22k + 4)E = \frac{(2k^{2} + 22k + 4)}{4k}V_{in} \qquad (14)$$

### FIGURE 4. Extension I of the four-switch five-level inverter.

*Extension II*: As shown in Fig.5, compared with extension I, a capacitor is added in this method.

In this extension, the number of the output voltage level increases by eight for each additional group of symmetrical capacitors and switches. The different equations of this topology shown in Fig. 5 are given as follow

$$N_{sw} = (6k+6) N_{gd} = (4k+6) N_{C} = (2k+1) N = (8k+5)$$

(15)

The TSV of each switch in the extended topology in Fig.5 can be calculated as

$$V_{S3} = (4k+2)E$$

$$V_{S1} = V_{D1} = (2k+2)E$$

$$V_{SH(k+1)} = 2kE$$

$$V_{SH1} = V_{SLk} = 2E$$

(16)

TABLE II

DIFFERENT EQUATIONS OF THE PROPOSED TOPOLOGIES Extension N<sub>SW</sub> NDC +11)1 T Π 1 Ш +1.25N + 1.25 $\sqrt{N} + 1.25$  $S_1$  $S_{H1}$ 2E $S_{L\Gamma}$ 2ED  $S_1$  $D_1 \star$  $S_{H(k+1)}$ 3E $2E^{\frac{1}{2}}$  $S_6$  $D_2$ В  $S_{(4k-3)}$ S<sub>4</sub>  $S_{L(2k)}$ 2E (k+1)E

FIGURE 5. Extension II of the four-switch five-level inverter.

Therefore, the total TSV of extension II is given as

$$TSV = (2k^{2} + 22k + 16)E = \frac{(2k^{2} + 22k + 16)}{4k + 2}V_{in} \qquad (17)$$

Extension III: As shown in Fig. 6, different types of DC are added to the cascade expansion III according to the actual demand, the number of levels also varies greatly. When the type and number of DC both are k, there are the following relationships.

$$\begin{array}{c}

\mathbf{N}_{sw} = 4k\\

\mathbf{N}_{gd} = 2k+2\\

\mathbf{N}_{DC} = k\\

\mathbf{N} = (k^2 + 3k+1)

\end{array}$$

(18)

The TSV of each switch in the extended topology shown in Fig. 6 can be calculated as

$$V_{S(4k-3)} = V_{S(4k-2)} = V_{S(4k-1)} = V_{S4k} = (k+1)E$$

$$V_{D1} = V_{D2} = 2E$$

(19)

Therefore, the total TSV of extension III is given as

$$TSV = (2k^{2} + 6k + 2)E = 4 + \frac{4}{k^{2} + 3k}V_{in}$$

(20)

Three extensions of the proposed basic unit have been summarized in Table II with equations in terms of the number of levels N.

FIGURE 6. Extension III of the four-switch five-level inverter.

# **IV COMPARATIVE STUDY**

In order to evaluate the advantages and disadvantages of the proposed topology, the comparisons of the proposed topology and other recently reported five level inverters are given in Table III. The comparisons include the number of power switches (N<sub>SW</sub>), the number of DC sources at the input side (N<sub>DC</sub>), the number of independent diodes (N<sub>d</sub>), the number of capacitors (Ncap), the number of reverse polarity coupling inductors (N<sub>T</sub>) and the topological TSV.

The proposed topology has the same number of power switches as that in [19], however, the number of independent diodes and reverse polarity coupled inductors is half of that, so the proposed topology has advantages in volume and loss.

Compared with the five-level topology reported in [12]-[18], the proposed topology has less power switches and gate drive circuits. The TSV of the proposed topology is only larger than that of the topology proposed in [13] and [16]. However, the topology described in [13] and [16] does not have the ability of frequency doubling. Therefore, under the same output waveform quality, the high-frequency switching frequency of the topology introduced in this paper is only half of that in [14], so switching loss and electromagnetic interference caused by high switching frequency can be reduced.

QD.CHEN et al.: New type single-supply four-switch five-level inverter with frequency multiplication capability

0

0

2

1

8

6

| TABLE III<br>COMPARISION OF KEY FEATURES BETWEEN THE NEW<br>TOPOLOGY AND THE RECENTLY REPORTED FIVE-LEVEL<br>INVERTER |                 |                 |       |           |                |     |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-------|-----------|----------------|-----|--|--|

| Ref.                                                                                                                  | N <sub>sw</sub> | N <sub>DC</sub> | $N_d$ | $N_{cap}$ | N <sub>T</sub> | TSV |  |  |

| [12]                                                                                                                  | 8               | 1               | 0     | 3         | 0              | 6   |  |  |

| [13]                                                                                                                  | 6               | 1               | 0     | 3         | 0              | 5   |  |  |

| [14]                                                                                                                  | 7               | 1               | 4     | 2         | 0              | 6.5 |  |  |

| [15]                                                                                                                  | 7               | 1               | 1     | 2         | 0              | 6   |  |  |

| [16]                                                                                                                  | 9               | 1               | 0     | 1         | 0              | 4.5 |  |  |

| [17]                                                                                                                  | 6               | 2               | 1     | 2         | 0              | 11  |  |  |

| [18]                                                                                                                  | 8               | 2               | 0     | 4         | 0              | 10  |  |  |

4

2

1

[19]

Proposed

4

4

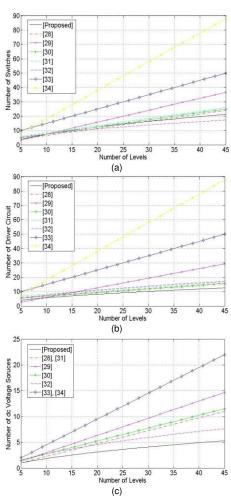

FIGURE 7. The relationships between the number of levels of expansion-III and (a) the number of switches, (b) the number of gate drive circuits and (c) the number of DC voltage sources.

The comparisons between Extension III and these topologies proposed in [28]-[34] have been given. As shown in Fig. 7, the curves that the number of switches, driving circuits and input DC voltage sources change with the increase of levels are compared respectively. The relationship between the number of switches and voltage levels is shown in Fig. 7(a). When the number of levels

continues to increase, fewer switches are required in the proposed topology. The curves of required gate drive and the number of levels is shown in Fig. 7(b). Compared with other cascaded multilevel expansion, the proposed topology has less number of gate drivers. Fig. 7 (c) shows the lower number of dc voltage source requirement of the proposed topology compared to other topologies.

FIGURE 8. The relationships between the number of levels of expansion-I, II and (a) the number of switches, (b) the number of gate drive circuits and (c) the number of DC voltage sources.

In addition, the extension I and II of the proposed topology have been compared with several other expansion circuits introduced in other literatures in Fig. 8. The curves of the number of switches and the number of gate drives with the number of levels are shown in Fig. 8(a) and (b), respectively. It should be noted that the number of gate drives of the proposed topology is consistent with the number of the switches. When the number of levels continues to increase, the number of switches and gate drives required by the proposed topology is significantly less than that of other types of single source extended circuits. The curves of the number of capacitors with the number of levels are shown in Fig. 8(c), the results show that the proposed topology also has more advantages.

# **V RESULTS AND DISCUSSION**

### A. Simulation results

As shown in Fig. 9, the MATLAB simulation model of 2kW four-switch five-level inverter is designed, where *i* and  $i_0$  are the currents flowing through the output filter inductor and the load respectively. The simulation parameters of four-switch five-level inverter are designed in Table IV. According to the data sheet of R6030ENX, the conduction resistance  $r_{s1}$ - $r_{s4}$  and drain-source capacitance  $C_{S1}$ - $C_{S4}$  of MOSFET S<sub>1</sub>-S<sub>4</sub> are determined. According to the data sheet of DSEI30, the conduction resistance  $r_{d1}$ - $r_{d2}$  and the forward conduction voltage drop of independent diodes  $D_1$ - $D_2$  are determined.

FIGURE 9. Simulation model of the proposed inverter. TABLE IV

| Parameters                                       | Value                                    |  |  |

|--------------------------------------------------|------------------------------------------|--|--|

| Input Voltage V <sub>in</sub>                    | 320V(rin:50mΩ)                           |  |  |

| Modulation index M                               | 0.9375                                   |  |  |

|                                                  | $Z_1:22.5\Omega$                         |  |  |

| Output load Z                                    | Z <sub>2</sub> :20.25Ω+31.22mH           |  |  |

|                                                  | $Z_3:20.25\Omega + 324.55\mu F$          |  |  |

| MOSFETs S1-S4                                    | r <sub>S1</sub> -r <sub>S4</sub> :0.115Ω |  |  |

| MOSFE18 51-54                                    | Cs1-Cs4:1900pF                           |  |  |

| Indonandant Diada D. D.                          | V <sub>F</sub> :1.01V                    |  |  |

| Independent Diode D <sub>1</sub> -D <sub>2</sub> | $r_{D1}$ - $r_{D2}$ :7.1m $\Omega$       |  |  |

| Coupled Inductance L                             | 2mH(r1-r2: 50mΩ)                         |  |  |

| Filter Capacitor C <sub>f</sub>                  | $16\mu F(r_f: 21.9m\Omega)$              |  |  |

| Filter Inductor L <sub>f</sub>                   | $0.25 mH(r_{\rm Lf}\!:20 m\Omega)$       |  |  |

| Switching Frequency fs                           | 16kHZ                                    |  |  |

| Frequency of the sinusoidal                      | 50HZ                                     |  |  |

| signal waveform $f_{ref}$                        | JUHZ                                     |  |  |

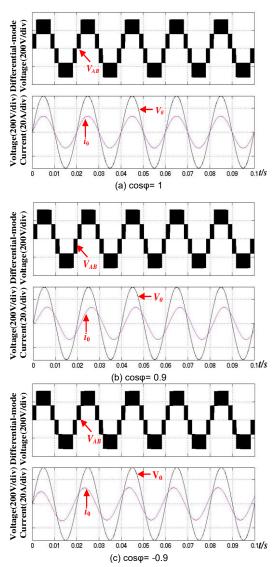

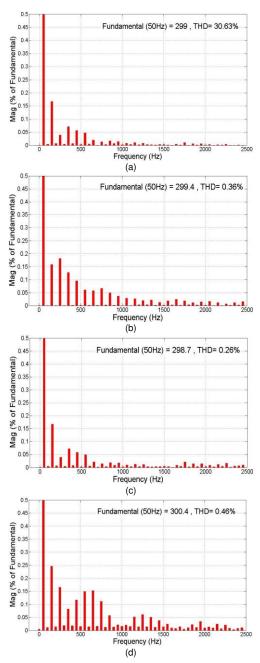

The simulation results of the proposed inverter in unity power factor and non-unit power factor (i.e.  $\cos \varphi = \pm 0.9$ ) are shown in Fig. 10. The FFT analysis under different loads is shown in Fig. 11. The THD of the five-level differential mode voltage  $V_{AB}$  in Fig. 11(a) is 30.63%, and according to [37], the calculation expression of THD is described as.

THD,%=

$$\frac{57.7}{(n-1)M}$$

,% (21)

Where n is non-negative level count. Therefore, the voltage THD at the modulation index of 0.9375 is estimated as 30.77%, which is well agreed with the experimental results.

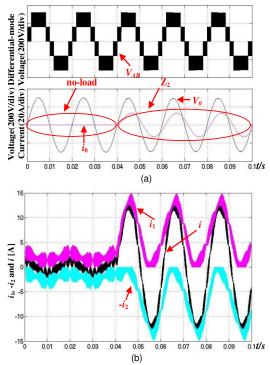

FIGURE 10. Simulation results of the reactive power adjustment capability of the five-level topology. (a)  $\cos\varphi=1$ . (b)  $\cos\varphi=0.9$ . (c)  $\cos\varphi=-0.9$ .

When the output load is Z<sub>1</sub>, the output current is in phase with the output voltage. As shown in Fig. 10(a), the THD of the current output current and the output voltage are both 0.36%. The simulation results of  $V_0$  ahead of  $i_0$  (i.e.  $\cos \varphi =$ 0.9) is shown in Fig. 10(b) when the output load is inductive load Z<sub>2</sub>. The THD of current output current and output voltage are 0.08% and 0.26% respectively. The THD of the output current in Fig. 10(b) is further reduced because the inductive load acts as a filter. In Fig. 10(c), the simulation results show that when the output load is capacitive load Z<sub>3</sub>,  $V_0$  lags  $i_0$  (i.e.  $\cos \varphi = -0.9$ ). The THD of output current and output voltage are 0.46% and 0.42% respectively. The FFT of corresponding output voltage are shown in Fig. 10(b), (c) and (d) when the load is Z<sub>1</sub>, Z<sub>2</sub> or Z<sub>3</sub>.

FIGURE 11. FFT of simulation results with (a) output five-level voltage  $V_{AB}$ . (b) output voltage  $V_0$  with Z<sub>1</sub>. (c) output voltage  $V_0$  with Z<sub>2</sub>. (d) output voltage  $V_0$  with Z<sub>3</sub>.

Fig. 12 shows the key waveform of four-switch five-level inverter when a load is suddenly added. The waveform diagrams of differential mode voltage  $V_{AB}$ , output voltage  $V_0$  and output current  $i_0$  under the condition of sudden change from no-load to inductive load  $Z_2$  are given in Fig. 12(a). The output voltage is stable and the output current can be smoothly transited. The current waveforms on the upper and lower sides of the reverse polarity coupling inductor and on the output filter inductor L are shown in Fig. 12(b). The leakage inductance current of the reverse polarity coupling inductor changes according to the

sinusoidal law, the self-current balance on the leakage inductance is realized.

**IEEE**Access

FIGURE 12. Simulation waveform when the load is suddenly changed. (a) Differential mode voltage  $V_{AB}$ , output voltage  $V_{0}$ , and current  $i_{0}$  (b) current  $i_{1}$ ,  $i_{2}$ , and i at unit power factor

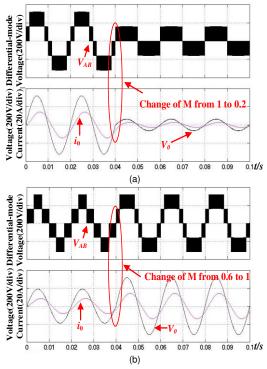

As shown in Fig. 13, the dynamic changes of M in the four-switch five-level inverter are listed when the load is  $Z_2$ . In Fig. 13(a), the modulation index increases from 0.2 to 1, while in Fig. 13(b) the modulation index is reduced from 1 to 0.6. In Fig. 13(a), although the number of levels is reduced when the modulation degree is 0.2, the dynamic performance does not decrease.

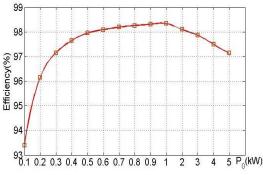

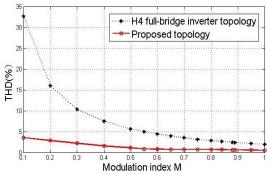

The curve of output efficiency changing with power is shown in Fig. 14 when the output load is reduced from 450 $\Omega$  to 9 $\Omega$ . When the output power P<sub>0</sub>=1.11kw, the maximum power conversion efficiency is 98.4%. The comparison curves of output voltage harmonic distortion rate between H4 full bridge inverter topology and proposed topology under different modulation index are shown in Fig. 15 when load is  $Z_1$  and output power is  $P_0=2kW$ . When H4 full bridge inverter topology and proposed topology under the same switching frequency, same filter inductance and filter capacitor, the output voltage THD of the proposed topology is significantly lower than that of the common H4 inverter topology, which means that under the same input voltage and the same THD standard, the output voltage regulation range of the proposed topology is wider than that of the H4 inverter topology.

FIGURE 13. Simulation results of propose topology when M is changed from. (a) 1.0 to 0.2 (b) 0.6 to 1.0

FIGURE 14. Efficiency of the proposed topology

FIGURE 15. The THD comparison of H4 inverter topology and proposed topology

# B. Experimental results

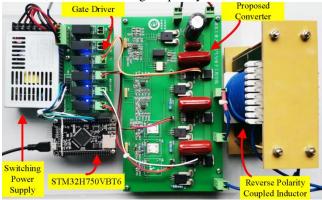

In order to verify the correctness and feasibility of the proposed five-level inverter topology and the modulation strategy, as shown in Fig. 16, a small experimental

VOLUME XX, 2020

prototype based on STM32 microprocessor was built. The control of the system is realized by STM32H750VBT6 single chip microcomputer. The DC side voltage is 100V, the AC side voltage peak value is 88V (50Hz), the load  $Z=21.4\Omega+26.7$ mH, the filter inductance is 1.1mH, and the filter capacitance is 8µF. The reverse polarity coupling inductor adopts double winding in parallel, the leakage inductance is 4.35µH, the magnetizing inductance is 2.38mH, and the switching frequency is 8kHz.

FIGURE 16. Hardware setup of the proposed inverter.

**FIGURE 17.** Experimental results of the proposed five-level inverter topology. (a) Differential mode voltage  $V_{AB}$ , output voltage  $V_0$  and output current  $i_0$ . (b) Current on both sides of reverse polarity coupling inductor.

The experimental results of four-switch five-level topology are shown in Fig. 17. As shown in Fig. 17(a), the output voltage level, filtered output voltage and output current waveform of the inverter system are presented. It should be noted that the output current  $i_0$  is slightly distorted due to the saturation of the load inductance. The current waveforms of the upper and lower sides of the

reverse polarity coupler are shown in Fig. 17(b). Because of the unidirectional current conduction of diodes  $D_1$  and  $D_2$ , the current  $i_1$  and  $-i_2$  are unipolar, and the changes of current  $i_1$  and  $-i_2$  are consistent with the theories.

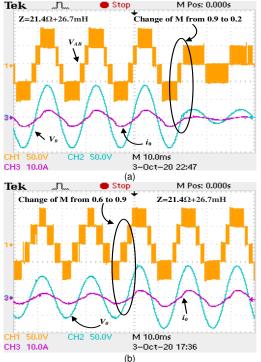

FIGURE 18. Experimental results of propose topology when M is changed from. (a) 0.9 to 0.2 (b) 0.6 to 0.9.

FIGURE 19. Experimental waveform when the load is suddenly changed, (a) the load is suddenly increased. (b) the load is suddenly reduced.

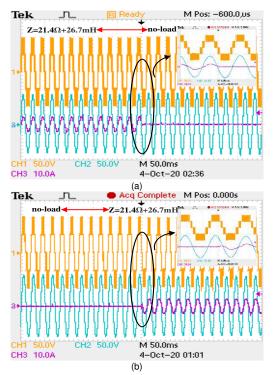

The experimental results of four-switch five-level topology with dynamic modulation in inductive load are shown in Fig. 18. In Fig. 18(a), the modulation index is reduced from 0.9 to 0.2, while in Fig. 18(b) the modulation index increased from 0.6 to 0.9. When the modulation index is dynamic, the waveform of output voltage and output current are smoothly, which means the dynamic performance is good. The experimental results when the load is suddenly changed are given in Fig. 19. The experimental results when the load is suddenly changed to no-load are shown in Fig. 19(a). Fig. 19(b) shows the experimental results when the load is suddenly added, and the experimental waveform is consistent with the simulation.

# **VI CONCLUSION**

This paper presented a novel five-level inverter topology with frequency doubling and expansion capability. The operation principle, the modulation method, analysis of the voltage stress on the coupling inductor, the comparison, simulation and experimental results of the three kinds of extended topologies are given. The number of components of the proposed five-level inverter is less than that of other five-level topologies. Because of the frequency doubling ability of the proposed topology, the switching loss is further reduced. In the simulation, the power loss analysis has been carried out, and the maximum efficiency of the proposed five-level topology reaches 98.4% when the output power is 1.1kW. In addition, three different multilevel extension circuits which have certain advantages in the number of devices are presented based on the proposed topology. In the simulation and experiment, the circuit has been confirmed by inductive load. It should be noted that the output current of the experiment is slightly distorted due to the saturation of the load inductor. In addition, the experimental results are completely consistent with the simulation results when the modulation index changes or load is suddenly changed.

# REFERENCES

- M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A new multilevel inverter topology with reduce switch count," *IEEE Access*, vol. 7, pp. 58584–58594, 2019.

- [2] Mohamad A S, Mariun N, Sulaiman N, et al, " A new cascaded multilevel inverter topology with minimum number of conducting switches," 2014 IEEE Innovative Smart Grid Technologies Asia (ISGT ASIA). Kuala Lumpur, Malaysia: IEEE, 2014: 164-169.

- [3] L. K. Haw, M. S. A. Dahidah, and H. A. F. Almurib, "Operation Mode Analysis and Peak Gain Approximation of the LLC Resonant Converter," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3577– 3588, Jul. 2015.

- [4] A. Nami, J. Liang, F. Dijkhuizen, and G. D. Demetriades, "Modular multilevel converters for HVDC applications: Review on converter cells and functionalities," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 18–36, Jan. 2015.

- [5] M. B. Ghat and A. Shukla, "A new H-Bridge hybrid modular converter (HBHMC) for HVDC application: Operating modes, control, and voltage balancing," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 6537–6554, Aug. 2018.

- 10.1109/ACCESS.2020.3035883, IEEE Access

- [6] I. A. Gowaid, G. P. Adam, A. M. Massoud, S. Ahmed, and B. W. Williams, "Hybrid and modular multilevel converter designs for isolated HVDC- DC converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 6, no. 1, pp. 188–202, Mar. 2018.

- [7] J. I. Leon, S. Vazquez, and L. G. Franquelo, "Multilevel converters: Control and modulation techniques for their operation and industrial applications," *Proc. IEEE.*, vol. 105, no. 11, pp. 2066–2081, Nov. 2017.

- [8] Siddique M D, Iqbal A, Ali J S M, et al. Design and implementation of a new unity gain nine-level active neutral point clamped multilevel inverter topology. *IET Power Electron.*, to be published, doi: 10.1049/ietpel.2020.0437.

- [9] J. Amini and M. Moallem, "A fault-diagnosis and fault-tolerant control scheme for flying capacitor multilevel inverter," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 1818–1826, Mar. 2017.

- [10] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 135–151, Jan. 2016.

- [11] R. Barzegarkhoo, H. M. Kojabadi, and L. Chang, "Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple DC link producer with reduced number of switches," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5604– 5617. Aug. 2016.

- [12] WANG Fusheng, DOU Sheng, FU Hang, ZHENG Deyou, Do Thanh Hieu, and Llu Fang, "An Optimized Decoupling Control Algorithm Between Flying Capacitor Voltage and Neutral-point Potential in ANPC-5L Inverter," *Proceedings of the CSEE. Power Electron.* vol. 39, no. 4, pp. 1150-1162, Sep. 2019.

- [13] Siwakoti YP, Palanisamy A, Mahajan A, Liese S, Long T, and Blaabjerg F, "Analysis and Design of a Novel Six-Switch Five-Level Active Boost Neutral Point Clamped Inverter," *IEEE Trans. Ind. Electron.*, vol. 67, no. 12, pp. 10485–10496, Nov. 2020.

- [14] M. Saeedian, S. M. Hosseini, and J. Adabi, "A Five-Level Step-Up Module for Multilevel Inverters: Topology, Modulation Strategy, and Implementation," *IEEE Trans. Power Electron*, vol. 6, no. 4, pp. 2215–2226. Aug. 2018.

- [15] Barzegarkhoo R, Siwakoti YP, and Blaabjerg F, "A New Switched-Capacitor Five-Level Inverter Suitable for Transformerless Grid-Connected Applications," *IEEE Trans. Power Electron.*, vol. 35, no. 8, pp. 8140–8153, Feb. 2020.

- [16] N. Sandeep, Jagabar Sathik Mohamed Ali, Udaykumar R. Yaragatti, and Krishnasamy Vijayakumar, "A Self-Balancing Five-Level Boosting Inverter With Reduced Components," *IEEE Trans. Ind. Electron.*, vol. 34, no. 7, pp. 6020–6024, Nov. 2019.

- [17] R. Samanbakhsh and A. Taheri, "Reduction of power electronic components in multilevel converters using new switched capacitordiode structure," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7204–7214, Nov. 2016.

- [18] R. Barzegarkhoo, E. Zamiri, N. Vosoughi, H. M. Kojabadi, and L. Chang, "Cascaded multilevel inverter using series connection of novel capacitor-based units with minimum switch count," *IET Power Electron.*, vol. 9, no. 10, pp. 2060–2075, Aug. 2016.

- [19] Shen Hong, Guo Zhongnan, Guan Honglei, Wang Baocheng, and Guo Xiaoqiang, "Research on Single-Phase Four-Switch Multilevel PV Inverter," *Transactions of China Electrotechnical Society, Power Electron.* vol. 33, no. 8, pp. 1775-1782, Apr. 2018.

- [20] M. D. Siddique, J. S. M. Ali, S. Mekhilefl, et al, 'Reduce Switch Count Based Single Source 7LBoost Inverter Topology," *IEEE Transactions on Circuits and Systems II: Express Briefs* to be published, doi: 10.1109/TCSII.2020.2988090.

- [21] B. P. Reddy, M. D. Siddique, Iqbal, et al, "7L-SCBI topology with minimal semiconductor device count," *IET Power Electron.*, to be published, doi: 10.1049/iet-pel.2020.0313.

- [22] R. S. Alishah, M. A. Bakar and K. Berttilsson, "A New Seven-Level Grid-Connected Converter Using Model Predictive Controller," PCIM Europe digital days 2020; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Germany, 2020, pp. 1-5.

- [23] J. A. Starzyk, Y. Jan, and F. Qiu, "A dc-dc charge pump design based onvoltage doublers," *IEEE Trans. Circuits Syst. I, Reg. Papers.*, vol. 48, no. 3, pp. 350–359, Mar. 2001.

- [24] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 858–867, Aug. 2002.

- [25] Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/parallel conversion with inductive load," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 878-887, Feb. 2012.

- [26] L. G. Franquelo, Rodriguez, Leon, S. Kouro, R. Portillo, and M. A.M. Prats, " The age of multilevel converters arrives," *IEEE Trans. Ind. Electron.*, vol. 2, no. 2, pp. 28-39, Jun. 2018.

- [27] A. Tsunoda, Y. Hinago, and H. Koizumi, "Level- and phase-shifted PWM for seven-level switched-capacitor inverter using series/parallel conversion," *IEEE Trans. Ind. Electron*, vol. 61, no. 8, pp. 4011-4021, Aug. 2014.

- [28] M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, M. Tayyab, and M. K. Ansari, "Low switching frequency based asymmetrical multilevel inverter topology with reduced switch count," *IEEE Access*, vol. 7, pp. 86374–86383, 2019.

- [29] E. Samadaei, S. A. Gholamian, A. Sheikholeslami, and J. Adabi, "An envelope type (E-type) module: Asymmetric multilevel inverters with reduced components," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7148–7156, Nov. 2016.

- [30] M. D. Siddique, S. Mekhilef, N. M. Shah, and M. A. Memon, "Optimal design of a new cascaded multilevel inverter topology with reduced switch count," *IEEE Access*, vol. 7, pp. 24498–24510, 2019.

- [31] E. Samadaei, A. Sheikholeslami, S. A. Gholamian, and J. Adabi, "A square T-type (ST-Type) module for asymmetrical multilevel inverters," *IEEE Trans. Power Electron.*, vol. 33, no. 2, pp. 987– 996, Feb. 2018.

- [32] Zeeshan Sarwer, M. D. Siddique, Atif Iqbal, Adil Sarwar, and S. Mekhilef, "An Improved Asymmetrical Multilevel Inverter Topology with Reduced Semiconductor," *Int. Trans. Electr. Energy Syst.*, to be published, doi: 10.1002/2050-7038.12587.

- [33] R. S. Alishah, E. Babaei, S. H. Hosseini, and M. Sabah, "A Developed Two-Leg Ladder Multilevel Converter Structure," *I Trans. Electr. Electron. Circ. Syst.*, vol. 27, no. 12, pp. 1–17, Feb. 2018.

- [34] R. S. Alishah, S. H. Hosseini, E. Babaei, M. Sabah, and J. F. Ardashir 'An Improved Symmetric H-Bridge Multilevel Converter Topology; An Attempt to Reduce Power Losses," *I Trans. Electr. Electron. Circ. Syst.*, vol. 27, no. 12, pp. 1–20, Feb. 2018.

- [35] M. D. Siddique, S. Mekhilef, N. M. Shah, et al. "Switchedcapacitor-based boost multilevel inverter topology with higher voltage gain," *IET Power Electron.*, to be published, doi: 10.1049/iet-pel.2020.0446.

- [36] M. D. Siddique, B. P. Reddy, A. Iqbal, et al, "Reduced switch countbased N-level boost inverter topology for higher voltage gain," *IET Power Electron.*, to be published, doi: 10.1049/iet-pel.2020.0359.

- [37] A. Ruderman, "About voltage total harmonic distortion for singleand three-phase multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1548–1551, Mar. 2015.