# NINO: An Ultrafast Low-Power Front-End Amplifier Discriminator for the Time-of-Flight Detector in the ALICE Experiment

F. Anghinolfi, P. Jarron, F. Krummenacher, E. Usenko, and M. C. S. Williams

Abstract—An ultrafast front-end preamplifier-discriminator chip called NINO has been developed for use in the ALICE time-of-flight detector. The chip has eight channels. Each channel is designed with an amplifier with less than 1-ns peaking time, a discriminator with a minimum detection threshold of 10 fC and an output stage. The output pulse has minimum time jitter (less than 25 ps) on the front edge, and the pulsewidth is dependent of the input signal charge. Each channel consumes 27 mW, and the eight channels fit in a  $2 \times 4 \text{ mm}^2$  ASIC processed in IBM 0.25- $\mu$ m CMOS technology.

*Index Terms*—CMOS analog integrated circuits, particle measurements, pulsewidth modulation, timing jitter.

#### I. INTRODUCTION

T HE time-of-flight detector is the major system for performing particle identification (PID) in the ALICE experiment. It has large azimuthal angle ( $\pm 45^{\circ}$ ) and full radial coverage. The detector is a cylinder of 3.7-m radius located around the TPC chamber. It is made of 10-gap double-stack multigap resistive plate chambers (MRPC) [1], [2]. Each stack has five gaps of 250  $\mu$ m. The total number of detector channels is 160 000. The RPC is chosen because of the very fast charge collection time (~100 ps). Particle identification is made by measuring the time-of-flight of the high-energy incident particles with a resolution better than 100 ps. This allows particle separation between e,  $\pi$ , K, and p in the momentum range 1–4 GeV/c.

#### **II. REQUIREMENTS AND CIRCUIT DESCRIPTION**

The very precise measurement of time, below 100-ps range at the system level, requires a very fast, minimum slew rate, front-end amplifier discriminator. To minimize signal reflection and crosstalk, the input impedance has to be low and matched to the impedance of the transmission line connecting detector to front-end.

The front-end channel specifications are given in Table I. The input stage is a very critical low-noise large-bandwidth circuit. We have chosen a robust current-to-voltage converter based

Manuscript received November 14, 2003; revised April 15, 2004.

F. Anghinolfi and P. Jarron are with CERN Meyrin, 1211 Geneva 23, Switzerland (e-mail: francis.anghinolfi@cern.ch; pierre.jarron@cern.ch).

F. Krummenacher is with Smart Silicon Systems S.A., CH-1007 Lausanne, Switzerland (e-mail: francois.krummenacher@epfl.ch).

E. Usenko is with the Institute for High Energy Physics, 142281 Protvino, Russia (e-mail: eugueni.oussenko@cern.ch).

M. C. S. Williams is with Istituto Nazionale di Fisica, I-40127 Bologna, Italy (e-mail: crispin.willams@cern.ch).

Digital Object Identifier 10.1109/TNS.2004.836048

TABLE I NINO CHIP SPECIFICATIONS

| Parameter                    | Value                       |

|------------------------------|-----------------------------|

| Peaking time                 | lns                         |

| Signal range                 | 100fC-2pC                   |

| Noise (with detector)        | < 5000 e- rms               |

| Front edge time jitter       | < 25ps rms                  |

| Power consumption            | 30 mW/ch                    |

| Discriminator threshold      | 10fC to 100fC               |

| Differential Input impedance | $40\Omega < Zin < 75\Omega$ |

| Output interface             | LVDS                        |

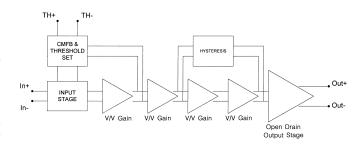

Fig. 1. Functional block diagram for one channel of the NINO chip.

on a balanced common gate circuit configuration. The subsequent signal amplification is performed with four identical cascaded amplifiers, which are optimized for delay and slew rate. They provide sufficient gain to operate as a discriminator. The threshold is set by a voltage difference applied on two symmetrical inputs, acting on a dc stabilization feedback circuit, which is used also as the common mode rejection circuit. A positive loop feedback circuit can be enabled to add a small hysteresis on the discriminator threshold.

The full channel configuration is depicted in Fig. 1. From inputs to outputs, a fully differential circuit is chosen to obtain a large immunity against power supply noise and ground noise.

The output stage is an open-drain differential circuit providing current switching between the two outputs of a channel. Output levels can be made compatible with commercial LVDS receivers.

#### A. Input Stage

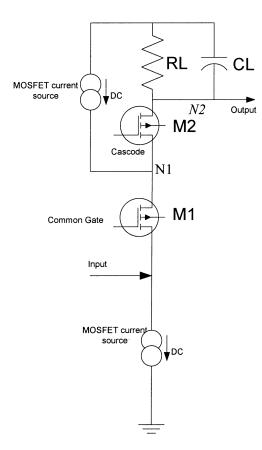

The detector signal is applied across the two inputs of a common gate differential circuit (Fig. 2).

Fig. 2. Simplified schema of the input stage (one side of the differential structure).

TABLE II INPUT STAGE TIME CONSTANTS

| Node   | Elements           | Time constant |

|--------|--------------------|---------------|

| OUTPUT | $R_{L}, C_{L}$     | 760ps         |

| N1     | Local cap, cascode | 155ps         |

| INPUT  | Input Cap, 1/gmsb  | 550ps         |

The input impedance on each branch of the differential circuit is thus 1/gmsb of the input transistor M1 (Fig. 2). The input charge, generated by the detector, is flowing through transistor M1 and the branch made of transistor M2 and load elements  $R_L$ and  $C_L$ . The output signal is the voltage on the output node N2. The structure is suited to high speed, because of the absence of feedback element acting on the signal. The frequency bandwidth is then determined by the time constant  $R_L \cdot C_L$  at node N2 and by the poles at input node and node N1. Typical values of time constants of the input stage are given in Table II.

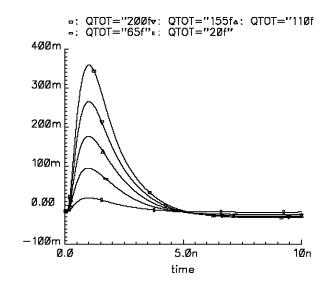

The typical signal on output of the first stage is shown in Fig. 3. The detector signal is modeled as a 200-ps-width current pulse. The circuit modeling for SPICE simulation includes the electrical model of the transmission line between detector and front-end.

#### B. Biasing Circuit

A common biasing block (not shown in Fig. 1) is used to provide biasing currents and voltages to the channels in the NINO chip.

Fig. 3. Differential voltage signal at the first stage outputs, for input charge values from 20 to 200 fC. Peaking time is 1 ns, gain 1.8 mV/fC.

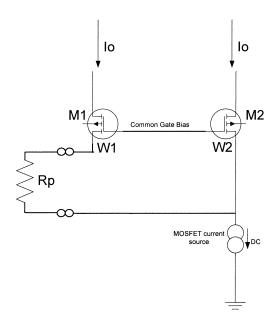

Fig. 4. Simplified schema of the biasing circuit for the input stage.

A dedicated circuit has been developed to match the channel input impedance, to an external resistance used as a reference. The matching circuit is presented in Fig. 4.

The two branches, which are biased with identical currents  $I_o$ , have differences in topology: the ratio W1/W2 of transistors M1 and M2, and the resistance Rp which is inserted at the source of M1. The asymmetry results in the following expression for current  $I_o$ :

$$I_{o} = \frac{1}{Kn \cdot (W2/L)} \cdot \frac{1}{Rp^{2}} \cdot \left(1 - \frac{1}{M}\right) \quad M = \sqrt{\frac{W1}{W2}}$$

If W1/W2 = 4, the source impedance of the transistor M2 is expressed as

$$1/gmsb_{M2} = \frac{1}{2\sqrt{Kn \cdot \frac{W2}{L} \cdot I_0}} = Rp.$$

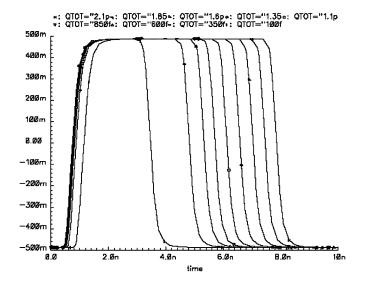

Fig. 5. SPICE simulation of the differential output signal. The input charge is swept from 100 fC to 2.1 pC. Threshold is set at 50 fC.

The above equations are established for circuit operating in strong inversion whereas transistors M1 and M2 are operating in moderate inversion. SPICE simulation was used to refine the ratio W1/W2.

The two input devices of the differential input stage are biased as the transistor M2 (same gate voltage and drain current). Thus impedance of the input devices is matched to the value of the reference resistance Rp.

# C. Cascaded Voltage Gain Stage

Voltage gain amplification after the input stage is provided with four cascaded identical high bandwidth differential pair amplifiers. Each amplifier has a voltage gain of 6, with -3 dB bandwidth above 500 MHz.

#### **III. RESULTS**

#### A. Simulation Outputs

The time response and the pulsewidth as function of the input charge, obtained from the SPICE simulation, are shown in Fig. 5.

The pulsewidth measurement will be used in the experiment, to estimate the input charge and correct for time walk. The pulsewidth is increasing as the result of the increasing saturation of the cascaded amplifiers.

### B. Noise Performance

Noise performance has been estimated using the noise analysis tool available with the SPICE simulator. With the detector capacitance of 10 pF at the inputs, the channel differential gain is measured as 1070 mV/fC. The integrated noise at the differential outputs is 570 mV rms. The calculated noise referred to the inputs is then calculated as 3320 electrons rms (0.53 fC). With a mean signal from the detector above 50 fC, the signal-to-noise

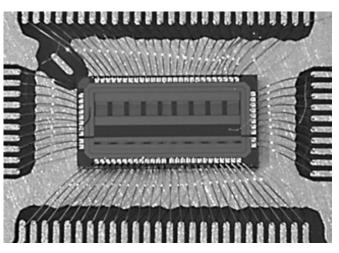

Fig. 6. The NINO chip mounted on test beam experiment PCB. Chip size is  $2 \times 4 \text{ mm}^2$ .

ratio (SNR) is sufficiently large to make the channel noise not critical. The circuit can operate with a threshold as low as 10 fC.

The above estimates from the simulator can be compared to calculations obtained from the simplified formulations for series and parallel noises in case of detector amplifiers [3]. The dominant contribution to the series noise comes from the input device (M1 in Fig. 2). This contribution is calculated as

$$\mathrm{ENC}_{s}^{2} = 4kT \cdot \frac{2}{3} \cdot \Gamma g m_{\mathrm{sb}}^{-1} \cdot \tau^{-1} \cdot C_{\mathrm{de}}^{2}$$

where  $gm_{\rm sb}$  is the input device transconductance,  $\Gamma$  the noise factor, and  $\tau$  the channel shaping time. With the following values for parameters:

$$gm_{\rm sb} = 37 \,\mathrm{mS}, \quad \Gamma = 1.5, \quad C_{\rm det} = 10 \,\mathrm{pF}, \quad \tau = 1 \,\mathrm{ns}$$

the value obtained for series noise is 1300 electrons (for one branch of the differential amplifier).

The parallel noise contribution comes mainly from the current source connected at the input node

$$\mathrm{ENC}_p^2 = 4kT \cdot \frac{2}{3} \cdot \Gamma g m_p \cdot \tau$$

where  $gm_p$  is the transconductance of the MOS current source at the input node. With the following values for parameters:

$$gm_p = 4.4 \text{ mS}, \quad \Gamma = 1.5, \quad \tau = 1 \text{ ns}$$

the value obtained for parallel noise is 1660 electrons (one branch of the differential amplifier).

Summing the series and parallel contribution, and summing for both branches of the differential circuit, the total noise referred at the inputs is then 3000 electrons rms. The simulation shows a 10% higher value. The difference can be attributed to the noise contributions of other circuit components and/or to the error in the estimation of the  $\Gamma$  or  $\tau$  parameters.

## C. Experimental Results

The  $2 \times 4 \text{ mm}^2$  NINO chip has been fabricated using a commercial 0.25- $\mu$ m process (Fig. 6).

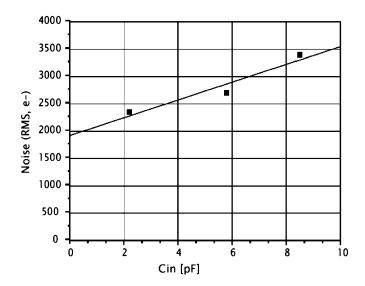

Fig. 7. The NINO chip input noise measurement.

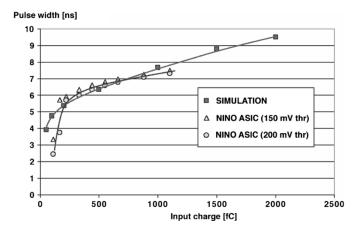

Fig. 8. Measurement of the pulsewidth for two threshold settings, and comparison with the simulation data.

The chip contains eight channels and the biasing circuit. The external biasing components are one resistor (Rp) which defines the input impedance and one resistor to define the output current. Four channels are built as described in Section II; four other channels have an additional circuit which introduces a small hysteresis in the comparator stage.

The ENC noise has been measured with input capacitors from 2 to 8 pF (Fig. 7).

The measured noise figure indicates parallel and series noise values of 1900 electrons rms and 165 electrons rms/pF. For the nominal capacitance of the TOF detector (10 pF), the noise level is 3550 electrons rms (0.57 fC). The minimum threshold at which the circuit was able to operate, with no particular protection against ringing, is 10 fC. For the experiment, the minimum threshold will be set at 50 fC, a factor 87 above the noise floor. The detector mean signal range is 0.5–0.8 pC.

The pulsewidths obtained from measurements for two thresholds have been compared with the width obtained from simulation data (Fig. 8). The measured and simulated widths are well matched up to 1 pC. Above this value, the measured signal width is smaller than the width predicted by SPICE simulation.

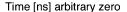

Fig. 9. Measurement of front edge time walk (arbitrary position "0" on vertical scale) versus pulsewidth for an input charge of 50 to 100 fC, threshold set at 30 fC.

Fig. 10. Measurement of time jitter on the front edge. The input charge is swept from 50 fC to 1.15 pC with a threshold set at 30 fC.

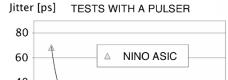

Fig. 11. Measurement of time jitter and detector efficiency, with test beam, MRPC detector and precision TDC unit.

The pulsewidth is increasing through the successive saturation of the amplifier stages. The difference in pulsewidth with large signal may be due to a simulation imperfection.

The correlation of pulsewidth with the front edge time walk is linear, as shown on Fig. 9. The pulsewidth measurement can thus be used to correct for the time drift of the front edge due to the discriminator time walk.

The jitter of the front edge of the signal, which determines the time measurement accuracy has been measured on test bench and found to be 20 ps rms (Fig. 10).

The time jitter of a complete setup with detector and readout electronics has been measured with a test beam (Fig. 11).

The detector efficiency was measured above 99.9% for the MRPC detector biased with high voltage above 12 kV. The system jitter was 41 ps rms. The individual contributions to the system jitter were separately evaluated: 14.4 ps for the beam spot, 25 ps for the MRPC detector, 21.2 ps for the time measurement circuit (HPTDC). and 20 ps for the NINO channel, a value identical to the one obtained with the test bench measurements (Fig. 10).

# IV. CONCLUSION

The NINO amplifier and discriminator chip has been developed for the precision time measurement required for the time-of-flight detector in the ALICE experiment. The present chip has eight channels with a peaking time of 1 ns with a resolution of 20 ps rms. The pulsewidth measurement is used to do charge measurement as well as time walk correction. The threshold can be set at 10 fC input charge. The power consumption per channel is 27 mW, including the LVDS compatible output driver. Only one power supply and two external resistors are needed to make the circuit operational.

#### REFERENCES

- E. Cerron-Zeballos, I. Crotty, D. Hatzifotiadou, J. Lamas-Valverde, S. Neupane, M. C. S. Williams, and A. Zichichi, "A new type of resistive plate chamber: The multigap RPC," *Nucl. Instrum. Methods Phys. Res.*, vol. A 374, pp. 132–136, 1996.

- [2] A. V. Akindinov, F. Anselmo, M. Basile, E. Cerron-Zeballos, L. Cifarelli, F. Cindolo, F. J. Choi, B. Cozzoni, A. De Caro, S. De Pasquale, D. W. Kim, N. Y. Kim, W. Klempt, A. Kluge, G. Laurenti, S. C. Lee, V. Golovine, D. Hatzifotiadou, A. N. Martemyanov, P. Martinengo, A. Pesci, E. D. Platner, J. Roberts, A. Seganti, A. A. Semak, A. I. Smirnitskii, M. Spegel, P. Szymanski, G. Valenti, D. Vicinanza, M. C. S. Williams, and A. Zichichi, "The multigap resistive plate chamber as a time-of-flight detector," *Nucl. Instrum. Methods Phys. Res.*, vol. A456, pp. 16–22, 2000.

- [3] V. Radeka, "Low-noise techniques in detectors," Ann. Rev. Part. Sci., vol. 38, pp. 217–277, 1988.