# Noise in Silicon Nanowires

Shahed Reza, Gijs Bosman, *Senior Member, IEEE*, M. Saif Islam, *Member, IEEE*, Theodore I. Kamins, *Fellow, IEEE*, Shashank Sharma, and R. Stanley Williams

Abstract—The current-voltage and noise characteristics of bridging silicon wires have been measured at room temperature. From the linear current-voltage characteristics the bulk and contact resistance contributions are extracted and modeled. The excess noise observed at low frequencies is interpreted in terms of bulk and contact noise contributions, with the former comparable, in terms of Hooge parameter values, to the low noise levels observed in high-quality silicon devices. The contact noise is significant in some devices and is attributed to the impinging end of the bridging nanowires.

Index Terms—Carbon nanotube, contact noise, nanowire, noise.

#### I. INTRODUCTION

THE fabrication and characterization of nanostructures are currently receiving significant interest from the research community. The tremendous advances in process control achieved in the last decade have enabled researchers to fabricate novel structures with feature sizes in the nanometer range and to explore their properties. At the same time, the current state-of-the-art silicon CMOS technology has already been scaled down to nanometer feature sizes and is approaching the physical lower limit of beneficial scaling. These trends motivate a search for device structures that may take the place of the current technology. One major limitation of conventional nanofabrication technology is lithography. The error in multiple mask alignments and the cost and complexity of advanced lithography tools limit the smallest feature sizes that can be economically achieved. For this reason a focus of current research is the development of devices that can "self-assemble" without the need for fine-scale lithography. Carbon nanotubes [1] and recently reported bridging silicon nanowires [2] belong in this category.

We present here the results of a noise study on lateral, bridging silicon nanowires. The results of the device resistance

Manuscript received March 27, 2006; revised May 5, 2006. This work was supported in part by the Defense Advanced Research Projects Agency (DARPA). The review of this paper was arranged by Associate Editor D. Frank.

- S. Reza is with the University of Florida, Gainesville, FL 32601 USA (e-mail: sreza@ieee.org).

- G. Bosman is with the Electrical and Computer Engineering Department, University of Florida, Gainesville, FL 32603 USA (e-mail: gbosm@ece.ufl. edu).

- M. S. Islam was with Quantum Science Research, Hewlett-Packard Laboratories, Palo Alto, CA 94304 USA He is now with the Electrical and Computer Engineering Department, University of California, Davis, CA 95616 USA (e-mail: saif@ece.ucdavis.edu).

- T. I. Kamins and R. S. Williams are with Quantum Science Research, Hewlett-Packard Laboratories, Palo Alto, CA 94304 USA (e-mail: kamins@hp.com; stan.williams@hp.com).

- S. Sharma was with Quantum Science Research, Hewlett-Packard Laboratories, Palo Alto, CA 94304 USA He is now with Spansion Inc., 915 Deguigne Drive, M/S 36 Sunnyvale, CA 94088 (e-mail: shanku98@yahoo.com).

Digital Object Identifier 10.1109/TNANO.2006.880908

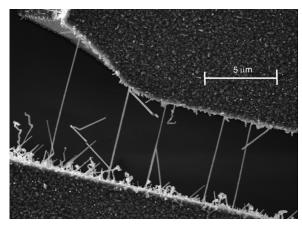

Fig. 1. Top-view SEM image of a device, showing nanowires connecting the electrodes.

analysis, a proposed model, and a noise comparison with carbon nanotubes will also be presented. The 1/f noise of carbon nanotubes is reported to be unusually high [3] and the origin of the noise is still unknown. Until a way to minimize this noise is found, the applicability of carbon nanotubes in electronic systems is substantially limited. Our study shows that the Si nanowires are orders of magnitude less noisy than carbon nanotubes, and that the main source of the noise is in the nanowire-bulk contact, which allows the possibility of optimizing the contact structure and reducing the noise even further.

#### II. EXPERIMENTAL METHODS

#### A. Description and Sample Preparation

Silicon nanobridges were grown between electrically isolated electrodes formed from the top silicon layer of (110)-oriented silicon-on-insulator substrates. Approximately 1 nm Au was deposited on the (111)-oriented sides of the electrodes and annealed in a  $\rm H_2$  ambient at 670 °C to form nanoscale Au-Si alloy catalyst islands. The structure was then exposed to a mixture of 15 sccm SiH<sub>4</sub>, 60 sccm HCl, and 30 sccm B<sub>2</sub>H<sub>6</sub> (100 ppm in H<sub>2</sub>) in a H<sub>2</sub> ambient at 680 °C and a total pressure of 1.3 kPa for 30 min to grow nanowires bridging between electrodes with a separation of 10  $\mu$ m or less. Before nanowire growth reactive ion etching was used to remove Au catalyst from all areas of the substrate other than the sidewalls. This helped suppress the uncatalyzed growth of Si between electrodes, ensuring good electrical isolation. Details of the fabrication process for the bridging nanowires are reported in [4].

The sample was mounted on a TO-8 package using conductive epoxy and wire bonded. After the measurements were complete, the sample was imaged using a Hitachi S-4000 scanning electron microscope (SEM). An SEM image is shown in Fig. 1.

|         | Device |                      | Wire 1               | Wi                   | re 2                 | Wi                   | re 3                 | Wi                   | re 4                 | Wi                   | re 5                 |

|---------|--------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|         |        | Length (cm)          | Radius (cm)          |

| Wafer 1 | a      | $7.5 \times 10^{-4}$ | $6.8 \times 10^{-6}$ | $6.6 \times 10^{-4}$ | $6.2 \times 10^{-4}$ |                      |                      |                      |                      |                      |                      |

|         | b      | $4. \times 10^{-4}$  | 5.8×10 <sup>-6</sup> | $4.7 \times 10^{-4}$ | $4.8 \times 10^{-4}$ |                      |                      |                      |                      |                      |                      |

|         | c      | 8.3×10 <sup>-4</sup> | $8.0 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |                      |                      |

|         | d      | $7.0 \times 10^{-4}$ | $6.8 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |                      |                      |

| Wafer 2 | a      | 3.0×10 <sup>-4</sup> | $6.7 \times 10^{-6}$ | 3.3×10 <sup>-4</sup> | 7.5×10 <sup>-6</sup> |                      |                      |                      |                      |                      |                      |

|         | b      | $3.4 \times 10^{-4}$ | $3.8 \times 10^{-6}$ | $3.6 \times 10^{-4}$ | $1.1 \times 10^{-5}$ | $3.0 \times 10^{-4}$ | $5.4 \times 10^{-6}$ |                      |                      |                      |                      |

|         | c      | $6.0 \times 10^{-4}$ | $7.5 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |                      |                      |

|         | d      | 6.3×10 <sup>-4</sup> | $4.2 \times 10^{-6}$ | $6.5 \times 10^{-4}$ | $5.0 \times 10^{-6}$ | $6.4 \times 10^{-4}$ | $8.3 \times 10^{-6}$ | $6.0 \times 10^{-4}$ | $6.7 \times 10^{-6}$ | $9.0 \times 10^{-4}$ | $4.7 \times 10^{-6}$ |

|         | e      | $8.4 \times 10^{-4}$ | $4.6 \times 10^{-6}$ | $1.1 \times 10^{-3}$ | $6.0 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |

|         | f      | $1.0 \times 10^{-3}$ | $5.0 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |                      |                      |

|         | g      | $1.0 \times 10^{-3}$ | 6.3×10 <sup>-6</sup> | $8.5 \times 10^{-4}$ | $4.2 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |

|         | h      | $1.0 \times 10^{-3}$ | $4.8 \times 10^{-6}$ | $1.0 \times 10^{-3}$ | $4.3 \times 10^{-6}$ |                      |                      |                      |                      |                      |                      |

|         | i      | $1.5 \times 10^{-3}$ | $4.7 \times 10^{-6}$ | $1.1 \times 10^{-3}$ | 5.6×10 <sup>-6</sup> |                      |                      |                      |                      |                      |                      |

TABLE I

MEASURED NANOWIRE DIMENSIONS FROM SEM

The number and dimensions of the nanowires between electrodes in the devices under study were measured using the SEM and are summarized in Table I.

### B. Resistance Measurements

The I-V characteristics of the devices were measured using an HP4145B semiconductor parameter analyzer. The devices were found to be very linear over the voltage range of  $\pm$  5 V. The device resistance  $R_m$  calculated from the slope of the I-V plot (see Table II) is the parallel combination of the resistances of the bridging wires  $(R_i)$  in the device, i.e.,

$$R_m = \frac{1}{\sum_{i=1,N} \frac{1}{R_i}}$$

(1)

where N is the number of wires in the device. The total resistance of an individual wire is the sum of bulk resistance  $R_{\rm bi}$  and contact resistance,  $R_{\rm ci}$  i.e.,

$$R_i = R_{\rm bi} + R_{\rm ci}. (2)$$

The bulk resistance of a wire is related to the bulk resistivity  $\rho_b$  by

$$R_{\rm bi} = \rho_b \cdot \frac{l_i}{\pi r_i^2} \tag{3}$$

where  $r_i$  and  $l_i$  are the radius and length of wire i, respectively. The effective resistivity  $\rho$  of a device is calculated from the measured resistances and the dimensions of the wires measured from SEM images using

$$\rho = R_m \cdot \sum_{i=1,N} \frac{\pi r_i^2}{l_i}.$$

(4)

TABLE II

DEVICE RESISTANCE AND RELATIVE NOISE MAGNITUDE

|          | Device | Number of wires | $R_m(\Omega)$        | A                      |  |

|----------|--------|-----------------|----------------------|------------------------|--|

|          | a      | 2               | $1.76 \times 10^5$   | 6.71×10 <sup>-9</sup>  |  |

| r 1      | b      | 2               | $3.11 \times 10^{5}$ | 1.20×10 <sup>-9</sup>  |  |

| Wafer 1  | c      | 1               | $1.38 \times 10^{5}$ | $2.92 \times 10^{-11}$ |  |

| _        | d      | 1               | $2.47 \times 10^5$   | 8.45×10 <sup>-9</sup>  |  |

|          | a      | 2               | 5.55×10 <sup>4</sup> | 1.22×10 <sup>-9</sup>  |  |

|          | ь      | 3               | $4.85 \times 10^4$   | 3.37×10 <sup>-10</sup> |  |

|          | c      | 1               | $1.89 \times 10^{5}$ | $1.61 \times 10^{-10}$ |  |

| 7        | d      | 5               | $7.47 \times 10^4$   | $4.04 \times 10^{-11}$ |  |

| Wafer 2  | e      | 2               | $5.08 \times 10^{5}$ | $1.69 \times 10^{-10}$ |  |

| $\aleph$ | f      | 1               | $6.30 \times 10^5$   | $2.76 \times 10^{-10}$ |  |

|          | g      | 2               | $1.76 \times 10^{5}$ | $3.51 \times 10^{-11}$ |  |

|          | h      | 2               | $2.64 \times 10^{5}$ | $4.21 \times 10^{-11}$ |  |

|          | i      | 2               | $3.93 \times 10^{5}$ | 4.73×10 <sup>-10</sup> |  |

From (2)–(4)

$$\rho = \rho_b \cdot R_m \cdot \sum_{i=1,N} \frac{1}{R_i - R_{ci}}.$$

(5)

So the effective resistivity calculated using (4) is equal to the bulk resistivity  $\rho_b$  only in the absence of contact resistance  $(R_{\rm ci} \approx 0)$  and greater otherwise.

## C. Noise Measurements

The voltage noise spectral density was measured with an HP3561A low-frequency spectrum analyzer for frequencies between 10 Hz and 100 kHz. The device was current biased

REZA et al.: NOISE IN SILICON NANOWIRES 525

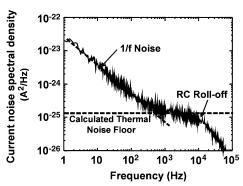

Fig. 2. A typical plot of current noise spectral density.

during the noise measurement. The measured voltage noise density  $S_v$  was converted into current noise density,  $S_i$  using [5]

$$S_i = \frac{S_v}{R_m^2}. (6)$$

The noise observed is a combination of frequency-dependent excess noise and a frequency-independent noise floor (Fig. 2). The noise floor was found to be equal to the thermal noise given by

$$S_{i\_\text{thermal}} = \frac{4k_B T}{R_m} \tag{7}$$

where  $k_B$  is the Boltzmann constant and T is the absolute temperature. No new information can be extracted from the thermal noise, so the focus of this work is on the excess noise. The excess noise was calculated by subtracting the thermal noise from the total measured noise. The excess noise was interpreted assuming a  $1/f^\beta$  frequency dependence and modeled as [5]

$$S_{1/f}(f) = \frac{A \cdot I_{\rm dc}^2}{f^{\beta}} \tag{8}$$

where  $I_{\text{dc}}$  is the dc current, f is the frequency, and A and  $\beta$  are constants. The values of A and  $\beta$  were estimated by fitting a line to the experimental data as shown in Fig. 2. The parameter  $\beta$  was found to be almost equal to unity, as expected for 1/f-type noise. The parameter A represents the relative magnitude of the 1/f noise (see Table II).

# III. RESISTANCE AND NOISE MODELING

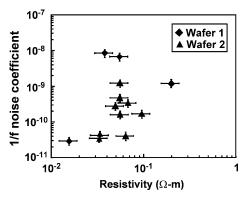

Both the resistance and the 1/f noise coefficient show significant variations from device to device. However the plot of A versus  $\rho$  (Fig. 3) shows that the devices from both wafers that have the lowest effective resistivity also generally show the lowest noise. Based on our earlier discussion, these devices can be identified as the devices with low contact resistance. The fact that the low-noise devices also have low contact resistance suggests that the source of the noise is the contact. To check this possibility further a model for the resistance was developed and will be presented next.

# A. Resistance Model

Bulk resistivity was calculated from the devices with the lowest resistivity and noise. As these devices have the lowest contact resistance, the resistivity calculated using (4) and initially neglecting contact resistance gives the best estimate of

Fig. 3. 1/f noise coefficient A versus effective resistivity  $\rho$ . The uncertainties in A and  $\rho$  due to the measurement uncertainties are shown.

the bulk resistivity. The carrier density p is related to the bulk resistivity by the following expression:

$$\rho = \frac{1}{q\mu_p p} \tag{9}$$

where  $\mu_p$  is the hole mobility and -q is the electron charge.

The corresponding carrier densities calculated using the resistivity versus impurity-concentration relationship for bulk Si at 300 K [6], are  $5 \times 10^{18}$  cm<sup>-3</sup> and  $1.3 \times 10^{18}$  cm<sup>-3</sup> for wafers 1 and 2, respectively. Cui et al. [7] reported that the carrier mobility in highly doped silicon nanowires is comparable to that observed in bulk silicon. Consequently the above listed values are assumed to be good estimates of the nanowire carrier densities. The bulk resistances of all other devices were calculated using these carrier concentrations. Note that dopant fluctuation is ignored in our analysis. This is a reasonable assumption given the large number of dopant atoms per wire. Also the physical diameters of the nanowire are used in the calculation. Due to the presence of surface charge, the surface region of the nanowire is expected to be depleted and as a result the effective diameter becomes less than the physical diameter. The depletion width depends on the surface charge density and the number of traps filled. Our initial estimate of surface charge density is  $2 \times 10^{12}$  cm<sup>-2</sup>. Our calculation shows that for the worst case scenario, the model presented here remains valid. Since the surface charge density is not well characterized at this time, the analysis using the physical diameters of the nanowires is presented.

From the devices containing only one nanowire, the contact resistance was obtained from

$$R_c = R_m - R_b. (10)$$

It was observed that the contact resistance is inversely proportional to the cross-sectional area with a proportionality constant  $K_c$  of  $1.69 \times 10^{-5} \Omega - \text{cm}^2$ , i.e.,

$$R_{\rm ci} = \frac{K_c}{\pi r_i^2}.\tag{11}$$

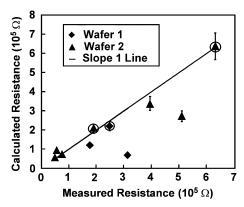

This model was applied to all other devices to calculate the contact resistance. The minimum and maximum contact resistances obtained from (11) for individual nanowires were 48.9 k $\Omega$  and 383 k $\Omega$ , respectively. The total resistance was calculated by combining the calculated contact and the bulk resistances. A plot of the measured resistance and the resistance

Fig. 4. Calculated versus measured resistance, including contact resistance. The uncertainties in the calculated resistance due to the measurement uncertainties are shown. The uncertainties for the measured resistance are too small to be displayed in the plot. The devices having only one nanowire are marked with a circle.

Fig. 5. Circuit representation of the noise model.

calculated using the above model is shown in Fig. 4. The plot shows good agreement between the measured and the calculated resistance for all devices except for two devices.

Our model suggests a common mechanism for the contact resistance in all devices, most likely resulting from the interface between the impinging end of the nanowire and the sidewall. The base end of the nanowire is connected epitaxially to the silicon sidewall, and thus the contact resistance on this side should be negligible. On the impinging side however, the nanowire makes contact to the silicon electrode through the pinholes of the native oxide [8], so the contact resistance on this side is expected to be dominant. It is possible for the actual contact area to be different from the wire cross section, because the nanowire has to burrow through a native oxide layer. However, the good fit of the model indicates that for all but two of the nanowires, the impinging contacts are very uniform. A closer SEM examination of these two devices showed a nanowire with a contact area much smaller than the cross section of the nanowire, which may explain why these two are different from the other devices. These two devices were not used for noise modeling.

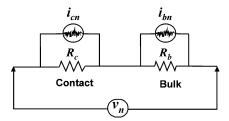

# B. Noise Model

A simple noise model in terms of the bulk and contact resistances discussed above is proposed. The circuit diagram of the model is shown in Fig. 5. From this circuit, the measured open-circuited noise voltage across the terminals is given by

$$v_n = i_{\rm bn} \cdot R_b + i_{\rm cn} \cdot R_c \tag{12}$$

where  $i_{\rm bn}$  and  $R_b$  are the noise current source and the resistance respectively for the bulk region, and  $i_{\rm cn}$  and  $R_c$  are the noise

current source and the resistance, respectively, for the contact region of a wire.

From (12) the total 1/f voltage noise spectral density  $S_v$  in terms of the individual current noise spectral densities is given by

$$S_v = S_{\rm ib} \cdot R_b^2 + S_{\rm ic} \cdot R_c^2 \tag{13}$$

where  $S_{\rm ib}$  and  $S_{\rm ic}$  are the current noise densities of the bulk and contact noise sources, respectively.

From (13), with the total resistance  $R = R_b + R_c$ , the total current noise spectral density can be written as

$$S_i = S_{ib} \cdot \left(\frac{R_b}{R}\right)^2 + S_{ic} \cdot \left(\frac{R_c}{R}\right)^2.$$

(14)

Using (8), the expression for 1/f noise with  $\beta \approx 1$  is

$$S_i = \frac{A}{f} \cdot I_{dc}^2 = \frac{A_b}{f} \cdot I_{dc}^2 \cdot \left(\frac{R_b}{R}\right)^2 + \frac{A_c}{f} \cdot I_{dc}^2 \cdot \left(\frac{R_c}{R}\right)^2$$

(15)

where  $A_b$  and  $A_c$  are the 1/f noise coefficients for the bulk and the contact region, respectively. Equation (15) can be simplified to

$$A = A_b \cdot \left(\frac{R_b}{R}\right)^2 + A_c \cdot \left(\frac{R_c}{R}\right)^2. \tag{16}$$

Most of our devices have multiple nanowires. The total noise of the device is the sum of the noise contribution from all the nanowires in the device. From (8)

$$S_{t} = \frac{A_{t}}{f} \cdot I_{t}^{2} = \sum_{i=1}^{N} \frac{A_{i}}{f} \cdot I_{i}^{2}$$

(17)

$$\Rightarrow A_t = \sum_{i=1}^{N} A_i \cdot \frac{I_i^2}{I_t^2} \tag{18}$$

where  $A_t$  and  $I_t$  are the combined noise coefficient and current for all the nanowires in the device under study, and  $A_i$  and  $I_i$  are the noise coefficient and current for the ith nanowire. Using (16)–(18)

$$A_t = \sum_{i=1}^{N} \left[ A_{\text{bi}} \cdot \left( \frac{R_{\text{bi}}}{R_i} \right)^2 + A_{\text{ci}} \cdot \left( \frac{R_{\text{ci}}}{R_i} \right)^2 \right] \cdot \left( \frac{I_i}{I_t} \right)^2. \tag{19}$$

From (19), the bulk and contact noise components can be separated. The bulk noise is given by

$$A_b = \sum_{i=1}^{N} \left[ A_{\text{bi}} \cdot \left( \frac{R_{\text{bi}}}{R_i} \right)^2 \right] \cdot \left( \frac{I_i}{I_t} \right)^2 \tag{20}$$

and the noise component from the contact is given by,

$$A_c = \sum_{i=1}^{N} \left[ A_{ci} \cdot \left( \frac{R_{ci}}{R_i} \right)^2 \right] \cdot \left( \frac{I_i}{I_t} \right)^2 \tag{21}$$

with

$$A_t = A_b + A_c. (22)$$

If either  $A_b$  or  $A_c$  is known, the other one can be calculated from (22).

The noise component of the bulk can be accurately determined from the devices that have negligible contact resistance. To understand this consider (16). For negligible contact resistance, i.e.,  $R_b \gg R_c$ , we have  $R \approx R_b$  and  $R \gg R_c$ . Then from (16)

$$A \approx A_b$$

. (23)

Also, from (20) with  $R_i \approx R_b$

$$A_b = \sum_{i=1}^{N} [A_{\text{bi}}] \cdot \left(\frac{I_i}{I_t}\right)^2. \tag{24}$$

From the well-known Hooge model for bulk 1/f noise [5]

$$A_{\rm bi} = \frac{\alpha_{\rm Hb}}{p \cdot V_i} \tag{25}$$

where  $\alpha_{\rm Hb}$  is the Hooge parameter, p is the density of carriers, and  $V_i$  is the volume of the ith wire. Using the Hooge model in (24)

$$A_b = \alpha_{\text{Hb}} \cdot \sum_{i=1}^{N} \frac{1}{p \cdot V_i} \cdot \left(\frac{I_i}{I_t}\right)^2 \tag{26}$$

$$\Rightarrow \alpha_{\rm Hb} = A_b / \sum_{i=1}^{N} \frac{1}{p \cdot V_i} \cdot \left(\frac{I_i}{I_t}\right)^2. \tag{27}$$

The Hooge parameters were calculated from the devices with the lowest resistivity and noise. As these devices have the lowest contact resistance, the  $\alpha_{\rm Hb}$  calculated using (27) gives the best estimate of the bulk Hooge parameter. The calculated Hooge parameters are  $1.1 \times 10^{-5}$  and  $7.5 \times 10^{-6}$  for wafer 1 and wafer 2, respectively. In general, the value of the Hooge parameter is a good indicator of the process quality, and the values obtained for the Si nanowires are comparable to Hooge parameters for modern low noise silicon bulk devices [9]. Using these calculated Hooge parameters the bulk and contact noise A values for the other devices were calculated using (20), (21), and (26).

However, unlike bulk noise, there is no known model for contact noise, so the contact noise magnitude per wire  $(A_{\rm ci})$  cannot be calculated directly from (21). To calculate the contact noise it is necessary to assume a functional dependence between the noise magnitude and some physical parameter such as the radius or length. One can expect the contact noise to be some function of radius but independent of length. Hence, the following model for the contact noise was adopted:

$$A_{\rm ci} \propto r_i^m$$

(28)

where  $r_i$  is the radius of the nanowire. The exponent m determines how the noise is related to the physical parameter of the corresponding nanowire. For example, for m=0, 1, and 2, the noise is independent, proportional to the radius and proportional to the cross-sectional area respectively. The values for m tested for a fit were -3, -2, -1, 0, 1, 2, and 3. The best fit to the data was obtained for m=-2, in other words the best-fit model suggests the relative noise is inversely proportional to the cross-sectional area of the nanowire, i.e.,

$$A_{\rm ci} \propto \frac{1}{\pi r_i^2}.$$

(29)

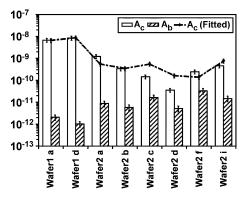

Fig. 6. Contact and bulk noise components calculated from measured data. The contact noise component calculated from the model is also shown. The calculated uncertainties due to measurement uncertainties are indicated.

The proportionality constants for wafers 1 and 2 are  $4.7 \times 10^{-18} \text{ cm}^2$  and  $4.6 \times 10^{-19} \text{ cm}^2$ , respectively. Comparing (11) and (29)

$$A_{\rm ci} \propto R_{\rm ci}$$

. (30)

This model suggests that the contact noise is proportional to the contact resistance, which is reasonable, considering that both the noise and the resistance indicate the quality of the contact. The calculated contact noise from measurements and the modeled noise are shown in Fig. 6. The plot shows good agreement between the model and the measured noise and also shows that the agreement is worse if the magnitudes of the bulk and contact noise components become comparable. This is expected because the calculation involves subtracting two statistical quantities; consequently, when the magnitudes of the two noise components are comparable, the error in  $A_{\rm c}$  calculated using (22) will become higher.

## IV. SUMMARY AND CONCLUSION

The resistance model presented enables the calculation of the bulk and contact components of the resistance. The contact resistance is believed to originate from the impinging end of the nanowire where the nanowire connects to the uncatalyzed silicon layer. To estimate the relative magnitudes of the bulkand contact-resistance components, consider a typical nanowire with a length and radius of 8  $\mu$ m and 50 nm, respectively. For a doping level of  $1 \times 10^{18}/\text{cm}^3$ , the bulk resistance is 424 k $\Omega$ . The contact resistance calculated from the model is 215 k $\Omega$ , and is a significant portion of the total resistance. It can probably be reduced by improved processing. The bulk 1/f noise coefficient for this nanowire for a Hooge parameter of  $1 \times 10^{-5}$  is  $5 \times 10^{-10}$ . The 1/f noise coefficient for the contact noise from the model is  $1 \times 10^{-8}$ , for a proportionality constant of  $1 \times 10^{-19}$ . Hence, the contact noise is the dominant noise mechanism in this nanowire. The likely mechanism for noise in the case of our devices is carrier trapping-detrapping in defects producing the well-known 1/f-like number fluctuation noise spectra [10]. The impinging end of the wire, where contact to the silicon electrode is made through possibly pinholes in the native oxide, is expected to be defect rich and thus the dominant source of contact noise whereas the base end of the nanowire is connected epitaxially to the silicon sidewall creating a defect lean, lower noise contact

configuration. Furthermore because of the higher resistance on the impinging side, any fluctuations in this contact will couple out more to the device contacts.

Now, a comparison between the noise characteristics of the measured nanowires and carbon nanotubes will be presented. As mentioned earlier, the 1/f noise in carbon nanotubes is reported to be unusually high [3], and the origin of this noise is still a subject of active research. The resistance in a carbon nanotube is mostly at the contact, and bulk resistance is negligible, as it is a one-dimensional mesoscopic quantum device [11]. So, for a fair comparison, the noise in carbon nanotubes will be compared with the contact noise of the nanowires. The quantity A/R (the ratio between the 1/f noise coefficient and the resistance) for a carbon nanotube can serve as a figure of merit for 1/f noise magnitude, and it was found to be approximately equal to  $10^{-11}\Omega^{-1}$  for single wall carbon nanotubes [3].

The quantity A/R for the contact region of the silicon nanowire (i.e.,  $A_c/R_c$ ) from the model presented here is also a constant, and from (30) the values for wafer 1 and 2 are  $2.8 \times 10^{-13}$  and  $2.7 \times 10^{-14}$ , respectively. So it can be concluded that a silicon nanowire has at least two orders of magnitude better noise performance than a carbon nanotube, which we attribute to better quality contacts with a lower defect density. Our analysis also shows that the Hooge parameter, the figure of merit for bulk noise performance, is within the range of Hooge parameters for modern low noise bulk devices [9]. Because the contact was identified as the dominant source of noise, we can envision further noise reduction by optimizing the contact. Reducing the contact resistance can potentially reduce contact noise because they originate from a common mechanism, as indicated by (30); moreover, less contact noise will couple out into the remainder of the circuitry as the contact resistance becomes a smaller fraction of the total resistance.

## REFERENCES

- S. Iijima, "Helical microtubules of graphitic carbon," *Nature*, vol. 354, pp. 56–58, 1991.

- [2] M. S. Islam, S. Sharma, T. I. Kamins, and R. S. Williams, "Ultrahigh-density silicon nanobridges formed between two vertical silicon surfaces," *Nanotechonology*, vol. 15, pp. L5–L8, 2004.

- [3] P. G. Collins, M. S. Fuhrer, and A. Zettl, "1/f noise in carbon nanotubes," *App. Phys. Lett.*, vol. 76, pp. 894–896, 2000.

- [4] M. S. Islam, S. Sharma, T. I. Kamins, and R. S. Williams, "A novel interconnection technique for manufacturing nanowire devices," *App. Phys. A*, vol. 80, pp. 1133–1140, 2005.

- [5] F. N. Hooge, T. G. M. Kleinpenning, and L. K. J. Vandamme, "Experimental studies on 1/f noise," *Rep. Prog. Phys.*, vol. 44, no. 5, pp. 479–532, 1981.

- [6] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. New York: Wiley, 1981.

- [7] Y. Cui, X. F. Duan, J. T. Hu, and C. M. Lieber, "Doping and electrical transport in silicon nanowires," *J. Phys. Chem. B*, vol. 104, no. 22, pp. 5213–5216, 2000.

- [8] S. Sharma, T. I. Kamins, M. S. Islam, R. S. Williams, and A. F. Marshall, "Structural characteristics and connection mechanism of gold-catalyzed bridging silicon nanowires," *J. Cryst. Growth*, vol. 280, pp. 562–568, 2005.

- [9] F. N. Hooge, "1/f noise sources," *IEEE Trans. Electron Devices*, vol. 41, no. 11, pp. 1926–1935, Nov. 1994.

- [10] A. Van der Ziel, Noise in Solid State Devices and Circuits. New York: Wiley, 1986.

- [11] R. Saito, G. Dresselhaus, and M. S. Dresselhaus, Physical Properties of Carbon Nanotubes. London, U.K.: Imperial College Press, 1998.

Shahed Reza received the B.S. degree in electrical engineering from the Bangladesh University of Engineering and Technology (BUET), Dhaka, in 1994 and the M.S. degree in electrical engineering from the University of Central Florida, Orlando, in 1998. He is currently working toward the Ph.D. degree in the Department of Electrical and Computer Engineering at the University of Florida, Gainesville. His thesis topic is "Excess noise in one-dimensional quantum nanowires."

He worked for the Bangladesh Atomic Energy Research Establishment before coming to the United States. He was a design engineer at Piezo Technology Inc. (PTI) from 1997 to 2000. At PTI, he designed precision crystal oscillators and *LC* filters. From 2000 to 2003, he designed analog microwave circuits at Agilent Technologies. Currently he is working as a Research Engineer at Invivo Diagnostic Imaging, Orlando. At Invivo, he is conducting research on image guided noise tomography and the modeling and simulation of RF probes used in MR imaging. As a Ph.D. student, he is also conducing research on the noise properties of carbon nanotubes and silicon page wives

**Gijs Bosman** (M'82–SM'89) received the B.S., M.S., and Ph.D. degrees in physics from the University of Utrecht, The Netherlands in 1971, 1976, and 1981, respectively.

In 1981 he joined the Department of Electrical and Computer Engineering of the University of Florida, Gainesville, where he is currently a Professor. His research interests include the electrical noise and charge transport properties of semiconductor devices and circuits. He has published more than 100 refereed journal and conference papers on these

topics. In addition to the College of Engineering Teacher of the Year Award for 1998–1999, he received several university and departmental awards for teaching and research.

Prof. Bosman is a member of the American and Dutch Physical Societies.

M. Saif Islam (S'98-M'02) received the B.Sc. degree in physics from Middle East Technical University (METU), Ankara, Turkey, in 1994, the M.Sc. degree in physics from Bilkent University, Ankara, Turkey, in 1996, and the M.S. and Ph.D. degrees in electrical engineering from the University of California at Los Angeles (UCLA), Los Angeles, in 1999 and 2001, respectively.

Before joining the University of California, Davis (UC Davis), in 2004 as an Assistant Professor, he worked at Hewlett-Packard Laboratories, Gazillion

Bits Inc., and SDL Inc./JDS Uniphase Corporation as a Staff Scientist, Senior Scientist and Postdoctoral Research Fellow. He also served as an adjunct faculty member with the ECE department of San Jose State University, San Jose, CA. He is the director of the Integrated Nanodevices and Systems Research (Inano) of UC Davis, has authored or coauthored more than 70 journal and conference papers, edited four books and conference proceedings and holds two patents with more than 30 pending patents as an inventor or a coinventor. His work has covered a broad variety of topics: molecular electronic devices, synthesis, device applications and CMOS integration of semiconductor nanowires, ultrafast optoelectronic devices, high-power and linear gain-clamped semiconductor optical amplifiers, fiber optical communication systems, and RF photonic devices and links. He was the first to demonstrate the velocity-matched distributed balanced photodetectors with a record high linear photocurrents and an ultrafast response. He also worked on the first demonstration of ultra-fast resonant cavity enhanced (RCE) Schottky photodiodes. Currently, his main interests are in the areas of massively parallel incorporation of low-dimensional nanowire devices with conventional IC elements, employing processes compatible with mass manufacturing for potential applications in biochemical sensing, nanoelectronics, nanophotonics, memory, and logic devices for future computing.

Dr. Islam's honors and awards include the NSF Faculty Early Career Development Award (2006); Professor of the Year 2005 (IEEE Davis Chapter), University of California Chancellor's Fellowship; Invited Research Fellowship with University of Maryland and National Security Agency (NSA); IEEE Laser and Electro-Optic Society (IEEE/LEOS) Fellowship (2000); Who's Who in Science

and Engineering; Student of the Year (1988) and the President's Award from the President of the Republic of Bangladesh (1989). He has served as the chairs of several international SPIE and MRS sponsored conferences on nanoscale sensors and devices and negative index materials and served as a guest editor for special issues of the *International Journal of Nanotechnology* (special issue on nanosensors) and *Applied Physics A: Materials Science and Processing* (special issue on metamaterials). He is a member of the Optical Society of America (OSA) and the American Physical Society, Material Research Society (MRS).

**Theodore I. Kamins** (S'65–M'68–SM'79–F'91) received the B.S., M.S. and Ph.D. degrees from the University of California, Berkeley.

He then joined the Research and Development Laboratory of Fairchild Semiconductor, where he worked with epitaxial and polycrystalline silicon before moving to Hewlett-Packard, where he has worked on numerous semiconductor material and device topics. He is Principal Scientist in the Quantum Science Research group at Hewlett-Packard Laboratories, Palo Alto, CA, where he is conducting

research on advanced nanostructured electronic materials and devices. He is also a Consulting Professor in the Electrical Engineering Department at Stanford University. He is coauthor with R. S. Muller of the textbook *Device Electronics for Integrated Circuits* (Wiley, 2002) and is author of the book *Polycrystalline Silicon for Integrated Circuits and Displays* (Kluwer, 1998).

Dr. Kamins is a Fellow of the Electrochemical Society.

Shashank Sharma received the B.Tech. degree in chemical engineering from Osmania University, Hyderabad, India, in 1998 and the M.S. and Ph.D degrees in chemical engineering from University of Louisville, Louisville, KY in 2000 and 2003, respectively.

He was a Postdoctoral Research Associate in the Quantum Science Research group at Hewlett-Packard Laboratories, Palo Alto, CA, from 2003 to 2006. He is currently a Senior Process Development Engineer at Spansion Inc., Sunnyvale, CA. His work at HP Labs focused on the development of a metal-catalyzed chemical vapor deposition process that will lead to large area semiconductor nanowire arrays integrated within micron scale devices. His research primarily involved using chemical vapor deposition to form nanostructures by self-assembly approach. In this approach, the chemical reactions providing the precursors for nanowire growth (silicon and germanium) are locally enhanced by a metal catalyst. He focused his efforts on controlling both the catalyzing nanoparticles and also the chemical reactions providing the silicon or germanium to yield nanowires with controlled and desired characteristics. His doctoral research focused on bulk nucleation and growth of inorganic one-dimensional nanostructures using chemical vapor deposition utilizing large pools of noncatalytic low-melting metal melts exposed to an activated gas phase containing the appropriate growth precursors.

Dr. Sharma was awarded with the John M. Houchens prize by the University of Louisville for outstanding dissertation among the graduating class of May 2003. He was nominated to Who's Who Among Students in American Colleges and Universities in 2001 and elected to the Phi Kappa Phi National All University Honor Society in 2000.

**R. Stanley Williams** received the B.A. degree in chemical physics from Rice University, Houston, TX, in 1974 and the Ph.D. degree in physical chemistry from the University of California, Berkeley, in 1978.

He was a Faculty Member (Assistant, Associate, and Full Professor) in the Chemistry Department at the University of California, Los Angeles, from 1980 to 1995. He is currently a Senior Fellow at Hewlett-Packard Laboratories, Palo Alto, CA, and Founding Director of the Quantum Science Research

(QSR) group. He has been awarded 47 U.S. patents and has published 270 papers in reviewed scientific journals. His primary scientific research during the past 25 years has been in the areas of solid-state chemistry and physics.

Dr. Williams' awards for scientific and academic achievement include the 2000 Julius Springer Award for Applied Physics, the 2000 Feynman Prize in Nanotechnology, and the 2004 Birnbaum Prize. He was named to the inaugural *Scientific American* 50 Top Technology leaders in 2002, and the molecular electronics program he leads was named the Technology of the Year for 2002 by *Industry Week* magazine.