OULU 2008

## UNIVERSITATIS OULUENSIS

## Lucian Stoica

# NON-COHERENT ENERGY DETECTION TRANSCEIVERS FOR ULTRA WIDEBAND IMPULSE RADIO SYSTEMS

FACULTY OF TECHNOLOGY, DEPARTMENT OF ELECTRICAL AND INFORMATION ENGINEERING, CENTRE FOR WIRELESS COMMUNICATIONS, INFOTEC OULU, UNIVERSITY OF OULU

#### ACTA UNIVERSITATIS OULUENSIS C Technica 292

LUCIAN STOICA

### NON-COHERENT ENERGY DETECTION TRANSCEIVERS FOR ULTRA WIDEBAND IMPULSE RADIO SYSTEMS

Academic dissertation to be presented, with the assent of the Faculty of Technology of the University of Oulu, for public defence in Raahensali (Auditorium L10), Linnanmaa, on February 8th, 2008, at 12 noon

OULUN YLIOPISTO, OULU 2008

Copyright © 2008 Acta Univ. Oul. C 292, 2008

Supervised by Doctor Ian Oppermann Professor Matti Latva-aho

Reviewed by Doctor John R. Farserotu Professor Kari Halonen

ISBN 978-951-42-8716-9 (Paperback) ISBN 978-951-42-8717-6 (PDF) http://herkules.oulu.fi/isbn9789514287176/ ISSN 0355-3213 (Printed) ISSN 1796-2226 (Online) http://herkules.oulu.fi/issn03553213/

Cover design Raimo Ahonen

OULU UNIVERSITY PRESS OULU 2008

## Stoica, Lucian, Non-coherent energy detection transceivers for Ultra Wideband Impulse radio systems

Faculty of Technology, University of Oulu, P.O.Box 4000, FI-90014 University of Oulu, Finland, Department of Electrical and Information Engineering, Centre for Wireless Communications, Infotech Oulu, University of Oulu, P.O. Box 4500, FI-90014 University of Oulu, Finland *Acta Univ. Oul. C 292, 2008* Oulu, Finland

#### Abstract

The focus of this thesis is Ultra Wideband (UWB) Impulse Radio (UWB-IR) transmitters and noncoherent receivers. The aim of the thesis is to investigate, analyze and design UWB-IR transmitter and receiver structures both from a theoretical and circuit design viewpoint.

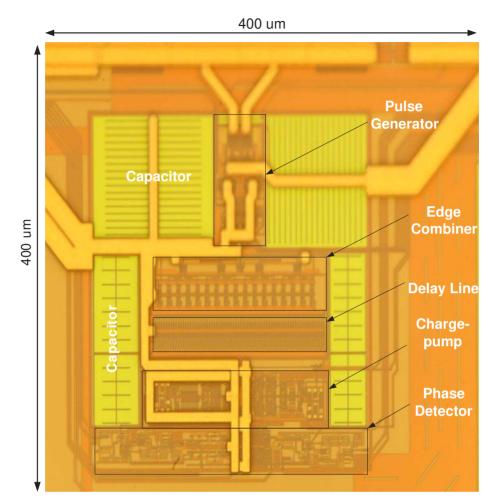

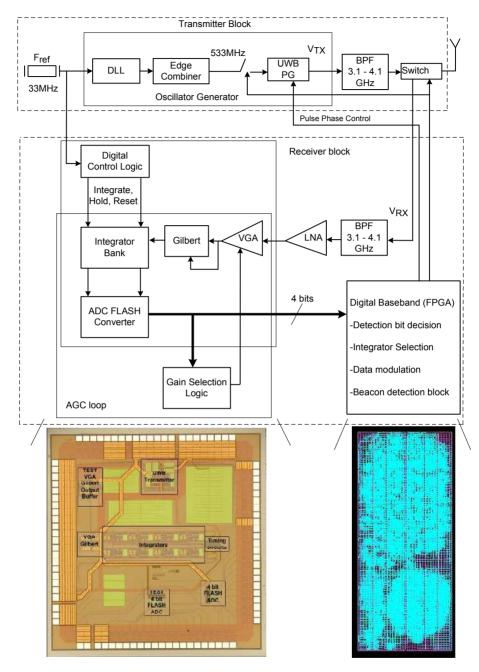

An UWB-IR transmitter structure is proposed and is the subject of a detailed investigation. The transmitter generates a Gaussian monocycle and can be modified to generate a family of Gaussian waveforms. The Gaussian monocycle is easy to generate while providing good bit-error-rate (BER) performance. The Gaussian monocycle has a wide -10 dB bandwidth and a zero-DC component which does not decrease antenna efficiency. The transmitter design includes a delay locked loop (DLL) based frequency synthesis approach. The advantage of using a frequency synthesis approach based on a DLL is based on the fact that a DLL generates less noise than a phase locked loop (PLL) and is inherently stable. The generated pulse has a width of less than 350 ps and a -10 dB bandwidth of 4.7 GHz. The power consumption of the designed UWBIR transmitter is 20 mW at a voltage supply of 3.3 V. Compared with other integrated UWB-IR transmitters, the transmitter presented in this thesis has the lowest pulse width for comparable integrated processes, one of the lower power consumptions and a low die area.

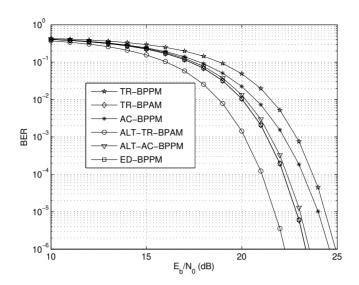

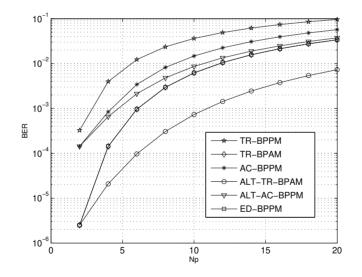

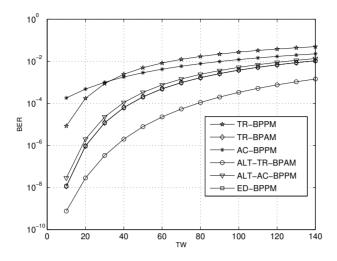

The BER performance of several UWB-IR non-coherent receiver structures is presented. The energy detection (ED) receiver offers the same BER performance as the transmitted reference scheme with binary pulse amplitude modulation (BPAM) but has a lower implementation complexity since it does not require an analogue delay line in its structure.

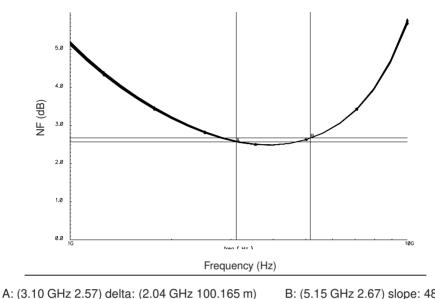

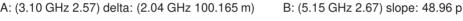

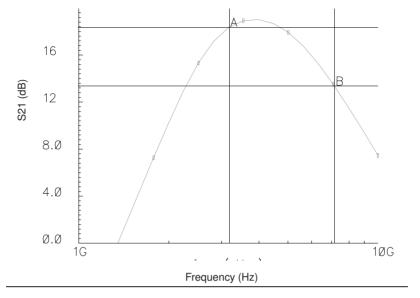

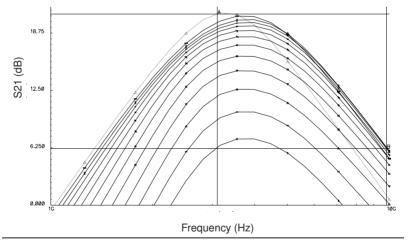

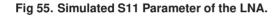

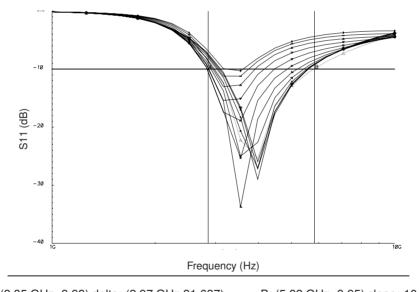

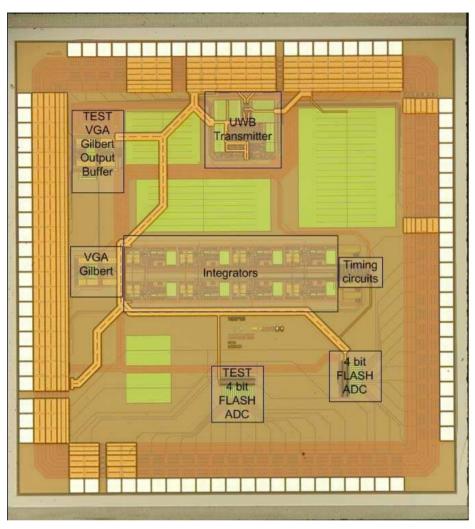

Circuit performance of several blocks of the ED receiver is presented. The radio frequency (RF) front-end and analogue baseband sections of the receiver have been designed as an integrated circuit (IC) in a 0.35  $\mu$ m bipolar complementary metal oxide semiconductor (BiCMOS) process. The RF front-end section includes a low noise amplifier (LNA), a variable gain amplifier (VGA) and a Gilbert cell. The LNA has a noise figure (NF) of less than 3 dB, a gain of 18 dB in the interest bandwidth and less than 20 mW of power consumption. The NF of the LNA can be reduced even further at the expense of a higher power consumption or by using input pads with lower capacitance values. The noise figure can be also lowered by using a process which provides transistors with higher transit frequency ( $f_T$ ). Trading-off power consumption for noise is still a key design issue in the design of integrated UWB-IR receivers.

The analogue baseband section includes a bank of integrators and a 4-bit analogue to digital converter (ADC). The ADC is running at a sampling rate equal to the symbol rate and takes only 2 mW of power at 3.3 V supply. The power consumption of the designed integrated front-end and analogue baseband receiver sections is 117 mW at a power supply of 3.3 V.

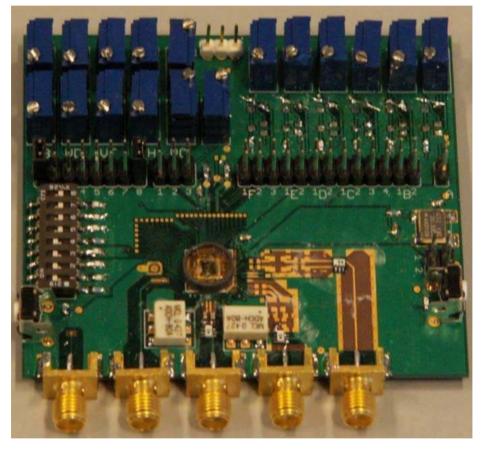

The digital baseband of the receiver have been implemented on a field programmable gate array (FPGA) technology. The power consumption of the baseband is 450 mW with a power supply of 1.2 V and a maximum supply of 3.3 V for input-output pins.

The total power consumption of the designed transceiver is 587 mW. When compared with other UWB receiver architectures, the energy detection receiver has the lowest power consumption due to the low power consumption of the LNA, simple synchronization architecture and low sampling rate of the ADC.

Keywords: energy detection, Gaussian monocycle, impulse radio, low noise amplifier, ultra wideband

To my family

## Preface

Research for this thesis has been carried out at the Centre for Wireless Communications (CWC), University of Oulu, Finland. I joined the CWC in March 2003 where I started my postgraduate studies. Having Dr. Ian Oppermann as a supervisor of my research work was truly a privilege and I would like to thank him for that. His high research standards and technical precision will always remain my professional goals. I thank Professor Matti Latva-aho for all support, advice and encouragements I received from him during my study years.

Most of the work presented in this thesis was conducted in the <u>U</u>ltra Wideband <u>RF-ASIC (URFA), <u>U</u>WB <u>W</u>ireless <u>E</u>mbedded <u>N</u>etworks (UWEN) and <u>P</u>ervasive <u>U</u>ltra wideband <u>Low Spectral Energy Radio Systems (PULSERS) projects.</u></u>

I would also like to thank other colleagues, most of which are from the UWB group, Alberto Rabbachin, Sakari Tiuraniemi, now with CERN, and Heikki Repo, now with Embio. Special thanks to Professor Timo Rahkonen, from the Electronics Laboratory, for his review of the first version of the UWB-IR IC transceiver I have worked. The discussions with him have been inspiring and informative.

The computer and technical support of Pekka Nissinaho and Jukka Lahti and administrative support of Laila Kuhalampi and Hanna Saarella are gratefully acknowledged. I thank all the personnel in the CWC and Telecommunication Laboratory for providing a pleasant working environment.

I wish to thank the reviewers of the thesis for their patience in reading the manuscript and for their insightful comments. Their comments have significantly improved the quality of the thesis.

During my postgraduate studies I had the privilege of being a student in the Infotech Oulu Graduate School as well as in three research projects. The financial support of Nokia, TEKES, the National Technology Agency of Finland, on these projects is gratefully acknowledged. I am also thankful to Elisa Communications foundation and Nokia Foundation for their financial support.

Thanks to Thales Electronic Solutions, Stuttgart Design Office, Germany for the help provided during the measurements and their hospitality during my 2005 visit. I would like to thank Professor Moe Win at Massachusetts Institute of Technology for his hospitality during my 2006 visit.

I wish to thank Ian and Therese Oppermann for their unforgettable open house events.

I am thankful to Professors Vlad Cehan, Nicolae Dumitru Alexandru and Gabriel Popescu from Technical University of Iasi, for their encouragement, advices and support during my study years. Finally, I wish to thank my mother Margareta and grandparents Elena, Grigore and Vasile for all the love and support she gave me throughout my life and hard years of study. My deep gratitude goes to Gheorghe and Floarea Iancu whom I will always regard as my second parents.

My warmest gratitude belongs to my lovely wife Iulia for all the sincere love, support and understading she had for me throughout all these years. Our children Victor-Markku and Diana-Aleksandra disconnected me from any thesis related troubles the moment I come home. Their support has been my solid ground to stand on.

## List of symbols and abbreviations

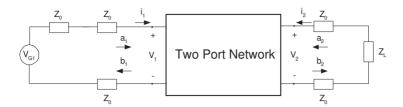

| $a_i$             | incident normalized power wave                |

|-------------------|-----------------------------------------------|

| $A_n$             | amplitude                                     |

| $b_i$             | reflected normalized power wave               |

| $B_{-10}$         | -10dB bandwidth                               |

| $B_f$             | fractional bandwidth                          |

| $B_{w}$           | bandwidth                                     |

| $B_R$             | resolution bandwidth                          |

| С                 | channel capacity                              |

| $C_{loop}$        | loop filter capacitor                         |

| $c_j$             | momentary code phase                          |

| d                 | distance                                      |

| $d_k$             | <i>k</i> -th data bit                         |

| $E_b$             | energy of bit                                 |

| $E_b/N_0$         | bit energy per noise power ratio              |

| $E_p$             | energy of a single pulse                      |

| $f_c$             | center frequency                              |

| $f_h$             | higher frequency limit                        |

| $f_l$             | lower frequency limit                         |

| $f_m$             | offset frequency                              |

| $f_{max}$         | maximum oscillation frequency                 |

| $f_o$             | output frequency of the cock multiplier block |

| $f_T$             | transit frequency                             |

| 8ds               | output conductance                            |

| $G_{RX}$          | receiver antenna gain                         |

| $G_{TX}$          | transmitter antenna gain                      |

| I <sub>pump</sub> | charge pump current                           |

| IIP <sub>3</sub>  | input third order harmonic intercept point    |

| IPI               | inter-pulse interference                      |

| ISI               | inter-symbol interference                     |

| j                 | index, transmitted bit                        |

| k                 | index                                         |

|                   |                                               |

| K <sub>D</sub>       | phase detector gain                                   |

|----------------------|-------------------------------------------------------|

| $K_F$                | charge pump-loop filter gain                          |

| $K_V$                | voltage controlled delay line gain                    |

| L                    | number of resolvable multipath                        |

| $L_{ch}$             | electrical channel length of a CMOS device            |

| $L_1$                | path loss at 1m                                       |

| $L_2$                | path loss at 3m                                       |

| n                    | path gain                                             |

| N <sub>collide</sub> | collide frame                                         |

| N <sub>0bit</sub>    | average noise power per bit                           |

| N <sub>bit</sub>     | preamble length                                       |

| Nint                 | number of integrators                                 |

| $N_p$                | number of pulses                                      |

| $N_{\mu}$            | number of users                                       |

| NF                   | noise figure                                          |

| NF <sub>min</sub>    | minimum noise figure                                  |

| $N_0$                | one sided power spectral density white Gaussian noise |

| OFF                  | closed switch                                         |

| ON                   | open switch                                           |

| $P_b$                | bit error probability                                 |

| $P_N$                | average noise power                                   |

| $P_{RX}$             | received power                                        |

| $P_{TX}$             | transmitted power                                     |

| PG                   | processing gain                                       |

| r <sub>b</sub>       | base resistance                                       |

| R                    | data rate                                             |

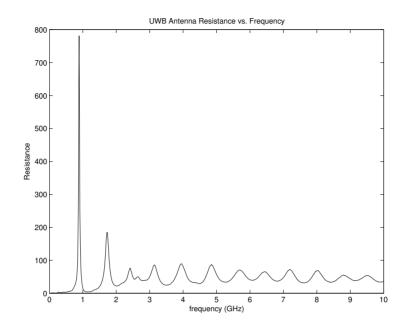

| $R_A$                | antenna resistance                                    |

| $R_g$                | generator resistance                                  |

| $R_L$                | antenna loss resistance                               |

| $R_T$                | load resistance                                       |

| s(t)                 | transmitted signal                                    |

| $s_r(t)$             | received signal                                       |

| $S_{\Phi}$           | phase noise                                           |

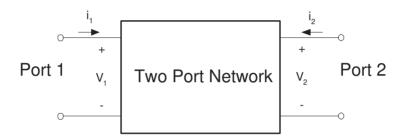

| $S_{11}$             | input reflection coefficient                          |

| $S_{21}$             | forward voltage gain                                  |

|                      |                                                       |

| $S_{12}$         | reverse voltage gain                          |

|------------------|-----------------------------------------------|

| $S_{11}$         | output reflection coefficient                 |

| Q                | quality factor                                |

| QoS              | quality of service                            |

| t                | time                                          |

| $t_{ox}$         | gate-oxide thickness of a CMOS device         |

| $T_c$            | chip length                                   |

| $T_d$            | symbol length                                 |

| $T_{PRF}$        | frame length                                  |

| $T_p$            | pulse width                                   |

| T <sub>ref</sub> | reference clock period                        |

| $T_{OUT}$        | output clock period                           |

| $T_s$            | symbol length                                 |

| TW               | time-bandwidth product                        |

| $X_A$            | antenna reactance                             |

| $X_g$            | generator reactance                           |

| $Y_1$            | observation variable                          |

| $Y_2$            | observation variable                          |

| $Z_A$            | antenna impedance                             |

| $X_T$            | load reactance                                |

| $Z_0$            | $50\Omega$ impedance                          |

| Zin              | input impedance                               |

| WTR              | transmitted pulse                             |

| α                | multipath gain coefficient, effective channel |

| β                | modulated symbols                             |

| δ                | Dirac's delta function                        |

| λ                | wavelength, arrival rate of paths             |

| Λ                | cluster arrival rate                          |

| $\sigma_t$       | standard deviation parameter                  |

| $\sigma_{th}$    | threshold matching parameter                  |

| $	au_n$          | delay                                         |

| $\omega_{if}$    | intermediate angular frequency                |

| $\omega_{LO}$    | local oscillator angular frequency            |

| $\omega_{rf}$    | angular frequency                             |

| AC               | auto-correlation                              |

|                  |                                               |

| ADC     | analogue to to digital converter                                 |

|---------|------------------------------------------------------------------|

| AFOM    | analogue figure of merit                                         |

| ALT     | alternate                                                        |

| AMPS    | advanced mobile phone system                                     |

| AMS     | AustriaMicrosystems                                              |

| ARAKE   | all rake receiver                                                |

| AWGN    | additive white Gaussian noise                                    |

| BER     | bit error rate                                                   |

| BiCMOS  | bipolar complementary metal oxide semiconductor                  |

| BPAM    | binary pulse amplitude modulation                                |

| BPF     | bandpass filter                                                  |

| BPM     | bit position modulation                                          |

| BPAM    | binary pulse amplitude modulation                                |

| BPSK    | binary phase shift keying                                        |

| CEPT    | European Conference of Postal and Telecommunications Administra- |

|         | tion                                                             |

| СМ      | channel model                                                    |

| CMFB    | common mode feedback                                             |

| CMOS    | complementary metal oxide semiconductor                          |

| CMRR    | common mode rejection ratio                                      |

| DAA     | detection and avoidance                                          |

| DARPA   | Defense Advanced Research Projects Agency (USA)                  |

| DB      | doublet based                                                    |

| DC      | direct current                                                   |

| DD      | delay detector                                                   |

| DECT    | digital enhanced cordless telecommunications                     |

| DH      | delay hoped                                                      |

| DLL     | delay locked loop                                                |

| DS      | direct sequence                                                  |

| DS - SS | direct sequence spread spectrum                                  |

| DVI     | digital visual interface                                         |

| EC      | European Commission                                              |

| ECC     | Electronic Communications Committee                              |

| ED      | energy detection                                                 |

| EGC     | equal gain combining                                             |

|         |                                                                  |

| EIRP    | equivalent isotropic radiated power                                    |

|---------|------------------------------------------------------------------------|

| ETSI    | European Telecommunications Standards Institute                        |

| FCC     | Federal Communications Commission                                      |

| FIR     | finite impulse response                                                |

| FM      | frequency modulation                                                   |

| FPGA    | field programmable gate array                                          |

| GPS     | global positioning system                                              |

| GSM     | global system for mobile communications                                |

| HBT     | heterojunction bipolar transistor                                      |

| IC      | integrated circuit                                                     |

| IR      | impulse radio                                                          |

| IEEE    | Institute of Electrical and Electronics Engineers                      |

| ITU     | International Telecommunication Union                                  |

| LNA     | low noise amplifier                                                    |

| LO      | local oscillator                                                       |

| LOS     | line of sight                                                          |

| LPD     | low probability of detection                                           |

| LPI     | low probability of interception                                        |

| OFCOM   | Office of Communications (UK)                                          |

| OFDM    | orthogonal frequency division multiplexing                             |

| OOK     | on-off keying                                                          |

| OTA     | operational transconductance amplifier                                 |

| MAI     | multiple access interference                                           |

| MAC     | medium access control                                                  |

| MBOA    | multiband-orthogonal frequency division multiplexing alliance          |

| MB-OFDM | multiband orthogonal frequency division multiplexing                   |

| MCS     | modulation and coding scheme                                           |

| MIC     | Ministry of Internal Affairs and Communications (Japan)                |

| MII     | Ministry of Information Industry (China)                               |

| MPC     | multipath components                                                   |

| MRC     | maximum ratio combining                                                |

| NBI     | narrow band interference                                               |

| NESP    | normalized effective signal power                                      |

| NICT    | National Institute of Information and Communication Technology (Japan) |

| NLOS    | non-line-of-sight                                                      |

|         |                                                                        |

| PAM    | pulse amplitude modulation                     |

|--------|------------------------------------------------|

| PAN    | personal area network                          |

| PCSNIM | power constrained noise optimization technique |

| PDP    | power delay profile                            |

| PHY    | physical layer                                 |

| PLL    | phase locked loop                              |

| PPM    | pulse position modulation                      |

| PRAKE  | partial rake receiver                          |

| PRF    | pulse repetition frequency                     |

| PSD    | power spectral density                         |

| PSM    | pulse shape modulation                         |

| PVT    | process-voltage-temperature variations         |

| RF     | radio frequency                                |

| RMS    | root mean square                               |

| RO     | The First Report and Order (FCC, USA)          |

| RX     | receiver                                       |

| SiGe   | silicon-germanium                              |

| SNR    | signal-to-noise ratio                          |

| SOC    | system-on-a-chip                               |

| SOP    | system-on-package                              |

| SR     | single reference                               |

| SRAKE  | selective rake receiver                        |

| SRD    | step recovery diode                            |

| SRMC   | state radio monitoring center (China)          |

| SS     | spread spectrum                                |

| SV     | Saleh-Valenzuela channel model                 |

| TG     | task group                                     |

| TH     | time hopping                                   |

| TOA    | time-of-arrival                                |

| TR     | transmitted-reference                          |

| TSMC   | Taiwan Semiconductor Company                   |

| ТХ     | transmitter                                    |

| UMTS   | universal mobile telecommunications system     |

| USAF   | United States Air Force                        |

| USB    | Universal Serial Bus                           |

|        |                                                |

| UWB   | ultra wideband                                                    |

|-------|-------------------------------------------------------------------|

| VCDL  | voltage controlled delay line                                     |

| VCO   | voltage controlled oscillator                                     |

| VGA   | variable gain amplifier                                           |

| VHDL  | very high speed integrated circuits hardware description language |

| WCDMA | wideband code division multiple access                            |

| WG    | work group                                                        |

| WPAN  | wireless personal area network                                    |

## Contents

| Ab | stra    | ct                                                             |      |

|----|---------|----------------------------------------------------------------|------|

| Pr | eface   |                                                                | 7    |

| Li | st of s | symbols and abbreviations                                      | 9    |

| 1  | Intr    | oduction                                                       | 19   |

|    | 1.1     | Background for UWB Communication                               | . 19 |

|    | 1.2     | Historical Review of UWB Technology Development                | .21  |

|    | 1.3     | Author's Contribution                                          | . 23 |

|    | 1.4     | Outline of the Thesis                                          | . 24 |

| 2  | Ove     | rview of UWB Signals and Transmitter Structures                | 27   |

|    | 2.1     | Introduction                                                   | . 27 |

|    | 2.2     | UWB Standardization and Spectrum Regulation                    | 28   |

|    | 2.3     | Transmitted Signal Requirements in UWB Communication Systems   | . 30 |

|    | 2.4     | UWB Pulses                                                     | . 31 |

|    | 2.5     | Review of UWB-IR Transmitters                                  | . 36 |

|    | 2.6     | Conclusions                                                    | . 40 |

| 3  | Ove     | rview of UWB Receiver Structures                               | 41   |

|    | 3.1     | Comparison of UWB-IR Receiver Structures                       | 42   |

|    |         | 3.1.1 Rake Receiver Structures                                 | . 42 |

|    |         | 3.1.2 Autocorrelation Receivers                                | . 43 |

|    | 3.2     | UWB System Description                                         | 54   |

|    | 3.3     | UWB Signal Format                                              | 55   |

|    | 3.4     | Overview of Integrated Circuits UWB-IR Receivers               | . 56 |

|    | 3.5     | Comparison of Autocorrelation Receivers From An Implementation |      |

|    |         | Complexity Viewpoint                                           |      |

|    | 3.6     | Conclusions                                                    | . 60 |

| 4  | Pro     | posed UWB-IR Transmitter Architecture                          | 63   |

|    | 4.1     | Introduction                                                   | . 63 |

|    |         | 4.1.1 UWB-IR IC Transmitter Test Board                         | . 66 |

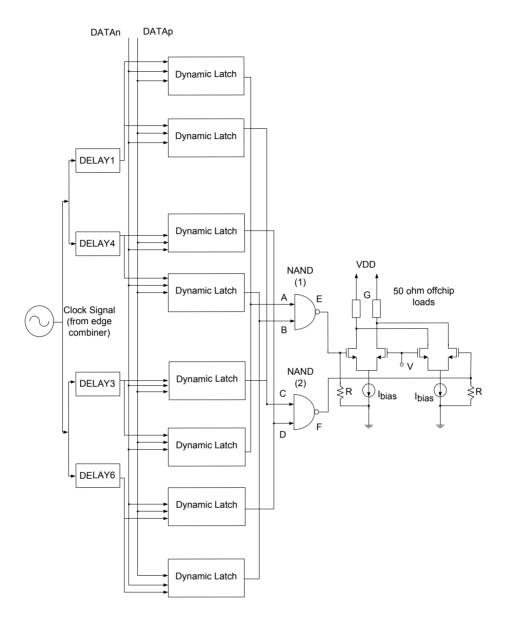

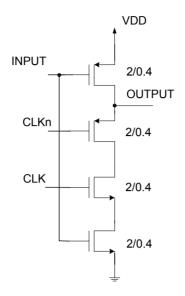

|    | 4.2     | Pulse Generator                                                | . 66 |

|    |         | 4.2.1 Approximation of the Gaussian Monocycle                  |      |

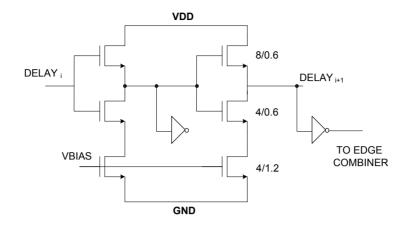

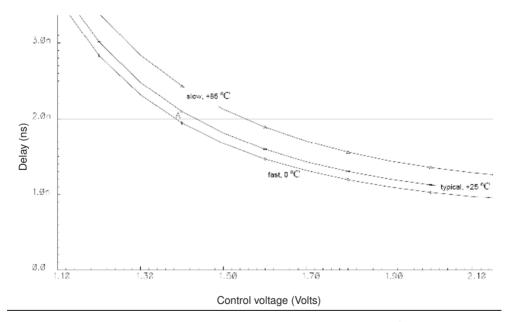

|    |         | 4.2.2 Delay Stage Block                                        | . 69 |

|    |         |                                                                |      |

|    |       | 4.2.3  | Pulse Shaper Block                                    | 72  |

|----|-------|--------|-------------------------------------------------------|-----|

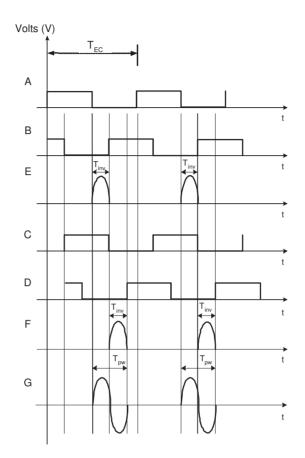

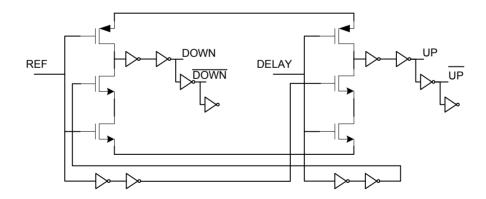

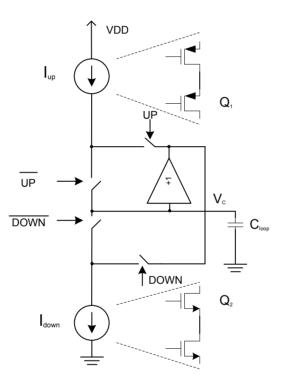

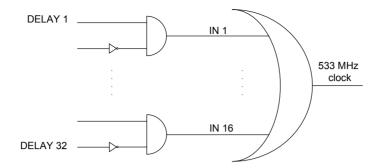

|    | 4.3   | Clock  | Multiplication Block                                  | 73  |

|    |       | 4.3.1  | DLL Based Clock Multiplier Block                      | 74  |

|    |       | 4.3.2  | Digital Edge Combiner                                 | 80  |

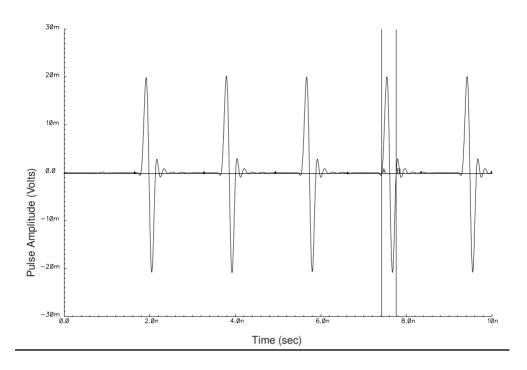

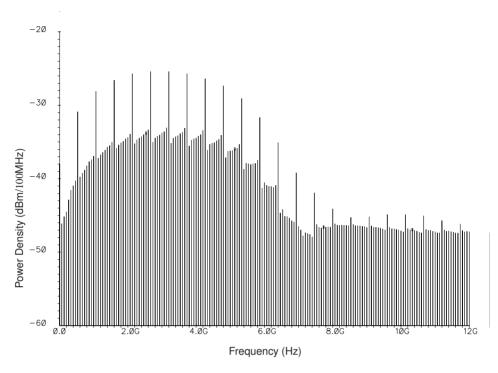

|    | 4.4   | Measu  | ured Results of the UWB-IR Transmitter                | 81  |

|    | 4.5   | Concl  | usions                                                | 88  |

| 5  | Pro   | posed  | UWB-IR Non-coherent Energy Collection Receiver Design | 91  |

|    | 5.1   | Link l | Budget Analysis                                       | 92  |

|    | 5.2   | Desig  | n Constraints                                         | 93  |

|    | 5.3   | Recei  | ver Front-end Implementation Design                   | 96  |

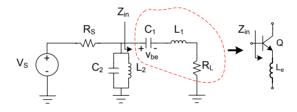

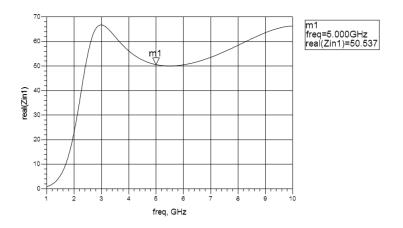

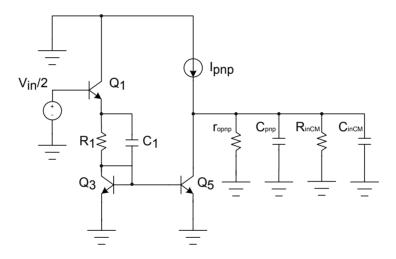

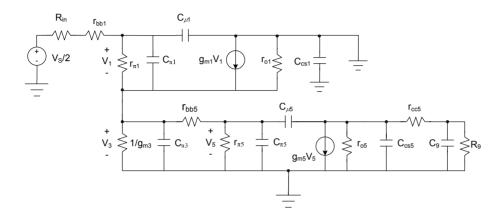

|    |       | 5.3.1  | UWB LNA Design                                        | 96  |

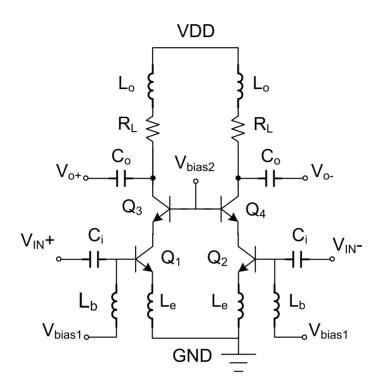

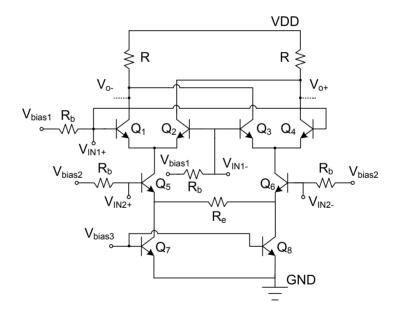

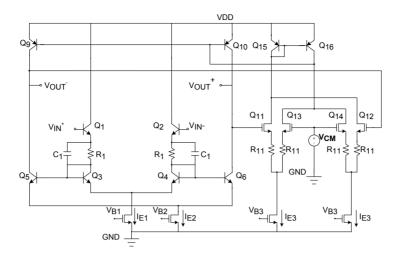

|    |       | 5.3.2  | Variable Gain Amplifier                               | 101 |

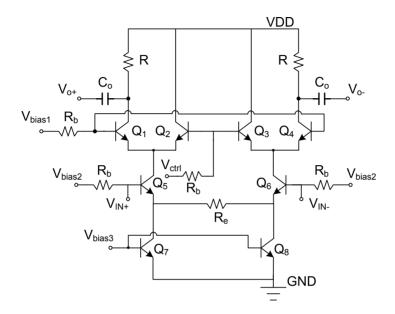

|    |       | 5.3.3  | Gilbert Cell                                          | 102 |

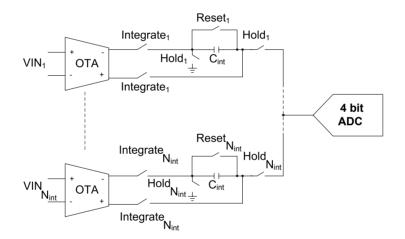

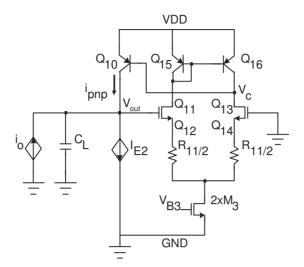

|    | 5.4   | Analo  | gue Baseband Receiver Design                          | 104 |

|    |       | 5.4.1  | Common Mode Feedback Analysis                         | 106 |

|    |       | 5.4.2  | OTA's Frequency Response Analysis                     | 108 |

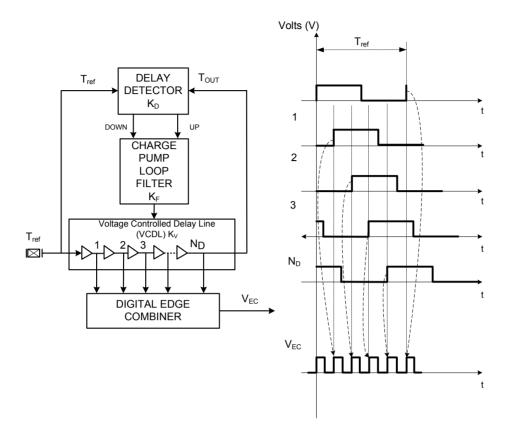

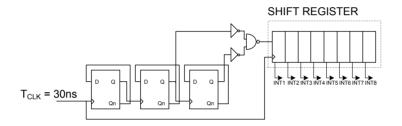

|    |       | 5.4.3  | Timing Circuits                                       | 111 |

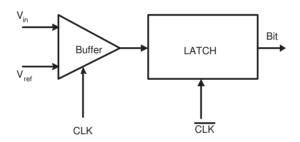

|    |       | 5.4.4  | ADC Architecture                                      | 112 |

|    | 5.5   | Digita | al Baseband Architecture Design                       | 114 |

|    | 5.6   | Simul  | ation and Measured Results                            | 115 |

|    |       | 5.6.1  | Digital Baseband FPGA Simulation Results              | 127 |

|    | 5.7   | Concl  | usions                                                | 128 |

| 6  | Cor   | clusio | ns and future work                                    | 131 |

|    | 6.1   | Concl  | usions                                                | 131 |

|    | 6.2   | Future | e Research Directions                                 | 133 |

| Bi | bliog | raphy  |                                                       | 136 |

| Aj | opene | dices  |                                                       | 149 |

### 1 Introduction

#### "The best way to predict the future is to invent it." -Alan Kay

Wireless communications have become a very important part of people's everyday life. The development of wireless technologies is already evident in the success of cellular telephony and wireless local area network (WLAN) applications. The integration of short range devices and networks, based on wireless standards within the IEEE802 suite, into the wireless wide-area infrastructure is far from trivial. Furthermore, new and increasingly challenging requirements constantly emerge from the user side: availability of high-rate data access, long battery life, location and tracking capabilities, and applications offering undisrupted service across different networks. As more and more devices go wireless, future wireless technologies will face spectral crowding and coexistence of wireless devices will be a major issue. Therefore, considering the limited bandwidth available, accommodating the demand for higher capacity and data rates is a challenging task, requiring innovative technologies that can coexist with devices operating at various frequency bands.

### 1.1 Background for UWB Communication

Ultra-Wideband (UWB) communication systems have the potential to provide solutions for many of today's challenges in the area of wireless communications and spectrum management. The approach employed by UWB communication systems is based on sharing spectrum already occupied by other wireless services, by using the overlay principle, rather than identifying still available new bands.

The main advantage of UWB technology can be perceived from Shannon's link capacity formula (97):

$$C = Blog_2(1 + SNR). \tag{1}$$

The link capacity is linearly proportional to the bandwidth and has a logarithmic relationship with the signal to noise ratio (SNR). Therefore, when the bandwidth is extremely large, only a very small signal power is needed to achieve high data rates. With its wide bandwidth, UWB has the potential to offer capacity much higher than the current narrowband systems for short-range applications.

Sensor networks are characterized by low complexity devices that have limitations

on memory and processing power, and restrictions on power consumption. Traffic in sensor networks is bursty with long periods of no activity. For the devices deployed, this has significant implications to the design of efficient medium access protocols, radio frequency technology and the reliability of information transfer (7).

In particular impulse-radio-based (IR) UWB communication systems have noise like-signals, are potentially low complexity and are resistant to severe multipath and jamming. UWB-IR signals have fine time domain resolution allowing for location and tracking applications (75). The low cost and low complexity of UWB-IR systems emerge from the baseband nature of the signal transmission. Unlike classical radio systems, the UWB-IR transmitter produces a very short time domain pulse without the need for an up-conversion mixing stage. The very wideband nature of the UWB signal means that it spans frequencies commonly used as carrier frequencies by existing wireless services. Also, the UWB-IR receiver does not require a down-conversion stage. This means that a local oscillator in the receiver can be omitted, which leads to removal of associated complex phase locked loop (7). As a result UWB-IR transceivers can be implemented in low cost complementary metal oxid-semiconductor (CMOS) or bipolar CMOS (BiCMOS) integrated circuit technologies (21), (73), (44).

The power consumption of UWB-IR devices can be reduced by integration, device scaling and low complexity transmitter and receiver architectures. The tradeoff between tighter variation of devices parameters and better yield, is one of the most important debates today between circuit designers and process engineers (90). From the signal processing viewpoint, the robustness of non-coherent receivers in multipath environments has been proven in open literature (85), (82), (98).

Low data rate UWB-IR is a good candidate for ad-hoc sensor network applications that utilize multi-hop data routing. Using multi-hop routing, UWB-IR transmitters could reduce their power emissions and thus also their coverage area allowing a large number of transmitters to operate simultaneously in the same given area, yielding increased spectral reuse and resulting in higher capacity per area. Thus, UWB based short range wireless communications provide high-spatial-capacity networks. Besides the ability to operate across bands occupied by existing narrowband systems, UWB radio systems offer flexibility in that they can maintain spatial capacity by adapting to either a large number of low-rate devices or a small number of high-rate devices, depending on the requirements of the application. It is not only the data throughput that benefits from the wide bandwidth, but also the ranging resolution of a communication system. The standard deviation of the timing resolution  $\sigma_t$ , which is inversely propor-

tional to that of bandwidth B, can be expressed as (112):

$$\sigma_t = \frac{1}{2B\sqrt{SNR}}.$$

(2)

The increase of bandwidth decreases the SNR necessary to achieve a certain resolution.

Due to the wide bandwidth of the transmitted signal, very high multipath resolution can be achieved. Impulse radio based UWB systems offer good LPI/LPD (low probability of interception/detection) properties which make it suitable for secure and military applications. UWB-IR is a natural choice for wireless sensor networks (WSN) with location and tracking due to the intrinsic properties of the signal, specifically short pulses supporting a high resolution of signal ranging estimation. Together with good through obstacle imaging, UWB signals offer opportunities for short range radar applications such as vehicular radar, collision avoidance, medical imaging, surveillance, mining, rescue and anti-crime operations. UWB-IR offers frequency diversity and suffers from severe multipath fading channel effects (7), (98).

Unintended detection of UWB signals is difficult due to the low energy density of the transmitted signal. There is evidence in the open literature that UWB-IR signal transmissions do not cause significant interference to existing radio systems if the distance between the victim receivers and UWB-IR transmitter is larger than few tens of centimetres (38), (40), (41). The results of the interference studies between UWB-IR transmitters and existing radio systems is the subject of heated debate between advocates and opponents of UWB.

#### 1.2 Historical Review of UWB Technology Development

UWB is seen as having potential for realizing exciting new applications that have not been fulfilled by other wireless short range technologies e.g., 802.11 local area networks (LANs) and Bluetooth personal area networks (PANs). Correspondingly, there has been a recent upsurge of interest in academic research into UWB as evidenced by (1), (2), (3) and an annual conference solely dedicated to UWB systems and technology (4). UWB-IR wireless communication systems utilize very short time domain pulses for transmission that result in a very wide spectrum signal. The use of UWB signals date back to the beginning of the last century with the spark-gap transmission experiments of Hertz (62). The era of spark-signals ended when the superiority of the continuous wave over spark signals was evident. The invention of Armstrong's regenerative receiver and sequently super-heterodyne receiver in 1917 effectively put a halt to spark gap communications (62).

The use of modern UWB technology started in the 1960's with a focus on development of impulse radars that used wideband signals primarily for extremely accurate localization and imaging in the context of secure communications. By the early 1970's, the basic components of UWB systems were already known, e.g., pulse generators and modulators, switching pulse train generators, detection receivers and ultra wideband antennas. The first systems which make use of the UWB technology were radars. In April 1973, Ross was granted the US Patent 3,728,632 which has been seen as the start for UWB communication systems (92). After the 1970's, the main innovations in the UWB field come from improvements of specific implementations of subsystems, but not in the system concept itself nor in the subsystems concepts (15). A summary of pulse generation methods in 1978 is presented in (17). After the 1970's, the emphasis was put on implementation of the known technology, and understanding the implications of transmitting short duration pulses on existing RF communication systems.

During the years from 1977 to 1989, the United States Air Forces (USAF) conducted a research program in UWB systems whose results were then used by the Defense Advanced Research Projects Agency (DARPA). The term UWB was applied in 1990 by the US Department of Defence. Some early work on UWB were conducted by Scholtz and his group in the early 1990s, focusing mainly on low-rate applications (95), (96), (129), (130). Recent developments in semiconductor manufacturing processes and narrow-band pulse generation has prompted new studies into UWB signal generation for different purposes: low speed, low cost, short range communications in support of a variety of multimedia transport applications in home and office environments.

Non-coherent UWB-IR receiver structures have lately been the focus of intense study. Auto-correlation (AC) receivers have been considered in (42), (25), (83), (117), (131). Transmitted-reference (TR) receivers have been considered in (42), (36). Energy detection receivers have been addressed in (85), (82), (106), (120), (94), (104).

US companies like Time Domain (74), Multispectral Solutions (32) and Alereon have presented various transmitter and receiver architectures enabling data communication and radar applications. Lately, companies from Europe and Japan, like Philips, STM and Sony have presented designs of IC UWB-IR transceivers (44), (101).

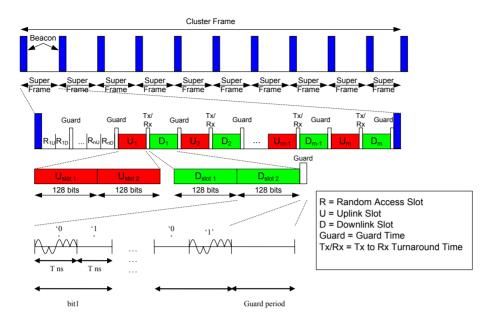

IEEE established two task groups to work on UWB physical layer (PHY) standardization: one responsible for the high data rate applications (IEEE802.15.3a) and one responsible for low data rate applications (IEEE802.15.4a). The main focus of the IEEE802.15.4a group is to define the PHY and medium access control (MAC) sublayer specifications for low data rate wireless connectivity with fixed, portable, and low mobility devices with low power consumption requirements typically operating in the personal area space of 10 m. The standardization activity of the IEEE802.15.4a group is currently ongoing and summaries and reports are available in (43).

The IEEE established the 802.15.3a High Rate Alternative PHY Task Group (TG3a) for Wireless Personal Area Networks (WPANs) to define a new PHY concept for short range, high data rate applications. Debate inside the IEEE 802.15.3a group raged over two competing PHY proposals: Direct-sequence UWB (DS-UWB) proposal employing short RF pulses for transmission; and Multiband Orthogonal Frequency Division Multiplexing (MB-OFDM) proposal that combines the multi-band approach (splitting the total available bandwidth into sub-bands) together with the OFDM techniques to achieve high-rate transmission.

The MB-OFDM proposal is supported by Intel and Texas Instruments and more than 80 companies (6). Companies which support the MB-OFDM technology have subsequently formed the WiMedia Alliance. The DS-UWB proposal was driven by Freescale and NICT (5). The major supporters of DS-UWB technology formed the UWB Forum. The solutions demonstrated by the Freescale platform ranged from wireless USB 2.0 over UWB, Bluetooth Wireless Technology over UWB, wireless DVI component video, 1394-over coax via UWB and UWB HDTV over electrical wire.

A split formed in early 2004, when WiMedia left the IEEE 802.15 Task Group 3a, after failing to gain the 75% vote needed to become the standard. Neither the DS-UWB or multi-band (MB)-OFDM alternatives received backing from the IEEE 802.15.3a. The IEEE802.15.3a group ceased to exist in January 2006 due to the failure to define an UWB PHY standard (50).

The Center for Wireless Communications (CWC) was strongly involved in the IEEE 802.15.4a standardization activities, and has proposed the energy detection transceiver architecture during this process.

### 1.3 Author's Contribution

The UWB-IR energy detection transceiver has been design to support research projects at CWC including that related to standardization activities, and to show that the concept of energy collection is feasible in practical environments. The main research area of the thesis covers low complexity, low data rate UWB impulse radio transceiver design from both a communication and circuit design viewpoint. At the time of writing, there was no other example of a complete implementation of a UWB-IR non-coherent ED transceiver. The study has been carried out by analysis and experimental methods. The analytical part is divided between simulations and theoretical calculations. Comprehensive circuit level simulations have been performed to determine the impact of different circuit sections on the performance of the UWB transceiver. Measurements of several blocks of the energy detection transceiver have been carried out. In addition, the performance from a wireless communication perspective of different UWB-IR transceivers have been simulated. It was determined that the low complexity energy detection receiver offers good performance compared to other coherent and non-coherent structures.

The author has been involved in the design of the transceiver circuit blocks by specifying its structure, designing circuits for the transceiver, defining the simulation and measurements setups and analyzing the results. In addition, the author was the main contributor to the journal and conference publications used as the original papers in this thesis.

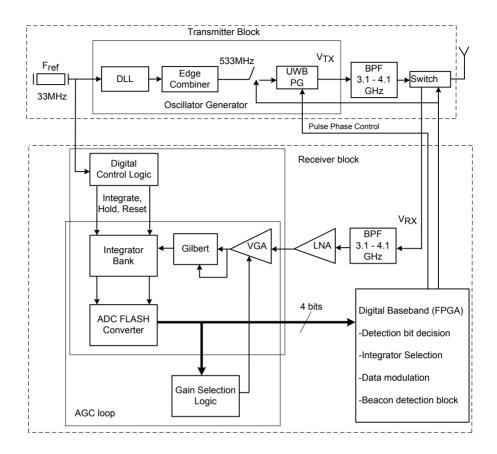

Papers (75), (102), (109), (84), (108), (107), (110), investigate the implementation of a time-hopping pulse position modulation design in a FPGA technology, the architecture of an UWB-IR non-coherent energy collection receiver for low data rate, low cost applications, the schematic block diagram of an improved UWB Gaussian pulse generator and the circuit details of the energy collection receiver. In paper (106), the architecture and performance of an UWB system architecture designed for low data rate, low-cost sensor networks applications was presented. In papers (105) and (103), the performance of time-of-arrival (TOA) position estimation techniques as well as the simulated and measured performances of an UWB-IR non-coherent energy collection receiver is shown. An overview of UWB-IR auto-correlation and energy detection receivers has been presented in paper (104).

### 1.4 Outline of the Thesis

The thesis is organized as follows: Chapter 2 presents a comprehensive literature review of related work on UWB pulse shapes and transmitter structures. Reviews of UWB-IR transmitters structures and circuit implementations are given in more detail. Chapter 2 provides the motivation for implementation of the Gaussian monocycle transmitter. Chapter 3 presents an overview of UWB-IR receivers structures. Reviews of UWB-IR receivers structures and circuit deigns are given in more detail. UWB-IR non-coherent

receiver structures, which are considered in more detail throughout the thesis, are also described. Chapter 3, which incorporates Paper (106), presents the performance of different UWB-IR non-coherent receivers from communication systems viewpoint. The theoretical performance versus implementation complexity challenges of UWB-IR receivers is presented. Chapter 3 provides the motivation for the implementation of the ED receiver. Chapter 4, which incorporates Papers (107) and (108), presents the design of an UWB-IR Gaussian pulse transmitter. The circuit implementation details are presented. Chapter 5, which is in part presented in Papers (84), (107) and (109), presents the design of several blocks of an UWB-IR non-coherent energy detection receiver. Chapter 6 concludes the thesis and the main results are summarized and discussed.

## 2 Overview of UWB Signals and Transmitter Structures

This chapter presents a literature review of different UWB-IR waveforms and transmitters architectures. The overview of the transmitters is presented from both a theoretical and implementation viewpoint. Section 2.1 gives the general introduction and a brief system description of a wireless communication system. Section 2.2 presents the UWB standardization efforts in the United States and Europe. Section 2.3 presents the FCC spectral limits for UWB-IR communication systems.

Section 2.4 shows various pulse shapes and their spectral properties. Sections 2.5 gives a performance overview of integrated and discrete UWB-IR transmitters. Section 2.6 presents the conclusions of Chapter 2.

### 2.1 Introduction

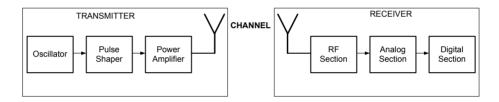

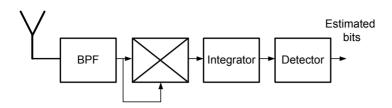

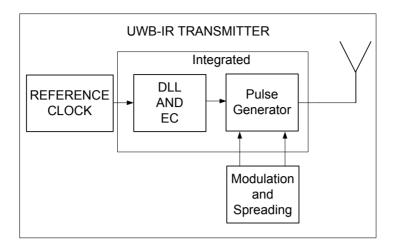

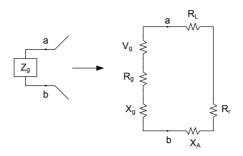

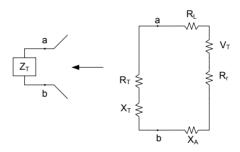

The diagram shown in Figure 1 illustrates the signal flow through a typical UWB-IR wireless communication system. This figure can serve as a guide through the chapters of this thesis. The transmitter section includes the oscillator, the pulse shaper, the power amplifier and the antenna. The oscillator represents the signal source for the pulse shaper. The pulse shaper generates the waveform to be used for communication. The pulse shaper may use either the signal at the oscillator's frequency or at a multiple of the oscillator's frequency. In the latter case, a frequency multiplier is used. The frequency multiplier may be integrated into the oscillator. The power amplifier amplifies the pulse shape to the desired transmit power level. The UWB antenna filters the transmitted signal. In some studies, the ideal UWB antenna behaviour is modelled as a differentiator, however other authors are not willing to accept this simplifications (86), (122).In (122), the authors show that the transmitted far field waveform is a scaled version of the voltage across the radiation resistor in the antenna model. The approach from (122), verifies that operating the antenna close to the first resonant frequency is still the optimal approach in terms of power match and nondispersive transmission. The receiver portion consists of an antenna, an RF section, an analogue section and a digital section. The receiver's antenna will again filter the incoming signal. The RF section consists of a bandpass filter (BPF), low noise amplifier (LNA), variable gain amplifier (VGA)

and squaring operation. The analogue section consists of all the analogue processing circuits, after the signal's down-conversion to baseband. The digital section consists of all the digital baseband algorithms, e.g., for data detection and synchronization.

Due to its overlaying nature, UWB systems share the existing spectrum with already defined radio systems. The main scope of regulatory masks is to define the dedicated bands where the UWB signals can coexist with the licensed wireless services in use. Therefore, the existing UWB spectral masks have a direct impact over the transmitted signals in UWB communication systems. Several pulse shapes which satisfy the FCC spectral masks, have been proposed in the literature (64), (99), (23). Among the waveforms presented, the Gaussian pulse and its derivatives, satisfies the FCC spectral mask while presenting a low implementation complexity. Since the central frequency of the Gaussian waveforms increases with the derivative order of the pulses, the allocated spectrum is used more efficiently.

Fig 1. Schematic Diagram of the UWB Communication System.

#### 2.2 UWB Standardization and Spectrum Regulation

UWB has the potential to offer new solutions to the problem of spectrum management, based on sharing the existing radio spectrum resources rather than looking for new bands. This idea was recently supported by the Federal Communications Commission (FCC) in the United States. The USA started the standardization of UWB in 1998 when the FCC released the "Notice of Inquiry" addressing possible use of UWB technology (28). The FCC radiation mask was released in February 2002 as "The First Report and Order" (RO). The RO allowed commercialization of UWB technology if the UWB radiation adheres to the spectrum mask.

According to (29), a signal was defined as being an UWB signal if its fractional

bandwidth,  $B_f$ , was greater than 0.25, where the definition of  $B_f$  is provided by (111):

$$B_f = 2\frac{f_h - f_l}{f_h + f_l},$$

(3)

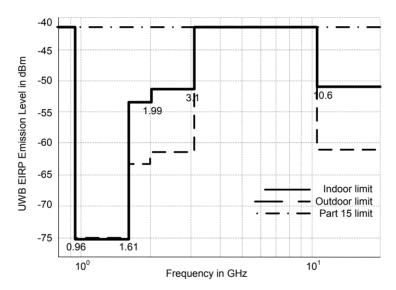

where  $f_h$  and  $f_l$  are the higher and lower -10 dB frequencies, respectively. A signal is also defined as being UWB if the -10 dB signal bandwidth is 500 MHz or larger (39). The frequency bands allowed for UWB operation are below 960 MHz, the 3.1 - 10.6 GHz band, and the 22 - 29 GHz band depending on the type of application. The existing FCC radiation limits for different indoor and outdoor UWB applications are presented in Figure 2. In Figure 2, the Part 15 limit was included as a reference, where Part 15 limit permits the operation of authorized low power radio frequency (RF) devices without a license from the Commission or the need for frequency coordination under general emissions limits (30).

Fig 2. FCC Indoor Mask and Part 15 limit.

The FCC indoor mask sets higher emission limits in the band 2 - 3.1 GHz and above 10.6 GHz. For outdoor emission, the maximum EIRP level in the 3.1 - 10.6 GHz band is set to -41.3 dBm/MHz and to -61.3 dBm/MHz above 10.6 GHz. For indoor emission, the maximum EIRP level in the 3.1 - 10.6 GHz band is set to -41.3 dBm/MHz and to -51.3 dBm/MHz above 10.6 GHz. All UWB devices must meet this spectral mask for

legal operation. References (29) and (30) describe the use of UWB technology in toys, aircraft and satellites or in fixed outdoor links.

In Europe, the European Commission Committee (ECC) has twice mandated the European Conference of Postal and Telecommunication Administration (CEPT) to harmonize all the UWB standardization activities within the EU area. The results of the first public inquiry were released in October 2004 (27). The UWB radiation limits are much more complex and sets much lower permitted power levels than the FCC's mask and so is far more difficult to meet for UWB-IR devices. In 2005, the ECC proposed in (27) a detection and avoidance mechanism (DAA) which should allow UWB devices to reduce their own transmit signal power if another signal is detected in the same frequency band. Radiation is allowed in the band 3.1 - 4.95 GHz if the activity factor is 5% or less over one second, or 0.5% over one hour. The use of the 4.1 - 4.8 GHz band is allowed until June 2010 since the upcoming fourth generation (4G) mobile cellular systems are expected to create additional demand on these frequency bands. The ECC is still waiting for comments from academia and industry to the draft report proposed in (27).

At the time of the writing (August 2007) UK, China and U.S are the only countries in the world which allow commercialization of license free UWB systems.

## 2.3 Transmitted Signal Requirements in UWB Communication Systems

The existing FCC mask regulation in the USA allows transmission of UWB signals below 960 MHz and within the 3.1 - 10.6 GHz band. The FCC indoor spectral mask sets the maximum EIRP level to -41.3 dBm/MHz in the 3.1 - 10.6 GHz band. EIRP is defined by the product of the available power of the transmitter  $P_{TX}$ , that is the maximum power that the transmitter can transfer to the transmitter antenna, and the gain off the transmitter's antenna  $G_{AT}$ .  $P_{TX}$  is an average power computed by averaging over the bit interval  $T_b$ , as shown in (16):

$$P_{av} = \frac{N_s E_p}{T_b} = \frac{E_p}{T_s},\tag{4}$$

where  $E_p$  is the energy of a single pulse,  $N_s E_p$  is the total energy of  $N_s$  the pulses representing one bit. Equation 4 shows that different pulse waveforms may have the same average power with big difference in pulse energy, depending on the number of pulses per bit. For equal waveform duration, the maximum instantaneous power may be signif-

icantly different among waveforms with similar average power. Utilization of the entire spectrum assigned by the FCC requires transmitter and receiver circuits with very fast frequency response, increasing the implementation complexity and decreasing the communication range due to the increasingly lossy nature of high frequency bands. When only a fraction of the bandwidth is used, the narrow band interference (NBI) suppression is improved. Pulse shaping is crucial since it affects the PSD of the transmitted signal. The transmitted spectrum can be shaped by changing the pulse waveform. The spectrum may be shaped by pulse width variation, pulse derivation, and combination of base functions. Among the most common waveforms are the pulses based on the baseband Gaussian pulses since their spectral properties satisfy the indoor FCC mask.

The spectral utilization efficiency of Gaussian pulses can be measured in terms of the normalized effective signal power (NESP) (7), (64), which is the ratio of the power transmitted in the designated passband of the spectral mask over the total power that is permissible under the given mask. The higher the derivative order of the Gaussian pulses, the higher the number of zero crossing in the same pulse width, acting as if a higher "carrier" frequency sinusoid is modulated by an equivalent Gaussian envelope. Therefore, as the order of the derivative increases, the allocated spectrum is used more efficiently. In section 2.4, we present different pulse shapes which adhere to the indoor FCC mask.

#### 2.4 UWB Pulses

A suitable pulse waveform can be any function which satisfies the spectral mask limitations. Among the most common pulse shapes are the Gaussian, Rayleigh and monocycle waveforms. The Gaussian waveform is given by equation (5) (74). The nominal centre frequency and the bandwidth of the Gaussian pulse depends on the pulse's width in time.

$$p_{G_0}(t) = \frac{1}{\sigma\sqrt{2\pi}} exp(\frac{-t^2}{2\sigma^2}).$$

(5)

By differentiating  $p_{G_0}(t)$  against *t*, the Gaussian pulse derivatives can be obtained. The  $n^{th}$  derivative is given by:

$$p_{G_n}(t) = \frac{d^n}{dt^n} p_{G_0}(t).$$

(6)

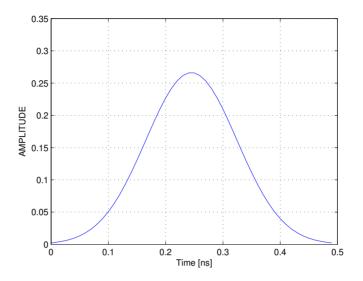

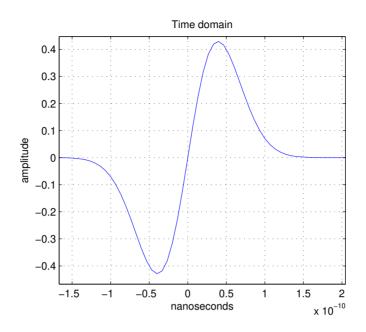

The Gaussian pulse with a pulse duration of 0.5 ns is presented in Figure 3.

Fig 3. Gaussian Pulse with a 0.5 ns Pulse Duration.

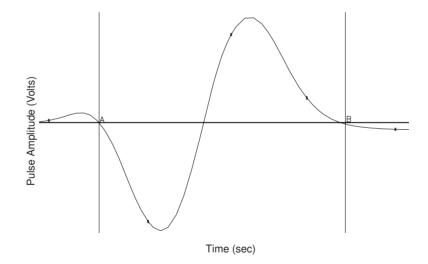

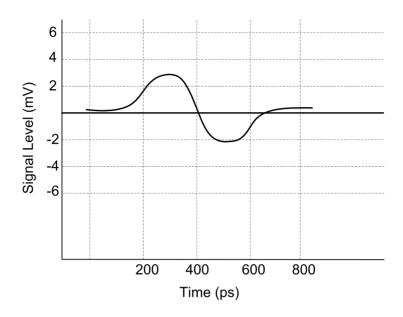

The theoretical formulation of the first derivative of the Gaussian pulse, namely the Gaussian monocycle, is presented as:

$$p_{G_1}(t) = -\frac{te^{-\frac{t^2}{2\sigma^2}}}{\sqrt{2\pi\sigma^3}}.$$

(7)

The nominal centre frequency and the bandwidth of the first derivative of the Gaussian pulse, known also as the Gaussian monocycle, depends on the monocycle width in time. The -3 dB bandwidth is approximately 116% of the monocycle's centre frequency  $f_c$  (113). The ideal Gaussian monocycle has a single zero crossing in the time domain. The spectrum decays with increasing frequency, but does not ever reach DC implying an infinite spectrum signal and therefore an finite time domain signal. From an implementation viewpoint, infinite duration pulses cannot be used. The pulse width or duration of the pulse can be defined as:

$$T_p = \sqrt{2\pi\sigma},\tag{8}$$

where  $\sigma$  is the variance of the Gaussian distribution. Outside the interval  $(-T_p/2, T_p/2)$ , the pulse must be nulled for practical implementation purposes.

The Fourier transform is calculated in order to obtain the spectrum of the impulses used in UWB transmissions. In Table 1, the first and second UWB Gaussian derivatives and their frequency spectrum are presented.

Table 1. UWB Gaussian Derivatives.

| Theoretical formula                                                                                                    | Frequency spectrum                                   | Central frequency            |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------|

| $p_{G_1}(t) = -\frac{te^{-\frac{t^2}{2\sigma^2}}}{\sqrt{2\pi\sigma^3}}$                                                | $P_{G_1}(f) = 2j\pi f e^{-2(\pi\sigma f)^2}$         | $f_0 = \frac{1}{T_p}$        |

| $p_{G_2}(t) = -\frac{1 - \frac{t^2}{\sigma^2}}{\sqrt{2\pi\sigma^3}} e^{-\frac{t^2}{2\sigma^2}}$                        | $P_{G_2}(f) = -4(j\pi f)^2 e^{-2(\pi\sigma f)^2}$    | $f_0 = \frac{\sqrt{2}}{T_p}$ |

| $p_{G_3}(t) = \frac{3 - \frac{t^3}{\sigma^2}}{\sqrt{2\pi\sigma^5}} e^{-\frac{t^2}{2\sigma^2}}$                         | $P_{G_3}(f) = -8j(\pi f)^3 f e^{-2(\pi \sigma f)^2}$ | $f_0 = \frac{\sqrt{3}}{T_p}$ |

| $p_{G_4}(t) = \frac{3 - 3\frac{t^2}{\sigma^2} + \frac{t^4}{\sigma^4}}{\sqrt{2\pi\sigma^5}} e^{-\frac{t^2}{2\sigma^2}}$ | $P_{G_4}(f) = 16(\pi f)^4 e^{-2(\pi\sigma f)^2}$     | $f_0 = \frac{2}{T_p}$        |

| $p_{G_5}(t) = \frac{\frac{15-10}{\sigma^2} + \frac{t^5}{\sigma^4}}{\sqrt{2\pi\sigma^7}} e^{-\frac{t^2}{2\sigma^2}}$    | $P_{G_5}(f)=32j(\pi f)^5e^{-2(\pi\sigma f)^2}$       | $f_0 = \frac{\sqrt{5}}{T_p}$ |

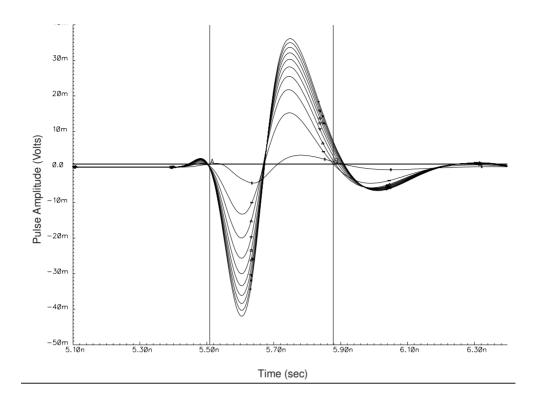

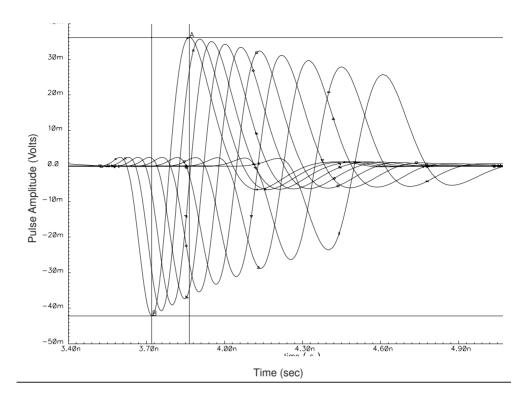

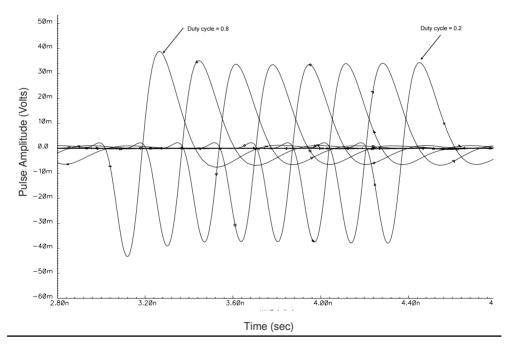

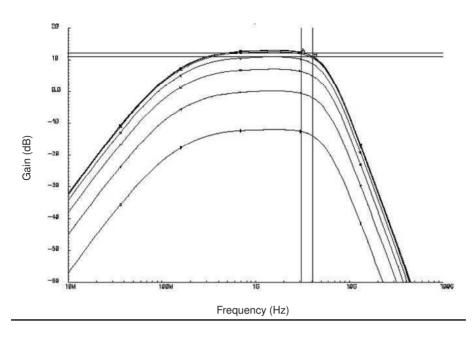

The higher order derivatives of the Gaussian pulse are presented in Figure 4.

Fig 4. PSD of the First, Second, Third, Fourth and Fifth Derivatives of the Gaussian Pulse with a Time Duration of 0.5 ns.

Scholtz's monocycle was proposed by Scholtz and his group in the early 1990s (95), (96), (130). The Scholtz's monocycle is given by (95):

$$p_{Scholtz}(t) = \left[1 - 4\pi \left(\frac{t}{\tau}\right)^2\right] e^{-2\pi \left(\frac{t}{\tau}\right)^2},\tag{9}$$

where  $\tau$  will adjust the pulse width. Comparing with the second derivative of the Gaussian pulse, Scholtz monocycle has the advantage that  $\tau$  parameter can adjust the pulse width.

Time Domain Corporation was one of the first commercial enterprises to employ Gaussian pulses and their derivatives in practical systems. The UWB pulse waveform proposed by Time Domain Corporation is given by (74):

$$p_{TD}(t) = 6A \sqrt{\frac{e\pi}{3}} \frac{t}{T_p} exp(-6\pi \frac{t}{\tau_p})^2,$$

(10)

where *A* is the pulse amplitude, *e* is Neper's constant and  $\tau_p$  is the pulse duration. The choice of this pulse waveform is given by the fact that antenna behaves approximately as a differentiator. The electromagnetic radiation of the antenna can occur if the transmitted pulse has a zero DC component. If  $\sigma$  is chosen to be small enough, the second derivative of the pulse which is presented as in equation (11) does not present sidelobes of the power density spectrum:

$$p_{TD_2}(t) = \frac{1 - \frac{t^2}{\sigma^2}}{\sigma^2 \sqrt{2\pi}} exp(\frac{t^2}{2\sigma^2}).$$

(11)

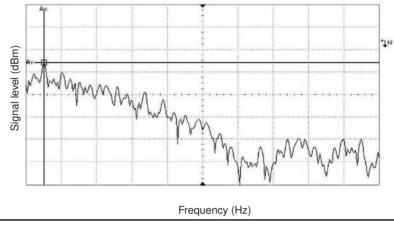

Power spectral measurements based on the Time Domain pulse generator have been presented in (14). Based on a measurement setup according to ITU-R Task Group 1/8, Geneva 2005, the measured PSD level was -50.1 dBm/MHz which is below the FCC mask value of -41.3 dBm/MHz while the -10 dB bandwidth was 3800 MHz.

A further evolution of Gaussian pulses was developed by Aether Wire of the US. The formula of the pulse used by Aether Wire is given by (74):

$$p_{ae}(t) = \frac{1}{\sigma\sqrt{2\pi}} exp(\frac{-(t-\mu)^2}{2\sigma^2}) - \frac{1}{\sigma\sqrt{2\pi}} exp(\frac{-((t-\tau_a)-\mu)^2}{2\sigma^2}),$$

(12)

where  $\tau_a$  is the time separation between the Gaussian pulses within a doublet. The pulse is a Gaussian doublet composed of two Gauassian pulses with variable time separation between them. One drawback of using a time separation is restricting the use in highspeed data communication systems because of the longer total bi-pulse width. The time separation can be used to generate nulls in the signal spectrum. Therefore, the transmitted spectrum can be shaped by modifying the time separation.

Orthogonal pulse shapers which meet the FCC spectral mask were recently proposed in (77). The orthogonal pulses presented in (77), are obtained by numerically evaluating the discretization of the convolution function between the filter response and its input signal. Converting the digital designs into analogue form uses digital-toanalogue operations at a rate of 64 GHz which is extremely expensive to implement with existing processes. An optimum pulse design methodology, where it was shown that pulse design problem is equivalent to a finite impulse response (FIR) filter was presented in (64). The pulses designed with the algorithm presented in (64) meet the FCC regulations, optimally exploit the allowable bandwidth and power, and are more resistant to narrowband interference than the Gaussian monocycle. The downside of the method is that the 28 GHz clock rate needed for implementation is too high to be implemented with existing digital processes.

In (39), the authors evaluate the level of interference caused by the following radio systems: GSM900, UMTS/WCDMA and GPS on different UWB signals, as well as the performance degradation of UWB-IR systems in the presence of narrowband interference and pulsed jamming. In (39), the authors stated that by decreasing the pulse width or increasing the order of the derivative of the radiated waveform, the UWB spectrum moves to the higher frequencies and eventually out of the range of the interfering frequency, giving a larger jamming margin against GSM interference in both TH-UWB and the DS-UWB systems. The interference experienced by UWB will depend on the proper selection of the UWB pulse waveform and width.

When measured in the presence of an interfering and jamming radio system, the UWB-IR system performance suffers most if the interference and the nominal center frequency of the pulse are overlapping. If the UWB-IR system is low rate and long pulses can be used, lower order derivatives offer better performance (39).

A new monocycle based on the fifth derivative derivative of the Gaussian pulse and which satisfies the FCC spectral limits, has been proposed in (99). In this paper it is stated that in order to maintain a bandwidth as wide as possible, the fifth-order derivative should be used for indoor systems and the seventh order for outdoor systems. A comparison in terms of spectrum characteristics, bit error rate (BER) performance in an AWGN channel and multiple access BER performance in an AWGN channel, between Gaussian pulse, Scholtz's monocycle and Gaussian monocycle has been presented in (23). In this paper, the authors report that Gaussian pulse and rectangle monocycle have DC components which reduces the antenna efficiency. Scholtz's monocycle and Gaussian monocycle have wider 3 dB bandwidth than sinus and RZ-Manchester pulses. Single link BER performance in AWGN channel shows that performances of Scholtz's and Gaussian monocycle are better than those of Gaussian and rectangle monocycle. In (137), several conclusions about UWB-IR system dependence on Gaussian monocycles are provided. Firstly, higher order monocycles give lower synchronization error variance, pulses generated from a higher order derivative imply higher SNR gain in single user and asynchronous multiple access channel but inferior interference resistance ability. Secondly, pulses with smaller time length imply higher SNR gain in asynchronous multiple access channel conditions, but inferior interference resistance ability.

If additional derivatives of the Gaussian pulse are taken, the relative bandwidth decreases, and the centre frequency increases for a fixed time delay constant  $T_p$  as shown in Figure 4. The higher the order of Gaussian pulse derivatives used, the higher the implementation complexity of the circuits required to implement the pulse shaper. This is because more analogue or digital circuit stages are required to synthesize the pulse shape.

#### 2.5 Review of UWB-IR Transmitters

The pulse generator in Figure 1 has the role of transmitting low power pulses starting from a low frequency reference clock generator. The main difference between UWB-IR transmitters and narrowband transmitters is the lack of the up-conversion stage and the digital-to-analogue converter (DAC) used to centre the transmitted pulse at the desired carrier frequency. This leads to a reduced complexity architecture of the UWB-IR transmitters and to a lower power consumption.

A fifth-order derivative Gaussian pulse generator implemented using the AMISemiconductor 0.5  $\mu$ m CMOS process, has been proposed in (53). The pulse width is 2.4 ns with corresponding bandwidth of approximately 416 MHz and the average power consumption is 1.159 mW with a pulse repetition frequency of 20 MHz. A design of the Scholtz (130) monocycle pulse shape implemented in Taiwan Semiconductor Manufacturing Company (TSMC) 0.18  $\mu$ m CMOS technology, has been published in (55). In this paper, the authors proposed a quadrant squarer circuit based on a vertical bipolar transistor available using a standard CMOS process, for implementation of the analogue circuit of the approximated Gaussian pulse. The approximated Scholtz monocycle is obtained by differentiating the output current and voltage by using an inductor and a capacitor, respectively. A pulse generator implemented in TSMC 0.18  $\mu$ m CMOS process for a closer approximation to the FCC spectral mask has been proposed in (51). The power consumption of the pulse generator presented in (51) is 0.4 mW for a 100 MHz pulse repetition frequency with a 1.8 V power supply level.

An UWB-IR pulse generator design for a 0.35  $\mu$ m CMOS process for TH-PPM UWB systems was reported in (118). The length of the monocycle is approximately 520 ps while the bandwidth is approximately 1.9 GHz. In this paper, the pulse repetition interval may be determined by the timing circuit presented in (102).

A programmable pulse modulator working in the 3.1 - 5 GHz band with a  $\pi/2$ -shift BPSK modulation scheme, fabricated in 0.18  $\mu$ m CMOS process has been presented in (44). In this paper, the authors used a four-bit barrel shifter to control a set of variable gain amplifiers which in turn modulate a 4 GHz clock in a cycle-to-cycle fashion with programmed gain values. Due to the large number of components and high toggling rates of the flip-flops, the designed presented in (44) has a power consumption of 105 mW. The power consumption of the pulse modulator reported in (44) is relatively high so would be unsuitable for low power applications.

A single chip impulse radio transmitter with all-digital-controlled pulse generator designed in 0.18  $\mu$ m, which supports BPSK modulation, has been presented in (71). The power consumption of the UWB-IR transmitter presented in (71) is 29.7 mW from a 2.2 V power supply. A single chip CMOS pulse generator designed for a 0.13  $\mu$ m process, which supports PPM and BPSK modulations and the third, fourth and fifth order derivatives of the Gaussian pulse, has been presented in (100). The power consumption of the pulse generator presented in (100) is 5 mA from a voltage supply of 1.2 V.

An UWB transmitter using a system-on-package (SOP) 0.35  $\mu$ m CMOS impulse generator together with an UWB bandpass filter (BPF) and a compact planar UWB antenna have been presented in (60). The output impulse amplitude is 650 mV, and the pulse duration and bandwidth are approximately 2 ns and 500 MHz respectively. The results presented in (60), emphasize the suitability of SOP technology for the miniaturization of UWB-IR transmitters.

An alternative BiCMOS pulse generator based on the idea described in (51) has been published in (138). An integrated pulse generator for both bi-phase and pulse-position modulations (PPM), designed in 0.18  $\mu$ m SiGe BiCMOS technology was presented in (8). The power consumption of that chip was estimated at 270 mW with a 2.7 V supply. A low power re-programmable pulse generator together with a power saving scheme, designed in TSMC 0.18 $\mu$ m CMOS technology, for both IR and MBOA UWB systems have been presented in (66). The main drawback of the pulse generator presented in (66) is the required off-chip RF choke and the need to design a fast clock generator to set the pulse repetition frequency. Also, the value of the delay elements is fixed at the time of designing and is dependent on the load. We believe that a variable delay value is most suitable for the pulse generator because a pulse with adjustable time duration can be generated. A 0.18  $\mu$ m SiGe BiCMOS pulse generator which generates a Gaussian monocycle, which consumes only 30 mW with a 1.8 V supply, was reported in (9). A co-design of the impulse generator presented in (9) together with a pulse-position modulator and a butterfly antenna, has been presented in (10). The current consumption of the full UWB-IR transmitter presented in (10) is 14.4 mA at 1.8 V supply.

A carrier based UWB-IR manufactured in a digital 0.18  $\mu$ m CMOS process has been presented in (93). In this paper, the authors used a frequency up-conversion technique where a triangular pulse is multiplied with an RF carrier frequency to suppress the signal power below 3.1 GHz to satisfy FCC requirements.

A Gaussian monocycle pulse generator designed in 0.18  $\mu$ m CMOS process has been presented in (119). The pulse generator consumes 2.7 mW and the pulse width is approximately 0.6 ns. A digitally controllable bi-phase CMOS UWB-IR pulse generator has been presented in (54). The pulse generator presented in this paper has been designed in AMISemiconductor 0.5  $\mu$ m CMOS technology and the total power consumption is 1.88 mW with a 1.8 V supply voltage. The resulting waveform shows substantial ringing while the transmitted pulse repetition frequency is 77 MHz.

A Gaussian monocycle pulse generator designed using a 0.18  $\mu$ m CMOS process has been presented in (139). In this paper, the pulse width is 800 ps, the -10 dB bandwidth is 2 GHz, the maximum transmission rate is 50 Mbps, while the power consumption is 7 mA. An interesting concept, where the frequency response of the antenna is used to shape the UWB waveform, which eliminates the need for pulse generator, is proposed in (115).

In Table 2, a comparison of previous presented integrated UWB-IR transmitters is shown.

| Process                 | Pulse Shape, Width                   | Consumption [mW]            | Reference |

|-------------------------|--------------------------------------|-----------------------------|-----------|

| 0.5 $\mu$ m AMI CMOS    | 5 <sup>th</sup> -derivative @ 2.4 ns | 1.159@3.3 V                 | (53)      |

| 0.18 $\mu m$ TSMC CMOS  | Scholtz @ 3 ns                       | <sup>a</sup> @ 3.3 V        | (55)      |

| 0.18 $\mu m$ TSMC CMOS  | <sup>b</sup> @ 500 ps                | 10.4@1.8 V                  | (138)     |

| 0.18 $\mu$ m BiCMOS     | с                                    | 270@ 2.7 V                  | (8)       |

| 0.18 $\mu m$ TSMC CMOS  | Monocycle                            | 8.47μW <sup>d</sup> @ 1.8 V | (66)      |

| 0.18 $\mu m$ IBM BiCMOS | Monocycle @ 250 ps                   | 30 @ 1.8 V                  | (10)      |

| 0.5 $\mu$ m AMI CMOS    | 3rd-order @ 420 ps                   | 1.88 @ 1.8 V                | (54)      |

| 0.18 $\mu$ m CMOS       | Doublet @ <sup>e</sup>               | 2.5 @ 2.5 V                 | (115)     |

| 0.18 $\mu$ m CSM CMOS   | Monocycle @ 800 ps                   | 12.6 @ 1.8 V                | (139)     |

| $0.35~\mu m$ AMS CMOS   | Monocycle @ 350 ps                   | 20.48 <sup>f</sup> @ 3.3 V  | (106)     |

Table 2. Comparison of Integrated UWB-IR Transmitters in CMOS and BiCMOS processes.

ulikilowil

<sup>b</sup>unknown

<sup>c</sup>unknown

<sup>d</sup> with power saving schemes

<sup>e</sup>unknown

<sup>f</sup>with 533MHz frequency synthesis circuits included

The most important part of the UWB-IR transmitter is the pulse generator.

Early techniques for the generation of short-pulse RF waveforms utilized the rapid rise or fall times of a baseband pulse to excite a wide-band antenna. A recent overview of short-pulse communications systems and short-pulse radar systems is presented in (32). In this paper, the authors stated that the physical properties of wide-band antennas determined the frequency and bandwidth characteristics of the resulting UWB pulses.

Some of the most commonly used components in discrete UWB-IR transceiver implementation are transistors operated in avalanche mode, tunnel diodes and step recovery diodes (SRD). Transistors operated in avalanche mode were one of the first techniques used as a source of UWB pulses due to their fast rise time (112), (15). In (32), the authors proposed a combination of conventional heterodyne and gated power-amplifier design. Time-gated oscillators are relatively easy to implement, used mostly for transmitter testing and prototyping for testing basic properties of the transmitted spectrum. The conventional heterodyne transmitters make use of a classic up-converter stage. The gated power-amplifier uses a digitally controllable power-amplifier for controlling the transmitted power spectrum and for reducing the power consumption. Among all discrete components, the fastest transition time of 25 ps is offered by the tunnel diode. SRDs have been used in high voltage, low repetition rates pulse generators (61). More details on semiconductor properties of tunnel diodes and other microwave discrete components can be found in (63).

Recently, time-gated oscillators and low-level impulse sources with time-gated power amplification for prime power minimization techniques have been used for generation of short-pulse waveforms based on discrete implementations (26).

# 2.6 Conclusions

This Chapter has presented a review of previous work over UWB-IR transmitters and the global UWB standardization efforts.

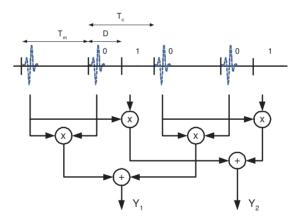

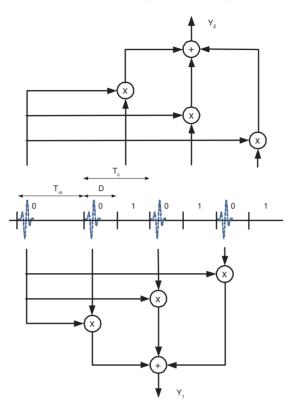

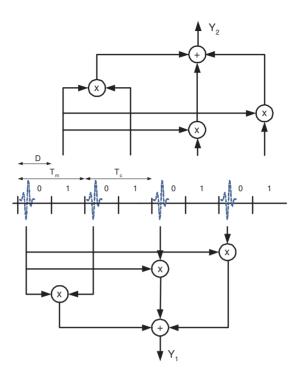

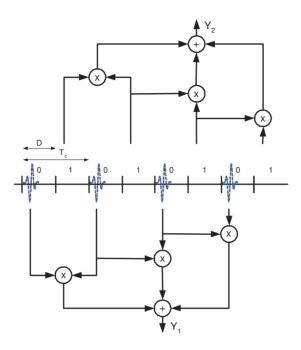

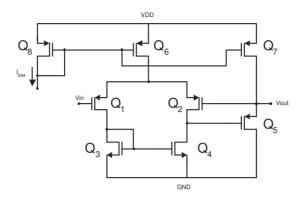

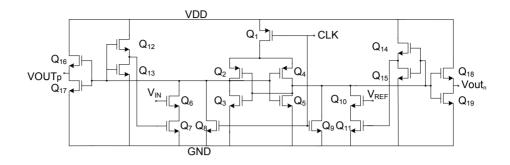

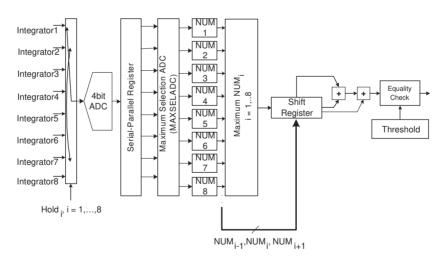

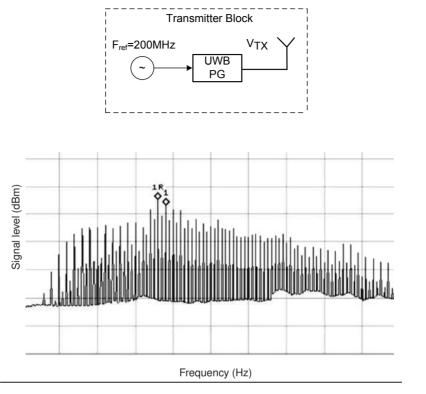

The UWB standardization activities in Europe and Japan are currently in progress. UK, China and United States are the only countries in the world which allowes commercialization of license free UWB systems.