Open access • Proceedings Article • DOI:10.1109/IFEEC.2017.7992148

### Novel efficiency-Optimal Frequency Modulation for high power density DC/AC converter systems — Source link ☑

Dominik Neumayr, Dominik Bortis, E. Hatipoglu, Johann W. Kolar ...+1 more authors

Institutions: ETH Zurich, Infineon Technologies

Published on: 01 Jan 2017 - IEEE International Future Energy Electronics Conference and ECCE Asia

Topics: AC/AC converter, Pulse-frequency modulation, Pulse-width modulation, Frequency modulation and Inductor

### Related papers:

- · Constant Frequency ZVS PWM Converter

- · Variable Switching Frequency PWM for Three-Phase Four-Wire Split-Capacitor Inverter Performance Enhancement

- Modulation Method to Reduce Losses in Inverters with LC-Filters

- A three-phase resonant PWM DC-DC converter

- · Current Ripple Prediction and DPWM Based Variable Switching Frequency Control for Full ZVS Range Two Parallel Interleaved Three-Phase Inverters

# Novel Efficiency-Optimal Frequency Modulation for High Power Density DC/AC Converter Systems

### **Conference Paper**

### Author(s):

Neumayr, Dominik; Bortis, Dominik (ii); Hatipoglu, Enes; Kolar, Johann W.; Deboy, Gerald

### **Publication date:**

2017

#### Permanent link:

https://doi.org/10.3929/ethz-b-000187517

### Rights / license:

In Copyright - Non-Commercial Use Permitted

### Originally published in:

https://doi.org/10.1109/IFEEC.2017.7992148

## Novel Efficiency-Optimal Frequency Modulation for High Power Density DC/AC Converter Systems

D. Neumayr, D. Bortis, E. Hatipoglu and J. W. Kolar Power Electronic Systems Laboratory, ETH Zurich, Switzerland Email: neumayr@lem.ee.ethz.ch G. Deboy

Infineon Technologies Austria AG,

Villach, Austria

Email: Gerald.Deboy@infineon.com

Abstract-State-of-the-art high power density AC/DC and DC/AC converter systems typically employ Triangular Current Mode (TCM) modulation or conventional PWM. TCM is characterized by a wide variation of switching frequency over the mains period and ensures soft-switching in all operating points, but results in increased conduction and high-frequency losses due to the necessary large current ripple. In contrast, PWM with constant switching frequency features a lower RMS current and thus reduced conduction losses, but cannot achieve softswitching over the entire mains period and suffers from turn-on losses. In this paper it is investigated if an optimal combination of these two operating modes, i. e. an optimal adjustment of switching frequency and/or current ripple amplitude throughout the mains period, can lead to an increase in conversion efficiency and how such an Optimal Frequency Modulation (OFM) control scheme can be implemented in practice. The presented analysis is based on an ultra compact 2kW, 400V DC/AC converter system designed to overcome the GOOGLE Little Box Challenge.

Index Terms—Optimal Frequency Modulation, Efficiency Optimal Switching Frequency, Optimal Current Ripple Modulation, Minimum Loss Control

### I. INTRODUCTION

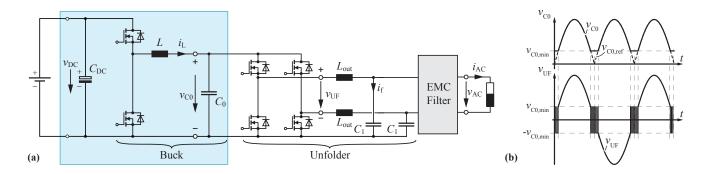

In kW-scale high power density AC/DC and DC/AC converter systems, typically a high switching frequency is selected in order to ensure a small size of the passive components [1]. As a consequence, Zero Voltage Switching (ZVS) of the power semiconductors over the entire mains period is desired to reduce switching losses and keep the conversion efficiency high and the volume of the cooling system small. Following this design philosophy, and with the insights gained from Pareto optimization results, a  $8.2 \,\mathrm{kW/dm^3} (134 \,\mathrm{W/in^3})$  single-phase Triangular Current Mode (TCM) PV inverter was realized in [2] to overcome the GOOGLE Little Box Challenge (GLBC) [3]. Further research conducted in the aftermath of the GLBC revealed that by means of an alternative inverter topology based on a DC/|AC| buck-stage with subsequent |AC|/AC unfolder (cf. Fig. 1) the power density of the 2 kW PV inverter can be further improved. The buck-stage, highlighted in light blue in Fig. 1, is operated either with TCM modulation or conventional PWM with large current ripple, and is controlled such that the output voltage  $v_{\rm C0}$  follows a rectified sinusoidal shape. In order to deal with reactive loads and retain full controllability of the inductor current,  $v_{\rm C0}$  is actually kept above a defined voltage  $v_{\rm C0,min}$  around the Zero Crossings

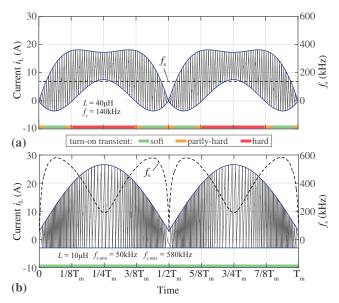

(ZC) of the mains voltage as indicated in Fig. 1 (b). During this interval, the |AC|/AC unfolder initiates PWM operation in order to ensure a sinusoidal shape of  $v_{\rm ac}$  at the converter output. The Pareto optimization presented in [2] identified that if the buck-stage is operated with PWM at EMI friendly 140 kHz and a 50 µH inductor is installed, a staggering power density of  $14.7 \,\mathrm{kW/dm^3}$  ( $241 \,\mathrm{W/in^3}$ ) at  $98.1 \,\%$  efficiency can be expected. Interestingly, TCM operation of the buckstage with a 10 µH inductor results in a slightly lower power density  $(14.0 \,\mathrm{kW/dm^3})$ . The resulting inductor current  $i_\mathrm{L}$ and switching frequency variation over a mains period for the PWM and TCM design of the buck-stage are shown in Fig. 2 (a) and (b) for a 2 kW ohmic load. As it becomes evident from Fig. 2 (a), PWM features lower conduction and winding losses due to the comparably small current ripple and thus lower RMS value of the inductor current. However, a hard turn-on of the high-side transistor over a wide range of the mains period results in high switching losses. Regarding efficiency it might be beneficial to lower  $f_{\rm s}$  between  $^{1}/_{8}T_{\rm m}$ and  $3/8T_{\rm m}$  in order to increase the current ripple and extend the region where ZVS applies. On the contrary, operation of the buck-stage with TCM modulation as shown in Fig. 2 (b) enables ZVS in all operating points throughout mains period, but the large current ripple significantly increases conduction and winding losses. In this case, it might be beneficial, in terms of overall efficiency, to limit the drop of  $f_s$  around the peak of the mains voltage (at  $^1/_4T_{

m m}$  and  $^3/_4T_{

m m}$ ) in order to decrease the current ripple despite ZVS is intermittently lost. Accordingly, the question arises, whether the benefits of TCM and PWM can be combined, if the switching frequency variation is considered as an additional degree of freedom to effectively minimize the power loss in the inverter at every instant in time over the course of the mains period. In [4] an optimal switching frequency for a full-bridge inverter was derived analytically by means of a sophisticated timedomain current ripple analysis. However, solely power losses in the transistors due to hard switching were considered in the optimization. The authors in [5] also included the power loss of the inductor in the analytical optimization. However, again, only hard-switching operation of the power transistors was considered. The optimal variable switching frequency for a 3-phase GaN based TCM inverter was derived in [6] based on approximate loss models of the involved power transistor

Fig. 1. (a) Inverter topology based on a DC/|AC| buck stage and a subsequent |AC|/AC| full-bridge unfolder. (b) Buck stage output voltage and unfolder output voltage showing intermediate PWM operation around the zero-crossing of the mains.

Fig. 2. Inductor current  $i_{\rm L}$  and the variation of switching frequency  $f_s$  throughout a mains period  $T_{\rm m}$  obtained for the Pareto optimal TCM and PWM DC/|AC| buck stage when operated at rated power, respectively.

and magnetic components. However, since ZVS operation was enforced in all operating points, the optimal trade-off between power transistor and filter component losses has not been completely investigated.

In this paper the optimal switching frequency variation is determined empirically by means of experimental hardware rather than based on mathematical loss models and simulations. Since it promises highest power density, the buck-unfolder inverter design with PWM operation of the buck stage presented in [2] will be the basis for the study presented in the following. In particular, the optimal switching frequency of the buck stage (cf. Fig. 1 (a)) in order to achieve loss minimal operation at every instant in time over the mains period is determined. Power losses in the remaining converter components, for instance conduction losses in the unfolder and losses in the subsequent EMC filter are assumed to be unaffected by the switching frequency of the buck stage and are therefore excluded from further consideration. The reader should be aware that EMI compliance imposes a stringent

side condition which restricts the feasible range of switching frequency variation and/or requires a reevaluation of the EMC filter afterwards which possibly leads to a decrease in power density of the overall inverter. However, the EMC filter of the buck-unfolder inverter, considered herein, is dimensioned such to provide enough attenuation to handle the intermediate High Frequency (HF) switching of  $v_{\rm C0,min}$  of the unfolder (cf. Fig. 1 (b)) and therefore provides enough margin to accommodate for a wide range of switching frequency variation in the DC/|AC| buck stage.

The loss minimization procedure based on switching frequency variation in quasi-stationary DC/DC operating points is outlined in Section II of this paper. The employed experimental test setup of the buck converter is introduced afterwards in Section III. The empirically obtained optimal switching frequency and the resulting inductor current envelope as a function of the point in time  $t_{\rm k}$  and/or angle considered within a main period  $T_{\rm m}$  are presented and discussed in Section IV. Finally, two control approaches to implement Optimal Frequency Modulation (OFM) in practice are briefly introduced in Section V.

### II. QUASI-STATIONARY DC/DC ANALYSIS

Since the buck-stage output voltage  $v_{\rm C0}$  changes very slowly throughout  $T_{\rm m}$  with respect to the actual switching period  $T_{\rm s}=^{1}/f_{\rm s}$ , the DC/|AC| operation of the buck converter can be approximated by a large number of consecutive, quasi-stationary DC/DC operating points defined by the DC-link voltage, the buck stage output-voltage

$$v_{\rm C0} \approx \max(v_{\rm C0,min}, |v_{\rm AC}(t_{\rm k})|),\tag{1}$$

and the average inductor current

$$\overline{i_L} = \operatorname{sgn}(v_{AC}(t_k)) \cdot (i_{AC}(t_k) + i_f(t_k)) \tag{2}$$

$$\approx \operatorname{sgn}(v_{\mathrm{AC}}(t_{\mathrm{k}})) \cdot i_{\mathrm{AC}}(t_{\mathrm{k}})$$

(3)

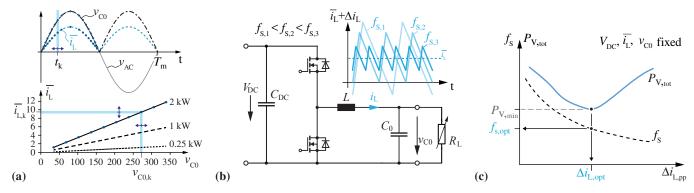

at distinct points  $t_{\rm k}$  over the mains period. Due to symmetry, it suffices to consider only the interval  $\varphi=\omega t=[0,\pi/2]$  of the mains. In this paper, only operating points resulting from a purely ohmic  $0.25\,{\rm kW}$ ,  $1.0\,{\rm kW}$  and  $2.0\,{\rm kW}$  load are considered as illustrated in Fig. 3 (a). Furthermore, the reactive current demand of the EMC filter is neglected. In a

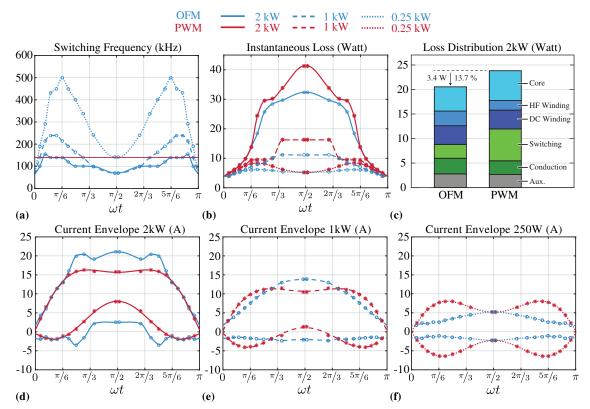

Fig. 3. Determining the switching frequency / current ripple which minimizes the total power loss of the DC/|AC| buck stage in a quasi-stationary DC/DC operating point. (a) Derived DC/DC operating points  $V_{DC}$ ,  $v_{C0,k}$  and  $\overline{i_{L,k}}$  for ohmic load at several distinct points  $t_k$  throughout the mains period  $T_m$ . (b) Resulting current ripple amplitude for switching frequency variation in a specific DC/DC operating point. (c) Variation of the switching frequency in order to determine the loss minimum in a given DC/DC operating point.

stationary operating point, the switching frequency of the buck stage can be varied which results in different current ripple amplitudes in the filter inductor L as illustrated in Fig. 3 (b). The switching frequency  $f_{\rm s,opt}$  and current ripple amplitude  $\Delta i_{\rm L,opt}$  which minimizes the total power loss in the buck stage in the selected DC/DC operating point is considered optimal as shown in Fig. 3 (c). After repeating the measurement and/or optimization procedure for all defined DC/DC operating points, the individual  $f_{\rm s,opt}$  points are joined and interpolated in order to obtain the optimal switching frequency variation over the course of the mains period.

The quasi-stationary DC/DC approach implicates the following approximations. The dielectric loss in the filter capacitor  $C_0$  due to the rectified sinusoidal voltage swing of  $v_{c0}$  is not covered by the quasi-stationary DC/DC approach. However, these losses are in a first approximation not affected by the switching frequency and can thus be treated as additional constant power loss. The winding losses in the inductor caused by the low-order spectral components in  $\overline{i_L}$  are also not correctly covered, since the losses are caused solely by the DC winding resistance,  $R_{\rm w,DC}$ , in the respective DC/DC operating point. Since the amplitude of the harmonics of  $\overline{i_L}$  drops with  $1/n^2$  and the frequency dependent winding resistance  $R_{\rm w,AC}(n \cdot f_{\rm m})$  is approximately constant up to several kHz, the resulting error is less than 1% as a numeric calculation revealed. Furthermore, harmonic sidebands, present in the current spectrum due the modulation of the rectified sinusoidal variation of the dutycycle during regular operation, are missing in case of the quasi-stationary analysis even if a large number of DC/DC operating points is considered because the duty-cycle is kept constant during the measurements and the spectral energy is located solely at multiples of the switching frequency. However, since the considered switching frequency range is much higher compared to the low-frequency harmonics in the baseband, the additional sidebands do not noticeably affect the losses. Moreover, the operating temperature of the power electronic components during the individual measurements of the quasi-stationary analysis (kept between  $35\,^{\circ}\mathrm{C}$  –  $45\,^{\circ}\mathrm{C}$  in every considered operating point) likely differs from the device temperature resulting from regular operation of the buck stage

Fig. 4. (a) Picture of the experimental test setup showing the implemented buck converter (GaN half-bridge with externally connected inductor) with cooling fans and measurement probes. The employed DC source, electronic load and power analyzer are not shown.

(max. 65 °C according to [3]).

### III. EXPERIMENTAL SETUP

The half-bridge circuit of the buck converter (cf. Fig. 1) is realized with normally-off gallium nitride gate (GaN) injection transistors (CoolGaN Samples from Infineon) in combination with a novel high-performance gate drive circuit, where two GaN transistors are connected in parallel per switch. The employed 50 µH HF inductor is realized with 27 turns (3 layers with each 9 turns) of  $180\times71\,\mu\mathrm{m}$  litz wire on a RM10 N87 ferrite core. The DC-link capacitor  $C_{\rm DC} \approx 10 \, \mu {\rm F}$ is realized with individual 2 µF/650 V CeraLink capacitors featuring exceptional low ESR at high frequencies and elevated operating temperatures. It should be noted that  $C_{\rm DC}$ is dimensioned to filter switching frequency noise and not to cope with the double-mains frequency power pulsation intrinsic to single-phase systems. The buck stage filter capacitor  $C_0 \approx 20 \,\mu\text{F}$  is composed of 12 parallel connected 2.2 μF/450 V X6S MLCCs. As mentioned in the introduction, the system parameters of the buck stage are in accordance with

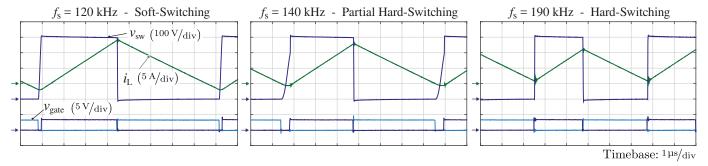

Fig. 5. Measured switch-node voltage  $v_{\rm sw}$ , inductor current  $i_{\rm L}$  and gate voltages in the DC/DC operating point  $V_{\rm DC}=400\,{\rm V},\,v_{\rm C0}=170\,{\rm V},\,\overline{i_{\rm L}}=5.9\,{\rm A}$  obtained with  $120\,{\rm kHz},\,140\,{\rm kHz}$  and  $190\,{\rm kHz}$  switching frequency.

the Pareto optimal buck-unfolder inverter design presented in [2]. The experimental test setup including cooling fans and attached measurement probes is depicted in Fig. 4. The dutycycle of the half-bridge and an electronic load (Chroma 63202) are adjusted to meet the correct output voltage and output power (average inductor current) in every DC/DC operating point. Depending on the specific operating point and selected switching frequency, the rising- and falling-edge dead-time of the half-bridge,  $t_{\rm d,r}, t_{\rm d,f} \in [20\,{\rm ns}, 400\,{\rm ns}]$ , are adapted such to ensure a complete resonant transition of the drain-source voltage and, in addition, minimize the conduction time of the anti-parallel diode. In case that  $i_{\rm L}$  remains strictly positive and hard-switching occurs, the rising-edge dead-time is set to the minimum value. The average power loss of the buck converter in every DC/DC operating point is measured with a Yokogawa WT3000 power analyzer. Auxiliary power for the digital control card and the gate drives are also included in the total power losses. Once the operating point of the buck converter is set, the total power loss at steady-state operation is recorded for several switching frequencies until a distinct loss-minimum can be identified. Fig. 5 shows experimental waveforms of the buck converter operating at  $V_{\rm DC} = 400 \, \rm V$ ,  $v_{\rm C0} = 170 \, \rm V$ ,  $\overline{i_{\rm L}} = 5.9 \, {\rm A}$  and switching frequencies of  $120 \, {\rm kHz}$ ,  $140 \, {\rm kHz}$ and 190 kHz. It can be seen how the triangular ripple, and consequently the RMS value, of the inductor current reduces with increasing switching frequency. The depicted switch-node voltage  $v_{\mathrm{sw}}$  reveals that the power-stage experiences complete soft-switching when operated with 120 kHz. If  $f_s$  is increased to 140 kHz, the slightly negative value of  $i_L$  at the start of the low- to high-side switching transition does not suffice to achieve a complete resonant transition of the the switch-node voltage for  $t_{\rm d,r} = 400 \, \rm ns$  and partial hard-switching occurs. Operating the buck converter with 190 kHz results in a hard turn-on of the high-side transistor since  $i_{\rm L}$  remains above zero due to the reduced amplitude of the triangular ripple. In the DC/DC operating point examined in Fig. 5, the optimal loss trade-off between power transistors and filter components is attained with  $f_s = 140 \, \text{kHz}$ .

### IV. EMPIRICALLY DETERMINED OPTIMAL SWITCHING FREQUENCY

Following the quasi-stationary approach, the loss-minimal switching frequency,  $f_{s,opt}$ , was determined at 10 distinct

TABLE I

FREQUENCY VARIATION AND LOSS SAVING OF OFM FOR DIFFERENT

OUTPUT POWER LEVELS

| Pout (W) | $f_{ m s,OFM}$ | $P_{\rm v}$ (W)     | $P_{\rm v}$ (W) | $\Delta P_{\rm v}$ (W / %) |

|----------|----------------|---------------------|-----------------|----------------------------|

|          | (kHz)          | $@~140\mathrm{kHz}$ | $@f_{s,OFM}$    |                            |

| 2000     | [70, 149]      | 24.0                | 20.6            | 3.4 / 13.7                 |

| 1000     | [70, 243]      | 10.8                | 8.4             | 2.4 / 22.0                 |

| 250      | [140, 500]     | 6.5                 | 5.5             | 1.0 / 15.7                 |

DC/DC operating points within the interval  $[0, \pi/2]$  of the mains period for an average output power of 250 W, 1 kW and 2 kW. The experimental results with interpolation between the discrete measured points are shown in Fig. 6. It should be noted that for a clearer visual representation, the measured points were mirrored at  $\pi/2$  to complement the interval  $[0,\pi]$ . The switching frequency variation and instantaneous power loss in the buck converter when operated with a fixed switching frequency of 140 kHz (plotted in red) and with varying optimal switching frequency (plotted in sky-blue) are shown in Fig. 6 (a) and (b), respectively. The corresponding envelope of the inductor current is displayed in Fig. 6 (d)-(f) for the three measured output power levels. At 2kW rated power,  $f_{\rm s,OFM} = f_{\rm s,opt}(\varphi)$  falls below 140 kHz over a wide range of the considered phase angle. Saturation of the power inductor limits the switching frequency to fall below  $70\,\mathrm{kHz}$  at  $\omega t = \pi/2$ . Observing the current ripple envelope of both PWM and OFM in Fig. 6 (d), it can be inferred that OFM tends to extend the interval where soft-switching applies despite the increased RMS value of the inductor current. As listed in Tab. I, the total losses in the buck converter decrease by roughly 14% when operating with a variable switching frequency  $f_{s,OFM}$  instead of  $f_{s,PWM} = 140 \, \text{kHz}$ . The loss distribution in Fig. 6 (c), calculated with experimentally verified mathematical loss model of the GaN transistors and power inductor, indicates that OFM significantly reduces the switching and core losses while it slightly increases the conduction and HF winding losses due to the larger current ripple. At half the nominal output power i.e. 1 kW, the optimal frequency curve exceeds  $f_{s,PWM}$  in the vicinity of  $\pi/6$  reaching a peak of 243 kHz. Similar as before, the optimal frequency drops below 140 kHz in the interval  $[\pi/3, 2\pi/3]$  and reaches the lowest value of  $70\,\mathrm{kHz}$  at  $\pi/2$ . At  $1\,\mathrm{kW}$  output power,  $22\,\%$

Fig. 6. Experimental results obtained with the test hardware depicted in Fig. 4 showing the optimal switching frequency  $f_{s,\mathrm{OFM}} = f_{s,\mathrm{opt}}(\varphi)$  in (a), the total instantaneous power loss in the buck converter in (b), and the resulting envelope of the current ripple in (d)-(f) over the interval  $\varphi \in [0,\pi]$  for  $2\,\mathrm{kW}$  (solid lines),  $1\,\mathrm{kW}$  (dashed lines) and  $0.25\,\mathrm{kW}$  (dotted lines) ohmic load. The distribution of power loss between the individual components of the buck converter at  $2\,\mathrm{kW}$  output power is shown in (c) for both OFM and  $140\,\mathrm{kHz}$  PWM.

of losses can be saved when the converter is operated with  $f_{\rm s,OFM}$  (cf. Tab. I). At 250 W part-load operation,  $f_{\rm s,OFM}$  exceeds 140 kHz almost over the entire interval, attaining a peak of 500 kHz at  $\omega t = \pi/6$  where  $v_{\rm C0} = V_{\rm DC}/2$ . As listed in Tab. I, nearly 16% of the total power loss can be saved when operating the buck stage with OFM at 250 W output power.

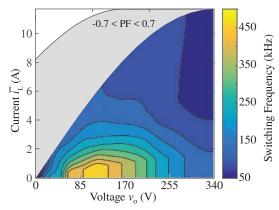

### V. DIGITAL CONTROL IMPLEMENTATION OF OFM

The empirically determined optimal switching frequency,  $f_{\rm s,OFM}$ , and/or optimal current envelope,  $\Delta i_{\rm L,OFM}$ , is stored in form of a 3-dimensional Look-Up Table (LUT) in a fast, microcontroller accessible memory in order to provide the data to the digital controller. Every sample in the set defined by all feasible operating points,  $\{V_{\rm DC}, v_{\rm C0}, \overline{i_{\rm L}}\}$ , defines a single entry of  $f_{\rm s,OFM}/\Delta i_{\rm L,OFM}$  in the LUT. Taking the actual value of  $V_{\rm DC}$  into consideration allows to adapt for a possible double line-frequency variation and/or output power dependent sag of the DC-link voltage. However, for the sake of simplicity, the DC-link voltage is fixed to 400 V in this paper as already mentioned in the previous section which reduces the LUT to two dimensions. A graphical representation of the 2dim  $f_{\rm s,OFM}$ -LUT obtained from interpolation of the measured data at  $0.25\,\mathrm{kW},\,1.0\,\mathrm{kW}$  and  $2\,\mathrm{kW}$  (cf. Fig. 6) is illustrated by means of a contour plot in Fig. 7. Since  $f_{s,OFM}$  was determined only for ohmic load, the combination of  $\overline{i_L}$  and  $v_{\rm C0}$  which would occur for a non-unity Power Factor ( -0.7 <PF < 0.7, [3]), is indicated by means of the grey-shaded

Fig. 7. Contour plot representation of the look-up table obtained from two-dimensional interpolation of the empirically determined  $f_{\rm s,OFM}$  (cf. Fig. 6) as a function of  $\overline{i_{\rm L}}$  and  $v_{\rm C0}$ .

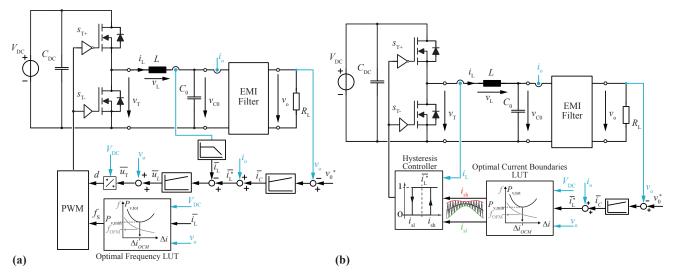

area. The envisioned digital control implementation of OFM is depicted in Fig. 8 (a) and follows a similar control structure as employed in classical PWM control. For the sake of clarity, the unfolder (cf. Fig. 1) and additional cascaded control loops to regulate voltages and currents in the EMI filter are omitted in this discussion. A more detailed description can be found in [7]. Moreover, it is assumed that the EMI filter does not affect the low-frequency harmonics in the buck stage output voltage, hence  $v_{\rm C0} \approx v_{\rm o}$ . The outer voltage and inner current control loop determine the modulation index d such that on

Fig. 8. Control implementation of OFM by means of conventional PWM with adjustable switching frequency in (a) where the optimal switching frequency is stored in a Look-Up Table (LUT), and by means of a hysteresis controller in (b) where the optimal upper and lower current boundary are accessed from a pre-computed LUT.

average over a switching period  $\overline{v_{\mathrm{T}}}$  is applied by the powerstage. In contrast to classical PWM, the carrier frequency is not fixed but permanently updated from the stored LUT for the measured operating point  $\{V_{dc}, v_o, \overline{i_L}\}$ . The carrier frequency can be kept for a specified number of switching cycles before a new value is assigned to the PWM modulator from the LUT. Since the PWM frequency varies over time, the control law is executed asynchronously with defined frequency. Another option is to store the optimal envelope i.e. upper and lower boundary of the inductor current as shown in Fig. 6 (d)-(f) in the LUT instead of  $f_{

m s,OFM}$  and use a hysteresis regulator to control the power-stage such that the inductor current remains inside the boundaries. This control strategy, herein termed Optimal Current amplitude Modulation (OCM), is outlined in Fig. 8 (b). For highest performance, the hysteresis controller can be implemented with analog comparator circuits where the switching thresholds are continuously adjusted by means of digital-to-analog conversion of the LUT values provided by the microcontroller. This approach allows to tightly control  $i_{\rm L}$ , but demands a current sensor with very high bandwidth.

#### VI. CONCLUSION

It has been shown that by combining the benefits of two well known and accepted switch-mode power converter modulation techniques, namely Triangular Current Mode (TCM) and Pulse Width Modulation (PWM), the overall conversion efficiency of a single-phase DC/AC converter can be improved. The presented novel operating mode, herein named Optimal Frequency Modulation (OFM), is characterized by a continuous adjustment of the actual switching frequency over the course of the mains period in order to minimize the converter power loss. Being relieved from the remaining inaccuracy and uncertainty of mathematical loss models, an experimental approach to determine the optimal switching frequency,  $f_{\rm s,OFM}$ , was presented. A quasi-stationary DC/DC approach was applied to the buck stage of a Pareto optimal  $2\,{\rm kW}$ , single-phase DC/AC

converter design comprising a DC/|AC| buck stage and a |AC|/AC unfolder. The total power loss can be reduced by 13.7% at  $2\,\mathrm{kW}$  output power when operated with  $f_\mathrm{s,OFM}$ . The potential loss saving increases to remarkable 22% at half the rated power and reduces just slightly to 16% at  $250\,\mathrm{W}$ . Finally, two practical look-up table based control implementations of the proposed operating mode, PWM with updated carrier frequency and current hysteresis control with variable hysteresis width were presented. Naturally, the OFM approach presented herein can also directly be applied to single-phase PFC rectifier and DC/DC converter systems.

### REFERENCES

- [1] M. C. Chen, C. Y. Yang, C. Y. Chou, J. L. Chen, J. Y. Lin, Y. C. Hsieh, H. J. Chiu, and C. M. Young, "High Power Density and High Efficiency Inverter with Ripple Decoupler Circuit," in *Proc. of the 8th IEEE Intern. Power Electron. and Motion Control Conf. (IPEMC-ECCE Asia)*, 2016.

- [2] D. Bortis, D. Neumayr, and J. W. Kolar, "ηρ -Pareto Optimization and Comparative Evaluation of Inverter Concepts considered for the Google Little Box Challenge," in Proc. of the 17th IEEE Workshop on Control Model. Power Electron. (COMPEL), 2016.

- [3] GOOGLE, "Detailed Inverter Specifications, Testing Procedure, and Technical Approach and Testing Application Requirements for the Little Box Challenge," Google, Tech. Rep., 2015. [Online]. Available: https://www.littleboxchallenge.com

- [4] X. Mao, R. Ayyanar, and H. K. Krishnamurthy, "Optimal Variable Switching Frequency Scheme for Reducing Switching Loss in Single-Phase Inverters Based on Time-Domain Ripple Analysis," *IEEE Transactions on Power Electronics*, vol. 24, no. 4, pp. 991–1001, 2009.

- [5] Y. Xia and R. Ayyanar, "Optimal Variable Switching Frequency Scheme to Reduce Combined Switching Loss and Inductor Core Loss of Single Phase Grid Connected Inverter," in *Proc. of the IEEE Energy Convers.* Congr. Expo. (ECCE), 2015.

- [6] M. Kaufmann, A. Tüysüz, and J. W. Kolar, "New Optimum Modulation of Three-Phase ZVS Triangular Current Mode GaN Inverter Ensuring Limited Switching Frequency Variation," in *Proc. of the IET Int. Conf.* on Power Electron., Machines and Drives (PEMD), 2016.

- [7] D. Bortis, J. Kolar, F. Krismer, Y. Lobsiger, and D. Neumayr, "Verfahren und Vorrichtung zur Steuerung eines Einphasen DC/AC-Konverters," Patent Application CH 01 139/15, 2015.