# Novel RF process monitoring test structure for silicon devices

Sia, Choon Beng; Ong, Beng Hwee; Lim, Kok Meng; Yeo, Kiat Seng; Do, Manh Anh; Ma, Jianguo; Alam, Tariq

2005

Sia, C. B., Ong, B. H., Lim, K. M., Yeo, K. S., Do, M. A., Ma, J. G., et al. (2005). Novel RF process monitoring test structure for silicon devices. IEEE Transactions on Semiconductor Manufacturing, 18(2), 246-253.

### https://hdl.handle.net/10356/84919

## https://doi.org/10.1109/TSM.2005.845095

IEEE Transactions on Semiconductor Manufacturing © 2005 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder. http://www.ieee.org/portal/site.

Downloaded on 26 Aug 2022 03:15:10 SGT

## Novel RF Process Monitoring Test Structure for Silicon Devices

Choon Beng Sia, Beng Hwee Ong, Kok Meng Lim, Kiat Seng Yeo, Manh Anh Do, Jian-Guo Ma, Senior Member, IEEE, and Tariq Alam

Abstract—This paper demonstrates a novel RFCMOS process monitoring test structure. Outstanding agreement in dc and radio frequency (RF) characteristics has been observed between conventional test structure and the new process monitoring test structure for MOSFET with good correlations in measured capacitances also noted for metal-insulator-metal capacitor and MOS varactor. Possible process monitoring test structure is also suggested as a reference benchmarking indicator for interconnects.

*Index Terms*—MIM capacitor, MOS varactor and interconnect, process monitoring, RFCMOS, scribe line.

#### I. INTRODUCTION

C EMICONDUCTOR foundries of today grant fabless integrated circuit design companies not only easy access to advanced silicon processing technologies but also provide reliable production capacity of high-yield wafer manufacturing. With the ever-growing interests of exploiting the mature and cost-effective silicon technology for radio frequency (RF) integrated circuit (IC) designs, limitations of the mixed-signal/RFCMOS processes must be carefully characterized and well understood by yield, device modeling, as well as circuit design engineers [1], [2]. Very often, because of circuit design sensitivities to process variations, a designer's product may still encounter setbacks even though production wafers are within the specification limits of the technology. Such sensitivities are detrimental and can manifest as yield loss, early life reliability failures or even shifts in circuit operating frequency, affecting the overall business performance of these circuit design companies.

Most foundries do not normally provide extensive information on electrical specifications, performance boundaries and process variations of the RF devices offered in the process design kits. Hence, the development of new RF process monitoring test structures to characterize these process variations and correlating them to the circuit performances become extremely important. Close partnerships between circuit design companies and foundries benefit both parties, making one-pass design success and high-yield RFCMOS process possible. Process monitoring test structures will help identify critical RF device performance indicators that are sensitive to the circuits, subsequently establishing them as important RF electrical specifications for that particular process. Reliable test structures and knowledge of critical parameters to monitor, allow RF performance distribution across the process to be accurately incorporated into device corner models. With these models, circuit designers can take preventive measures prior to circuit fabrication if the process variations are found to have adverse effects during circuit simulations.

#### II. TEST STRUCTURES, RESULTS AND DISCUSSIONS

In this paper, novel layout designs for RF process monitoring test structures are proposed. Silicon devices are characterized to investigate and verify the functionality for this new design. Conventional device test structures are usually layout in the east-west configuration, allowing calibrated RF probes to touch down on the two sets of ground-signal-ground (GSG) pads. Such layout schemes are very popular and widely adopted for RF device characterization as well as device model development.

To monitor a process, scribe line test structures residing between adjacent dies on the wafer have to be designed such that the overall width of the whole test structure typically do not exceed more than 80–100  $\mu$ m wide. This imposes limitations in designing scribe line RF test structures because it is believed that calibration of the test instrument and cables up to the probe tips for test pads in the nonconventional layout style, involves technical expertise and experience to obtain reliable measured S-parameters. In this paper, new test structure layout approach together with Cascade Microtech's Infinity probes [3] that allow devices to be tested with smaller pad geometries, demonstrate reliable and repeatable on-wafer RF scribe line device measurements on MOSFET, metal-insulator-metal (MIM) capacitor, and MOS varactor.

#### A. MOSFET

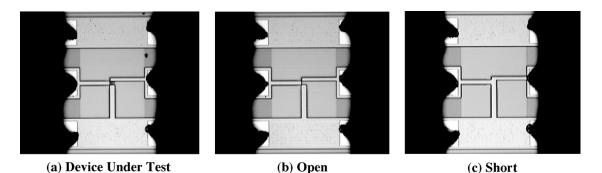

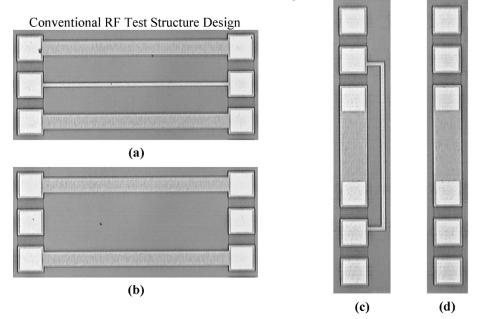

RF nMOSFET with channel width (W) and length (L) ratio of W/L = 24/0.18  $\mu$ m (6 Fingers) layout using both the conventional and scribe line designs are fabricated in the current 0.18  $\mu$ m RFCMOS processing technology. Fig. 1 shows the die photos of the conventional RF test structures, with the device under test, its corresponding open and short de-embedding calibration structures. In Fig. 1(a), the gate (Port 1) of the NMOS is on the west side, the drain (Port 2) is on the east side. The source and bulk of the transistor are connected together and tied to the RF ground pads. Fig. 2, on the other hand, consolidates die photos of the RF process monitoring test structures with new

Manuscript received July 9, 2004; revised January 4, 2005.

C. B. Sia and K. M. Lim are with the Advanced RFIC (S) Pte. Ltd., Singapore 609930 (e-mail: cb.sia@arfic.com).

B. H. Ong, K. S. Yeo, M. A. Do, and J. G. Ma are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798.

T. Alam is with the Cascade Microtech, Inc., Beaverton, OR 97006 USA. Digital Object Identifier 10.1109/TSM.2005.845095

Fig. 1. (a) Die photos showing the conventional GSG RFCMOS test structures (CON) with cascade microtech infinity probes for (a) a 6-finger RF NMOS, (b) its open and (c) short de-embedding structures.

Fig. 2. Die photos showing the proposed Scribe Line Process Monitoring test structure (SLM) with and without infinity probes for (a) a 6-finger RF NMOS (a), its open (b) and (c) short de-embedding structures.

scribe line layout scheme having GSG pads in the north-south configuration.

Characterization experiments to compare the performances of this device in the two designs help verify if the new scribe line design function unfailingly. First part of the experiment evaluates the dc characteristics of the transistors using kelvin force/sense measurements available in Agilent 4156C semiconductor parameter analyzer. High-frequency on-wafer S-parameter measurements are subsequently carried out using Agilent 8510C Vector Network Analyzer [4] and Cascade Microtech Infinity probes. The wafer and RF probes are shielded within the Microchamber of the S300 Semi-automated Probe Station during the test and measurements. Two-port S-parameters of the transistors are extracted over the frequency range from 50 MHz to 20.05 GHz. Two-step de-embedding technique, both open and short, are performed to accurately remove the parasitics of the test frame [5]. To facilitate the de-embedding process, both open pad and short calibration structures are fabricated next to the devices.

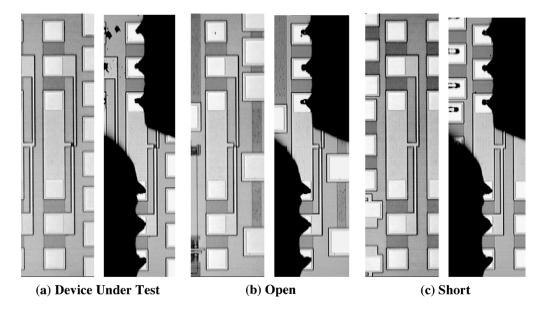

Comparing the dc characteristics of the two test structure designs in Fig. 3(a) and (b), there are no significant differences in drain current, transconductance and the output resistance at various terminal biases. Moving on to the RF performance comparison, for gate bias sweep from 0.5 to 1.8 V in steps of 0.1 V and at constant drain bias of 1.8 V, Fig. 3(c)–(f) consolidates the 2-Port characteristics of the NMOS transistor. Both test structure designs produce similar input and output match characteristics. Fig. 3(e) and (f) shows no significant differences in gain-frequency response between the two designs with only small deviations of about 3.5% and -2% in S21 magnitude and phase, respectively, for most of the gate biases. The extracted unity-gain cutoff frequency,  $F_T$ , for both designs are also in good agreement with a deviation of no more than  $\pm 1.5\%$ . Studies on PMOSFETs and transistors of other sizes, together with impacts of de-embedding technique on the correlations of the two test structure designs have been investigated and reported in [6].

#### B. Metal-Insulator-Metal (MIM) Capacitor

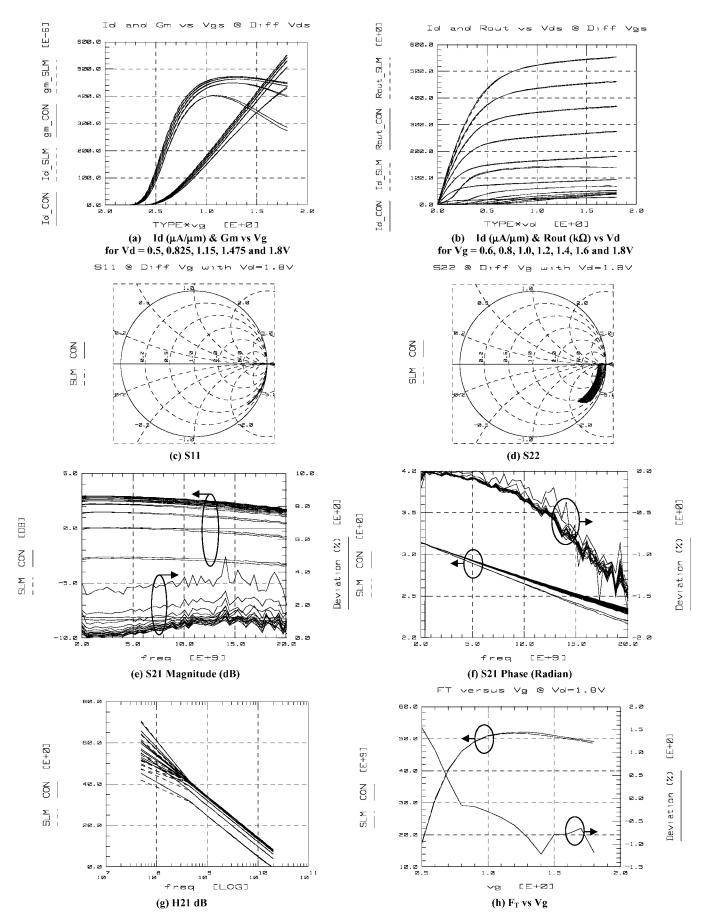

2-pF MIM capacitors fabricated between metal 5 and 6 of the 0.18  $\mu$ m technology have been included for further investigations to ensure that the proposed scribe line test structure design is reliable and extendable to other devices. Fig. 4(a) shows the conventional test structure layout for the MIM capacitor. On-wafer Two-Port S-parameter measurements up to 10 GHz

Fig. 3. Conventional (CON) versus Scribe Line (SLM) design for a 6-finger NMOS transistor (W/L =  $24/0.18 \ \mu m$ ). (a)–(b) IV; (c)–(f) S-parameters; (g) H21; and (h)  $F_T(h)$  for Vg = 0.5 - 1.8 V in steps of 0.1 V @ Vd = 1.8 V.

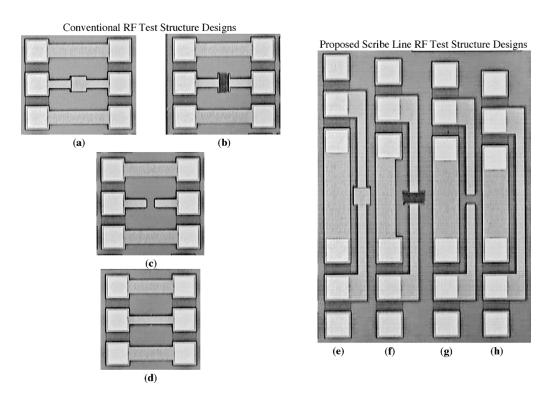

Fig. 4. Die photos showing the conventional (CON) versus proposed scribe line (SLM) design for 2 pF MIM capacitor and MOS varactor with open and thru' de-embedding structures. (a) MIM capacitor; (b) MOS varactor; (c) open; (d) thru'; (e) MIM capacitor; (f) MOS varactor; (g) open; (h) thru'.

are performed on the MIM capacitor in similar experimental setup as described for the MOSFET in Section II-A. A two-step de-embedding technique using open and thru' calibration structures shown in Fig. 4(c) and (d) is used to remove the pad capacitive and test leads resistive and inductive parasitics respectively. RF characterization is repeated for the MIM capacitor in scribe line layout design, its open and thru' de-embedding test structures as shown in Fig. 4(e), (g), and (h), correspondingly.

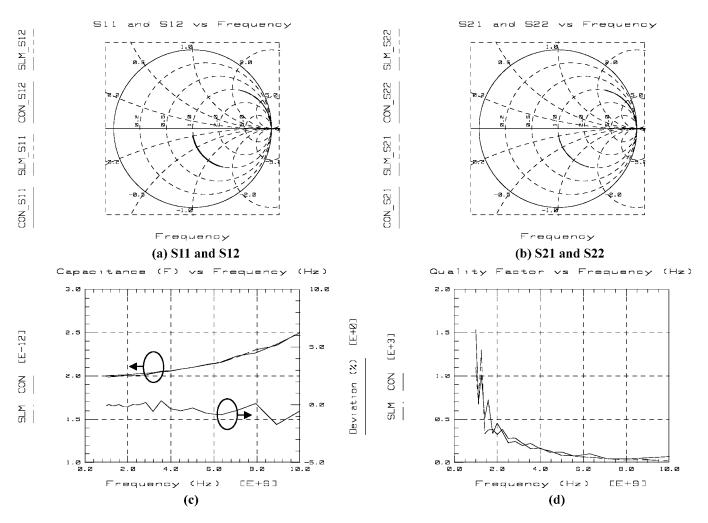

The measured results for the MIM capacitors are compared in Fig. 5. Up to 10 GHz, the two test structure designs yield good agreement in measured capacitance with deviation of not more than -2%. Both layout schemes produce similar trends in quality factor frequency response as shown in Fig. 5(d), exhibiting good correlations between the proposed scribe line and conventional RF layout schemes. Such excellent association between conventional and scribe line approach is achievable due to the reliable two-step, open-thru' de-embedding methodology.

#### C. MOS Varactor

Identical MOS varactors, readily available in 0.18-µm RFCMOS technology device library, with tuning capacitance range from 0.6 to 2.6 pF are layout in both the conventional and proposed scribe line test structure designs. MOS varactors used in this experiment are actually nMOSFET in Nwell, operating in the accumulation mode i.e. Polysilicon gate is the capacitor top plate and bottom plate refers to Nwell. Shown in Fig. 4(b), (c), and (d) are die photos of the MOS varactor under test and its open and thru' calibration structures, respectively for the conventional test structure designs. Scribe line designs for this

MOS varactor, on the other hand, are revealed in Fig. 4(f), (g), and (h). S-parameter measurements are performed with the vector network analyzer and the semiconductor parameter analyzer supplies dc biases to the gate and Nwell of the MOS varactor in similar experimental setup used for MOSFET's. A linear potential sweep from -1.8 to 1.8 V in steps of 0.1 V is applied to the gate of the MOS varactor and Nwell, on the other hand, is tied at 0 V.

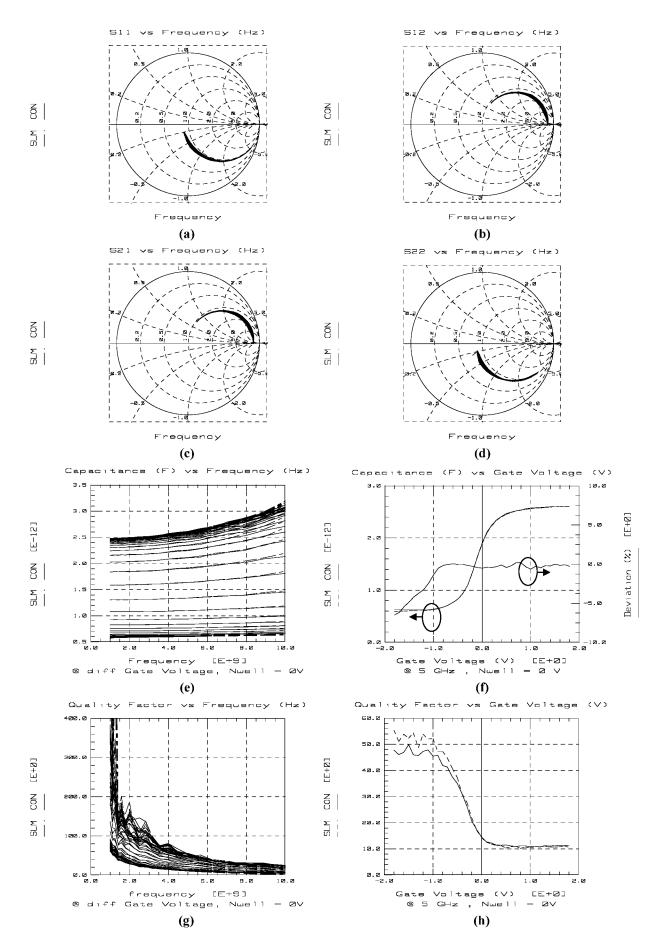

Fig. 6(a)–6(d) consolidate the measured Two-Port S-parameters of the MOS Varactor showing good agreement between the conventional and scribe line test structure designs at various bias conditions. Fig. 6(e) compares the measured capacitance versus frequency and good agreement is noted between the two test structure designs. When capacitances at 5 GHz are extracted from Fig. 6(e), capacitance versus gate voltage plot is obtained as depicted in Fig. 6(f). Excellent correlations are observed between the conventional and scribe line designs with capacitance deviations of not more than  $\pm 1\%$  for positive gate biases, a region which is generally of greater interests to circuit designers. Both layout schemes also reveal similar trends in quality factor versus frequency characteristics and quality factor versus gate bias behavior at 5 GHz.

#### D. Interconnects

Inductors are important components in RFCMOS designs and they are used primarily in matching networks and LC tank circuitries. Nonetheless, process monitoring of spiral inductors for RF applications is difficult since these inductors generally have huge dimensions and cannot be accommodated in the scribe lines. When inductors are used as important circuit components, routing of devices in circuit design also introduces additional

Fig. 5. Conventional (CON) versus Scribe Line (SLM) design for 2 pF MIM capacitor, (a) and (b) S-parameters, (c) capacitance, and (d) quality factor versus frequency.

metallization into the circuits. Self-inductances of these interconnects at gigahertz frequencies are nonnegligible. Parasitic resistance associated with these metal lines will increase with frequency due to skin effects and their substrate losses also become dominant at the high RF regime.

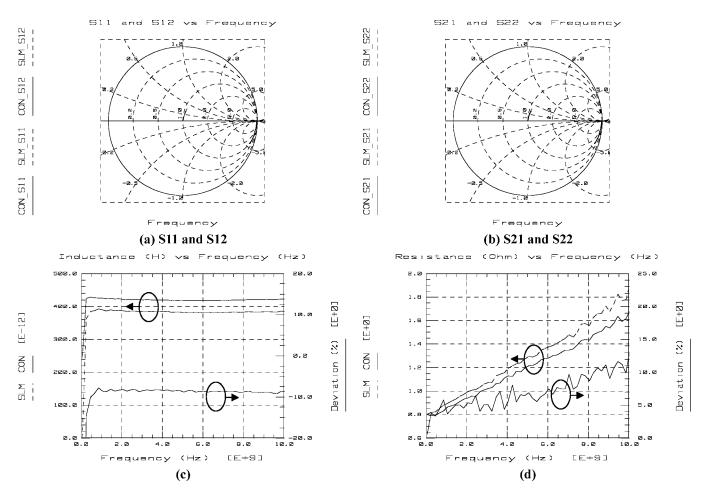

Hence, it is important to perform RF characteristics process monitoring of metallization to ensure that detrimental effects of these interconnects on circuit performance are kept in checks, providing also insights as to how spiral inductors behave in the production environment. A possible scribe line design for interconnects is proposed in this work. Die photos of conventional and scribe line designs for interconnects with corresponding open calibrations structures are consolidated in Fig. 7. Due to the north-south placement of GSG probes in the scribe line design, metal 6 interconnect line with identical length and width of 500 and 10  $\mu$ m, respectively, has to be layout with two 90° bends as compared to the conventional layout style shown in Fig. 7(c).

On-wafer RF characterization are performed on these interconnect test structures. Fig. 8(a) and (b) compares S-parameters of the interconnect lines from the conventional and scribe line layout schemes. Fig. 8(c) and (d) reveals that up to 10 GHz, there is about 10% difference in the extracted parasitic inductance and resistance of the interconnect line. At low frequencies, extracted resistances from the two test structures correlates well since the interconnects have identical length and width. Up to 4 GHz, the scribe line design has a +5% deviation in resistance when compared against interconnect in the conventional layout scheme. Although measured RF characteristics between the conventional and scribe line designs do not agree completely, primarily due to the two 90° bends, the proposed scribe line design can still be adopted to monitor the RF characteristics of metallization.

Good correlations between conventional and the proposed scribe line layout schemes for devices like transistors, capacitors, and varactors must be achieved since the device models used in circuits are developed with measurement data from test structures in the conventional layout style. It is however uncertain to know the dimensions of the RF interconnects used in different parts of the circuits and the smallest useful spiral inductors are still too large to fit into scribe lines between dies. Therefore, until a better scribe line design for interconnect is developed, interconnects' parasitic inductance and resistance derived from the proposed scribe line test structure can still serve as a benchmarking reference indicator for a particular process, allowing process engineers to react accordingly if inductances and resistances associated with interconnects increase abnormally.

Fig. 6. (a)-(d) Conventional (CON) versus scribe line (SLM) design for 2 pF MOS Varactor, (a)–(d) S-parameters, (e) capacitance versus frequency @ diff gate bias, (f) capacitance versus gate bias @ 5 GHz, (g) quality factor versus frequency @ diff gate bias, and (h) quality factor versus gate bias @ 5 GHz.

#### Proposed Scribe Line RF Test Structure Design

Fig. 7. Die photos showing the conventional (CON) versus proposed scribe line (SLM) design for metal 6 interconnect structure (Length =  $500 \,\mu$ m, Width =  $10 \,\mu$ m) with open de-embedding structures. (a) Interconnect; (b) open; (c) interconnect; (d) open.

Fig. 8. Conventional (CON) versus scribe line (SLM) design for metal 6 interconnect (Length =  $500 \ \mu m$ , Width =  $10 \ \mu m$ ), (a) and (b) S-parameters, (c) parasitic inductance, and (d) resistance versus frequency.

#### **III.** CONCLUSION

This paper highlighted and emphasized the need for reliable RF process monitoring test structures to understand circuit sensitivities to process variations, allowing both semiconductor foundries and circuit design companies to achieve better process and circuit yield. A novel design for RF process monitoring test structure has been proposed in this paper. The functionality and reliability aspects of this new test structure design have been tested extensively. Excellent agreement in measured RF characteristics has been observed for MOS transistors, capacitors and varactors. A possible scribe line design is also proposed to serve as a reference benchmarking indicator for interconnects.

#### References

- L. E. Larson, "Integrated circuit technology options for RFICs—present status and future directions," *IEEE J. Solid-State Circuits*, vol. 32, no. 3, pp. 387–397, Mar. 1998.

- [2] B. Razavi, "CMOS technology characterization for analog and RF design," *IEEE J. Solid-State Circuits*, vol. 34, no. 3, pp. 268–276, Mar. 1999

- [3] Cascade Microtech. [Online]. Available: http://www.cmicro.com

- [4] Agilent. [Online]. Available: http://www.agilent.com

- [5] E. P. Vandamme, D. M. M.-P. Schreurs, and C. van Dinther, "Improved three-step de-embedding method to accurately account for the influence of pad parasitics in silicon on-wafer RF test structures," *IEEE Trans. Electron Devices*, vol. 48, no. 4, pp. 737–742, Apr. 2001.

- [6] C. B. Sia, B. H. Ong, K. M. Lim, K. S. Yeo, M. A. Do, J. G. Ma, and T. Alam, "A novel RFCMOS process monitoring test structure," in *Proc. IEEE Intl. Conf. Microelectronics Test Structures*, vol. 17, Mar. 2004, pp. 45–50.

**Choon Beng Sia** received the bachelor's and master's degrees in electrical and electronics engineering from Nanyang Technological University, Singapore, in 1999 and 2001, respectively.

He is currently working in Advanced RFIC (S) Pte Ltd., as a Principal Engineer in the RF Device Modeling group. His research interests include design optimization and modeling of on-chip inductors as well as RF interconnects. He currently holds one U.S. patent, with five pending and has coauthored six technical publications.

**Beng Hwee Ong** was born in Singapore in 1975. He received the B.S. degree in electrical engineering from the Nanyang Technological University, Singapore, in 2001.

He joined NTU as a member of the research staff in 2002, and is currently working on RFCMOS circuit designs.

**Kok Meng Lim** received the Diploma degree in mechatronics from Singapore Polytechnic, Singapore, in 1997. Following completion of his diploma, he spent three years at Nanyang Technological University of Singapore to obtain the bachelors Degree.

Since 2001, he has been working as an EDA Engineer in Advanced RFIC (S) Pte Ltd.

**Kiat Seng Yeo** received the B.E. degree (with Honors) in electronics and Ph.D. degree in electrical engineering from Nanyang Technological University, Singapore, in 1993 and 1996, respectively.

He joined the School of Electrical and Electronic Engineering, Nanyang Technological University as a Lecturer in 1996, and became an Assistant Professor and an Associate Professor in 1999 and 2002, respectively.

Currently, he provides consulting to statutory boards and multinational corporations in the areas

of semiconductor devices and electronic circuit design. He has been extensively involved in the modeling and fabrication of small MOS/Bipolar integrated technologies for the last ten years. His research interests also include the design of new circuits and systems (based on scaled technologies) for low-voltage low-power applications; RF IC design; integrated circuit design of BiCMOS/CMOS multiple-valued logic circuits, domino logic, and memories; and device characterization of deep submicrometer MOSFETs. He is the Sub-Dean of School of Electrical and Electronic Engineering, the program manager of the system-on-chip flagship project, the coordinator of the integrated circuit design research group and the principal investigator of the integrated circuit technology research group at NTU. He has authored two books: Low-Voltage Low-Power Digital BiCMOS Circuits: Circuit Design, Comparative Study, and Sensitivity Analysis (Prentice Hall, NJ: Upper Saddle River, 2000, International Edition) and CMOS/BiCMOS ULSI: Low-Voltage, Low-Power (Prentice Hall, NJ: Upper Saddle River, 2001, International Edition), filed/granted eight patents, and published more than 100 articles on CMOS/BiCMOS technology and integrated circuit design in leading technical journals and conferences worldwide, and is a technical reviewer for several prestigious international journals.

Prof. Yeo was the Technical Chair of the 8th and 9th International Symposium on Integrated Circuits, Devices and Systems (ISIC-1999 and ISIC-2001, respectively). He also served in the program committee of the International Symposium on VLSI Technology, Systems, and Applications (VLSI-TSA) and the International Symposium on Low-Power and High-Speed Chips (COOL Chips) since 1999 and 2002, respectively. He was listed in Marquis Who's Who in the World and Marquis Who's Who in Science and Engineering.

Manh Anh Do received the B.E. degree (with Honors) in electronics in 1973, and Ph.D. degree in electrical engineering in 1977, both from University of Canterbury, Canterbury, New Zealand, in 1973 and 1977, respectively.

Between 1977 and 1989, he held various positions including: R&D Engineer and Production Manager at Radio Engineering Ltd., Research Scientist at Fisheries Research Centre, New Zealand, and Senior Lecturer at National University of Singapore. He joined the School of Electrical and Electronic Engineering,

Nanyang Technological University (NTU), Singapore, as a Senior Lecturer in 1989, and became Associate Professor in 1996 and the Professor in 2001. He has been a consultant for many projects in the Singapore electronic industry, and was the principal consultant for the design, testing and implementation of the \$200 million Electronic Road Pricing (ERP) island-wide project in Singapore, from 1990 to 2001. His current research is on digital and mobile communications, RF IC design, mixed-signal circuits, and intelligent transport systems. Before that, he specialized in sonar designing, biomedical engineering, and signal processing. Since 1995, he has been Head of Division of Circuits and Systems, School of EEE, NTU.

Prof. Do is a Fellow of Institution of Electrical Engineers (IEE), U.K., a chartered engineer (U.K.), and a professional engineer (Singapore).

Jian-Guo Ma (M'96–SM'97) received the B.Sc. and M.Sc. degrees with honors form Lanzhou University of China, in 1982 and 1988, respectively, and the Ph.D. degree in engineering from Gerhard-Mercator University of Germany in 1996.

From January 1982 to March 1991, he has worked with Lanzhou University of China on RF & Microwave Engineering. Before he joined Nanyang Technological University in 1997, he was with Technical University of Nova Scotia, Canada. He is currently Associate Professor and Director of the

Center for Integrated Circuits & Systems, Nanyang Technological University of Singapore.

His research interests are in RFIC designs for wireless applications, RF characterization and modeling of semiconductor devices, RF interconnects and packaging, SoC and Applications, and EMC/EMI in RFICs. He has published more than 130 technical papers and two books in these areas. He holds six patents in CMOS RFICs.

Prof. Ma He is Associate Editor for IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

**Tariq Alam** received the B.Eng. degree (with Honors) in electrical and electronic engineering and the Ph.D. degree in microwave engineering from Leeds University, Leeds, U.K., in 1994 and 1998, respectively.

His research was focused on on-wafer device characterization and modeling at millimeter-wave frequencies. He joined Cascade Microtech Inc. as a Senior Applications Engineer in 1999, and became the World Wide RF/Microwave Segment Manager in 2002.