## This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# On-chip antennas for 60-GHz radios in silicon technology

Guo, L. H.; Zhang, Yue Ping; Sun, Mei

2005

Zhang, Y. P., Sun, M., & Guo, L. H. (2005). On-Chip Antennas for 60-GHz Radios in Silicon Technology. IEEE Transactions on Electron Devices, 52(7), 1664-1668.

https://hdl.handle.net/10356/91144

https://doi.org/10.1109/TED.2005.850628

© 2006 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.

Downloaded on 23 Aug 2022 22:16:42 SGT

active/standby power requirement in a single chip can result in the coexistence of both PD and FD devices in the same circuit by design, as indicated by (7).

Using (7) to estimate the immunity of floating-body effect for devices with various feature size is also crucial to SOI compact modeling. To circumvent the modeling challenge imposed by the trend of coexistence of PD and FD devices in a single chip, a unified SOI compact model based on the concept of body-source built-in potential lowering has been proposed [8], [10]. Under this generic model framework where the PD/FD module may be selected through a module selector, the value of  $\Delta V_{\rm bi}({\rm inv})$  estimated by (7) can be used to determine the PD/FD module adequately in a per-instance manner to gain both simulation accuracy and efficiency.

In conclusion, the geometry-dependent floating-body effect can be explained and predicted by the correlation between  $\Delta V_{\rm bi}$  and  $V_T$ . This brief points out the underlying mechanism responsible for the coexistence of PD and FD devices in a state-of-the-art SOI chip.

#### ACKNOWLEDGMENT

The authors would like to thank to Dr. F.-L. Yang, K.-W. Su, and S. Fung.

#### REFERENCES

- [1] The International Technology Roadmap for Semiconductor, 2003.

- [2] J. O. Plouchart et al., "Application of an SOI 0.12 μm CMOS technology to SOCs with low power and high frequency circuits," IBM J. Res. Develop., vol. 47, no. 5/6, p. 611, Sep./Nov. 2003.

- [3] F.-L. Yang *et al.*, "A 65 nm node strained SOI technology with slim spacer," in *IEDM Tech. Dig.*, Dec. 2003.

- [4] M. Celik et al., "A 45 nm gate length high performance SOI transistor for 100 nm CMOS technology applications," in Symp. VLSI Tech. Dig., Jun. 2002, p. 166.

- [5] D. Bearden, "SOI design experiences with Motorolas high-performance processors," in *Proc. IEEE Int. SOI Conf.*, Oct. 2002, p. 6.

- [6] D. H. Allen, "A VLSI design methodology for SOI technology," in *Proc. IEEE Int. SOI Conf.*, Oct. 2004, p. 5.

- [7] F.-L. Yang et al., "Strained FIP-SOI (FinFET/FD/PD-SOI) for sub-65 nm CMOS scaling," in Symp. VLSI Tech. Dig., Jun. 2003, p. 137.

- [8] P. Su, S. Fung, P. Wyatt, H. Wan, M. Chan, A. Niknejad, and C. Hu, "A unified model for partial-depletion and full-depletion SOI circuit designs: Using BSIMPD as a foundation," in *Proc. IEEE Custom Integrated Circuits Conf.*, San Jose, CA, Sep. 2003, p. 241.

- [9] P. Su and W. Lee, "Modeling geometry-dependent floating-body effect using body-source built-in potential lowering for scaled SOI CMOS," in *Proc. Int. Conf. Solid State Devices Materials*, Tokyo, Japan, Sep. 2004, p. 510.

- [10] P. Su, S. Fung, P. Wyatt, H. Wan, A. Niknejad, M. Chan, and C. Hu, "On the body-source built-in potential lowering of SOI MOSFETs," *IEEE Electron Device Lett.*, vol. 24, no. 2, p. 90, Feb. 2003.

- [11] P. Su, "An international standard model for SOI circuit design," Ph.D. dissertation, Dept. EECS, Univ. California, Berkeley, Dec. 2002.

- [12] J. C. S. Woo, K. W. Terrill, and P. K. Vasudev, "Two-dimensional analytic modeling of very thin SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 37, no. 9, pp. 1999–2006, Sep. 1990.

- [13] S. M. Sze, Semiconductor Devices: Physics and Technology. New York: Wiley, 1985.

- [14] L. Su, J. Jacobs, J. Chung, and D. Antoniadis, "Deep-submicrometer channel design in silicon-on-insulator (SOI) MOSFETs," *IEEE Electron Device Lett.*, vol. 15, no. 9, pp. 366–369, Sep. 1994.

- [15] Z. Liu, C. Hu, J. Huang, T. Chan, M. Jeng, P. Ko, and Y. Cheng, "Threshold voltage model for deep-submicrometer MOSFETs," *IEEE Trans. Electron Devices*, vol. 40, no. 1, pp. 86–95, Jan. 1993.

- [16] H. Ueno et al., "Impurity-profile-based threshold-voltage model of pocket-implanted MOSFETs for circuit simulation," *IEEE Trans. Electron Devices*, vol. 49, no. 10, pp. 1783–1789, Oct. 2002.

- [17] L. Akers, "The inverse-narrow-width effect," IEEE Electron Device Lett., vol. EDL-7, no. 7, pp. 419–421, Jul. 1986.

- [18] Y. Cheng and C. Hu, MOSFET Modeling and BSIM3 Users Guide: KAP,

### On-Chip Antennas for 60-GHz Radios in Silicon Technology

Y. P. Zhang, M. Sun, and L. H. Guo

Abstract—The recent advances in 60-GHz radios have called for the parallel development of compact and efficient millimeter-wave antennas. This brief addresses for the first time the design, fabrication, and characterization of on-chip inverted-F and quasi-Yagi antennas for 60-GHz radios. The design was made using the Zeland IE3D software package. The fabrication was realized with the back-end-of-line process of silicon substrates of low resistivity 10  $\Omega$ ·cm. The characterization was conducted on wafer with Cascade Microtech coplanar probes and an HP8510XF network analyzer. The results show that the inverted-F antenna achieved a minimum return loss of 32 dB and a gain of -19 dBi at 61 GHz; while the quasi-Yagi antenna achieved a minimum return loss of 6.75 dB and a gain of -12.5 dBi at 65 GHz. Good agreement has been observed between the measured and simulated results.

*Index Terms*—60-GHz radios, inverted-F antennas, on-chip antennas, quasi-Yagi antennas, wireless personal area network (WPAN).

#### I. INTRODUCTION

There is much interest today in exploiting the 60-GHz band for wireless personal area network (WPAN) applications because a large bandwidth of 7 GHz is available [1]. The large bandwidth and millimeter-wave frequency have indeed created many challenges in the design of radio front-ends. The 60-GHz radio front-end implemented as an assembly of microwave monolithic integrated circuits (MMICs) in gallium arsenide (GaAs) semiconductor technology has proven feasible but rather expensive [2]. The 60-GHz radio front-end based on MMICs in silicon germanium (SiGe) semiconductor technology has been attempted. For instance, Renolds et al. demonstrated 60-GHz radio front-end circuits including a low-noise amplifier (LNA), a direct down converter, a power amplifier, and a voltage-controlled oscillator (VCO) in SiGe technology [3]. Design toward realizing a low-cost fully integrated SiGe 60-GHz radio front-end has been carried out. As the high-frequency capabilities of complimentary metal oxide semiconductor (CMOS) technology improve through scaling, CMOS has become a viable technology for millimeter-wave operation. Doan et al. has explored CMOS for 60-GHz applications and designed an LNA using a standard 0.13  $\mu$ m CMOS process [4]. Luiz et al. demonstrated 64- and 100-GHz VCOs in 90-nm CMOS [5]. Liu et al. demonstrated a 63-GHz VCO in a standard 0.25- $\mu$ m CMOS [6]. In addition, CMOS technology that promises to integrate a complete 60-GHz system (radio front-end plus digital processor) on a single chip (SoC) further enhances its competitiveness.

An antenna plays a key role in a radio. It has independent properties that affect the radio as a whole. Current antennas for 60-GHz radios are mainly discrete designs on conventional dielectric substrates [7], [8]. A relatively new development for 60-GHz antenna designs is the application of multichip module (MCM) technologies, which embeds antennas into integrated circuit packages [9]. At 60 GHz, the antenna form factor is on the order of millimeters or less and opens up new

Manuscript received February 28, 2005. The review of this brief was arranged by Editor J. N. Burghartz.

Y. P. Zhang and M. Sun are with the Integrated Systems Research Laboratory, School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: eypzhang@ntu.edu.sg; SUNM0001@ntu.edu.sg).

L. H. Guo is with the Semiconductor Process Technology Laboratory, Institute of Microelectronics, Singapore 117685 (e-mail: lihui@ime.a-star.edu.sg). Digital Object Identifier 10.1109/TED.2005.850628

integration options. Integration of millimeter-wave antennas on silicon substrates of high resistivity has been investigated [10]–[12]. However, to combat the large loss due to low resistivity silicon substrate as the frequency increases to millimeter-wave range, various techniques such as micromachining process and proton implantation have to be employed. The micromachining process removes the loss silicon substrate underneath the antenna radiating element [12], while the proton implantation increases significantly the resistivity of the silicon substrate underneath the antenna radiating element from 10 to  $10^6\ \Omega\cdot cm$  [13]. In our brief, we adopt the post-BEOL process developed at IME for RF CMOS passives to overcome this problem. We present here for the first time the design, fabrication, and characterization of on-chip inverted-F and quasi-Yagi antennas for 60-GHz radios on silicon substrates of low resistivity  $10\ \Omega\text{-cm}$ .

#### II. DESIGN OF ON-CHIP INVERTED-F AND QUASI-YAGI ANTENNAS

Antennas for 60-GHz applications should feature the following properties: 1) low fabrication cost and readily amenable to mass production; 2) light weight and small size; 3) high efficiency and broad bandwidth; and 4) integratable with other radio front-end circuitry [1]. Most antennas on silicon substrates of high resistivity are microstrip antennas, planar inverted-F antennas and Yagi–Uda antennas [10]–[12]. Considering the potential that the microstrip patch and the planar element may cause micro fracture to the silicon substrate, we chose linear inverted-F and quasi-Yagi antennas for our brief.

The linear inverted-F antenna consists of a horizontal line, a shortcircuited vertical line, and a signal-driven vertical line. It is well known that the inverted-F antenna originated from the modification of the inverted-L antenna. The modification is very important because the input impedance of an inverted-F antenna can be arranged to have an appropriate value to match the source impedance, without using any additional circuit between the antenna and the source. One more important property of the inverted-F antenna is its performance with both vertical and horizontal polarizations, because the antenna has both the vertical and horizontal elements. Its performance with two-polarization would be very useful for WPAN applications. In a WPAN environment, the radio signal has random fluctuating distributions, compounding of the vertical polarization and the horizontal polarization can provide a diversity effect and improve the reception. Another advantage of the inverted-F antenna is its small vertical dimension, which enables it to be favorable for on-chip integration as it can be designed at one of chips' edges. Taking these facts into account it can be said that the inverted-F antenna is an especially attractive antenna for WPAN applications.

The Yagi–Uda antenna has found wide applications in the HF-UHF band. For frequencies up to millimeter-wave range, microstrip-fed quasi-Yagi antennas have been built on conventional dielectric substrate ( $\varepsilon_r=9.8$ ) [14]. The Yagi–Uda is based on the principles of parasitic elements that are not directly fed by an energy source. These elements focus the radiation pattern using currents induced in them by radiation from the driven element. According to their length and spacing from the driven element, the parasitic elements become either directors or reflectors. Directors are shorter than the driven element and result in the radiation pattern being sharply focused in the direction of the directors. Reflectors are longer than the driven element and result in a radiation pattern directed away from them. The overall result is an endfire radiation pattern, which is an attractive property for point-to-point radio communications [12].

The inverted-F and quasi-Yagi antennas were designed using the electromagnetic simulator Zeland IE3D. This software package based on the method of moments performs a full wave electromagnetic analysis of dispersion, discontinuities, surface waves, higher order modes, conductor loss, dielectric loss, and radiation loss.

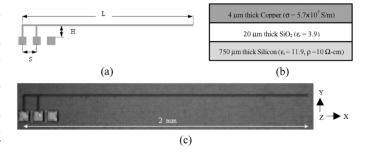

Fig. 1. On-chip inverted-F antenna: (a) layout, (b) cross-sectional view, and (c) top view photograph.

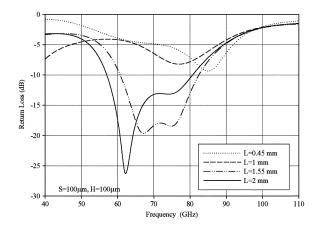

Fig. 2. Return loss of inverted-F antenna for  $\boldsymbol{L}$  variation.

#### A. Inverted-F Antenna

The layout, cross-sectional view, and top view photograph of the on-chip inverted-F antenna are illustrated in Fig. 1. The test ground-signal-ground (GSG) pads are squares of  $80~\mu\text{m} \times 80~\mu\text{m}$ . The width of the line elements is  $10~\mu\text{m}$ . Given the technology, the design parameters are L, H, and S. The effective length (L+H) controls the frequency of resonance, while the separation distance S can adjust the antenna impedance to match to the source. To ease our design H and S are fixed as  $100~\mu\text{m}$ , respectively. The simulated return loss of the inverted-F antenna for the parameter L variation is then shown in Fig. 2. It is evident from the figure that when L reaches 2 mm, the return loss drops to 17 dB indicating good matching to the  $50~\Omega$  source at 60~GHz. We know that for conventional inverted-F antenna the resonance occurs at

$$(L+H) = n\lambda/4 \tag{1}$$

where  $\lambda$  is the wavelength and n is the mode order. At 60 GHz, the wavelength in CMOS silicon substrate of low resistivity of Fig. 1(b) is about 2.2 mm. Thus, it seems that (L+H) should be 0.55 mm for the first-order mode to resonate at 60 GHz. However, our simulation shows in Fig. 2 that the resonance does not occur for the first-order mode with this length. The resonance occurs near 60 GHz when (L+H) reaches 2.1 mm, which indicates the fourth-order mode is excited.

The simulated radiation patterns of the inverted-F antenna in the azimuth and elevation planes at 60 GHz are shown in Fig. 3 where L,S, and H are taken as 2 mm, 100, and 100  $\mu$ m, respectively. In the azimuth plane, as expected, the maximum radiation occurs in the  $0^{\circ}$  direction for the copolarization radiation and the radiation is stronger in the upper hemisphere. The cross-polarization radiation is much weaker than the

Fig. 3. Radiation patterns of the inverted-F antenna (azimuth plane:  $\theta=85^\circ$ . Elevation plane:  $\varphi=0^\circ$ ).

copolarization radiation, for example, in the  $0^\circ$  direction the cross-polarization radiation is 32 dB weaker. In the elevation plane, the radiation patterns, both co- and cross-polarizations can only be obtained for the upper hemisphere because the electromagnetic model assumes infinite extension of the ground plane. The copolarization radiation pattern becomes asymmetric because of the shorted-circuit line element. The radiation gets stronger in the directions away from the shorted-circuit line element. The cross-polarization radiation is stronger as compared with that in the azimuth plane. The cross-polarization radiation is only about 9 dB weaker than the copolarization radiation in the  $0^\circ$  direction in the elevation plane.

#### B. Quasi-Yagi Antenna

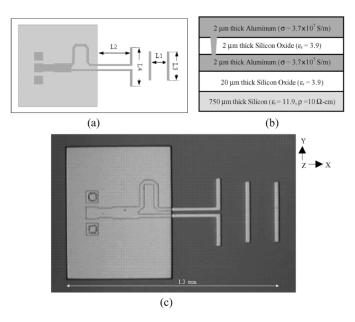

Fig. 4 shows the layout, cross-sectional view, and top view photographs of the on-chip quasi-Yagi antenna. It consists of one driver, two directors, and a truncated ground plane that acts as reflector. The antenna is fed by a microstrip line. It should be mentioned that the GSG probes require the testing pads being squares of  $80~\mu m$  by  $80~\mu m$  with a pitch of  $100~\mu m$ . As a result, the impedance between the signal pad and the ground plane with 2-  $\mu m$ -thick silicon oxide separation is small. This small impedance of a few ohms avoids the short circuit and a part of the signal reach the antenna to radiate.

It is known that the quasi-Yagi antenna has significantly more gain and a better-controlled front-to-back ratio when it employs at least three elements. We chose four elements for our design [14]. As shown in Fig. 4(a), parameters considered to optimize the design are L1, L2, L3, and L4. Parameter L1 is the distance between the driver and the first director, which equals the distance between the first director and the second director to simplify the design. Parameter L2 is the distance between the driver and the ground plane, parameter L3 is the length of the director, and parameter L4 is the length of the driver. The optimized parameters are L1 = 146, L2 = 270, L3 = 382, and  $L4 = 426 \,\mu\text{m}$ . It is found that the return loss is insensitive to the variation of parameters L1 and L3. When L1 is varied by 30 from 116 to 176  $\mu\text{m}$ , and L3 by 30 from 352 to 412  $\mu\text{m}$ , respectively, the return loss remains unchanged.

Fig. 4. On-chip quasi-Yagi antenna. (a) Layout. (b) Cross-sectional view. (c) Top view photographs.

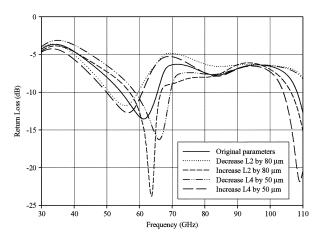

Fig. 5. Return loss of quasi-Yagi antenna for parameter variation.

It is also found that the return loss is sensitive to the variation of parameters L2 and L4 as shown in Fig. 5. They affect both impedance bandwidth and resonant frequency. The resonant frequency increases when the parameter L2 increases from 190 to 350 by 80  $\mu$ m. The resonant frequency decreases when the parameter L4 increases from 376 to 476 by 50  $\mu$ m. The final optimized parameters for the quasi-Yagi antenna yield the axial length of the quasi-Yagi antenna 1.3 mm and a broad -10 dB bandwidth from 55 to 65 GHz.

The simulated radiation patterns of the quasi-Yagi antenna in the azimuth and elevation planes at 60 GHz are shown in Fig. 6. Note that the quasi-Yagi antenna results in low cross-polarization radiation. They are 18.7 dB lower in the azimuth plane and 29.7 dB lower in the elevation plane as compared with copolarization radiation. The poor front-to-back ratio is due to the lossy substrate configuration.

#### III. FABRICATION OF ON-CHIP INVERTED-F AND QUASI-YAGI ANTENNAS

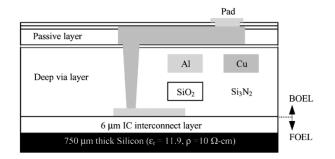

The post BOEL process is illustrated in Fig. 7. Note that a standard low resistivity silicon wafer of diameter 8 in and a thickness of 750  $\mu$ m is used. First, a 6- $\mu$ m-thick SiO<sub>2</sub> layer is grown on the

Fig. 6. Radiation patterns of the quasi-Yagi antenna (azimuth plane:  $\theta = 85^{\circ}$ ; elevation plane:  $\varphi = 0^{\circ}$ ).

Fig. 7. BEOL process.

wafer to simulate the insulator used for on-chip interconnect in standard CMOS process and over it a 7.5 KÅ thin aluminum pattern is deposited, which is equivalent to the Al pad used in standard CMOS ICs. Then, a 20- $\mu$ m-thick SiO $_2$  layer is grown to enhance the isolation of the RF passives from the silicon substrate of low resistivity. The 20- $\mu$ m-thick SiO $_2$  layer and the associated deep via capability are two important features of this BEOL process. Next, a 1-KÅ thin Si $_3$ N $_2$  layer is grown. After this process, we proceed to grow a 4  $\mu$ m-thick SiO $_2$  layer. In the 4- $\mu$ m-thick SiO $_2$  layer the copper passive pattern is embedded. Deep vias are formed to connect the aluminum with the copper layers. This is followed by growing a 3-KÅ thin Si $_3$ N $_2$  layer and a 3-KÅ thin SiO $_2$  layer for passivation sequentially. The aluminum test pads are finally formed for testing.

The inverted-F antenna was fabricated with the simplified post BEOL process. This can be seen from Fig. 1(b) where no aluminum layer is deposited and no deep via is formed. The inverted-F antenna is separated from the silicon substrate by a 20- $\mu$ m thick  $SiO_2$  layer. The quasi-Yagi antenna was fabricated with the modified post BEOL process. As seen from Fig. 4(b), the antenna is formed by two 2- $\mu$ m aluminum layers separated by a 2- $\mu$ m  $SiO_2$  layer. The driver, two directors, and its feeding structure are etched on the top aluminum layer, while the truncated ground plane used as the reflector is etched

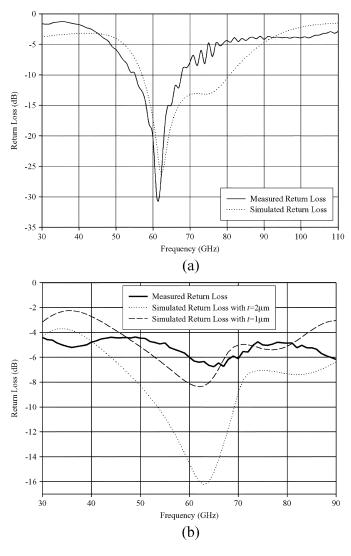

Fig. 8. Measured and simulated return loss. (a) Inverted-F antenna and (b) quasi-Yagi antenna.

on the bottom aluminum layer. The ground pads are connected to the truncated ground plane by vias to eliminate the capacitance effect between the two aluminum layers. The whole antenna structure is separated from the silicon substrate by a 20- $\mu$ m-thick SiO<sub>2</sub> layer. It is obvious that the antennas can be built on CMOS IC chips using the post BEOL process if they are proved to be successfully fabricated with the simplified post BEOL process discussed here.

#### IV. CHARACTERIZATION OF ON-CHIP INVERTED-F AND QUASI-YAGI ANTENNAS

The measurements were performed on-wafer with Cascade Microtech coplanar probes and an HP8510XF network analyzer. The S-parameters were measured for both antennas up to 110 GHz. Fig. 8(a) shows the measured and simulated return loss of the inverted-F antenna. It is evident from the figure that the measured result agrees well with the simulated one. It is more important to note from the measurement result that a sharp dip exists at 61 GHz, which indicates excellent antenna quality and good matching to the  $50-\Omega$  source. Using a threshold of -10 dB, the measured bandwidth for the inverted-F antenna covers from 55 to 67.5 GHz. Fig. 8(b) shows the measured and simulated return loss of the quasi-Yagi antenna. Note that a resonance null occurs at 65 GHz. Using a threshold of -6 dB,

the measured bandwidth covers from 61 to 70 GHz. The measured resonant frequency agrees with the simulated one. However, the matching is not good to achieve the lower return loss at the resonant frequency. It might be the reason of fabrication tolerance that makes the fabricated antenna not as fine as the designed. Fig. 8(b) also shows the tolerance influence of the thickness t of the silicon oxide layer between the top antenna structure and the truncated ground plane on the return loss. This can give one important possible reason why the measured return loss is so low at the resonant frequency.

The gains of both inverted-F and quasi-Yagi antennas were measured with the technique presented in [15]. The technique requires two identical antennas placed face-to-face and separated by a distance d. The distance d measures the separation between the reference planes used for far-filed measurements. One antenna functions as a transmit antenna, the other as a receive antenna. From transmission measurements the antenna gain can be estimated by

$$G^2 = |S_{21}|^2 \left[ \frac{4\pi d}{\lambda} \right]^2. \tag{2}$$

The technique does not permit one to determine the radiation pattern. However, the goal of this brief was to validate the design method and to optimize the process in order to integrate a complete 60-GHz radio front-end. The antenna gain is extracted from the measurements with d=20 mm. In our measurement a gain of -19 dBi is obtained at 61 GHz for the inverted-F antenna; while a gain of -12.5 dBi at 65 GHz for the quasi-Yagi antenna. The simulated radiation efficiency is 3.5% for the inverted-F antenna and 5.6% for the quasi-Yagi antenna. If they were implemented in conventional CMOS, the simulated radiation efficiency would only be 1.7% for the inverted-F antenna and 2% for the quasi-Yagi antenna.

#### V. CONCLUSION

This brief discussed the design, fabrication, and characterization of the on-chip inverted-F and quasi-Yagi antennas for 60-GHz radios for the first time. The design was based on intensive electromagnetic simulations using the Zeland IE3D software package. The antennas were tested on-wafer for return loss and gain. The measurement results show that the inverted-F antenna achieved a minimum return loss of 32 dB and a gain of -19 dBi at 61 GHz; while the quasi-Yagi antenna return loss of 6.75 dB and a gain of -12.5 dBi at 65 GHz. Good agreement has been observed between the measured and simulated results for the inverted-F antenna. The discrepancy between the measured and simulated results for the quasi-Yagi antenna was due to the process inaccuracy. The performance of the on-chip inverted-F and quasi-Yagi antennas can be further enhanced with the packaging techniques. It is therefore anticipated that the results and design details on the on-chip antennas presented here are useful and inspiring for engineers interested in 60-GHz radio front-end designs.

#### ACKNOWLEDGMENT

The authors would like to thank C. O. Mei for her assistance in the brief.

#### REFERENCES

- P. Smulders, "Exploring the 60 GHz band for local wireless multimedia access: Prospects and future directions," *IEEE Commun. Mag.*, vol. 40, no. 1, pp. 140–147, Jan. 2002.

- [2] K. Ohata, K. Maruhashi, M. Ito, S. Kishimoto, K. Ikuina, T. Hashiguchi, N. Takahashi, and S. Iwanaga, "Wireless 1.25 Gb/s transceiver module at 60 GHz band," in *Proc. IEEE Solid-State Circuits Conf.*, 2002, pp. 298–299.

- [3] S. Reynolds, B. Floyd, U. Pfeiffer, and T. Zwick, "60 GHz transceiver circuits in SiGe bipolar technology," in *Proc. IEEE Solid-State Circuits Conf.*, 2004, pp. 442–451.

- [4] C. H. Doan, S. Emami, A. M. Niknejad, and R. W. Brodersen, "Design of CMOS for 60 GHz applications," in *Proc. IEEE Solid-State Circuits Conf.*, 2004, pp. 440–449.

- [5] L. M. Franca-Neto, R. E. Bishop, and B. A. Bloechel, "64 GHz and 100 GHz VCOs in 90 nm CMOS using optimum pumping method," in *Proc. IEEE Solid-State Circuits Conf.*, 2004, pp. 444–453.

- [6] R. C. Liu, H. Y. Chang, C. H. Wang, and H. Wang, "A 63 Ghz VCO using a standard 0.25 mm CMOS process," in *Proc. IEEE Solid-State Circuits Conf.*, 2004, pp. 446–453.

- [7] J. Y. Park, Y. X. Wang, and T. Itoh, "A 60 GHz integrated antenna array for high-speed digital beamforming applications," in *Proc. IEEE MTT-S Int. Symp.*, vol. 3, 2003, pp. 1677–1680.

- [8] Y. Murakami, T. Kijima, H. Iwasaki, T. Ihara, T. Manabe, and K. Iigusa, "A switchable multisector antenna for indoor wireless LAN systems in the 60-GHz band," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 6, pp. 841–843, Jun. 1998.

- [9] E. Öjefors, "Micromachined Antennas for Integration with Silicon Based Active Devices," Lic. theses, Uppsala Univ., Uppsala, Sweden, Apr. 2003.

- [10] C. R. Trent and T. M. Weller, "Design and tolerance analysis of a 21 GHz CPW-fed, slot-coupled, microstrip antenna on etched silicon," in *IEEE AP-S Dig.*, vol. 1, 2002, pp. 402–405.

- [11] P. M. Mendes, S. Sinaga, A. Polyakov, M. Bartek, J. N. Burghartz, and J. H. Correia, "Wafer-level integration of on-chip antennas and RF passives using high-resistivity polysilicon substrate technology," in *Proc. Electronic Components Technology Conf.*, 2004, pp. 1879–1884.

- [12] D. Neculoiu, P. Pons, M. Saadaoui, L. Bary, D. Vasilache, K. Grenier, D. Dubuc, A. Muller, and R. Plana, "membrane supported Yagi–Uda antennae for millimeter-wave applications," in *Proc. Int. Elect. Eng. Mi*crow. Antennas Propag., vol. 151, 2004, pp. 311–314.

- [13] B. Chen, Y. D. Lin, T. S. Duh, and W. J. Lin, "Integrated antennas on Si, proton-implanted Si, and silicon-on-quartz," in *IEDM Tech. Dig.*, 2001, pp. 903–906.

- [14] P. R. Grajek, B. Schoenlinner, and G. M. Rebeiz, "A 24-GHz high-gain Yagi-Uda antenna array," *IEEE Trans. Antennas Propag.*, vol. 52, no. 5, pp. 1257–1261, May 2004.

- [15] R. N. Simions and R. Q. Lee, "On-wafer characterization of millimeterwave antennas for wireless application," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 1, pp. 92–96, 1999.