# On-Chip, Efficient and Small Antenna Array for Millimeter-Wave Applications

H. Dinis, M. Zamith, J. Fernandes, J. Magalhães, P. M. Mendes Dept. of Industrial Electronics, University of Minho, Guimarães, Portugal

*Abstract*— The high path losses experienced by wireless applications at millimeter wavelengths may be mitigated using high gain antennas. The intrinsic small wavelengths makes very attractive to develop solutions with on-chip integrated antennas. However, due to silicon high losses, on-chip antenna elements on RFCMOS technology have reduced efficiency. This paper proposes a solution to obtain an on-chip integrated antenna array based on 3D efficient antenna elements. A 4 element antenna was designed to operate at 57.5 GHz central frequency, with maximum gain of 5.8 dB, and maximum expected efficiency of 45%.

Keywords—integrated antenna, on-chip antenna, antenna array, 60 GHz.

#### I. INTRODUCTION

It is expected that systems using millimeter-wave bands will offer new possibilities for systems requiring the use of radio links [1]. The millimeter-wave systems offer new solutions: from wireless sensors to short-range high-speed mobile data rate. However, such systems are complex to design and price reduction will depend on the ability to increase the integration level, desirably using RFCMOS technologies [2]. One element requiring integration is the antenna, preferably an antenna array. Many solutions have been proposed (e.g., [3-9]) for antenna integration, but they are either complex to design, or non-CMOS compatible, or both.

One way towards design complexity and price reduction is system integration using CMOS technology, where the antenna may be considered for on-chip placement due to its intrinsic small size. One challenge when considering on-chip integration is to obtain good antenna efficiency [9]. The solution to increase the antenna efficiency is to rely on new integration approaches. The use of self-folding technology to obtain 3D on-chip structures allows the fabrication of on-chip 3D antennas [10].

In this paper we propose and analyse the expected performance for an antenna array fabricated with an innovative integration methodology, that allows the design of on-chip array antennas on RFCMOS compatible technology.

## II. SYSTEM DESIGN

The main concept is based on the use of a 3D element [10], allowing an antenna that is floating on top of the substrate.

## A. Integration Methodology

Fig. 1 shows the proposed antenna integration concept. The four antenna elements are obtained using 3D self-folding

Fig. 1. Proposed solution to obtain an on-chip antenna array (artistic view).

## methodology [11].

After obtaining the antenna array on top of a silicon wafer, the integration with the remaining system my be obtained using wafer level chip scale packaging methodologies, multichip methodologies, or by using a post-processing module applied to the RFCMOS wafer.

### B. Antenna Element

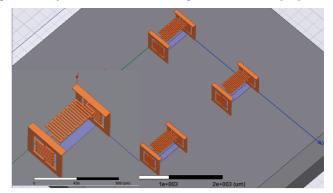

Fig. 2 shows the HFSS antenna model. It shows the fourantenna element, with a close-up to one single antenna. The antennas are placed on top of a silicon wafer, with electrical permitivity,  $\varepsilon_r = 4.25$ , and loss tangent, tan $\delta = 0.15$  [12].

Fig. 2. Ansys HFSS model single antenna element and antenna array.

It was assumed that the wafer bottom was grounded and no isolation layer, like  $SiO_2$  was placed on top of the wafer, between antennas and silicon wafer.

## III. RESULTS AND DISCUSSION

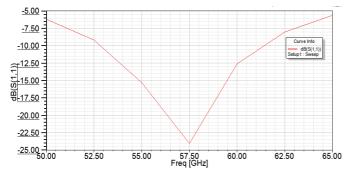

Fig. 3 shows the antenna operating central frequency and bandwidth.  $% \left( {{{\rm{F}}_{{\rm{F}}}}_{{\rm{F}}}} \right)$

### A. Antenna Properties

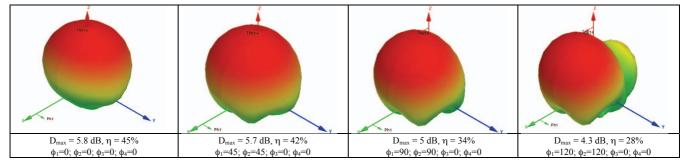

Using the antenna array model from Fig. 2, the results shown in table 1 were obtained for a distance between

antennas of d = 1.15 mm Since we have four antennas, the radiation pattern may be controlled using the phase shifts.

Fig. 3. Ansys HFSS computed S11 array operating characteristics.

From table 1, we can see that the maximum efficiency was  $\eta = 45\%$  and max gain was G = 5.8 dB. The gain and efficiency changes as we change the radiation pattern. The values shown in table 1 may not seem very high, but when compared with values from [9], we may conclude that this new approach is very competitive, since it gives almost the same values without the need of extra room required by the artificial materials. Moreover, this new approach does not require any complex antenna design methodology.

#### B. Measurement Setup

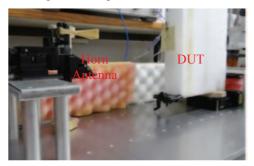

To test the proposed antenna integration methodology, the setup shown in Fig. 4 was implemented.

Fig. 4. Measurement setup to characterize the on-chip antenna array.

The left transmitting side is comprised by a signal generator, a frequency multiplier (minicircuits ZX90-2-24+), followed by the HXI frequency multiplier (HAFMV4-187), and a horn antenna (Q-par QSH-SL-50-75-V-20). The right receiving side (DUT) is comprised by the silicon chip with the 3D antennas mounted on it.

#### IV. CONCLUSIONS

In this work we propose the integration of 3D antennas on top of a silicon wafer. A solution was proposed towards the development of fully integrated RFCMOS transceivers at millimetre-wave band, with improved efficiency.

#### ACKNOWLEDGMENT

Work supported by Portuguese Foundation for Science and Technology (SFRH/BD/63737/2009, and PTDC/ EEI-TEL/ 2881/2012, Programa Operacional Temático Fatores de Competitividade-COMPETE, Fundo and Comunitário Europeu-FEDER).

#### REFERENCES

- [1] S Rangan, T.S. Rappaport, E. Erkip, "Millimeter-Wave Cellular Wireless

- [1] S Rangai, H.S. Rappaport, E.ERRP, Hummer-wave echual whereas Networks: Potentials and Challenges", Proceedings of the IEEE, pp: 366 385 Vol. 102, Issue: 3, March 2014

[2] A. Moroni, R. Genesi, D. Manstretta, "Analysis and Design of a 54 GHz Distributed "Hybrid" Wave Oscillator Array With Quadrature Outputs", IEEE Journal of Solid-State Circuits, pp. 1158 1172 Vol: 40 June 5 March 2014 49, Issue: 5, May 2014

[3] – L. Dussopt, L. Zevallos, A. Siligaris, "On-chip/in-package integrated

- [3] E. Dussop, E. Evanos, A. Singars, On-only in package integrated antenna for millimeter-wave medium and long-range applications", Int. Work. Ant. Tech. (iWAT), 2013, pp 203 206

[4] K. Chin; W. Jiang; W. Che; C. Chang; H. Jin, "Wideband LTCC 60-GHz Antenna Array With a Dual-Resonant Slot and Patch Structure", IEEE

- Frans. Ant. and Prop., pp. 174 182 Vol. 62, Issue: 1, Jan. 2014

[5] X. Bao; Y. Guo; Y. Xiong, "60-GHz AMC-Based Circularly Polarized On-Chip Antenna Using Standard 0.18-\$mu\$ m CMOS Technology", IEEE Trans. Ant. and Prop., pp.: 2234 2241 Vol. 60, Iss. 5, May 2012

[6] A. Enayati, G.A.E Vandenbosch, W. Deraedt, "Millimeter-Wave Horn-Technology and the property of the provide the provide the provided the provide

- Type Antenna-in-Package Solution Fabricated in a Teflon-Based Multilayer PCB Technology", IEEE Trans. Ant. and Prop., pp. 1581 -1590 Vol. 61, Issue: 4, April 2013

- [7] W. Hong, K. Baek, A. Goudelev, "Grid Assembly-Free 60-GHz Antenna Module Embedded in FR-4 Transceiver Carrier Board", IEEE Trans. Ant. and Prop., pp. 1573 - 1580 Vol. 61, Issue: 4, April 2013 J.A.Z. Luna, L. Dussopt, A. Siligaris, "Hybrid On-Chip/In-Package Integrated Antennas for Millimeter-Wave Score-Range

- [8] -Communications", IEEE Trans. Ant. and Prop., pp. 5377 - 5384 Vol: 61, Issue: 11, Nov. 2013

- [9] A. Barakat, A. Allam, H. Elsadek, "Small Size 60 GHz CMOS Antennaon-Chip: Gain and Efficiency enhancement using asymmetric Artificial Magnetic Conductor," in 44st European Microwave Conference (EuMC), Rome, Italy, 5-10 October, 2014.

- [10] S. Gomes, J. Fernandes, P. Anacleto, E. Gultepe, D. Gracias, P. M. Mendes, "Ultra-Small Energy Harvesting Microsystem for Biomedical Applications," 44st EuMC, Rome, Italy, 5-10 October, 2014

S. Pandey, E. Gultepe, D. H. Gracias, "Origami inspired self-assembly

- of patterned and reconfigurable particles.," J. Vis. Exp., no. 72, p. e50022, 2013.

- [12] F. Guttierrez, T. S. Rappaport and J. Murdock "Millimeter-wave CMOS antennas and RFIC parameter extraction for vehicular applications", Proc. IEEE Vehicular Technology Conf., 2010