# **On-chip Hot Spot Remediation** with Miniaturized Thermoelectric Coolers

Avram Bar-Cohen · Peng Wang

Received: 24 March 2009 / Accepted: 6 July 2009 / Published online: 24 July 2009 © Springer Science + Business Media B.V. 2009

Abstract The rapid emergence of nanoelectronics, with the consequent rise in transistor density and switching speed, has led to a steep increase in chip heat flux and growing concern over the emergence of onchip "hot spots" in microprocessors, along with such high flux regions in power electronic chips and LED's. Miniaturized thermoelectric coolers ( $\mu$ -TEC's) are a most promising cooling technique for the remediation of such hot spots. This paper presents a comprehensive review of recent advances in novel applications of superlattice, mini-contact, and silicon-based miniaturized thermoelectric coolers in reducing the severity of on-chip hot spots.

**Keywords** Thermal management • Electronic cooling • Thermoelectric cooler • Hot spot cooling

# Introduction

Microelectronics has become the heart of any modern electronic product from home/office PC systems to advanced military/defense electronic systems. However,

A. Bar-Cohen (⊠) · P. Wang Department of Mechanical Engineering, University of Maryland, College Park, MD 20742, USA e-mail: abc@umd.edu

P. Wang e-mail: wangp2007@gmail.com because all the microelectronic devices require power for their use, the conversion of electrical energy to thermal energy is an unavoidable byproduct of the normal operation of any electronic devices and leads to higher microprocessor temperature that, if not properly managed, will significantly affect the performance, leakage power, and reliability of microelectronic chip, assembly, and product. Moreover, recent advances in device miniaturization and design complexity are causing highly non-uniform power distribution on the microprocessors, producing "high-flux hot spots". These specific regions on the chip can have a heat flux several times higher than the chip average, and of the order of 1 kW/cm<sup>2</sup>, thus resulting in exceedingly high local temperatures and degrading microprocessor performance and system reliability dramatically (Shakouri 2006). On the other hand, if effective localized cooling of the hot spots can be achieved, the resulting "cold chip" can produce speed gains as large as 200% in some CMOS microprocessors (Tritt 2006). For this reason, mitigating the chip-level hot spot effects through localized cooling has become one of the most significant factors in the design of high-performance electronic products and developed into a primary driver for today's innovation in electronics cooling technology. Due to technical difficulties, the development of efficient cooling technologies to handle such micro-scale high flux hot spots poses a significant challenge in thermal management research and has become a primary roadblock in developing the next generation of microelectronic devices and systems.

Two-phase flow cooling techniques, such as microchannel heat sinks, spray cooling, and pool boiling, provide very high heat transfer coefficients and could be used to meet high-flux cooling requirements as well as provide thermal management in future spacecraft and space stations (Di Marco and Grassi 2002; Silk et al. 2008; Kabov et al. 2007). However, under microgravity conditions, the thermal/fluid characteristics of two-phase systems could significantly differ from that at 1-g condition. Although extensive research has been conducted in this area since the Space Station was proposed, the two-phase heat transfer mechanisms under microgravity environments are still unclear. Therefore, successful use and optimization of two-phase cooling systems for space applications, requires the determination of the as yet unavailable flow patterns, pressure drops, and heat transfer coefficients associated with the flow at microgravity conditions. Because of this lack of understanding, lower power components have to be used in space-based systems since higher power systems requiring the use of two-phase flow has been considered to be risky (Kim 2003). Therefore, the relatively poor understanding of gravity effect on two-phase flow heat transfer has been identified as one of the primary obstacles to reliable design of electronic cooling systems.

Recently advanced miniaturized thermoelectric coolers (TEC's) have received great attention for hot spot thermal management because these solid state devices can offer high reliability, can be locally and selectively applied for spot cooling, can provide high cooling heat flux, can be integrated with IC processing, and is not vulnerable to the gravity effect (Wang et al. 2009; Yang et al. 2007; Wang and Bar-Cohen 2007a, b; Chowdhury et al. 2009; Wang et al. 2006a, b). In this paper, the recent advances of several advanced miniaturized thermoelectric coolers for on-chip hot spot remediation, including mini-contact enhanced TEC's, silicon  $\mu$ TEC's, superlattice TEC's, and miniaturized bismuth telluride TEC's are evaluated.

# **Mini-Contact Enhanced TEC**

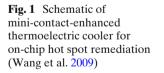

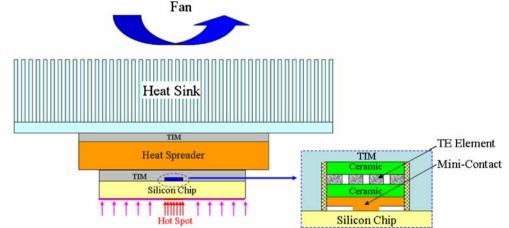

Conventional thermoelectric coolers can only provide a cooling heat flux about 5 to  $10 \text{ W/cm}^2$ , which severely limits the application of these devices to hot spot remediation (Shakouri 2006). Recently, a novel use of a mini-contact pad, which connects the TEC and the silicon chip, thus concentrating thermoelectric cooling power on the top of the silicon chip to significantly improve hot spot cooling performance, was proposed and investigated (Wang et al. 2009; Yang et al. 2007). The physical phenomenon underpinning the use of mini-contact-enhanced thermoelectric coolers is displayed in Fig. 1, where it can be seen that the minicontact pad is used to concentrate the thermoelectric cooling power on the top of the silicon chip. A 3D FEM thermal model was developed and used to determine the efficacy of applying such a mini-contact TEC cooler to a chip with 70 W/cm<sup>2</sup> background heat flux 1250 W/cm<sup>2</sup>, 400  $\mu$ m × 400  $\mu$ m hot spot. Figure 2 shows the temperature profiles that could be achieved along a line bisecting the bottom of the silicon chip, with a 20 µm-high Bi<sub>2</sub>Te<sub>3</sub> legs TEC. When such an advanced miniaturized TEC is activated with 10W and enhanced with a 1,250  $\mu$ m  $\times$  1,250  $\mu$ m mini-contact pad, a 17°C hot spot temperature reduction can be obtained (Wang et al. 2009). However, due to the effect of the heat concentrating/spreading resistance inside the minicontact pad and the silicon chip, this is the "optimum" geometry for this application and if the mini-contact size is extended to 2,400  $\mu$ m  $\times$  2,400  $\mu$ m or reduced to  $600 \ \mu\text{m} \times 600 \ \mu\text{m}$ , the hot spot cooling is decreased to 12°C and 9°C, respectively.

It is also found that achieving low thermal resistance interfaces is critical to the success of mini-contact TEC

137°C

128°C

125°C

120°C

no TEC & no hotspot

no TEC & with hotspot

2400µm mini-contact tip

1250um mini-contact tip

600µm mini-contact tip

<sup>16</sup>AAAAAAAA

140

135

130

125

120

115

110

105

100

Temperature (°C)

20µm thick Bi2Te3 element, R=1x10<sup>-7</sup>m<sup>2</sup>K/W

cooling, since a high thermal resistance at the minicontact/chip interface will significantly reduce the effectiveness of the mini-contact enhancement. Moreover, a poor thermal interface between the TEC and the TIM will impede the conduction of thermoelectric and Joule heat into the heat spreader and then into the heat sink and the ambient, raising the temperature of the TEC. Figure 3 displays the interplay between the thermal contact resistance and the maximum achievable hot

Fig. 3 Influence of thermal contact resistance on hot spot cooling (Bismuth telluride leg thickness is  $20 \ \mu m$  and silicon chip thickness is  $500 \ \mu m$ ) (Wang et al. 2009)

spot cooling, with the assumption of equal thermal contact resistance at the two interfaces (e.g.  $R_{c1} = R_{c2} = R_c$ ), revealing that with increasing thermal contact resistance at both interfaces, the net cooling achievable on the hot spot diminishes. For the typical configuration studied, the mini-contact is seen to provide excellent cooling with interface resistances below  $1 \times 10^{-6} m^2$ K/W but to display diminishing returns as the contact resistances increase and to elevate the hot spot temperatures for thermal contact resistances equal to or above  $1 \times 10^{-5} \text{ km}^2/\text{W}$ .

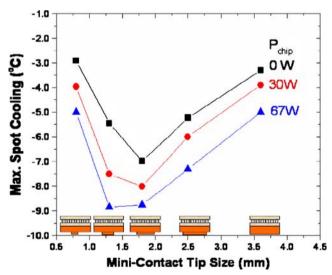

To demonstrate mini-contact enhancement of TEC coolers, 200 µm-thick miniaturized TECs from Thermion (model number: 1MC04-018-02-2200D) (www.thermion-company.com) were tested. The experimentally observed effect of the mini-contact tip size on the temperature reduction at the targeted spot of a uniformly heated chip is displayed in Fig. 4 for three different power dissipations on a 2 mm  $\times$  2 mm  $\times$ 500 µm chip. For the case of no power dissipation on the silicon chip, if the mini-contact is of the same size as the TEC base, the measured maximum spot cooling is about 3.3°C. However, if a 1.8 mm  $\times$  1.8 mm copper mini-contact is integrated onto the TEC, 7.1°C maximum spot cooling can be obtained which results in 115% improvement on spot cooling performance. Similarly, spot cooling performance can be improved by 100% and 80% if the power dissipation of the silicon chip is 30 W and 67 W, respectively.

Recently more advanced 130  $\mu$ m-thick Thermion miniaturized TEC's were used to further test the spot

Fig. 4 Variation of measured spot cooling with copper minicontact size (Bismuth telluride leg thickness of Thermion miniaturized TEC is 130  $\mu$ m and silicon chip thickness is 500  $\mu$ m) (Wang et al. 2009)

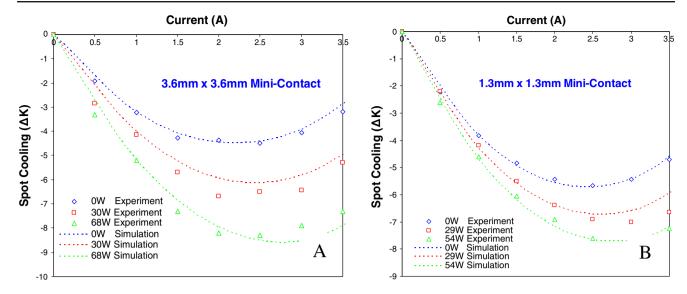

Fig. 5 TEC spot cooling performance with a mini-contact size of **a** 3.6 mm  $\times$  3.6 mm. **b** 1.3 mm  $\times$  1.3 mm (Bismuth telluride leg thickness of Thermion miniaturized TEC is 200  $\mu$ m and silicon chip thickness is 500  $\mu$ m) (Litvinovitch and Bar-Cohen 2009)

cooling capability of a mini-contact TEC. The results displayed in Fig. 5 for 3.6 mm × 3.6 mm and 1.3 mm × 1.3 mm mini-contact sizes, showed very close agreement between the FEM simulations and experiments and revealed that, despite the relatively high contact resistance ( $9 \times 10^{-6}$  m<sup>2</sup> K/W and  $8.5 \times 10^{-5}$ m<sup>2</sup> K/W for the 3.6 × 3.6mm<sup>2</sup> and  $1.3 \times 1.3$ mm<sup>2</sup> mini-contact tests, respectively) significant cooling of nearly 8°C could be achieved with this configuration (Litvinovitch and Bar-Cohen 2009). Using the calibrated FEM model, the effect of the chip thickness and contact resistance

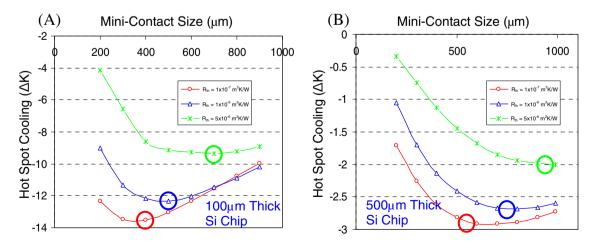

on hot spot cooling performance of the mini-contact TEC was evaluated. As indicated in Fig. 6, for the best thermal interface (with a contact resistance of  $1 \times 10^{-7}$  m<sup>2</sup> K/W) the numerical simulations show that the mini-contact can achieve a maximum of 13.8°C hot spot cooling on a 100 µm thick chip but less than 3°C hot spot cooling on a 500 µm-thick chip. For both chip thicknesses, an increase in the contact resistance to  $5 \times 10^{-6}$  m<sup>2</sup> K/W, decreases the hot spot temperature reduction by approximately 33% and nearly doubles the dimensions of the optimum mini-contact pad.

Fig. 6 Effect of chip thickness and thermal contact resistance on mini-contact enhanced TEC hot spot cooling (Bismuth telluride leg thickness is 20 µm) (Litvinovitch and Bar-Cohen 2009)

#### **In-Plane Silicon Microcooler**

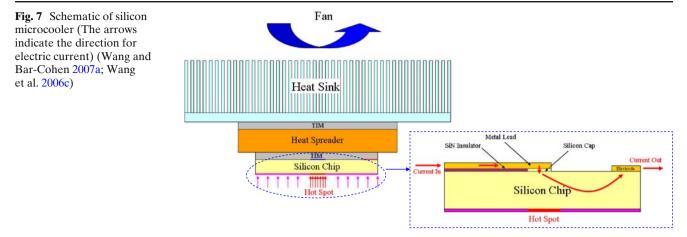

The concept of silicon thermoelectric microcooler for on-chip hot spot cooling, fabricated on the back of the silicon chip, is illustrated in Fig. 7, which displays a single microcooler, activated by an electric current entering the silicon chip through the metal lead and the silicon cap, flowing laterally through the chip, and exiting at the ground electrode located on the periphery of the chip (Wang et al. 2006c). The possible use of silicon microcoolers for the remediation of on-chip hot spots is facilitated by the use of well established metalon-silicon fabrication techniques, yielding a very low thermal contact resistance between the metal and the chip. In addition, incorporation of the silicon chip into the thermoelectric circuit makes it possible to transfer the absorbed energy via the electric current to the edge of the chip, far from the location of the hot spot, thus substantially reducing the detrimental effect of thermoelectric heating on the temperature of the active circuitry.

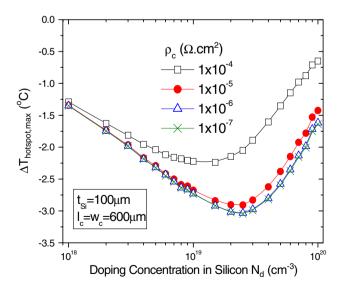

The thermoelectric properties of silicon material are strongly dependent on doping concentration but modestly on the doping type (Herwaarden and Sarro 1986). The variation of maximum hot spot cooling with doping concentration for various microcooler sizes is presented in Fig. 8 for 100  $\mu$ m thick chip with 70 W/cm<sup>2</sup> background heat flux and 680 W/cm<sup>2</sup>, 70  $\mu$ m × 70  $\mu$ m hot spot and the specific electric contact resistance ranging from 1 × 10<sup>-7</sup>  $\Omega$  cm<sup>2</sup> to 1 × 10<sup>-4</sup>  $\Omega$  cm<sup>2</sup>,

**Fig. 8** Hot spot cooling as a function of boron doping concentration for various specific electric contact resistances (Wang and Bar-Cohen 2007a)

Fig. 9 In-plane silicon thermoelectric hot spot cooling as a function of microcooler size and chip thicknesses (Wang and Bar-Cohen 2007a)

S355

revealing that across the range of microcooler sizes studied, with increasing doping concentration the hot spot cooling increases until reaching a maximum value and then decreases with further increases in the doping concentration.

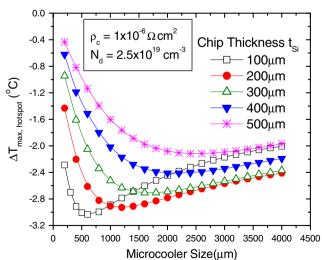

The effect of microcooler size on cooling performance involves the interplay of thermoelectric cooling by the microcooler and thermal diffusion from the hot spot to the microcooler. Figure 9 displays this behavior and shows the temperature reductions at the hot spot for a wide range of microcooler sizes and silicon chips operating under the background and hot spot heat fluxes of 70 W/cm<sup>2</sup> and 680 W/cm<sup>2</sup>, respectively. It is seen that the temperature reduction at the hot spot first increases with microcooler size and, after reaching the maximum value of  $3.0^{\circ}$ C for 600  $\mu$ m  $\times$  600  $\mu$ m microcooler, decreases with a further increase in microcooler size. In the application of silicon microcoolers to hot spot remediation, the silicon chip plays multiple roles, functioning as a thermoelectric material, to provide onchip cooling and, at the same time, as an electrical conductor to transfer electrons from the ground electrode to the microcooler, and as a thermal conductor

to provide a diffusion path for the heat generated in the chip to the ambient. Therefore, the chip thickness influences Joule heating distribution inside the chip, heat spreading from the hot spot, heat diffusion from the hot spot to the microcooler, and heat diffusion from the ground electrode, where Peltier heating occurs, to the hot spot. As the chip becomes thinner, the thermal resistance between the microcooler and the hot spot decreases, allowing the microcooler to achieve greater hot spot temperature reductions, e.g.,  $2.05^{\circ}$ C to  $3.03^{\circ}$ C as the chip thickness decreases from 500 µm to 100 µm, for the conditions of Fig. 9.

Although the in-plane configuration of the silicon does minimize the parasitic effects of "back conduction" (from the hot to the cold side of the TEC), its extremely low ZT value of about 0.01, limits the usefulness of the current silicon microcooler to relatively small high flux "micro" hot spots. Recent breakthroughs in silicon thermoelectrics shows that nanowire structured silicon can reach a ZT value of 0.6 at room temperature and 1.0 at 200 K due to reduction of thermal conductivity (Hochbaum et al. 2008; Boukai et al. 2008). Moreover, it is predicted that it should

Fig. 11 Hot spot heat flux distribution: **a** without microcooler, and **b** with microcooler powered with 0.6 A. (Hot spot size is 70  $\mu$ m × 70  $\mu$ m, chip thickness is 50  $\mu$ m, and microcooler size is 150  $\mu$ m × 150  $\mu$ m) (Wang et al. 2005)

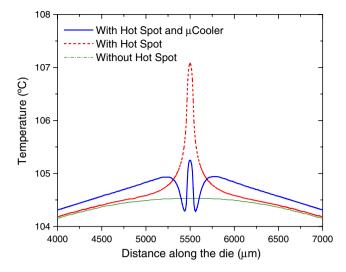

Fig. 12 Temperature profile on the bottom of silicon chip (Silicon chip thickness is 50 µm and the SiGe superlattice microcooler size is  $150 \ \mu\text{m} \times 150 \ \mu\text{m}$ ) (Wang et al. 2005)

be possible to reach even higher values of ZT by optimizing the diameter, doping and other properties of the nanowires. Similar improvements might be possible through the use of functionally-graded doping of the silicon. If such modified silicon nanomaterials can be commercialized and integrated with semiconductor silicon chips, they could enable a dramatic advance in in-plane silicon thermoelectric cooling and make this the technology of choice for thermal management of silicon-based semiconductor devices.

### Si/SiGe Superlattice Microcooler

the TEC attached to the

et al. 2009)

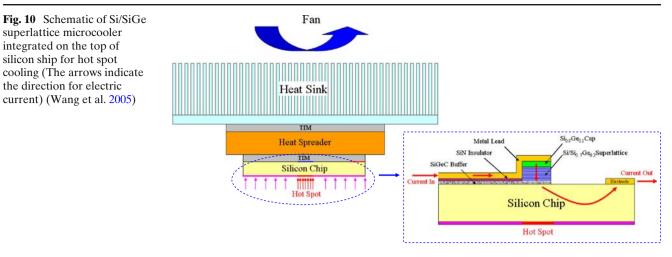

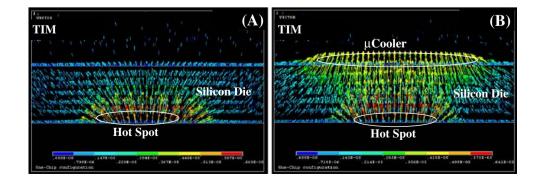

SiGe/Si superlattices have been investigated extensively for more than 15 years due to their unique nanostructure, with very low thermal conductivity and thus high thermoelectric figure of merit, ZT, value. However, there are few reports of the on-chip hot spot cooling potential of SiGe/Si microcoolers when integrated into electronic packaging (Zhang et al. 2005). Bar-Cohen, Shakouri and co-workers pioneered this study using the configuration shown in Fig. 10. The corresponding temperature profile along the bottom (active surface) of the silicon chip (11 mm  $\times$  13 mm  $\times$  $50 \,\mu\text{m}$ ) 70 W/cm<sup>2</sup> background heat flux and 680 W/cm<sup>2</sup>,  $70 \ \mu m \times 70 \ \mu m$  hot spot is illustrated in Fig. 11 (Wang et al. 2005; Litvinovitch et al. 2008). It is observed that when a 3 µm thick Si/SiGe superlattice cooler is integrated onto the top of the silicon chip with an optimized applied current of 0.6 A, the hot spot temperature is reduced by 1.8°C, corresponding 80% reduction of the local temperature rise produced by the 680 W/cm<sup>2</sup>, 70  $\mu$ m  $\times$  70  $\mu$ m hot spot. Figures 11 and 12 show the heat flux profile and temperature profile, respectively, around the hot spot and the Si/SiGe microcooler. It can be seen that when the microcooler is not powered, heat spreading from the hot spot dominates while when the microcooler is operating, the heat flux leaving the hot spot is re-directed towards the microcooler. Their studies revealed that for best effect, the Si/SiGe microcooler should substantially exceed the size of the hot spot, thus, serving to not only directly cool the hot spot but also indirectly reducing the temperature of the surrounding silicon.

# **Bi2Te3 Superlattice Microcooler**

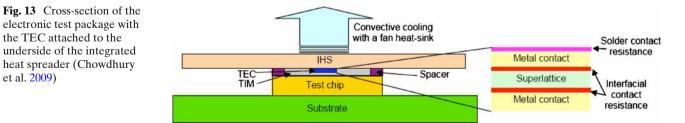

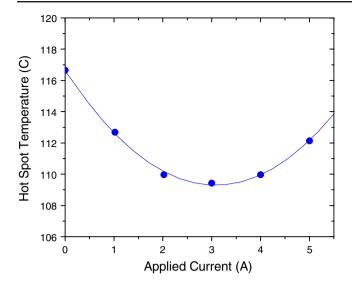

Recently Chowdhury integrated a 100 µm thick Bi<sub>2</sub>Te<sub>3</sub> superlattice cooler into an electronic package to investigate its hot spot cooling capability and the test vehicle is illustrated in Fig. 13 (Chowdhury et al. 2009). The silicon chip background heat flux is 42.7 W/cm<sup>2</sup> and the hot spot is 400  $\mu$ m  $\times$  400  $\mu$ m with a heat flux of 1,250 W/cm<sup>2</sup>. The superlattice TEC consists of ptype Bi<sub>2</sub>Te<sub>3</sub>/Sb<sub>2</sub>Te<sub>3</sub> and n-type Bi<sub>2</sub>Te<sub>3</sub>/Bi<sub>2</sub>Te<sub>2.83</sub>Se<sub>0.17</sub> that were grown by metal-organic chemical vapour deposition (MOCVD) on GaAs substrates. The TEC, with a lateral dimension of 3.5 mm  $\times$  3.5 mm and a total thickness of 100 µm, was then mounted on a heat spreader and embedded into a layer of thermal interface material when integrated into the electronic package. Figure 14 gives the thermoelectric cooling performance on the hot spot, showing that, at the optimum

**Fig. 14** Temperature of the localized high heat-flux region on the chip as a function of current through the thermoelectric cooler (Chowdhury et al. 2009)

current of 3 A, this bismuth–telluride superlattice TEC can offer an impressive temperature reduction of  $7.3^{\circ}$ C of a very aggressive hot spot. The authors noted the strong dependence of the cooling capability of such microcoolers on the interface thermal resistance.

# Conclusion

Recent advances in development of miniaturized thermoelectric coolers for the thermal management of onchip hot spots have been reviewed. A number of novel applications and designs of miniaturized thermoelectric components, ranging from mini-contact enhanced  $\mu$ TECs, through in-plane silicon microcoolers, and on to bismuth-telluride superlattice microcoolers, have been discussed from both modeling and experimental viewpoints. The experimentally-observed temperature reductions and model-based predictions of hot spot cooling have shown that such miniaturized thermoelectric coolers are a potent tool in the remediation of on-chip hot spot effects in advanced semiconductor devices.

## References

- Boukai, A., Bunimovich, Y., Tahir-Kheli, J., Yu, J., Goddard, W. III, Heath, J.R.: Silicon nanowires as efficient thermoelectric materials. Nature 451, 168–171 (2008)

- Chowdhury, I., Prasher, R., Lofgreen, K., Chrysler, G., Narasimhan, S., Mahajan, R., Koester, D., Alley,

R., Venkatasubramanian, R.: On-chip cooling by superlattice-based thin-film thermoelectrics. Nature Nanotechnology, Published online: 25 January 2009. doi:10.1038/nnano.2008.417

- Di Marco, P., Grassi, W.: Motivation and results of a long-term research on pool boiling heat transfer in low gravity. Int. J. Therm. Sci. **41**, 567–585 (2002)

- Herwaarden, A.W., Sarro, P.M.: Thermal sensors based on the Seebeck effect. Sens. Actuators **10**, 321–346 (1986)

- Hochbaum, A., Chen, R., Delgado, R.D., Liang, W., Garnett, E., Najarian, M., Majumdar, A., Yang, P.: Enhanced thermoelectric performance of rough silicon nanowires. Nature 451, 163–167 (2008)

- Kabov, O.A., Chinnov, E.A., Cheverda, V.: Two-phase flow in short rectangular mini-channel. Microgravity Sci. Technol. 19(3–4), 44–47 (2007)

- Kim, J.: Review of reduced gravity boiling heat transfer: US research. J. Jpn. Soc. Microgravity Appl. 20(4), 264–271 (2003)

- Litvinovitch, V., Bar-Cohen, A.: Effect of thermal contact resistance on optimum min-contact TEC cooling of on-chip hot spots. In: Proceedings of the Pacific Rim/ASME International Electronic Packaging Technical Conference and Exhibition (InterPack'09), San Francisco, July 19–23, Paper No. 2009-89289 (2009).

- Litvinovitch, V., Wang, P., Bar-Cohen, A.: Impact of integrated superlattice μ-TEC structure on hot spot remediation. In: Proceedings of the 11th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic System, Orlando, Florida (ITHERM'08), pp. 1231–1241 (2008)

- Shakouri, A.: Nano-scale thermal transport and microrefrigerators on a chip. Proc. I.E.E.E. 94, 1613–1638 (2006)

- Silk, E.A., Golliher, E.L., Selvam, R.P.: Spray cooling heat transfer: technology overview and assessment of future challenges for micro-gravity application. Energy Convers. Manag. 49, 453–468 (2008)

- Tritt, T.M.: Thermoelectric materials, phenomena, and applications: a bird's eye view. MRS Bull. **31**(3), 188–194 (2006)

- Wang, P., Bar-Cohen, A.: On-chip hot spot cooling using siliconbased thermoelectric microcooler. J. Appl. Physi. 102(3), 034503-1-11 (2007a)

- Wang, P., Bar-Cohen, A.: Analysis and simplified thermal model of silicon microcooler for on-chip hot spot thermal management. In: Proceedings of Pacific Rim/ASME International Electronic Packaging Technical Conference and Exhibition (InterPack'07), Vancouver, Canada, July 8–12, Paper No: IPACK2007-33940 (2007b)

- Wang, P., Bar-Cohen, A., Yang, B., Zhang Y., Shakouri, A.: Thermoelectric microcooler for hot spot thermal management. In: Proceedings of the Pacific Rim/ASME International Electronic Packaging Technical Conference and Exhibition (InterPack'05), San Francisco, California, July 17–22, Paper No: IPACK2005-73244 (2005)

- Wang, P., Bar-Cohen, A., Yang, B.: Impact of thermal contact resistance on hot spot cooling using mini-contact enhanced thermoelectric coolers. In: Proceedings of IMAPS Thermal Management 2006, Palo Alto, California, September 10–13, (CDROM) (2006a)

- Wang, P., Bar-Cohen, A., Yang, B.: Multiple silicon-based thermoelectric microcoolers for hot spot thermal management. In: Proceedings of the 13th International Heat Transfer

- Wang, P., Bar-Cohen, A., Yang, B.: Analytical modeling of silicon thermoelectric microcooler. J. Appl. Physi. 100(1), 14501-1-13 (2006c)

- Wang, P., Bar-Cohen, A., Yang, B.: Mini-contact enhanced thermoelectric coolers for on-chip hot spot cooling. Heat Transf. Eng. 30(9), 736–743 (2009)

- Yang, B., Wang, P., Bar-Cohen, A.: Mini-contact enhanced thermoelectric cooling of hot spot in high power devices.

IEEE Trans. Compon. Packag. Technol., Part A **30**, 432–438 (2007)

Zhang, Y., Zeng, G., Shakouri, A., Wang, P., Bar-Cohen, A.: Experimental demonstration of microrefrigerator flip-chip bonded with IC chips for hot spot thermal management. In: Proceedings of the Pacific Rim/ASME International Electronic Packaging Technical Conference and Exhibition (InterPack'05), San Francisco, California, July 17–22, Paper No: IPACK2005-73466 (2005)