# On-Chip Sinusoidal Signal Generators for Electrical Impedance Spectroscopy: Methodological Review

Soon-Jae Kweon, *Member, IEEE*, Ayesha Kajol Rafi, Song-I Cheon, *Graduate Student Member, IEEE*, Minkyu Je, Senior Member, IEEE, and Sohmyung Ha, Senior Member, IEEE

Abstract—This paper reviews architectures and circuit implementations of on-chip sinusoidal signal generators (SSGs) for electrical impedance spectroscopy (EIS) applications. In recent years, there have been increasing interests in on-chip EIS systems, which measure a target material's impedance spectrum over a frequency range. The on-chip implementation allows EIS systems to have low power and small form factor, enabling various biomedical applications. One of the key building blocks of on-chip EIS systems is on-chip SSG, which determines the frequency range and the analysis precision of the whole EIS system. On-chip SSGs are generally required to have high linearity, wide frequency range, and high power and area efficiency. They are typically composed of three stages in general: waveform generation, linearity enhancement, and current injection. First, a sinusoidal waveform should be generated in SSGs. The generated waveform's frequency should be accurately adjustable over a wide range. The firstly generated waveform may not be perfectly linear, including unwanted harmonics. In the following linearity-enhancement step, these harmonics are attenuated by using filters typically. As the linearity of the waveform is improved, the precision of the EIS system gets ensured. Lastly, the filtered voltage waveform is now converted to a current by a current driver. Then, the current sinusoidal signal is injected into the target impedance. This review discusses the principles, advantages, and disadvantages of various techniques applied to each step in state-of-the-art on-chip SSGs. In addition, state-of-the-art designs are compared and summarized.

Index Terms—Bioimpedance, current driver, current injection, impedance measurement, linearity enhancement, sinusoidal waveform generation, spurious-free dynamic range, total harmonic distortion.

Manuscript received January 10, 2022; revised March 29, 2022; accepted April 23, 2022. Date of publication April 28, 2022; date of current version July 14, 2022. This work was supported in part by the National Research Foundation of Korea (NRF) through Basic Science Research Program funded by the Ministry of Education, Republic of Korea, under Grant 2021R1A6A3A03043927, and in part by the DGIST R&D Program of the Ministry of Science and ICT, South Korea, under Grant 21-IJRP-01. This paper was recommended by Associate Editor P. Mohseni. (Corresponding author: Sohmyung Ha.)

Soon-Jae Kweon is with the Division of Engineering, New York University Abu Dhabi, Abu Dhabi 129188, UAE (e-mail: sj.kweon89@nyu.edu).

Ayesha Kajol Rafi is with the Department of Electrical Engineering, Indian Institute of Technology (IIT) Delhi, New Delhi, Delhi 110016, India (e-mail: ayeshakajolrafi8@gmail.com).

Song-I Cheon and Minkyu Je are with the School of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 34141, Republic of Korea (e-mail: 1000thd2@kaist.ac.kr; mkje@kaist.ac.kr).

Sohmyung Ha is with the Division of Engineering, New York University Abu Dhabi, Abu Dhabi 129188, UAE, and with the Tandon School of Engineering, New York University, New York, NY 10012 USA (e-mail: sohmyung@nyu.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TBCAS.2022.3171163.

Digital Object Identifier 10.1109/TBCAS.2022.3171163

# I. INTRODUCTION

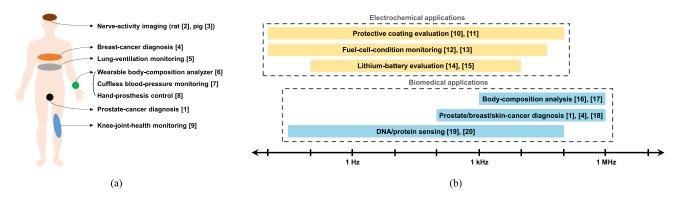

MPEDANCE of biomedical tissues (or bioimpedance) provides with valuable information about the target biomedical material. The bioimpedance of a tissue is a property related to the electrical current flow through the tissue and its ability to store electrical charges, indicating tissue architectures such as cellular size, cellular density, cellular spacing, and the constituents of the extracellular matrix [1]. As a result, the bioimpedance has been widely used as a marker in various medical applications to monitor physiological status, as shown in Fig. 1(a) [1]–[9].

Since the bioimpedance is strongly dependent on the frequency, electrical impedance spectroscopy (EIS), in which the target impedance is measured over a range of frequency, is one of popular techniques not only in biomedical but also in electrochemical fields. It has been widely used for characterizing materials, devices, biological tissues, and so on, as shown in Fig. 1(b) [1], [4], [10]–[20]. In particular, as portable EIS devices are required for some applications, such as wearable body-composition analysis, wearable cancer diagnosis, and other internet-of-thing (IoT) applications, there have been great interests in on-chip EIS systems implemented in the form of integrated circuits (ICs). One of the representative examples of this trend is body-composition analyzers. These analyzers were too large, heavy, and expensive to use personally in the early days of commercialization. However, they have become smaller, lighter, and cheaper. In recent years, even wearable versions of devices, such as smart watches and wrist bands, have emerged as a market trend. These wearable devices should be designed with a small form factor and low power consumption for user convenience and long operating time. On-chip implementation of EIS systems is typically inevitable for such wearable devices.

In EIS, the impedance spectrum can be obtained by two methods: (1) wide-band-signal excitation and (2) single-tone excitation. When a wide-band signal is delivered to the target material, demodulation of the signal obtained from the target material can result in impedance information for a wide band or multiple frequencies at once [21]. Such wide-band signals include white noise [22], chirp [21], [23], maximum length sequences (MLS) [21], differential maximum length sequence (DMLS) [21], and multiple-sine signals [23]. On the contrary, when a single-tone signal is delivered to the target material, the impedance spectrum can be obtained by measuring the impedance for the particular frequency at a time [24], [25]. And then, by repeating the measurements at different frequencies, the impedance spectrum can

Fig. 1. (a) Biomedical applications of impedance measurement and (b) applications of electrical impedance spectroscopy and their required frequency ranges.

be obtained. As such, the wide-band-signal excitation method can obtain the impedance spectrum with a shorter measurement time compared to the method using single-tone stimulus. At the sacrifice of the measurement speed, the single-tone stimulus can achieve a higher signal-to-noise ratio (SNR) than the method using wide-band-signal stimulus [21]. In the single-tone excitation method, the signal power is all concentrated at the single tone, leading to a better measurement sensitivity. As shown, there is a trade-off between measurement speed and sensitivity in EIS systems. The single-tone excitation is suitable for applications that require high sensitivity. Some wearable applications require very small resolution from 1 to 100 m $\Omega_{RMS}$  [21]. In addition, the single-tone excitation method is known to be easier to implement on-chip and has better accuracy [26], [27]. Moreover, widely used commercial impedance analyzer ICs (Texas Instruments AFE4300 and Analog Devices AD5933) also use the single-tone excitation method, and much more numerous researches have focused on achieving better performances with the single-tone excitation method than the wide-band excitation methods.

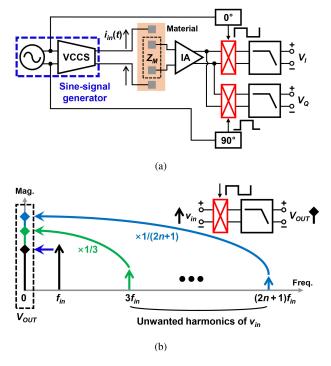

Fig. 2(a) shows a general block diagram of widely used onchip EIS systems based on the single-tone stimulus method [28]– [30]. A sinusoidal signal generator (SSG) injects a sinusoidal current signal into the target material, and a demodulator extracts the real and imaginary parts of the target impedance by quadrature mixing with the in-phase and quadrature-phase (90°-shifted) signals. In another way, a sinusoidal voltage signal can be applied to the target material [31]-[37], but the current-injection method is more common due to the safety issue, especially in biomedical applications. The SSG is one of the key building blocks in on-chip EIS systems because its frequency range and linearity determine the frequency range and precision of the whole EIS system. Since many applications require a wide frequency range over three decades, as shown in Fig. 1, the SSG should have a wide frequency range. When an on-chip EIS system should support several applications, the required frequency range of the SSG should be wider. In order to know the effect of the linearity on the precision of the whole system, we should review the mixing process of general on-chip EIS systems in more detail.

Fig. 2(b) illustrates the down-conversion by the chopper in the frequency spectrum to show the effect of the SSG's linearity to the final impedance results. Since linear multipliers typically consume very large power [29], choppers, which consist of

Fig. 2. (a) Block diagram of general on-chip EIS systems. (b) Error caused by the signal harmonic folding at the frequency mixing stage in the demodulator.

switches only, have been adopted widely for the quadrature multiplications due to their simplicity and low power consumption. The fundamental tone of the input signal at  $f_{in}$  is demodulated and down-converted to DC by multiplication with the demodulation clock signal at the same fundamental frequency. Although the chopper also generates another high-frequency tone at  $2f_{in}$ , the following low-pass filter (LPF) removes this tone. However, when the input signals have odd-order harmonics, the chopper causes errors in the final result due to the odd-order harmonics of the chopper clock. The odd-order harmonics of the input signal are also down-converted to DC by the multiplications with the corresponding odd-order harmonics of the clock signal. The filters after choppers cannot prevent this harmonic-folding error since the folding happens at the mixing stage. To avoid this harmonic-folding error, the SSG should generate a sinusoidal signal with high linearity by suppressing the harmonics as much as possible.

| TABLE I                                                       |

|---------------------------------------------------------------|

| KEY PERFORMANCE PARAMETERS OF REPRESENTATIVE ON-CHIP SSGs FOR |

| THREE DIFFERENT EIS APPLICATIONS                              |

|                         | Implantable EIS | Wearable EIS      | Miniature EIS |  |  |

|-------------------------|-----------------|-------------------|---------------|--|--|

|                         | system [38]     | system [28]       | instrum. [24] |  |  |

| Frequency [Hz]          | 20k             | 0.1k - 100k       | 40m – 40k     |  |  |

| SFDR [dB]               | 65.2            | 59.0              | 63.0          |  |  |

| THD [%]                 | 0.088           | 0.2               | < 0.1         |  |  |

| Power [W]               | $6.2\mu$        | N. R <sup>a</sup> | N. R          |  |  |

| Area [mm <sup>2</sup> ] | 0.059           | 0.74 <sup>b</sup> | 0.64          |  |  |

<sup>&</sup>lt;sup>a</sup>Not reported, but total EIS system consumes 53.4 mW.

Table I shows main performance parameters of on-chip SSGs for the following three applications: implantable EIS systems, wearable EIS systems, and miniature EIS instruments. To minimize the harmonic-folding errors in the impedance measurement, high spurious-free dynamic range (SFDR) and low total harmonic distortion (THD) are needed for all the applications. In many systems, a SFDR of higher than 60 dB and a THD of less than 0.2% have been achieved. For implantable EIS systems, the power consumption should be low. For example, for ensuring the life time of pacemaker over 10 years, the power consumption of the EIS system is required to be less than 10  $\mu$ W [39]. To save the power consumption, implantable EIS systems often support one or a few particular frequencies only at low frequency like the one shown in Table I [38]. In contrast, many wearable EIS systems support a wider frequency range thanks to their higher power budget. As reported in [21], a total power consumption is recommended to be less than 500  $\mu$ W. Miniature EIS instruments are much less restricted by the power consumption, so they can more easily widen the frequency range for supporting various applications. For example, the EIS system in [24], which is for electrochemical applications, is designed to support a wide frequency range of six decades from 40 mHz to 40 kHz. Besides, some EIS systems for biomedical applications are designed to support high frequencies as 10 MHz [30].

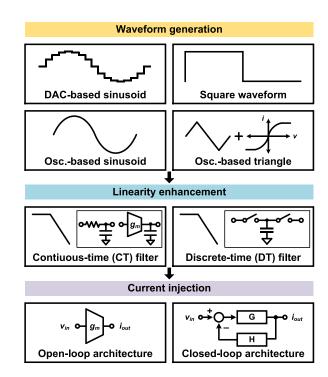

There are several reviews on impedance measurement systems [21], [40]-[43], but they do not provide an in-depth discussion on the architectures and implementation of on-chip SSGs. To fill the gaps, this paper reviews various design techniques in the implementation of on-chip SSGs on the basis of four performance metrics: frequency range, linearity, power consumption, and chip area. On-chip SSGs typically consist of three stages to achieve improved performance metrics: waveform generation, linearity enhancement, and current injection. First, SSGs generate a sinusoidal waveform at a frequency. And the frequency should be easily and accurately controlled over a wide frequency range. Because the generated waveform is not perfect and includes unwanted harmonics, the harmonics should be attenuated further by using filters in the SSG before delivering the sinusoidal signal to the target material. By improving the linearity of the SSG, the harmonics-folding error, which occurs at the mixing stage of demodulator, can be reduced. Lastly, the voltage waveform should be converted to a current signal and injected into the target.

Each of these stages will be reviewed in the remainder of this paper, which is organized as follows. Section II introduces

Fig. 3. Three main stages of on-chip SSGs and representative techniques for each stage.

overall architecture of on-chip SSGs. Sections III, IV, and V review widely used circuits and techniques for waveform generation, linearity enhancement, and current injection, respectively. Section VI concludes the paper with a performance summary of state-of-the-art designs.

# II. OVERALL ARCHITECTURE

Fig. 3 shows three major stages of on-chip SSGs and representative methods of each stage: waveform generation, linearity enhancement, and current injection. Each stage is briefly introduced in this section.

# A. Waveform Generation

First, on-chip SSGs should generate a base waveform. Various waveform generation methods have been demonstrated for on-chip SSGs: digital-to-analog converter (DAC)-based sinusoid, square waveform, oscillator-based sinusoid, and oscillatorbased triangle. The methods based on discrete-time (DT) signals, including the DAC-based sinusoid and the square waveform, are widely used because their fundamental frequency can be easily and accurately controlled by their digital clock frequency. The DAC-based sinusoid is typically generated by a multi-bit-resolution DAC with oversampling. The higher the bit DAC's resolution and oversampling ratio (OSR), the clearer the sinusoidal waveform is generated with smaller harmonics. In contrast, the square waveform can be generated by a simple one-bit DAC, which can be implemented with digital blocks only, with no need for oversampling. While the generation of this square waveform requires much simpler hardware and a lower-speed clock, the DAC-based sinusoid is much better than

bEstimated area.

the square waveform in terms of linearity due to its multi-bit resolution and oversampling.

As alternatives to these discrete methods, sinusoidal waveforms can be generated by using oscillators without any DAC or oversampling. Two types of oscillators have been demonstrated. The first-type oscillators directly generate a sinusoidal signal while the second type, which involves a simpler structure, generates a triangular waveform. This triangular waveform is converted to a sinusoidal signal by a waveform shaper based on the non-linear V-I characteristics of a CMOS differential pair. These oscillator-based signals may achieve better linearity than the DAC-based sinusoids using low OSR and low-resolution DAC. However, frequency control of the oscillator is more difficult than that of DT signals because the oscillation frequency is determined by the oscillator's constituents, which are prone to change by PVT variations. The process variation can cause just a static error in the output frequency, which can be calibrated before the measurement if a reference frequency is given. However, it is still more difficult and complex to precisely control the oscillator's frequency over a wide range than the DT methods based on a clock frequency. In addition, it is difficult for oscillators to achieve a wide frequency range as more than three decades at a given area and power. It is because large-sized passive components are required for generating lowfrequency signals, and large power is required for generating high-frequency signals.

## B. Linearity Enhancement

After the waveform generation stage, the signal may still have unwanted harmonics. Depending on the linearity requirements, these harmonics should be attenuated further. While filters can be used to attenuate the harmonics of continuous-time (CT) signals generated by oscillators, they are more widely used to attenuate the harmonics of signals generated by DT-based methods. The 50%-duty square waveform has large odd-order harmonics, which is expressed as follows:

$$I_{\rm in}(t) = \frac{4}{\pi} \sum_{n=1,3,5,...}^{\infty} \frac{\sin(n \times 2\pi f_{SG}t)}{n}$$

(1)

where  $f_{SG}$  is the fundamental frequency of the signal. The thirdorder harmonic tone is -9 dBc, which is considered very large for most cases. Odd-order harmonics of the DAC-based sinusoid are smaller than those of the square waveform [44], [45], but they need to be attenuated further for high linearity in many cases.

SSGs have adopted two types of filters: CT and DT filters. The CT low-pass filters (LPFs), which is usually made of RC components and  $g_m$  stages, are suitable for attenuating high-order harmonics but not for attenuating low-order harmonics. Note that the error caused by low-order harmonics is larger than that caused by high-order harmonics, as shown in Fig. 2(b). Thus, low-order harmonics of the CT LPF's input signal should be already sufficiently suppressed, or the CT LPF should have high-order attenuation characteristics. Besides, in view of physical implementation, CT LPFs require very small  $g_m$  and/or very large-sized passive components when the EIS system analyzes the material at low frequencies.

In contrast, DT filters, which are based on switched-capacitor circuits, can support low frequencies easily without large-sized passive components. DT filters can easily control the cut-off frequency by changing the sampling frequency, thereby easily achieving low and wide  $f_{SG}$  ranges. Compared to CT LPFs, the DT filters can attenuate low-order harmonics further by using their nulls located at harmonics and/or high-order roll-off.

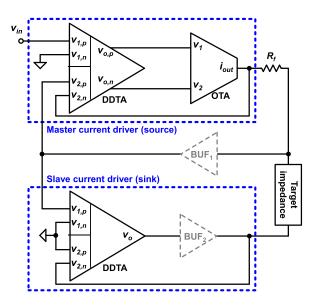

#### C. Current Injection

The generated sinusoidal waveform should be delivered to the target impedance. The delivery can be made in voltage or current. A more detailed comparison between these two methods is well presented in the literature [31], [32]. The voltageexcitation method can support higher  $f_{SG}$  than the currentinjection method in general. The current injection is limited at high frequencies because it is hard to maintain the output impedance at high frequencies due to the output and parasitic capacitances. The current injection is preferred to the voltage excitation in most biomedical applications because it can more effectively prevent the target tissue from damages by unwanted high currents that may happen in the voltage excitation. This safety issue can be prevented by a current limiting resistor in the voltage-excitation method. But, additional read-out circuits are typically required to measure the actual current flowing through the target material. In addition, as the target impedance increases, the flowing current decreases. Then, the magnitude of resulting voltage signal from the target material decreases, degrading the sensitivity of the impedance measurement circuit. In other words, the current injection method is easier to obtain a larger signal magnitude than the voltage excitation method. As such, to avoid the tissue damage while obtaining the maximized signal magnitude, the current injection is preferred to the voltage excitation in most biomedical applications. Since most filters are implemented in the voltage domain, a current driver is needed to convert the voltage signal to current, which can be safely injected into the target material.

There are two important parameters in the implementation of current drivers: output impedance and linearity. The current driver should have a high output impedance to provide a constant current amplitude regardless of the target impedance. In addition, this large output impedance has to be maintained over a wide frequency range to provide a constant current over the entire frequency range. Finally, SSGs should inject the current without degrading the linearity of the sinusoidal signal generated by the waveform generation and linearity enhancement stages.

There are two main architectures of the current drivers in general: open-loop and closed-loop architectures. The open-loop architecture injects the current without feedback, thereby achieving simpler hardware complexity and a wider bandwidth with a given power consumption than the closed-loop ones. In contrast, the closed-loop architecture injects the current with feedback so that it can improve the output impedance and linearity and obtain more reliable transconductance compared to the open-loop ones. Since various current driver circuits are well reviewed in the literature [40], [41], representative and basic structures are briefly reviewed in Section V.

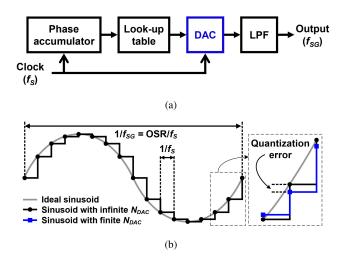

Fig. 4. (a) Block diagram of direct digital synthesizer for generating DAC-based sinusoid [46] and (b) an example DAC-based sinusoid when OSR = 16.  $f_{SG}$  is the frequency of the generated sinusoidal waveform, and  $f_S$  is the sampling frequency. OSR =  $f_S/f_{SG}$ .

## III. WAVEFORM GENERATION

This section reviews four representative waveform-generation methods adopted in SSGs. For each waveform, basic characteristics and various circuit techniques that can improve the overall performance of the on-chip EIS system are discussed. Some techniques verified in off-chip designs are also included if they are applicable to on-chip designs.

#### A. DAC-Based Sinusoid

For the generation of DAC-based sinusoids, direct digital synthesizers (DDSs) are widely used in on-chip EIS systems [35], [36], [39], [47], [48]. Fig. 4(a) shows a block diagram of the most basic DDS architecture [46]. Fig. 4(b) shows an example DAC-based sinusoid when OSR =  $f_{SG}/f_S$  = 16.  $f_{SG}$  is the output sinusoid frequency, and  $f_S$  is the sampling frequency. As the DAC-based sinusoid gets closer to the ideal sinusoid, its harmonics are typically more suppressed. As the OSR increases, more samples reconstruct one sinusoidal period of  $f_{SG}$ . Then, the resulting DAC-based sinusoid becomes closer to the ideal sinusoid with smaller harmonics. Note that DDSs usually operate with a fixed  $f_S$ . Thus, as  $f_{SG}$  increases with a fixed  $f_S$ , the OSR decreases, thereby increasing the harmonics and degrading the linearity. As shown in the inset of Fig. 4(b), deviation of the DAC value from the ideal sinusoid, which is defined as the quantization error, is also a dominant parameter in determining the magnitudes of harmonics. As the number of the quantization levels  $(N_{DAC})$  increases (the DAC's resolution increases), the quantization error gets smaller. To sum up, the DAC-based sinusoid becomes closer to the ideal single-tone sinusoid with better linearity as the OSR and/or  $N_{DAC}$  increase.

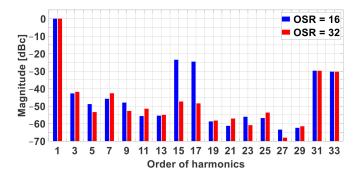

In order to characterize the effect of  $N_{DAC}$  and OSR on the linearity in more detail, a commercial impedance analyzer IC (Texas Instruments AFE4300) is used for the following tests. This IC includes a 6-bit 1-MSps DAC to generate DAC-based sinusoids. Using this IC, two sinusoidal waveforms are generated with OSR or 16 and 32. The corresponding  $f_{SG}$  is 62.5 kHz

Fig. 5. Simulated harmonic magnitudes of a sinusoid generated by a 6-bit DAC with an OSR of 16 and 32.

and 31.25 kHz, respectively. Fig. 5 shows simulated harmonic magnitudes of the sinusoidal signals. By the sampling theorem, the sampling harmonics are generated at  $k \cdot f_S \pm f_{SG}$  where k is an integer number and  $f_S$  is the sampling frequency. Each of these tones' magnitude can be found by using the following transfer function:

$$|H_{sinc}(f)| = \left| \frac{\sin(\pi \cdot f \cdot f_S)}{\pi \cdot f \cdot f_S} \right|.$$

(2)

Among the harmonics for the DAC-based sinusoid with OSR of 16, the 15th, 17th, 31st, and 33th harmonics are generated by the sampling operation, and their magnitudes are determined by (2). Similarly, for OSR = 32, the 31st and 33th harmonics are attributed to the sampling operation. Other harmonics are generated by the DAC's finite resolution.

The linearity of DAC-based sinusoids can be quantitatively evaluated by the signal's SFDR and THD. SFDR is defined as the power ratio of the fundamental signal to the largest harmonic signal. As shown in Fig. 5, the OSR exerts much more influence on the SFDR than  $N_{DAC}$  does because the largest harmonic is determined by the OSR. Therefore, another quantitative metric considering all other harmonics is required to evaluate the effect of the finite  $N_{DAC}$  on the linearity of DAC-based sinusoids. One of such metrics is THD, which is defined as the ratio of the sum of the power of all the harmonics to the power of the fundamental tone. It is useful to show the effect of the finite resolution because THD takes all the harmonics within the frequency range of interest into account. The DAC's finite resolution causes quantization errors between the DAC output signal and the perfect sinusoid, as shown in Fig. 4(b). When the DAC generates a sinusoid signal based on an look-up table (LUT), the quantization errors generate harmonics, not white noise, due to its deterministic characteristic.

Especially, since lower order harmonics cause much larger errors in EIS systems (Fig. 2(b)), it is also necessary to analyze THD considering low-order harmonics only up to ith-order (THD $_i$ ) excluding the sampling harmonics. THD $_i$  can be calculated from SQR $_i$ , which is the signal to the quantization noise power (SQR) when the quantization noise power is calculated over a frequency range from 0 to  $i \cdot f_{SG}$ . Then, THD $_i$  equals -SQR $_i$  in the dB scale and 1/SQR $_i$  in the linear scale. When the DAC utilizes the full scale of the DAC to generate the DAC-based

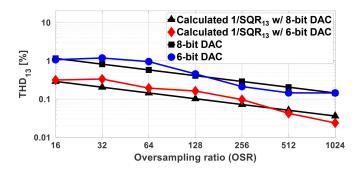

Fig. 6.  $\,$  THD  $_{\!13}$  versus OSR for 8- and 6-bit DAC cases in comparison with the calculated 1/SQR  $_{\!13}.$

sinusoid,  $SQR_i$  is expressed as follows [49]:

$$SQR_i [dB] = 1.76 + 6.02N_{DAC} + 10 \log \left(\frac{OSR}{i}\right)$$

(3)

where OSR - 1 > i. As the OSR increases, the power of quantization noise over the specific frequency range from 0 to  $i \cdot f_{SG}$ decreases because the noise power spectral density decreases. As a result,  $SQR_i$  depends on not only  $N_{DAC}$  but also the OSR. Note that (3) does not include the sampling harmonics. When  $i \geq OSR - 1$ , the sampling harmonics are included within the frequency range of interest, and (3) does not hold. But, for OSR - 1 > i, (3) is useful to quantitatively evaluate the effect of low-order harmonics on the linearity. Fig. 6 shows the calculated  $1/SQR_{13}$  and simulated  $THD_{13}$  for  $N_{DAC}$  of 6 and 8 when the DAC utilizes the full scale of DAC. When a 50%-duty square waveform is injected into the target material instead of a single-tone sinusoidal signal, the summed error caused by the harmonics from the 5th to 13th of the square waveform is also significant compared with that caused by the 3rd harmonic [50]. Thus, i = 13 is chosen here. Since the order of the sampling harmonic is higher than 13 for OSRs higher than 16,  $THD_{13}$  is well-matched with the calculated 1/SQR<sub>13</sub>. THD<sub>13</sub> decreases as either  $N_{DAC}$  or OSR increases.

To sum up, the SFDR is a useful parameter showing the linearity of DAC-based sinusoid when the OSR is the dominant parameter on the linearity, i.e.,  $N_{DAC}$  is high enough. In contrast,  $\mathrm{THD}_i$  is more informative when the quantization error is the dominant parameter on the linearity due to a high enough OSR.

The linearity of a DAC-based sinusoid can be improved by increasing the OSR as shown in Fig. 6. However, as the OSR increases, the hardware gets more complex, and the power consumption increases. More specifically, the number of the sampling points per one sinusoid period increases, requiring a larger memory to store a larger LUT [52]. To reduce the LUT size, adaptive quantizing techniques according to the signal scale can be used [53]–[58]. For example, in [53]–[57], when the current level at a certain sampling point is less than 2/3 of the peak current of the sinusoid, the quantization level is rounded off to the nearest multiple of two of the unit current cell. As a result, the hardware complexity, including the LUT size, is reduced while keeping the low order harmonics less than the magnitude of the 63th harmonic, which is the main

Fig. 7. Operation principle of a sinusoidally tapped resistor DAC for sinusoidal waveform generation. The resistor chain with only eight taps is demonstrated for simplicity. In [51], [52], 33 taps with 1000 unit resistors were used.

harmonic caused by the sampling operation. Similarly in [58], the linearity is further improved by a finer rounded-off. Although the complexity caused by high OSR can be mitigated to some extent by these methods [53]–[58], the maximum  $f_{SG}$  is still limited by the required high clock speed for such high OSR.

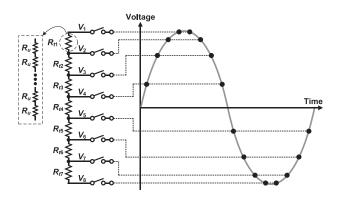

In addition to the OSR,  $N_{DAC}$ , the DAC's resolution, is another dominant parameter in determining magnitudes of the loworder harmonics. As shown in Fig. 6, the linearity is improved by increasing  $N_{DAC}$ . But, at the same time, the required switch control logic of the DAC gets more complex and larger [52]. This results in an increase of the required silicon area occupying the switches and routing lines [52]. In order to reduce the complexity while keeping a target  $N_{DAC}$ , a sinusoidally tapped resistor DAC (RDAC) with a fixed OSR can be used [52]. Fig. 7 briefly describes its overall operation concept. It consists of a resistor chain, which is sinusoidally rationed, and switches. The resistor chain is shown with only eight taps here for simplicity. Note that the OSR is fixed here when  $f_{SG}$  is varied. The switches are just connected to the taps corresponding to each phase while the amplitude corresponding to each phase is fixed. Although this DAC still uses as many unit resistors corresponding to its  $N_{DAC}$ as DACs of DDS, this DAC eliminates the need of connecting switches to all the unit resistors, thereby reducing the number of switches greatly. As shown in Fig. 7, the number of switches is reduced from  $1 + 2^{N_{DAC}}$  to 8 only. The number of switches can be minimized to 0.5OSR.

As shown above, the smaller the OSR is, the lower the complexity of the switching logic and routing lines are required. As the OSR and the number of taps decrease, however, the burden of the following LPF can be increased in many cases to meet a certain linearity target. When the OSR is decreased, the order of the sampling harmonics also gets lower, and their magnitudes get higher according to (2). Consequently, the following LPF is required to have higher attenuation characteristics. Moreover, the cut-off frequency of LPF should be lowered when  $f_{SG}$  decreases. It is hard to implement an LPF that has both a low cut-off frequency and high attenuation characteristic with a small area. Thus, it is important to optimize the OSR and the number of taps. For instance, in [51], [52], a DAC with 33 taps with OSR of 64 and a second-order  $g_m$ -C filter are adopted to generate a single-ended DAC-based sinusoid. Its routing area is decreased

by 87% compared to that of an alternative with 256 taps without an LPF [52]. The  $g_m$ -C filter is chosen because a low cut-off frequency can be implemented with a small area by utilizing a small  $g_m$ . Due to its hardware simplicity, the DAC structure shown in Fig. 7 has been widely adopted in the waveform stage of various on-chip SSGs with OSR from 8 to 32 [59]–[63].

To reduce the burden of LPF, a linear interpolation technique is proposed for a sinusoidally 65-tapped DAC [63]. It employs one additional fine DAC, which interpolates rapidly between two voltage levels that are generated by the main DAC. As the fine DAC's bit resolution improves, the resulting transfer function becomes closer to the square function of (2) [64]. Although the interpolation attenuates the sampling harmonics further, the fine voltage levels should be generated very quickly. Inevitably, the required clock speed of the interpolation DAC is higher than that of typical DAC-based SSGs without interpolation. To address this issue, chain delay lines are used for the interpolation [64]. It can attenuate the sampling harmonics without increasing the required clock speed.

Besides, in order to reduce both unit components and switching logics, DAC-based sinusoids with a small  $N_{DAC}$  and a small OSR have been employed in spite of their large harmonics [38], [44], [45], [50], [65]–[67]. For instance,  $N_{DAC}=3$  [44], [45] and 20 unit cells [65] are adopted with OSR = 16. Although the complexity and area can be reduced thanks to the reduced  $N_{DAC}$  and OSR, these waveforms need sufficiently steep filtering to attenuate not only the sampling harmonics but also the low-order harmonics. Implementation of filters is reviewed in detail in Section IV.

As an alternative technique to generate these DAC-based sinusoids with low  $N_{DAC}$ , delta-sigma modulation (DSM) has been adopted in SSGs [38], [66], [67]. DSM with oversampling reduces the in-band quantization noise by shifting it to the out-band. The shaped out-band noise can be more easily filtered out by an LPF. While an EIS system adopting a single-bit DSM without an explicit LPF is verified using external instruments and board-level design [68], [69], on-chip SSGs based on DSM typically include an LPF to achieve high linearity [38], [66], [67]. A simple RC LPF [66] and a 2nd-order  $g_m$ -C LPF [38] are adopted for attenuating the fast-moving out-band noises, finally generating a cleaner sinusoidal signal. In other way, an FIR-filter-embedded DAC is demonstrated to attenuate the remaining harmonics further while reducing the analog LPF's area [67]. In some works, higher-order multiple-bit DSMs are used to improve the linearity of the output sinusoids instead of using single-bit first-order DSMs. The higher  $N_{DAC}$  and the order of DSM are, the lower the in-band quantization noise becomes. In [38], a capacitor DAC with  $N_{DAC}$  of three and a 3rd-order DSM are used. In addition, a pseudo-random number generator (PRNG), which feeds random values to the digital input signal of the DSM, is adopted for removing the periodicity of the signal generated DSM, thereby spreading the power of harmonics over a frequency range. In summary, by utilizing DSMs in SSGs, better linearity can be achieved. In addition, they need a very low  $N_{DAC}$ , thereby reducing the DAC-related hardware complexity. However, it is difficult to increase  $f_{SG}$ due to high OSR when the system clock speed is limited. For example, in [67], the maximum  $f_{SG}$  is 20 kHz only with  $f_S$  of 2 MHz due to its oversampling.

To adopt a low  $N_{DAC}$  without employing DSM or LPF, a technique to control the transition timings of a DAC with three levels only, i.e., +1, 0, and -1, is proposed [50]. Among the harmonics less than the 10th order, the 5th-order harmonic of the injected signal is suppressed by controlling the transition times between the three levels. In addition, the demodulation signal in the EIS demodulator is also generated with these three levels, now with different transition timings so that the signal's 3rd and 9th-order harmonics are suppressed. Only the 7th-order harmonic remains as an error source among the harmonics less than the 10th order during the demodulation. With this technique, the errors caused by the low-order harmonics are effectively reduced with three voltage levels only. However, it still needs a very fast clock speed  $(30f_{SG})$  to accurately control the transition times between the levels.

#### B. Square Waveform

The square waveform, which is basically a digital clock, is another widely used base waveform in on-chip SSGs due to its simple implementation and low required clock speed. Especially, the 50%-duty-cycle-ratio square waveform has been widely adopted as the base waveform because its even-order harmonics are ideally zero and practically very low. However, it includes significantly large odd-order harmonics. When the 50%-duty square waveform is solely used as the injection signal for the general on-chip EIS system shown in Fig. 2(a), odd-order harmonics of the 50%-duty square waveform are folded to the final output, resulting in significant errors. There are several onchip EIS systems that can accept such errors while targeting low power consumption and simple hardware implementation [70]— [72]. But, most on-chip EIS systems have adopted the square waveform with the following additional techniques to avoid the folded errors: linearity enhancement techniques [24], [73], use of one more down-conversion stage in the demodulator [74]–[80], or error cancellation algorithms [29], [81].

The most straightforward way to adopt the 50%-duty square waveform in on-chip EIS systems is to use some linearity enhancement techniques in the following stage. Filters can attenuate the harmonics of the square waveform. Because the largest harmonic is the 3rd-order harmonic, which is too close to the fundamental tone, a very steep characteristic is required for the filter. Another approach is to add one more down-conversion stage in the demodulator. This additional stage down-converts the input signal from  $f_{SG}$  to an intermediate frequency (IF). By this down-conversion and quadrature demodulation, the harmonics are not folded onto the IF. Then, the second down-conversion is performed from the IF to DC. The remaining down-converted harmonics generated during the two-step down-conversion can be attenuated more easily. More details of the demodulator are well-reviewed in [21]. Finally, simple error-cancellation algorithms, which are based on the fact that the magnitudes of the square waveform's harmonics are known, are demonstrated [29], [81].

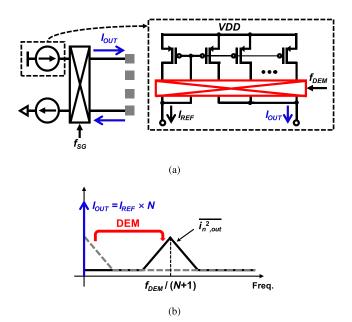

Fig. 8. (a) A square waveform generator based on a single-bit current DAC whose current source employs a dynamic element matching (DEM) technique. (b) Noise characteristics of the square waveform generator with DEM.

In terms of implementation, a single-bit DAC can generate the square waveform. Like DAC-based sinusoids, the square waveform can be generated by resistor-, capacitor-, or current-DACs. Among them, the current DAC has been widely adopted for injecting the square-waveform current directly to the target impedance [70]–[72], [74]–[80]. The SSG's hardware complexity can be greatly reduced by directly injecting the current into the target material without an additional current driver.

Fig. 8(a) shows an example of a single-bit current DAC. It is composed of a sinking current source, a sourcing current source, and a chopper. The chopper operating at  $f_{SG}$  multiplexes the two current sources to generate the square waveform. 1/f noise of the current sources often becomes the bottleneck limiting the measurement sensitivity of the on-chip EIS system for monitoring bioimpedance activities, such as respiration and body fluid change, which ranges less than 10 Hz [76], [77]. The DEM can be adopted to mitigate the 1/f noise, improving the noise performance of the on-chip EIS system. The unit transistors in each current source are swapped sequentially at the DEM frequency  $f_{DEM}$ . Then, 1/f noise of the transistors is up-converted to  $f_{DEM}/(N+1)$ , as shown in Fig. 8(b). N is the current gain of the current mirror. Since the 1/f noise is now far from  $f_{SG}$ , it can be more easily attenuated by using filters in the demodulator. But, the DEM cannot mitigate the noise from  $I_{REF}$ . To address this issue, a correlated noise cancellation technique is proposed and applied to an EIS demoulator [78].

Together with 1/f noise, it is also important to reduce the mismatch between the source and sink current sources in order to prevent the second-order harmonic [70]. The mismatch can be easily mitigated by adopting N=1 with  $f_{DEM}=2f_{SG}$  (Fig. 8) [70], [74]. However, in this case, since the 1/f noise is also up-converted to  $f_{SG}$ , the noise cannot be mitigated. Thus, the square waveform generator in [76] adopts N=5 to mitigate

Fig. 9. Two sinusoidal oscillators based on Wien-bridge architecture: (a) a single-ended design [82], [83] and (b) a fully differential design [5], [28].

the 1/f noise while maintaining good matching characteristics. Here each current source has less than 1% current variation over their target PVT corners.

# C. Oscillator-Based Sinusoidal Waveform

When on-chip EIS systems should support high  $f_{SG}$  with a limited system-clock frequency, the SSGs using oscillators, which do not require oversampling or DAC, can be a good alternative. Moreover, they do not require an LUT, which occupies a large area for a large memory size [52], [84]. Two types of oscillators have been adopted in on-chip EIS systems: RC-controlled and  $g_m$ -C-controlled structures.

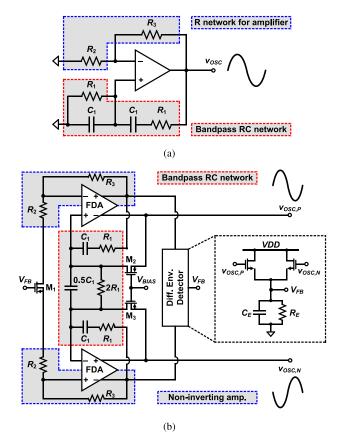

RC-controlled structures, which are based on the Wien-bridge architecture, have been adopted in on-chip EIS systems that target  $f_{SG}$  less than 200 kHz [5], [28], [84]–[86]. Fig. 9(a) shows an example single-ended oscillator based on the Wien-bridge architecture [82], [83]. This oscillator is composed of an operational amplifier, a band-pass RC feedback network, and an R network. The RC feedback network forms a positive feedback loop with the amplifier, making the circuit oscillate. The R network forms negative feedback with the amplifier, amplifying the oscillating signal. The total loop gain of this oscillator in Fig. 9(a),  $T(\omega)$ , is expressed as follows:

$$T(\omega) = \frac{1 + \frac{R_3}{R_2}}{3 + j\left(\omega R_1 C_1 - \frac{1}{\omega R_1 C_1}\right)}.$$

(4)

It oscillates at the frequency when  $|T(\omega)| \ge 1$  and  $\angle T(\omega) = 0$ . Therefore, when  $1 + R_3/R_2$ , which is the gain of the non-inverting amplifier, equals three, the oscillation frequency of the Wien-bridge architecture  $(f_{OSC,WIEN})$  is expressed as follows:

$$f_{OSC,WIEN} = \frac{1}{2\pi R_1 C_1}.$$

(5)

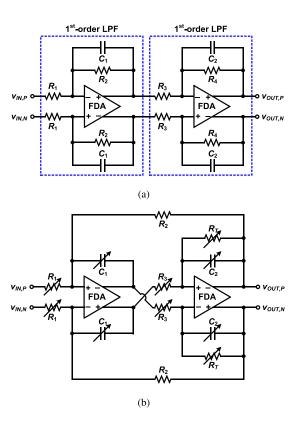

Fig. 9(b) shows a block diagram of an example fully differential sinusoidal oscillator using Wien bridge for on-chip EIS systems [5], [28]. The fully differential design is adopted to suppress the even-order harmonics [85]. The band-pass RC feedback network and the two non-inverting amplifiers based on fully differential amplifiers (FDAs) induce an oscillation at  $f_{OSC,WIEN}$ . In [5], a differential envelope detector restrains the output swing by controlling the oscillator's loop gain. The envelope detector senses the amplitude of the output differential signals, and the sensed amplitude  $(V_{FB})$  is fed to the gate of M<sub>1</sub> so that the gains of non-inverting amplifiers are adjusted. Then, the loop gain is changed accordingly, as shown in (4). In general, the initial gain of the non-inverting amplifiers is set to be greater than three to satisfy the oscillation condition. After starting an oscillation, the loop gain is lowered to stabilize the output swing within the linear output ranges of the FDAs while keeping the oscillation. Here the output swing is set to 200 mV and the 3rd-order harmonic of the output is less than -60 dBc [5]. Without the amplitude-control loop, this SSG has a 3rd-order harmonic of -42 dBc [85]. Although the oscillator shown in Fig. 9(b) achieves high linearity, the envelope detector requires a large-sized capacitor, which is too large to be integrated on-chip. An 1.8-nF off-chip capacitor is used with an 8-M $\Omega$  on-chip resistor, consuming a large area [28]. In order to avoid off-chip components, back-to-back diodes are connected in parallel to the feedback resistors in a replacement of the differential envelope detector and  $M_1$  [86]. Diodes can be integrated inside the chip, but the THD of the oscillator is higher than -60 dBc.

These oscillators generate a sinusoidal signal without oversampling or DAC so that their achievable highest  $f_{SG}$  does not depend on the system clock speed. This makes the oscillatorbased architectures more attractive than the DAC-based SSGs when it is required to generate sinusoids of high  $f_{SG}$  with low system-clock speed. However, these oscillators are not suitable for supporting a wide  $f_{SG}$  range. As shown in (5), the oscillation frequency is inversely proportional to the area of the passive components. Thus, the lowest  $f_{SG}$  is strictly limited by the die area. Furthermore, the highest  $f_{SG}$  is limited by the gain-bandwidth product (GBW) of the amplifiers. The linearity of these oscillators is dependent on the quality (Q) factor of the band-pass filter [86], [87]. Since the Q factor is strongly dependent on the gain of amplifier [84], a large GBW is required to obtain high linearity in the high-frequency region. For example, the FDAs in [84] has 80-MHz GBW to support  $f_{SG}$ up to 76 kHz with 2.38% THD. Similarly in [86], the amplifier has 10-MHz GBW to support  $f_{SG}$  of 100 kHz with THD of less than 1%. As the GBW is required to be about 100 times higher than the target  $f_{SG}$ , the maximum  $f_{SG}$  is limited by the achievable GBW in a given power budget.

Fig. 10. An example  $g_m$ -C sinusoidal oscillator [89].

In addition, precise control of  $f_{SG}$  is much more difficult for the oscillator-based SSGs than other methods. In the oscillator-based SSGs,  $f_{OSC,WIEN}$  is determined by the resistor and capacitor values, which are susceptible to process and temperature variations. Moreover,  $f_{OSC,WIEN}$  is also dependent on the GBW of the amplifier [82], [83]. Note that the GBW can be varied not only by the process and temperature but also by the supply voltage. Thus,  $f_{SG}$  of these types of oscillators is prone to change by PVT variations. Although a technique combining two types of resistors, which have temperature coefficients of opposite signs, is employed in this type of oscillator to reduce the temperature dependency [88], it would still be challenging to obtain  $f_{SG}$  precisely due to other variations.

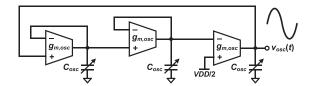

The  $g_m$ -C sinusoidal oscillator shown in Fig. 10 is used for an on-chip EIS system which supports a frequency range from 6.3 MHz to 22.6 MHz [89]. The output sinusoidal voltage  $(v_{osc}(t))$  is expressed as follows [89]:

$$v_{osc}(t) = \frac{I_{SS}}{g_{m,osc}} \sin\left(\frac{g_{m,osc}}{2\pi C_L}t\right)$$

(6)

where  $g_{m,osc}$  and  $C_L$  are  $g_m$  and the load capacitance of the  $g_m$  cell, respectively, and  $I_{SS}$  is the bias current. Since  $g_{m,osc}$  is changed by both the frequency and the amplitude,  $C_L$  is controlled to sweep the oscillation frequency. Similar to the RC-controlled SSC structures, the  $g_m$ -C structure is also hard to achieve wide  $f_{SG}$  range and control  $f_{SG}$  precisely. The maximum  $f_{SG}$  is limited by both the maximum achievable  $g_{m,osc}$  and the bandwidth of the transconductor. Particularly, this structure is considered hard to be adopted in on-chip EIS systems supporting low  $f_{SG}$  because of the large size of the required capacitor and the difficulty in obtaining a small and precise  $g_m$ .  $g_m$  and the capacitance are also prone to change by PVT variations.

#### D. Oscillator-Based Triangular Waveform

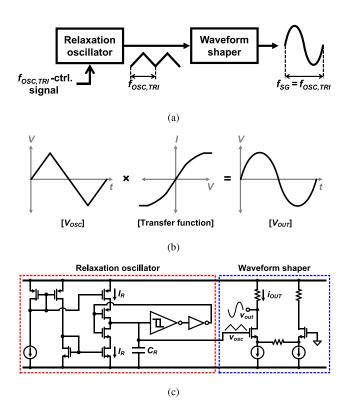

There are many practical difficulties in designing an oscillator that directly generates a sinusoidal waveform over a wide frequency range [90]. In particular, the linearity of the sinusoidal oscillators largely depends on the performance of the amplifiers in the oscillators, and a significantly large GBW is required, limiting the maximum  $f_{SG}$  with a given power budget. To address these issues, techniques based on triangular waveform generation have been proposed to reduce the burden of the oscillator itself, as shown in Fig. 11(a) and (b). Instead of generating a highlinearity sinusoidal signal, a low-linearity triangular waveform is generated first by a relaxation oscillator. Then, the following waveform shaper converts the triangle signal to a sinusoidal signal by using its transfer function, as shown in Fig. 11(b).

Fig. 11. (a) The block diagram of SSGs based on oscillator-based triangular waveform [90]–[92], (b) an operation principle of the waveform shaper [92], [93], and (c) a schematic of the SSG based on oscillator-based triangular waveform for EIS [92].

Various waveform shaper designs have been proposed to obtain a transfer function generating the output as close as the sinusoidal waveform [94]. Their waveform shaping is based on [94]: a polynomial approximation of  $x(1-x^2)/(1+x^2)$  [95], [96], Taylor series expansion with low-order terms [90]–[93], [97], a sum of hypertangent functions [94], [98], [99], or a sum of parabolically spaced exponential functions [100].

Fig. 11(c) shows a schematic of an SSG using a relaxation oscillator for triangular waveform generation [92]. The frequency of the triangular waveform ( $f_{OSC,TRI}$ ) is expressed as follows:

$$f_{OSC,TRI} = \frac{I_R}{2C_R(V_{ST,H} - V_{ST,L})} \tag{7}$$

where  $V_{ST,H}$  and  $V_{ST,L}$  are the upper and lower threshold voltages, respectively.  $f_{OSC,TRI}$  can be controlled by adjusting  $I_R$ ,  $C_R$ , and  $V_{ST,H} - V_{ST,L}$ . Since  $V_{ST,H} - V_{ST,L}$  determines not only  $f_{OSC,TRI}$  but also the amplitude of the triangular waveform,  $V_{ST,H} - V_{ST,L}$  is mainly used for setting the amplitude of the triangular waveform, which determines the amplitude of the output signal. As shown in Fig. 11(b), the peak of the triangular waveform should be slightly saturated by the transfer function for obtaining the sinusoidal signal. Since the source degeneration resistor of the waveform shaper shown in Fig. 11(c) determines the saturation points, it should be properly determined by the target amplitude.

Compared to the DAC-based SSGs, the SSGs based on the triangular waveform have the same advantages as the SSGs

based on sinusoidal oscillators. This method generates a sinusoidal signal without oversampling or DAC. Therefore, it is more suitable than the DAC-based SSGs when it is required to support high  $f_{SG}$  with low system clock speed. However, like the sinusoidal oscillator-based method, this method based on the triangular waveform is not suitable for supporting wide  $f_{SG}$ range and controlling  $f_{SG}$  precisely. The relaxation oscillator and the waveform shaper can easily support several MHz ranges. Therefore, the SSGs based on the triangular waveform are more suitable to support high  $f_{SG}$  than the SSGs based on sinusoidal oscillators. Yet, the lowest  $f_{SG}$  is strictly limited by die area because  $f_{OSC,TRI}$  is inversely proportional to the capacitance as shown in (7). In addition, compared to the DAC-based SSGs, the precise control of  $f_{SG}$  is also more difficult for the SSGs based on the triangular waveform because  $f_{OSC,TRI}$  is determined by the capacitance, resistance, and threshold voltages, which are vulnerable to PVT variations.

The on-chip SSG in [92] achieves 0.41%-THD when  $f_{SG}=1$  MHz. This THD is very close to the THD in [97], which is implemented using discrete MOS transistors, and even higher than  $f_{SG}$  achieved by sinusoidal oscillators in [5] and [28]. However, according to the simulations results in [92], the THD strongly depends on the circuit parameters such as the size of input pairs and the magnitude of current sources in the waveform shaper. The 0.41%-THD is obtained when input pairs are operated in the moderate inversion region, but the THD is degraded to 1.59% when the input pairs are operated in the weak inversion region. Moreover, in order to achieve high linearity by setting appropriate saturation points of the triangular waveform, all the circuit parameters should be set very carefully in consideration of PVT variations.

The SSG in [101] also adopts a triangular waveform as its starting waveform. This SSG uses a bandpass filter for attenuating the harmonics instead of a waveform shaper. By appropriately setting the parameters of the filter, i.e., order, bandwidth, filters can be more effective in the linearity enhancement compared to waveform shapers. Note that odd-order harmonics of the triangular waveform are lower than those of the 50%-duty square waveform. Adopting the triangular waveform makes the requirements of the filter more relaxed or improves the linearity when the same filter is adopted. Although ring oscillators have not been used in SSGs, they could be a good alternative. They also have much simpler hardware than the sinusoidal oscillators. And, they do not use an amplifier. However, the output of ring oscillators is typically similar to a square waveform.

## E. Trade-Offs and Summary

DAC-based sinusoids can achieve high linearity by increasing the OSR and/or  $N_{DAC}$ . However, there is a trade-off between the OSR and  $f_{SG}$  range. With a given clock speed in the system, the maximum  $f_{SG}$  is limited by the clock speed:

$$f_{SG,\max} \le \frac{f_{CLK}}{OSR}$$

(8)

where  $f_{SG,\max}$  is the maximum  $f_{SG}$  that can be obtained with the given clock speed  $f_{CLK}$  and OSR. When  $f_{SG}$  is required to be higher for a given clock speed, the OSR should be reduced. It

makes the resulting sinusoidal output to have a higher sampling harmonics at lower frequencies, demanding a steeper filter. This trade-off is typically not a major issue in implantable and wearable EIS systems that support  $f_{SG}$  of less than several hundred kHz. For example, when a sinusoidal signal at  $f_{SG}$  of 200 kHz is required in implantable or wearable systems, an OSR of 100 can be achieved with a 20-MHz clock, which can be easily available. On the contrary, when the  $f_{SG}$  range needs to be high as several tens of MHz, this trade-off needs to be taken care of. In this case, a much higher clock speed is required, such as several hundreds MHz or higher, increasing the overall power consumption. Alternatively, the OSR should be lowered, requiring a steeper harmonic filtering.

DAC-based sinusoids have another trade-off between  $N_{DAC}$  and the area. As  $N_{DAC}$  increases, number of the unit components and switching logics increase, resulting in an increase of the required silicon area. Some optimization techniques, such as the method using DSM and the sinusoidally tapped DAC, have been demonstrated for reducing the area while maintaining the linearity. The DSM-based method can achieve a high area efficiency. However, it requires a high OSR, so its maximum supporting  $f_{SG}$  is limited by the reference clock speed. In contrast, the sinusoidally tapped DAC can be implemented with a lower OSR between 8 and 64. Thus, this method can support a high  $f_{SG}$  range up to several MHz for miniature EIS instruments. However, both of these methods require an LPF, so their minimum supporting  $f_{SG}$  is limited by the minimum achievable cut-off frequency of the following LPF.

The 50%-duty square waveform does not have the two trade-offs of DAC-based sinusoids since it is designed by a single-bit DAC and can be operated with a low-speed clock. Yet, when a sinusoidal signal is generated from the square waveform after filtering, the frequency range, power, linearity, and area are strongly dependent on the performance of the filter. Therefore, some on-chip EIS systems directly use the square waveform without filtering. Particularly, for wearable EIS systems [76]–[79], the 50%-duty square waveform has been widely used with a demodulator using one more down-conversion stage and an intermediate frequency. This method using an additional down-conversion can reduce the harmonic folding errors compared to the direct conversion to DC.

Sinusoidal oscillators have a trade-off between the maximum supporting  $f_{SG}$  and power consumption due to the requirement of high GBW of the amplifiers. Their lowest supporting  $f_{SG}$ is limited by the area because its oscillation frequency is determined by the passive components. The lower the oscillation frequency, the larger the required area for the components. Therefore, these oscillator-based SSGs have been used in wearable EIS systems covering a  $f_{SG}$  range that is neither too high nor too low, such as from 0.1 kHz to 200 kHz [5], [28], [84], [85]. Moreover, they can support only a few frequencies within the frequency range because the frequency is controlled by changing the component value. For example, the oscillator in [28] only supports four frequencies within the  $f_{SG}$  range from 0.1 kHz to 100 kHz. Triangular-waveform-based relaxation oscillators can relax the trade-off between the maximum supporting  $f_{SG}$ and power consumption to some extent by avoiding the use

Fig. 12. Categorization of linearity enhancement techniques using filters in on-chip EIS systems.

of high-GBW amplifiers. However, when the waveform shaper is used in triangular-waveform-based relaxation oscillators, the linearity is greatly susceptible to the PVT variations. When the triangular waveform is converted to a sinusoidal signal by a filter, the filter specification can be more relaxed than the case using the square waveform as the starting waveform.

#### IV. LINEARITY ENHANCEMENT

Some of the base waveforms like DAC-based sinusoids with low  $N_{DAC}$  and the 50%-duty square waveform are not highly linear intrinsically, including unwanted harmonics. These unwanted harmonics are likely to be folded onto the final impedance measurement result during the impedance demodulation process, causing significant errors in the result, as shown in Fig. 2(b). Hence, these harmonics should be further attenuated for more precise EIS systems.

The linearity of the SSG output waveform can be enhanced typically by filters, which can attenuate the unwanted frequency tones. They have been widely adopted to attenuate the harmonics of DAC-based sinusoids and the 50%-duty square waveform, but they can also be used to further attenuate the harmonics of the waveforms generated by oscillators [101].

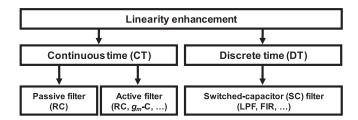

Fig. 12 shows an overall categorization of filters employed in the linearity enhancement stage of on-chip SSGs. They can be largely divided into two types of filters: CT and DT filters. CT filters can be further categorized into two types: passive and active filters. Among passive filters, RC filters are widely employed in many designs because inductors are difficult to be integrated on-chip due to their large size. Active filters, including active RC and  $g_m$ -C filters, have been adopted to control various circuit parameters more easily, such as the gain, the type of frequency response, and Q factor. In general, attenuation of CT LPFs gets smaller as the frequency decreases, so it is difficult for them to attenuate low-order harmonics. Moreover, when the EIS system needs to support a low  $f_{SG}$ , the CT LPF requires a very small  $g_m$  and/or very large-sized passive components.

In order to improve the attenuation of low-order harmonics and offer low cut-off frequencies without large-sized passive components, DT filters based on switched-capacitor (SC) circuits have been employed in SSGs. DT filters can easily control the cut-off frequency by changing the sampling frequency, thereby easily achieving low and wide  $f_{SG}$  ranges. The low-order harmonics can be attenuated further by using the nulls located at the low-order harmonics and/or their high-order roll-off.

The following subsections review various CT and DT filters adopted in on-chip SSGs more in detail. For each filter type, basic characteristics and various circuit techniques that can improve the SFDR or THD of on-chip SSGs are discussed.

# A. Linearity Enhancement in CT Domain

CT filters have been widely adopted in on-chip SSGs [35], [36], [38], [39], [44], [45], [47], [51], [52], [59], [62], [63], [73], [101], [102]. The most simple but fundamental CT filter is passive RC LPFs. RLC or RL filters can be used for SSGs in the board-level design, but these filters are not suitable for on-chip implementation because inductors typically require to occupy a very large chip area. A passive RC LPF is adopted in [45]. Two first-order RC LPFs are cascaded to attain a sufficient degree of attenuation of the harmonics. An unit-gain buffer can be optionally used for ensuring that the response is not affected by the preceding circuit. The resistances and capacitances can be varied for changing the bandwidth of the LPF. In [45], this filter is used to suppress the sampling harmonics of the DT signal with a constant OSR of 16. Here  $f_{SG}$  is varied from 1 kHz to 2.048 MHz, so the location of the largest sampling harmonic is changed from 15 kHz to 30.72 MHz. Attenuation of this harmonic over such a wide range can be done by changing the cut-off frequency of the LPF according to  $f_{SG}$ . In contrast, a constant  $f_S$  can be used with a high OSR while covering a range of  $f_{SG}$  as in [35]. Then, the sampling harmonics are located near the fixed  $f_S$ , so the cutoff frequency of the LPF can be fixed.

Although passive RC filters typically involve simpler implementation, active RC filters have been chosen over passive filters in several cases [47], [62]. Active RC filters can have additional gain and higher Q factor compared to passive ones. A larger output amplitude can be obtained through the additional gain, and the harmonic can be more attenuated through the high Q factor.

As an example, Fig. 13(a) shows a second-order active RC LPF adopted in [47]. The filter consists of two first-order LPFs. Although the frequency response of this active RC LPF can be implemented similarly by using passive LPFs, this active RC LPF can offer a large signal gain. The SSG, which adopts an 8-bit DAC and this active RC filter, attenuates all the unwanted harmonics less than –58 dBc [47].

Fig. 13(b) shows another 2nd-order active RC LPF, which is called Tomas biquad LPF [103]. The biquad LPF can adjust the quality factor (Q factor), bandwidth, and gain. The Q factor of the biquad LPF is expressed as follows:

$$Q = \frac{R_T}{\sqrt{R_2 C_2}} \sqrt{\frac{C_1}{C_2}}.$$

(9)

Here  $R_T$  can be used to change the Q factor while the other values are used for setting the bandwidth and gain. A constant gain in the pass-band region near the cut-off frequency of LPF  $(f_{C,LPF})$  can be achieved by setting the Q factor higher than that of its passive equivalent. When  $f_{C,LPF}$  of each 1st-order LPF in Fig. 13(a) is set to  $f_{SG}$ , the output sinusoidal signal is attenuated by 6 dB. Therefore,  $f_{C,LPF}$  must be higher than  $f_{SG}$  to avoid such amplitude degradation. For example, in [45],

Fig. 13. Example active RC filters: (a) a 2nd-order active RC LPF for an on-chip SSG [47] and (b) a 2nd-order Tomas biquad RC LPF [103].

$f_{C,LPF}$  is chosen as  $2.5 \times f_{SG}$  to reduce the degradation. On the contrary,  $f_{C,LPF}$  of the biquad LPF can be reduced thanks to the constant pass-band by the improved Q factor. Consequently, this structure can achieve better attenuation of the harmonics by locating  $f_{C,LPF}$  close to  $f_{SG}$ . To prevent an overshoot near the  $f_{C,LPF}$ , the Q factor should be appropriately set to about 1. When Q factor equals 1, the resulting overshoot is 0.69 dB.

Both passive and active RC filters cannot offer a low  $f_{C,LPF}$  easily because  $f_{C,LPF}$  of RC filters is inversely proportional to the resistance and capacitance. Bulky resistors and capacitors, which occupy larger areas, are needed to implement a low  $f_{SG}$ . For example, 3-Mohm resistors and 153.6-pF capacitors are used to generate  $f_{SG}$  of 1 kHz in [45]. Note that some EIS applications require generating sinusoidal waveforms of very low frequency (below 1 kHz), as shown in Fig. 1(b). It is not practically possible for passive or active RC filters to support cutoffs lying in such a low-frequency range due to large-sized passive components, which require to occupy a prohibitively large die area. The minimum  $f_{SG}$  of the SSG adopting a passive RC LPF is 1 kHz in [45] and that of SSG adopting the active RC LPF is 15.625 kHz in [47].

Alternatively, active  $g_m$ -C filters have been adopted for decreasing the minimum  $f_{SG}$  with small die area [38], [39], [44], [51], [52], [59], [73], [101], [102]. Fig. 14 shows a 2nd-order biquad  $g_m$ -C LPF, which is adopted in [52].  $f_{C,LPF}$  of this  $g_m$ -C LPF is expressed as follows:

$$f_{C,LPF} = \frac{1}{2\pi} \sqrt{\frac{g_m}{C_1 C_2}}.$$

(10)

Fig. 14. A 2nd-order biquad  $g_m$ -C LPF adopted in [52].

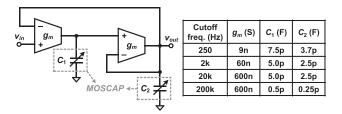

A low  $f_{C,LPF}$  can be implemented by lowering  $g_m$  without the need for bulky resistors and capacitors. The minimum achieved  $f_{C,LPF}$  here is 250 Hz, which is much smaller than that of [45], [47]. Moreover,  $f_{C,LPF}$  of  $g_m$ -C filters can be adjusted by tuning  $g_m$ , which can be more easily controllable than passive components.  $g_m$ -C filters typically occupy a smaller area than the equivalent RC filters for a given order and  $f_{C,LPF}$ . However, in general, the linearity of  $g_m$ -C filters is poorer than that of active RC filters [104]–[106], and thus  $g_m$  cells should be carefully designed not to degrade the linearity of the output.

When CT filters are employed for a waveform whose low-order harmonics are more dominant, the required order gets higher. High-order CT filters need more active circuits and passive components, which result in higher power and area consumption, respectively. For example, in [73], to generate a sinusoidal signal with THD = 1.40% and SFDR = 36.67 dB from the 50%-duty square waveform, a high-order  $g_m$ -C filter which consists of 12  $g_m$  cells and 6 capacitors is required. Similarly in [102], a high-order CT filter, which cascades seven  $g_m$ -C integrators coupled with high-pass filters between the stages, is adopted to achieve THD of –51 dBc and SFDR of 51 dB from the 50%-duty square waveform.

Due to such hardware and power overhead of higher-order CT filters, the 1st-order and 2nd-order CT filters have been more widely used in on-chip SSGs for EIS systems [38], [39], [44], [45], [47], [51], [52], [59], [62], [63], [101]. They occupy less die area and do not consume a lot of power. However, they are not suitable for attenuating low-order harmonics, and thus they have been mainly employed along with DT starting waveforms, of which low-order harmonics are already suppressed by a high-complexity DAC with high  $N_{DAC} \ge 6$  [39], [47], [63] or a large number of unit cells [51], [52], [59], [62]. In addition, DSMs in the waveform generation stage [38], [66], [67] or FIR filters in front of the CT LPF [44], [45] have also been employed for the same purpose. Similarly, a second-order CT filter has been adopted to generate a sinusoidal signal from a triangular waveform, which has smaller low-order harmonics compared to the 50%-duty square waveform [101]. In applications using other waveform generation techniques, additional types of filters have also been used along with low-order CT filters. In such scenarios, the CT filters mainly serve the purpose of attenuating the higher harmonics, which are caused by the sampling operation in DAC-based sinusoids.

Besides, CT filters have two main disadvantages. First, their frequency responses are vulnerable to PVT variations.  $f_{C,LPF}$  of RC filters is determined by the absolute values of the resistance and capacitance. The capacitance is vulnerable to the

process variations, and the resistance is vulnerable to the process and temperature variations. In the case of the  $g_m$ -C filters,  $f_{C,LPF}$  is determined by  $g_m$  and the capacitance.  $g_m$  is very vulnerable to PVT variations. As a result, it is difficult for RC and  $g_m$ -C filters to obtain a precise  $f_{C,LPF}$ . To improve the preciseness, a calibration scheme is required [107]. Second, their low  $f_{C,LPF}$  range is limited by the area occupied by passive components, especially capacitors. Although there is a method that reduces the chip area by adopting an extremely low  $g_m$  of 9 nS and a MOS capacitor [51], [52], these make the filter more susceptible to PVT variations.

# B. Linearity Enhancement in DT Domain

DT filters have been adopted for controlling  $f_{C,LPF}$  precisely, supporting low  $f_{SG}$  ranges, and/or achieving high attenuation of low-order harmonics. Since DT filters are a sampled-data system, its frequency response can be controlled simply by changing  $f_S$ . Note that  $f_S$  can be easily adjusted by digital circuits like dividers with off-chip PVT-tolerant frequency generators, such as crystal oscillators. As such,  $f_{C,LPF}$  of DT filters can be precisely adjusted regardless of PVT variations. In addition, low  $f_{C,LPF}$  can be obtained by just reducing  $f_S$ without increasing the sizes of passive components. Therefore, the area is not one of the main factors that limit the lowest  $f_{SG}$  in DT filters. Moreover, unlike CT filters adopted in on-chip SSGs, DT filters can attenuate low-order harmonics more effectively by implementing high-order roll-off characteristic [24] or using inherent nulls of FIR functions [44], [45]. The remaining part describes how to obtain high-order roll-off and FIR response in the DT domain and use them in the linearity enhancement in SSGs, respectively.

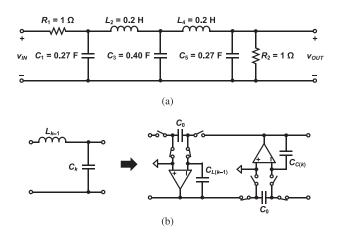

1) Techniques Using High-Order Roll-Off of DT Filters: Large-sized equivalent inductance and capacitance can be implemented by SC integrators with small-size capacitors only, thus allowing a high-order filter with low  $f_{C,LPF}$  to be integrated on-chip. As a result, an SSG that adopts a simple waveform and supports a wide  $f_{SG}$  range can be implemented. Here is an implementation example [24]. By implementing a 5th-order Chebyshev type-I frequency response in the DT domain, even the 50%-duty square waveform, which is the simplest waveform among the starting waveforms of on-chip SSGs, can be adopted. Because this SSG adopts the 50%-duty square waveform,  $f_{C,LPF}$  should be adjusted according to  $f_{SG}$  over the wide frequency range of six decades. Moreover, the filter should attenuate the low-order harmonics sufficiently. Attenuations of 41 dBc and 51 dBc are required to reduce the 3rd-order harmonic of the 50%-duty square waveform to less than 50 dBc and 60 dBc, respectively. A DT filter based on SC integrators can be adopted for achieving such high attenuation of low-order harmonics with wide  $f_{C,LPF}$  range. Such DT filters can be implemented using equivalent LC ladders. Fig. 15(a) shows an LC-ladder-based 5th-order Chebyshev type-I LPF with 1-Hz corner frequency and 0.5-dB pass-band ripple [24]. Although LC values are scaled down as  $f_{C,LPF}$  increases, the values are still too large to be implemented on-chip. Moreover, it is difficult to accurately change the inductances and capacitances

Fig. 15. (a) The 5th-order Chebyshev type-I LPF using LC ladders with 1-Hz  $f_{C,LPF}$  and 0.5-dB pass-band ripple [24] and (b) implementation method of a LC pair with SC circuits [24].

for widely varying  $f_{C,LPF}$ . Alternatively, each LC pair of the LC ladder can be implemented with SC integrators by using the conversion method shown in Fig. 15(b). When  $R_S$ , which is the scaling resistance for calculating the LC values, is set to 1  $\Omega$ , the corresponding on-chip capacitances in the SC integrators are expressed as follows [24]:

$$C_{L(k-1)} = L_{k-1}C_0 f_S (11)$$

$$C_{C(k)} = C_k C_0 f_S \tag{12}$$

where  $L_{k-1}$  and  $C_k$  are the targeted inductance and capacitance of the LC ladder, respectively.  $C_0$  is the unit capacitance of the SC integrators. By using this conversion, large-sized inductors and capacitors can be replaced by SC integrators with small onchip capacitors. When  $C_0=300$  fF and  $f_S/f_{C,LPF}=100$ , the maximum capacitance of 11.4 pF only is needed for designing the 5th-order DT LPF [24]. Thanks to this filter, the SSG achieves <0.1% THD from the 50%-duty square waveform for  $f_{SG}$  from 40 mHz to 40 kHz.

The DT filters based on SC integrators have several advantages likewise. Compared to CT filters, they can accurately obtain  $f_{C,LPF}$  because their equivalent inductance and capacitance  $(L_{k-1} \text{ in } (11) \text{ and } C_k \text{ in } (12))$  depend on  $f_S$  and a capacitor ratio, not on any active or passive components like  $g_m$ , R, or C. Moreover,  $f_{C,LPF}$  can be adjusted by changing  $f_S$  over a wide frequency range. In addition, high-order roll-off and low- $f_{C,LPF}$  filters can be integrated on-chip because large-sized passive components can be implemented by using small-size capacitors.

On the other hand, the DT filters based on SC integrators have two main disadvantages: 1) a trade-off between area and power consumption and 2) difficulty in supporting high  $f_{SG}$  ranges. As shown in (11–12),  $f_S$  should be increased to reduce  $C_{L(k-1)}$  and  $C_{C(k)}$  for given  $L_{k-1}$  and  $C_k$ . As  $f_S$  increases, the bandwidth of the amplifiers in the SC integrators should also be increased to be much larger than  $f_S$ , which results in the increase in the power consumption of the amplifiers. Second, this type of DT filters is not suitable for supporting a high  $f_{SG}$  range with

Fig. 16. Frequency responses of moving average (MA)-2, MA-3, and MA-4 filters

a given  $f_S$  because it needs a high OSR for reducing the area. Moreover, since the required power consumption of amplifiers is proportional to  $f_S$ , there is another trade-off between the power consumption and the maximum  $f_{SG}$ .

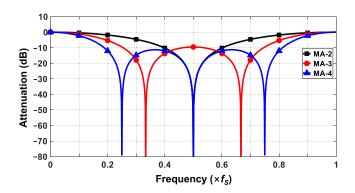

2) Techniques Using Nulls of FIR Functions: Because DT filters based on FIR functions can attenuate the low-order harmonics at a low OSR, they have been adopted to increase the highest  $f_{SG}$  range [44], [45]. In order to see how the FIR functions can attenuate the low-order harmonics with a low OSR, Fig. 16 shows frequency responses of the MA-2, MA-3, and MA-4 filters, which are the basic and representative FIR filters. From 0 to  $f_S$ , the MA-N filters have several nulls at integer multiples of  $f_S/N$ . These frequency responses are repeated for every  $f_S$  according to the sampling theory. These nulls can be used to attenuate the harmonics by locating them exactly at the harmonic frequencies. The null positions can be varied by changing the weights of the input samples [108], [109]. For example, in [108], the null positions are analyzed when three consecutive sample weights are  $[1, \alpha, 1]$ . As shown in Fig. 16, the MA-3 filter of which sample weights are [1, 1, 1] has two nulls at  $f_S/3$  and  $2f_S/3$ . When  $1 < \alpha < 2$ , the null at  $f_S/3$  is moved to a position between  $f_S/3$  and  $f_S/2$ . At the same time, the null at  $2f_S/3$  is also moved to a position between  $f_S/2$  and  $2f_S/3$ . In [109], the required sample weights for attenuating the odd-order harmonics are found for OSR of 6, 8, 10, 12, 14, and 16.

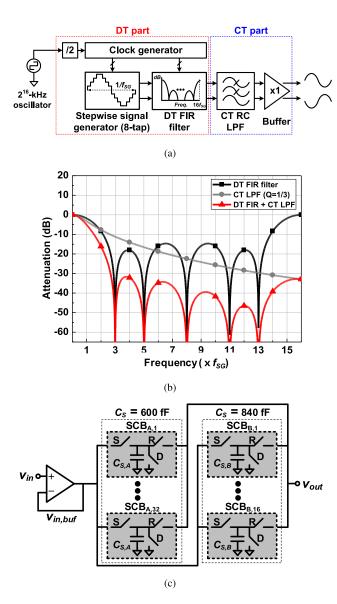

As a practical implementation example, a block diagram of an SSG based on DT FIR filter is shown in Fig. 17(a) [45]. Since the DT filter operating with OSR of 16 can attenuate the low-order harmonics by using the frequency response shown in Fig. 17(b), the SSG can adopt a simple waveform generated by an 8-tap DAC with  $N_{DAC}$  of 3 and OSR of 16. The DT frequency response in Fig. 17(b) is obtained from sample weights of [1, 1, 1.4, 1.4, 1, 1]. The block diagram of the DT FIR filter with these sample weights is shown in Fig. 17(c). The DT FIR filter has nulls at  $3f_{SG}$ ,  $5f_{SG}$ ,  $8f_{SG}$ ,  $11f_{SG}$ ,  $13f_{SG}$ , attenuating the 3rd- and 5th-order harmonics effectively. Although there is no null at  $7f_{SG}$  and  $9f_{SG}$ , the null at  $8f_{SG}$  along with the following CT LPF attenuates the 7th and 9th harmonics by about 35 dB. Therefore, all the low-order harmonics other than 15th harmonic can be suppressed effectively. Since both

Fig. 17. A SSG based on DT FIR filter [45]: (a) a block diagram of the overall architecture, (b) frequency responses of the DT and CT filters, and (c) a block diagram of the DT FIR filter.

the starting waveform and the DT filter operate with OSR of 16, the 15th harmonic still needs to be attenuated further, so the following 2nd-order passive RC LPF attenuates it and other high-order sampling harmonics near the integer multiples of  $f_S$ . In summary, this SSG effectively attenuates the low-order and high-order harmonics using the combination of DT and CT filters so that it can use a simple starting waveform and low OSR. Thanks to the low OSR, this SSG is more suitable for obtaining higher  $f_{SG}$  compared to other SSGs based on SC integrators. On the other hand, since this structure requires a low-order CT filter, the lowest  $f_{SG}$  is limited by the minimum achievable  $f_{C,LPF}$  of the CT filter. This achieves 0.2% THD<sub>10</sub> and 0.7% THD<sub>40</sub> for  $f_{SG}$  from 1 kHz to 2.048 MHz. Since the frequency response of the DT filter can be adjusted by controlling  $f_S$ , a lower  $f_{SG}$  can be supported by replacing the RC filter with a  $g_m$ -C filter.

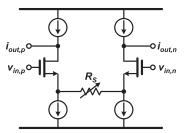

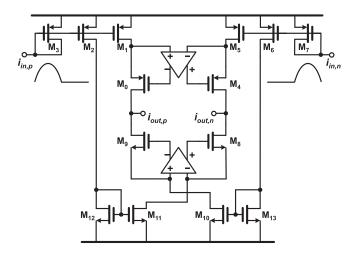

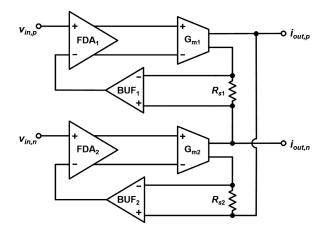

Two other types of DT filters have been adopted for on-chip SSGs [44], [109]. The DT filter in [44] uses a  $g_m$  cell instead of