# On recoverable behavior of PBTI in AlGaN/GaN MOS-HEMT

Eliana Acurio, Felice Crupi, Paolo Magnone, Lionel Trojman, Gaudenzio Meneghesso, Ferdinando Iucolano

### ▶ To cite this version:

Eliana Acurio, Felice Crupi, Paolo Magnone, Lionel Trojman, Gaudenzio Meneghesso, et al.. On recoverable behavior of PBTI in AlGaN/GaN MOS-HEMT. Solid-State Electronics, Elsevier, 2017, 132, pp.49-56. 10.1016/j.sse.2017.03.007 . hal-02952520

# HAL Id: hal-02952520 https://hal.archives-ouvertes.fr/hal-02952520

Submitted on 29 Sep 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## On Recoverable Behavior of PBTI in AlGaN/GaN MOS-HEMT

E. Acurio<sup>1\*</sup>, F. Crupi<sup>1</sup>, P. Magnone<sup>2</sup>, L. Trojman<sup>3</sup>, G. Meneghesso<sup>4</sup>, F. Iucolano<sup>5</sup>

\* E-mail: e.acurio@dimes.unical.it

<sup>1</sup>UNICAL, Università della Calabria, Rende 87036, Italy

<sup>2</sup>Università di Padova, I-36100 Vicenza, Italy

<sup>3</sup>Universidad San Francisco de Quito, Quito, Ecuador

<sup>4</sup>Università di Padova, via Gradenigo 6B, 35131 Padova and IUNET, Italy

<sup>5</sup> STMicroelectronics, Stradale Primosole 50, Catania, Italy

Abstract

This experimental study focuses on the positive bias temperature instability (PBTI) in a fully recessed-gate AlGaN/GaN

MOS-HEMT. A positive stress voltage to the gate results in positive threshold voltage shift ( $\Delta V_{th}$ ), which is attributed to

the trapping of electrons from the GaN layer into the pre-existing oxide traps. The trapping rate exhibits a universal

decreasing behavior as a function of the number of filled traps, independently of stress time, stress voltage, stress

temperature, and device-to-device variability. The stress-induced  $\Delta V_{th}$  can be fully recovered by applying a small

negative voltage, which causes the electron de-trapping. In the explored time window (between 1 s and thousands of s),

the recovery dynamics is well described by the superimposition of two exponential functions associated with two

different traps. Both trap time constants are independent of the stress voltage, decrease with temperature and increase

with the recovery voltage. The activation energy of the slower trap is 0.93 eV, while the faster trap exhibits an activation

energy with a large spread in the range between 0.45 eV and 0.82 eV.

Keywords: PBTI, AlGaN/GaN MOS-HEMT, oxide traps, recessed gate, SiO<sub>2</sub>.

Introduction

In the field of power electronics, there is a continuous requirement of advanced power transistors, enabling to improve the

efficiency and the power density of converters. AlGaN/GaN HEMTs have been recently considered as a possible replacement

to conventional Si-based devices [1]-[4]. Indeed, GaN-based devices benefit of an intrinsic better tradeoff between on-

resistance and breakdown voltage, enabling also the operation at very high frequencies [5]-[8].

The potentiality of GaN HEMT has been largely proved in literature, and although the reliability of such a device is still the

main concern [9][10], commercial power devices are already available. Nevertheless, an important limitation of GaN HEMTs

is their normally-on behavior. Although cascade solutions can be implemented, there is a significant effort in developing

normally-off solutions [11][12]. The device considered in this paper is an AlGaN/GaN MOS-HEMT, in which a metal/oxide/ semiconductor stack is adopted to switch-off the current at zero gate voltage. The performance of AlGaN/GaN HEMTs is typically limited by the current collapse phenomenon, which consists of a current reduction due to the application of a negative stress [13]-[16]. In the case of MOS structure, another important issue affecting device performance is the bias temperature instability (BTI), i.e. a degradation of electrical parameters (such as threshold voltage and charge carrier mobility) induced by the application of high gate voltages and high temperatures. This phenomenon has been extensively studied in CMOS devices for logic applications [17]-[20]. Recently, experimental studies on BTI have been performed also in the case of AlGaN/GaN MOS- or MIS-HEMTs [21]-[27], in order to analyze the impact of different gate dielectrics and to understand the physics associated with the defects responsible of BTI (spatial and energy distribution).

In [21] we have recently conducted a correlation study between 1/f noise and BTI degradation in AlGaN/GaN MOS-HEMTs. We found out that defects originating 1/f noise are responsible for a significant dispersion in the fresh threshold voltage, while different defects (perhaps with different energy or spatial localization) lead to BTI effect. Following the study in [21], this paper aims at carrying out a more comprehensive analysis of BTI on such devices, by evaluating and modeling the influence of stress voltage and temperature on the threshold voltage shift. Moreover, we investigate the time constants and the activation energy of traps involved during BTI. Even though AC measurement techniques have been proposed to capture the behavior of fast traps [28], we focused our work on the study of the slow components of the threshold voltage degradation by using DC characterization.

The remainder of the paper is organized as follows: in Section 2 we provide the details of the devices under test and of the characterization methodology; in Section 3 we report and discuss the results of the experimental analysis; finally in Section 4 the main achievements of the paper are summarized.

#### 2. Experimental

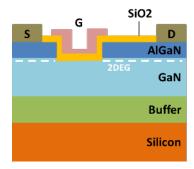

The structure of the AlGaN/GaN MOS-HEMT studied in this work is shown in Fig.1. It is grown Al<sub>0.25</sub>Ga<sub>0.75</sub>N/GaN heterostructure on 150 mm Silicon (111) substrates in a MOCVD reactor. First of all, the ohmic contacts were formed evaporating the Ti/Al-based metallizations and carrying out a rapid thermal annealing at 850 °C [29]. After that, the recession of the AlGaN layer was performed with a dry chemical process based on chlorine to ensure a normally-off operation. The 50 nm-thick SiO<sub>2</sub> layer was deposited by plasma enhanced chemical vapor deposition (PECVD) by using a tetraethyl orthosilicate precursor, followed by a thermal annealing at 850 °C in N<sub>2</sub> [21]. Gate contacts were evaporated on the SiO<sub>2</sub> by using Ni-based metals [30].

In order to study the complete dynamics of the trapping and de-trapping process in our devices, a set of stress-recovery experiments was performed at different stress voltages and temperatures with the parameter analyzer Keithley 4200-SCS. All measurements were done at high temperatures ranging from 75°C to 190°C and with  $V_{DS}$ =50 mV. The threshold voltage is

determined using the fixed current criterion at  $10 \mu A$ . The adopted measurement procedure consists of three phases: initial stabilization, stress, and recovery.

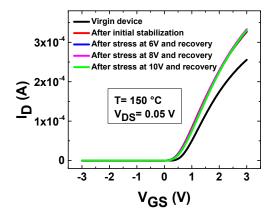

The initial stabilization is performed by applying a negative gate voltage (typically -1 V) for 3000 s. During this phase, the virgin device is stabilized by releasing the charges originally contained in trapping centers [22][23]. It is worth noting that without applying the initial stabilization, positive and negative  $\Delta V_{th}$  were observed in different samples and in different stress conditions, due to the concomitant charge trapping and releasing during the stress. After this phase, we measured a complete  $I_{D}$ - $V_{GS}$  curve sweeping  $V_{GS}$  from -3 V to 3 V. It was necessary to measure the curve up to 3 V, which is significantly higher than  $V_{th}$  in fresh device, in order to be able to measure the  $V_{th}$  after stress also in the case of high  $\Delta V_{th}$  shifts. As shown in Fig. 2, the  $I_{D}$ - $V_{GS}$  curve after the initial stabilization is significantly different from the  $I_{D}$ - $V_{GS}$  curve measured in a virgin device. This stabilization is performed each time that we change the temperature because it allows the device to reach a reproducible reference state for the subsequent experiments. As a matter of fact, after the recovery stage following the stress phase for different stress voltages, the  $I_{D}$ - $V_{GS}$  curve always comes back to this reference state.

During the stress phase, the device is biased with a positive gate voltage ( $V_{stress}$ ) ranging between 6 V and 14 V. Temperatures above 190°C and higher voltages were not used in order to avoid oxide breakdown. In order to monitor the evolution of the stress-induced degradation, the stress was interrupted at fixed time intervals and an  $I_D$ - $V_{GS}$  curve was measured and compared with the reference curve obtained in the stabilization step to calculate  $\Delta V_{th}$ .

Immediately after the stress phase, we executed the recovery phase, by biasing the device with a gate voltage (V<sub>recovery</sub>) ranging between 0 V and -2 V for at least 1000 s. Also in this phase, in order to monitor the recovery evolution, we interrupted the recovery at fixed time intervals and an I<sub>D</sub>-V<sub>GS</sub> curve was measured and compared with the reference curve obtained in the stabilization step. Fig. 2 illustrates that by applying the recovery procedure after the stress, the I<sub>D</sub>-V<sub>GS</sub> curve comes back to the initial stabilized state indicating that no permanent damage was introduced during the stress phase. It is worth noting that the absence of permanent damage is related to the investigated gate voltage values during the stress (6 V to 14 V) and it cannot be extended to higher gate voltages.

#### 3. Results and discussion

#### A. Stress Phase

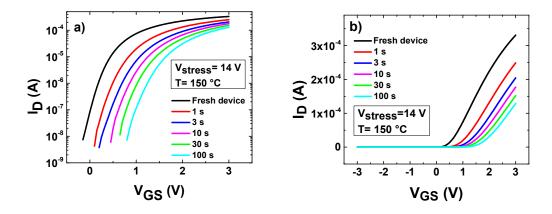

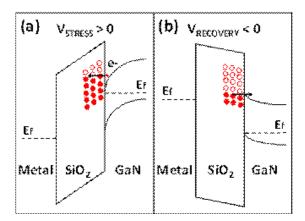

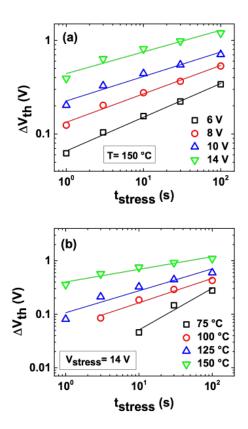

In Fig. 3 we report the evolution of  $I_D$ - $V_{GS}$  curves with stress in the case of a representative sample. It can be seen that after each stress interval, the  $I_D$ - $V_{GS}$  curve moves toward the positive  $V_{GS}$  direction, showing the notorious threshold voltage degradation. The observed  $\Delta V_{th}$  shift can be ascribed to the electron trapping from the channel (under the gate oxide) into the traps located in the  $SiO_2$  energy gap (see Fig. 4 (a)). Fig.5 shows  $\Delta V_{th}$  during the stress at different stress voltages and

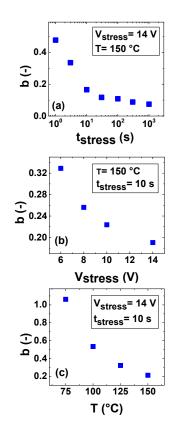

temperatures. In order to determine the  $\Delta V_{th}$  evolution, we evaluated the trapping rate parameter defined as  $b = \frac{\partial \log \Delta V_{th}}{\partial \log t}$ . It can be noted that if b is constant,  $\Delta V_{th}$  evolution follows a classic power law function, i.e.  $\Delta V_{th} = at_{stress}^{b}$  [31][32]. As shown in Fig. 6 (a), the trapping rate parameter significantly decreases during the stress, thus indicating that  $\Delta V_{th}$  evolution does not follow a power law. Fig. 6 (b) and Fig. 6 (c) also illustrates that b considerably declines by increasing stress voltage and temperature.

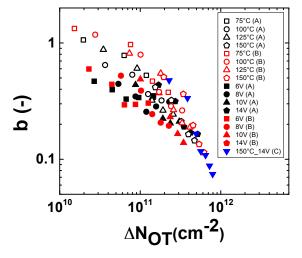

In order to understand the physics behind these phenomena, we plot the trapping rate parameter b, which is a measure of the PBTI charging rate, as a function of the number of trapped charges per unit area,  $\Delta N_{OT}$  (see Fig. 7), for different experimental conditions (i.e. time, voltage and temperature) and different samples. The density of trapped charges has been estimated as  $\Delta N_{OT}$ =  $(C_{OX} * \Delta V_{th})/q$ , where  $C_{OX}$  and q are the oxide capacitance per unit area and the elementary charge, respectively. The overall measurement results illustrate a universal decreasing behavior of the charging rate as a function of the number of filled traps independent of stress time, stress voltage, stress temperature, and device-to-device variability. This trend suggests that the probability of charging traps is associated with the number of available empty traps that exist in the analyzed time window. As an additional cause, this decreasing tendency could be explained by a charge feedback mechanism in which the electrons accumulated near or in the SiO<sub>2</sub>/GaN interface during the stress increase the barrier potential and diminishes the effect of the forward bias [33][34]. The longer the stress, the more the barrier potential is increased and this could be related to the decreasing trend of the trapping parameter b observed in Fig. 6 (a).

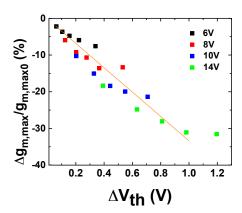

Additionally, we observe a linear correlation by plotting the transconductance variation as a function of the threshold voltage shift for different stress voltages in Fig. 8. This observation suggests that there is also the additional contribution of the charge trapping at the SiO2/GaN interface [23][24], which causes mobility degradation.

#### B. Recovery Phase

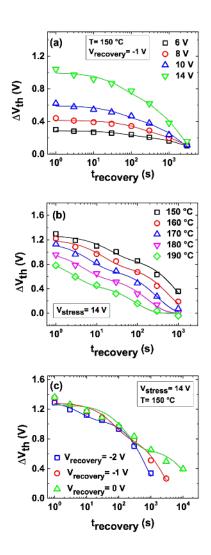

Fig. 9 shows the relaxation data measured after different stress voltages, temperatures and recovery voltages. For a sufficiently high recovery time,  $\Delta V_{th}$  tends to zero, thus indicating that in our experimental conditions no permanent damage was introduced during the stress phase. In other words, the observed PBTI is fully recoverable. The observed  $\Delta V_{th}$  evolution during the recovery phase is ascribed to the release of electrons from the energy states of the SiO<sub>2</sub> band-gap into the GaN layer (see Fig. 4 (b)). Several models have been proposed to describe the BTI relaxation dynamics [35]-[38]. As shown in Fig. 9, we

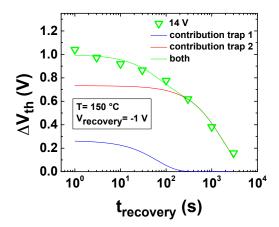

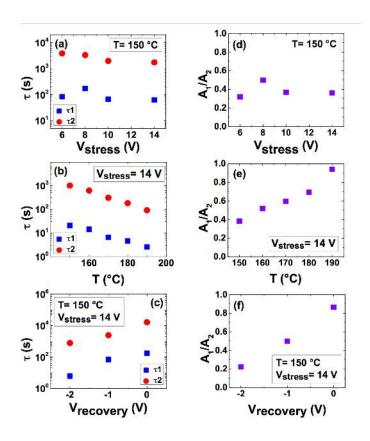

$\Delta V_{th} = A_1 \exp\left(-\frac{t}{\tau_1}\right) + A_2 \exp\left(-\frac{t}{\tau_2}\right)$ considered a simple model based on the superimposition of two exponential functions where  $A_1$  and  $A_2$  represent the amplitudes and  $\tau_1$  and  $\tau_2$  are the time constants. The good agreement between experimental data and fitting lines indicates that in the observed time window (between 1s and thousands of seconds), the recovery dynamics under different conditions is well described by two effective sets of oxide traps located at different energy and/or position [39]. As an example, we can observe the final fitting and the individual contribution of trap 1 and 2 for the recovery data after  $V_{stress}$ =14V in Fig. 10. As shown in Fig. 11 (a), both time constants are independent of the stress voltage (between 6V and 14V). This result suggests that the same sets of traps have been filled independently of the applied stress voltage. From the Fig. 11 (b) it can be seen that the two-time constants strongly decrease with temperature. Furthermore, both time constants decrease with more negative gate voltage (Fig. 11 (c)). As previous studies indicate [16][17], a reverse electric field accelerates the de-trapping process of the charges by enhancing the electron tunneling back to the semiconductor layer. The main limitation of using a negative gate voltage for the recovery is to find the appropriate value to rapidly release charges from the traps without inducing a new stress phase.

In addition, we illustrate the ratio between the two amplitudes which is independent of the stress voltage (Fig. 11 (d)) and gradually increases with temperature (Fig. 11 (e)) and recovery voltage (Fig. 11 (f)). It is worth noting that the ratio less than one implies a dominant trap characterized by time constant  $\tau_2$ .

In general, a wide distribution of time constant is expected for such a device, since a Gaussian distribution of the energy barrier is foreseen for the emission of single defects. Therefore, we tried to fit the relaxation data with a higher number of time constants. By comparing these results with the ones obtained by using only two exponentials, we observe that the data fitting is only slightly improved, but the trends of the time constants are quite noisy and unstable due to the limited set of experimental points. For this reason, we prefer to adopt the parsimonious model with only two effective time constants, but this is a simplified and purely empirical description of the underlying complex physical mechanism behind the BTI relaxation phase.

Furthermore, we evaluated the fitting of the recovery data by using the universal relaxation law [40] with the assumption of a negligible permanent component. The trends of the  $\beta$  parameter (see Eq. 8 in [40]) as a function of experimental parameters (stress voltage, stress temperature and recovery voltage) completely agree with the results obtained by using the sum of two exponentials (clearly, since  $\beta$  measures the recovery speed, the observed agreement means that  $\beta$  shows the opposite behavior of the two-time constants). However, we prefer to adopt the two-time constants model since it shows a better match with the experimental data.

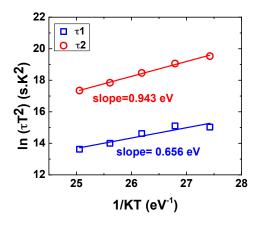

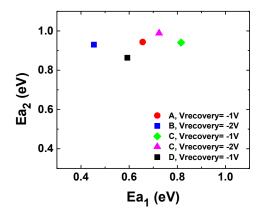

In order to determine the apparent activation energies for the two sets of traps, we used the Arrhenius plot reported in Fig. 12. The two extracted activation energies,  $Ea_1$  and  $Ea_2$ , in diverse samples and by applying different recovery voltages can be found in Fig. 13. On the one hand, the average activation energy of the slower trap ( $Ea_2$ ) is 0.93 eV and this value is almost independent of the recovery voltage and the investigated sample. On the other hand, the estimated value of the activation energy of the faster trap ( $Ea_1$ ) exhibits a significantly higher dispersion, falling in the range between 0.45 eV and 0.82 eV. The larger energy spread is ascribed to the lower accuracy in the evaluation of the time constant of the faster trap, due to the lower amplitude. It is important to highlight that the extracted activation energies are related to the traps that exist in the analyzed time window (1 to 100 s) and cannot be extended to fast traps in the regime of  $\mu$ s and ns.

#### 4. Conclusions

The observed completely recoverable PBTI in AlGaN/GaN MOS-HEMT is ascribed to the initial trapping of electrons from the GaN layer into the traps located in the SiO<sub>2</sub> energy gap (stress phase) and the successive electron de-trapping (recovery phase). The PBTI trapping rate parameter exhibits a universal decreasing behavior during the stress phase as a function of the number of filled traps, independently of stress time, stress voltage, stress temperature, and device-to-device variability. In the observed time window (between 1 s and thousands of s), the recovery dynamics is well described by the superimposition of two exponential functions. Both time constants decrease for more negative recovery voltages and for higher temperatures, while they are stress-voltage independent. Relaxation measurements at different temperatures indicate that the slower trap, which is the dominant, exhibits an average activation energy of 0.93 eV, while the average activation energy of the faster trap shows a large spread in the interval between 0.45 eV and 0.82 eV.

#### Acknowledgment

The research leading to these results was supported by the ENIAC-324280 Energy Efficient Converters using GaN Power Devices (E2COGaN).

#### References

- [1] T. Baltynov, V. Unni, and E. M. S. Narayanan, "The world's first high voltage GaN-on-Diamond power semiconductor devices," Solid. State. Electron., vol. 125, pp. 111–117, 2016.

- [2] S. Yagi, M. Shimizu, M. Inada, Y. Yamamoto, G. Piao, H. Okumura, Y. Yano, N. Akutsu, and H. Ohashi, "High breakdown voltage AlGaN/GaN MIS-HEMT with SiN and TiO2 gate insulator," Solid. State. Electron., vol. 50, no. 6, pp. 1057–1061, 2006.

- [3] O. Seok and M. W. Ha, "AlGaN/GaN MOS-HEMTs-on-Si employing sputtered TaN-based electrodes and HfO2 gate insulator," Solid. State. Electron., vol. 105, pp. 1–5, 2015.

- [4] W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, and I. Omura, "Recessed-Gate Structure Approach Toward Normally Electronics Applications," IEEE Trans. Electron Devices, vol. 53, no. 2, pp. 356–362, 2006.

- [5] F. Schwierz and J. J. Liou, "RF transistors: Recent developments and roadmap toward terahertz applications," Solid. State. Electron., vol. 51, no. 8, pp. 1079–1091, 2007.

- [6] W. Lu, J. Yang, M. A. Khan, and I. Adesida, "AlGaN / GaN HEMTs on SiC with over 100 GHz fT and low microwave noise," IEEE Trans. Electron Devices, vol. 48, no. 3, pp. 581–585, 2001.

- [7] V. Kumar, W. Lu, R. Schwindt, a. Kuliev, G. Simin, J. Yang, M. Asif Khan, and I. Adesida, "AlGaN/GaN HEMTs on SiC with fT of over 120 GHz," IEEE Electron Device Lett., vol. 23, no. 8, pp. 455–457, 2002.

- [8] O. I. Saadat, J. W. Chung, E. L. Piner, and T. Palacios, "Gate-first AlGaN/GaN HEMT technology for high-frequency applications," IEEE Electron Device Lett., vol. 30, no. 12, pp. 1254–1256, 2009.

- [9] G. Meneghesso, G. Verzellesi, F. Danesin, F. Rampazzo, F. Zanon, A. Tazzoli, M. Meneghini, and E. Zanoni, "Reliability of GaN high-electron-mobility transistors: State of the art and perspectives," IEEE Trans. Device Mater. Reliab., vol. 8, no. 2, pp. 332–343, 2008.

- [10] J. A. del Alamo and J. Joh, "GaN HEMT reliability," Microelectron. Reliab., vol. 49, no. 9–11, pp. 1200–1206, 2009.

- [11] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, "Gate injection transistor (GIT) A normally-off AlGaN/GaN power transistor using conductivity modulation," IEEE Trans. Electron Devices, vol. 54, no. 12, pp. 3393–3399, 2007.

- [12] D. S. Kim, K. S. Im, K. W. Kim, H. S. Kang, D. K. Kim, S. J. Chang, Y. Bae, S. H. Hahm, S. Cristoloveanu, and J. H. Lee, "Normally-off GaN MOSFETs on insulating substrate," Solid. State. Electron., vol. 90, pp. 79–85, 2013.

- [13] D. Jin and J. A. Del Alamo, "Methodology for the study of dynamic ON-resistance in high-voltage GaN field-effect transistors," IEEE Trans. Electron Devices, vol. 60, no. 10, pp. 3190–3196, 2013.

- [14] A. Tarakji, G. Simin, N. Ilinskaya, X. Hu, A. Kumar, A. Koudymov, J. Yang, M. Asif Khan, M. S. Shur, and R. Gaska, "Mechanism of radio-frequency current collapse in GaN-AlGaN field-effect transistors," Appl. Phys. Lett., vol. 78, no. 15, pp. 2169–2171, 2001.

- [15] T. Mizutani, Y. Ohno, S. Kishimoto, and K. Maezawa, "A study on current collapse in AlGaN/GaN HEMTs induced by bias stress," IEEE Trans. Electron Devices, vol. 50, no. 10, pp. 2015–2020, 2003.

- [16] S. Arulkumaran, G. I. Ng, C. H. Lee, Z. H. Liu, K. Radhakrishnan, N. Dharmarasu, and Z. Sun, "Study of current collapse by quiescent-bias-stresses in rf-plasma assisted MBE grown AlGaN/GaN high-electron-mobility transistors," Solid. State. Electron., vol. 54, no. 11, pp. 1430–1433, 2010.

- [17] F. Crupi, C. Pace, G. Cocorullo, G. Groeseneken, M. Aoulaiche, and M. Houssa, "Positive bias temperature instability in nMOSFETs with ultra-thin Hf-silicate gate dielectrics," Microelectron. Eng., vol. 80, no. SUPPL., pp. 130–133, 2005.

- [18] B. Kaczer, T. Grasser, P. J. Roussel, J. Franco, R. Degraeve, L. A. Ragnarsson, E. Simoen, G. Groeseneken, and H. Reisinger, "Origin of NBTI variability in deeply scaled pFETs," IEEE Int. Reliab. Phys. Symp. Proc., pp. 26–32, 2010.

- [19] T. Grasser, H. Reisinger, P. J. Wagner, F. Schanovsky, W. Goes, and B. Kaczer, "The time dependent defect spectroscopy (TDDS) for the characterization of the bias temperature instability," IEEE Int. Reliab. Phys. Symp. Proc., pp. 16–25, 2010.

- [20] J. Franco, B. Kaczer, G. Eneman, P. J. Roussel, M. Cho, J. Mitard, L. Witters, T. Y. Hoffmann, G. Groeseneken, F. Crupi, and T. Grasser, "On the recoverable and permanent components of Hot Carrier and NBTI in Si pMOSFETs and their implications in Si0.45Ge0.55 pMOSFETs," IEEE Int. Reliab. Phys. Symp. Proc., pp. 624–629, 2011.

- [21] F. Crupi, P. Magnone, S. Strangio, F. Iucolano, and G. Meneghesso, "Low Frequency Noise and Gate Bias Instability in Normally OFF AlGaN/GaN HEMTs," IEEE Trans. Electron Devices, vol. 63, no. 5, pp. 2219–2222, May 2016.

- [22] T.-L. Wu, D. Marcon, N. Ronchi, B. Bakeroot, S. You, S. Stoffels, M. Van Hove, D. Bisi, M. Meneghini, G. Groeseneken, and S. Decoutere, "Analysis of slow de-trapping phenomena after a positive gate bias on AlGaN/GaN MIS-HEMTs with in-situ Si3N4/Al2O3 bilayer gate dielectrics," Solid. State. Electron., vol. 103, pp. 127–130, Jan. 2015.

- [23] K. Zhang, M. Wu, X. Lei, W. Chen, X. Zheng, X. Ma, and Y. Hao, "Observation of threshold voltage instabilities in AlGaN/GaN MIS HEMTs," Semicond. Sci. Technol., vol. 29, no. 7, p. 075019, 2014.

- [24] A. Guo and J. A. del Alamo, "Positive-bias temperature instability (PBTI) of GaN MOSFETs," in 2015 IEEE International Reliability Physics Symposium, 2015, pp. 6C.5.1–6C.5.7.

- [25] P. Lagger, C. Ostermaier, G. Pobegen, and D. Pogany, "Towards understanding the origin of threshold voltage instability of AlGaN/GaN MIS-HEMTs," Tech. Dig. Int. Electron Devices Meet. IEDM, pp. 299–302, 2012.

- [26] W. Choi, H. Ryu, N. Jeon, M. Lee, N. H. Lee, K. S. Seo, and H. Y. Cha, "Impacts of conduction band offset and border traps on Vth instability of gate recessed normally-off GaN MIS-HEMTs," Proc. Int. Symp. Power Semicond. Devices ICs, no. 2012, pp. 370–373, 2014.

- [27] T. Wu, J. Franco, D. Marcon, B. De Jaeger, B. Bakeroot, S. Stoffels, M. Van Hove, G. Groeseneken, and S. Decoutere, "Toward Understanding Positive Bias Temperature Instability in Fully Recessed-Gate GaN MISFETs," IEEE Trans. Electron Devices, vol. 63, no. 5, pp. 1853–1860, May 2016.

- [28] G. P. Lansbergen, K. Y. Wong, Y. S. Lin, J. L. Yu, F. J. Yang, C. L. Tsai, and A. S. Oates, "Threshold voltage drift (PBTI) in GaN D-MODE MISHEMTs: Characterization of fast trapping components," in 2014 IEEE International Reliability Physics Symposium, 2014, p. 6C.4.1-6C.4.6.

- [29] F. Iucolano, G. Greco, and F. Roccaforte, "Correlation between microstructure and temperature dependent electrical behavior of annealed Ti/Al/Ni/Au Ohmic contacts to AlGaN/GaN heterostructures," Appl. Phys. Lett., vol. 103, no. 20, pp. 0–4, 2013.

- [30] F. Iucolano, C. Miccoli, M. Nicotra, A. Stocco, F. Rampazzo, A. Zanandrea, M. V. Cinnera, A. Patti, S. Rinaudo, F. Soci, A. Chini, E. Zanoni, and G. Meneghesso, "Influence of properties of Si3N4 passivation layer on the electrical

- characteristics of Normally-off AlGaN/GaN HEMT," in The 1st IEEE Workshop on Wide Bandgap Power Devices and Applications, 2013, pp. 162–165.

- [31] M. Cho, J.-D. Lee, M. Aoulaiche, B. Kaczer, P. Roussel, T. Kauerauf, R. Degraeve, J. Franco, L.-Å. Ragnarsson, and G. Groeseneken, "Insight Into N/PBTI Mechanisms in Sub-1-nm-EOT Devices," IEEE Trans. Electron Devices, vol. 59, no. 8, pp. 2042–2048, Aug. 2012.

- [32] S. Mahapatra and M. a. Alam, "A predictive reliability model for PMOS bias temperature degradation," in Digest. International Electron Devices Meeting, 2002, pp. 505–508.

- [33] P. Lagger, C. Ostermaier, and D. Pogany, "Enhancement of Vth drift for repetitive gate stress pulses due to charge feedback effect in GaN MIS-HEMTs," in 2014 IEEE International Reliability Physics Symposium, 2014, no. c, p. 6C. 3.1-6C.3.6.

- [34] P. Lagger, M. Reiner, D. Pogany, and C. Ostermaier, "Comprehensive Study of the Complex Dynamics of Forward Bias-Induced Threshold Voltage Drifts in GaN Based MIS-HEMTs by Stress/Recovery Experiments," IEEE Trans. Electron Devices, vol. 61, no. 4, pp. 1022–1030, Apr. 2014.

- [35] J. Joh and J. A. del Alamo, "A Current-Transient Methodology for Trap Analysis for GaN High Electron Mobility Transistors," IEEE Trans. Electron Devices, vol. 58, no. 1, pp. 132–140, Jan. 2011.

- [36] H. Reisinger, T. Grasser, K. Ermisch, H. Nielen, W. Gustin, and C. Schlunder, "Understanding and modeling AC BTI," in 2011 International Reliability Physics Symposium, 2011, p. 6A.1.1-6A.1.8.

- [37] H. Reisinger, T. Grasser, W. Gustin, and C. Schlunder, "The statistical analysis of individual defects constituting NBTI and its implications for modeling DC- and AC-stress," in 2010 IEEE International Reliability Physics Symposium, 2010, pp. 7–15.

- [38] G. Pobegen and T. Grasser, "On the Distribution of NBTI Time Constants on a Long, Temperature-Accelerated Time Scale," IEEE Trans. Electron Devices, vol. 60, no. 7, pp. 2148–2155, Jul. 2013.

- [39] A. N. Tallarico, E. Sangiorgi, C. Fiegna, P. Magnone, G. Barletta, and A. Magri, "Modeling spatial and energy oxide trap distribution responsible for NBTI in p-channel power U-MOSFETs," in Proceedings of the International Symposium on Power Semiconductor Devices and ICs, 2015, vol. 2015-June, pp. 153–156.

- [40] T. Grasser, W. Gos, V. Sverdlov, and B. Kaczer, "The Universality of NBTI Relaxation and its Implications for Modeling and Characterization," in 2007 IEEE International Reliability Physics Symposium Proceedings. 45th Annual, 2007, pp. 268–280.

#### Figures:

Figure 1: Schematic of AlGaN/GaN MOS-HEMT analyzed in this work.

**Figure 2**: Transfer curves in the linear regime for a virgin device, after the initial stabilization and after successive stress-recovery experiments. No permanent damage is observed for the investigated stress voltages after the recovery phase.

Figure 3:  $I_D$   $_{GS}$  experiments at  $V_{DS}$  electron trapping.

**Figure 4**: Sketch of the band diagram for the stress phase (a) and the recovery phase (b). During the stress phase, electrons from the 2DEG channel are trapped into the oxide traps, while during the recovery phase; electrons are released from the oxide traps.

Figure 5: Experimental (markers) and power law fitting curves (lines) of the  $\Delta V$ th evolution during the stress phase at different stress voltages (a) and temperatures (b). In the investigated time window, an apparently good fit with the classic power law model is observed.

Figure 6: The trapping rate parameter  $b = \frac{\partial \log \Delta V_{th}}{\partial \log t}$  significantly decreases during the stress (a), and by increasing stress voltage (a) and temperature (b).

Figure 7: Trapping rate parameter  $b = \frac{\partial \log \Delta V_{th}}{\partial \log t}$  as a function of the density of trapped charges at different stress voltages and temperatures applied to different samples (A, B and C). A clear universal decreasing behavior is observed.

**Figure 8**: Transconductance variation vs. correlation is observed (straight line).

**Figure 9**: Experimental (markers) and fitting curves based on Eq. 2 (lines) of the phase for different stress voltages (a), temperatures (b) and recovery voltages (c). The fitting curves consist of the superimposition of two exponential functions.

Figure 10: Final fitting and individual contribution of trap 1 and 2 for the recovery data after a stress phase at  $V_{\text{stress}}=14V$ .

**Figure 11**: Both recovery time constants are independent of stress voltage (a), decrease with temperature (b) and increase with recovery voltage (c). The ratio between the two amplitudes is also stress voltage independent (d) and gradually rises with temperature (e) and recovery voltage (f).

**Figure 12**: Arrhenius plot of the characteristic recovery time constants extracted from the exponential fitting during the recovery phase. The two activation energies are obtained by the slope of the fitting lines.

**Figure 13**: Apparent activation energy of the two traps (Ea1 and Ea2) obtained in different samples (A, B, C and D) at different recovery voltages. These values include the acceleration of trapping and de-trapping at the same time while the chuck is maintained at the same temperature during the whole measurement. The activation energy of the faster trap (Ea1) exhibits a lower mean value and a higher dispersion.