Received 19 November 2018; revised 23 January 2019; accepted 5 February 2019. Date of publication 13 March 2019; date of current version 23 August 2019. The review of this paper was arranged by Editor A. Khakifirooz.

Digital Object Identifier 10.1109/JEDS.2019.2902953

# On the Characterization and Separation of Trapping and Ferroelectric Behavior in HfZrO FET

MD. NUR KUTUBUL ALAM<sup>® 1,2</sup>, BEN KACZER<sup>1</sup>, LARS-ÅKE RAGNARSSON<sup>1</sup>, MIHAELA POPOVICI<sup>1</sup>, GERHARD RZEPA<sup>3</sup>, NAOTO HORIGUCHI<sup>1</sup>, MARC HEYNS<sup>1,2</sup>, AND JAN VAN HOUDT<sup>® 1,4</sup> (Fellow, IEEE)

Institute for Microelectronics, IMEC, 3001 Leuven, Belgium

Department of Materials Engineering, KU Leuven, 3000 Leuven, Belgium

Institute for Microelectronics, TU Vienna, 1040 Vienna, Austria

4 ESAT, KU Leuven, 3000 Leuven, Belgium

CORRESPONDING AUTHOR: M. N. K. ALAM (e-mail: md.nur.kutubul.alam@imec.be)

**ABSTRACT** *N*-channel FETs with ferroelectric (FE) HfZrO gate oxide are fabricated, showing steep subthreshold slope under certain conditions. Possible origins of  $I_D-V_G$  hysteresis, the hysteresis versus subthreshold slope tradeoff, dependence on the bias voltage and temperature and the competition between trapping and FE behavior are reported and discussed. A band of active traps in the FE layer responsible for charge trapping during device operation is characterized. Transient  $I_D-V_G$  measurements are introduced to facilitate differentiating between trapping and FE behavior during subthreshold slope measurements.

**INDEX TERMS** Steep-slope FET, ferroelectric FET, trap characterization.

### I. INTRODUCTION

The transfer characteristic of MOSFETs has a fundamental thermodynamic limit in its steepness known as "Boltzmann tyranny" that restricts the minimum possible subthreshold slope to  $\sim 60$  mV/dec at room temperature. In recent years, ferroelectric (FE) FETs have been experimentally demonstrated to break this limit [1]-[8]. Despite such successful demonstrations, some critical challenges need to be addressed for the FEFET to be of use to the industry. Firstly, a FE material is needed to be compatible with the existing CMOS processing technology, i.e., deposited by ALD. In addition, as FE films are known to lose its ferroelectric properties below certain critical thickness, the material to be used must possess its ferroelectricity at a thickness that would allow metal gate and gate dielectric (DE) to fit in the fin-to-fin space and gate trench. Previously, doped HfO<sub>2</sub> has been demonstrated to meet these criteria. However, in doped HfO<sub>2</sub>, the required mole fraction for Si, Al, Y, Gd, La and Sr as a dopant are less than 15% to get the FE phase [9]. Such dopants can be used in the thick FE oxide-based devices but may become impractical in ultra-scaled ones.

In this work we therefore use planar n-channel FEFET fabricated by gate-last process with  $Hf_{0.5}Zr_{0.5}O_2$  FE gate oxide as it is more scalable. Even though the gate stack is not optimized for steep slope operation [10], the devices

show < 60 mV/dec threshold under certain measurement conditions. We discuss possible mechanisms contributing to the device hysteresis, the hysteresis vs. subthreshold slope tradeoff and we report the effect of oxide thickness, lateral scaling, anneal and measurement temperatures, and bias voltage on trapping and polarization behavior [11].

Charge trapping in the gate oxide of FET originates from oxide defects and leads to various degradation effects, such as bias temperature instability (BTI) [12]. These defects can be located at any spatial position within the oxide as well as can have different ionization energies. In this extended work [11] we extract the defect energy band active in our  $Hf_{0.5}Zr_{0.5}O_2$  n-channel FEFET from Non-radiative Multi-Phonon (NMP) theory using BTI-like methodology [13] below the device ferroelectric coercive voltage. Finally, we propose a simple method to separate the trapping and ferroelectric behavior in the FEFET during  $I_D$ - $V_G$  characterization using transient-current measurements.

# **II. EXPERIMENTAL**

The following device fabrication and electrical characterization were employed in this work.

*i) Device fabrication:* We used gate-last process for fabricating planar FEFETs. The high-k oxide of 3nm, 5nm and 8nm thickness has been deposited using ALD, followed by

See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

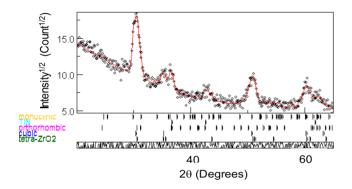

the deposition of 10nm TiN on top of the oxide as gate metal. Finally, to crystallize the oxide, post-metallization-annealing was done at  $500^{0}$ C,  $550^{0}$ C and  $600^{0}$ C. The interfacial SiO<sub>2</sub> layer has a thickness of 0.8nm. Fabricated devices have the dimensions (width  $\times$  gate length) of  $10\mu$ m  $\times 10\mu$ m,  $1\mu m \times 1\mu m$  and  $1\mu m \times 70nm$ . The GIXRD data shown in Fig. 1 confirm that we have properly crystallized oxide. In the 8nm HfZrO, we have  $\sim 40\%$  of the oxide crystallized as orthorhombic phase (the rest are a mixture of other, non-polar phases), needed to induce FE behavior. Al doped HfO<sub>2</sub> based FET was fabricated in which the oxide did not show ferroelectric behavior. To compare the performance of FEFETs, we also fabricated other dielectric (DE) FETs of the same device dimensions with HfO2 and SiO2 as gate oxide. Neither of the reference HfO2 stacks received a high-temperature anneal.

FIGURE 1. GIXRD spectrum showing crystalline phase of 8nm  $Hf_{0.5}Zr_{0.5}O_2$  annealed at 550°C.

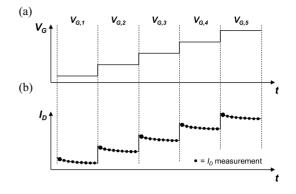

*ii)* Electrical characterization: We performed basic FEFET characterization by measuring the  $I_D$ - $V_G$  transfer characteristics in the linear regime (drain bias  $V_D = 50$  mV), sweeping gate bias  $V_G$  from either 0 to Vm or  $-V_m$  to  $V_m$  and back. Different values of  $V_m$  have been used for the double sweep. For the extraction of defect energy band we used the extended Measurement-Stress-Measurement (MSM) sequence [14]. Finally, as will be discussed in detail below, we have designed a multiple-sweep transient  $I_D$ - $V_G$  measurement, in which the drain current  $I_D$  is measured as a function of time after every  $V_G$  step. Analysis of the  $I_D$  transients facilitates separating trapping and ferroelectric behavior.

#### **III. ORIGINS OF FEFET HYSTERESIS**

Several phenomena are known to cause and impact the FEFET transfer characteristics, particularly its hysteresis and the corresponding threshold voltage shift  $\Delta V_{th}$ .

• In response to the oxide electric field  $E_{ox}$  generated by the application of  $V_G$ , FE dipoles are reoriented along the direction of the field, or in other words, polarize the oxide. When the  $E_{ox}$  field is removed, the FE experiences a depolarization field as it is connected in series with another capacitor that arises from the Si channel [15]–[17]. In addition, presence of non-polar phase in the FE oxide creates the same effect [16]. • In addition to FE polarization, gate-oxide *charging* will typically take place during FEFET operation due to charge carriers tunneling into and out of the insulator preexisting oxide defect centers [18]. Charge trapping/detrapping at the channel side (CS) will generally result in  $\Delta V_{th}$  with the opposite sign from FE polarization (Fig. 2a) as electrons are trapped during the forward  $V_G$  sweep. On the other hand, detrapping of electrons at the gate side (GS) will result in the same sense of hysteresis as FE polarization and may be therefore convoluted or confused with FE polarization switching [19], [20]. When the  $E_{ox}$  field is removed (during reverse sweep), the trapped charge can get de-trapped (Fig. 2b) [20].

**FIGURE 2.** Direction of threshold voltage shift  $\Delta V_{th}$  caused by channel side (CS) and gate side (GS) trapping, detrapping and FE depolarization. At constant  $V_{G}$ , the effects result in change of drain current with time.

• Apart from charge trapping,  $V_{th}$  shift may also arise from ionic motion inside the oxide [21]. This latter mechanism is not considered in this study.

The directions of hysteresis and the impact on the full n-channel FEFET double-sweep  $I_D$ - $V_G$  characteristic are summarized in Fig. 2c.

*Results and discussion:* In this section we show the results obtained from the measurements and discuss the physical origin of the observations. The section is divided into three sections: basic device operation, extraction of the oxide defect bands, and the transient  $I_D$ - $V_G$  technique.

#### A. BASIC DEVICE OPERATION

We start with a fresh ferroelectric FET device, the oxide of which is not woken up by any electric field cycling. Double-sweep  $I_D$ - $V_G$  transfer characteristics of this FEFET

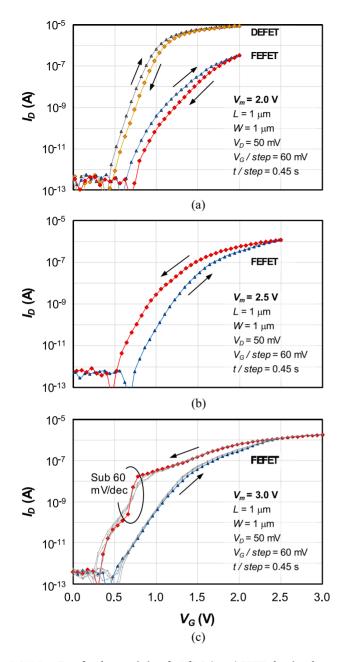

**FIGURE 3.** Transfer characteristics of a HfZrO (8 nm) FEFET showing the effect of the maximum sweep value  $V_m$ . (a) At low  $V_m$ , hysteresis is likely due to CS trapping; (b) at higher  $V_m$ , hysteresis from polarization switching dominates; (c) at even higher  $V_m$ , the same hysteresis sense with steep subthreshold slope is observed. Stress-Induced Leakage Current (SILC) and significant degradation of the gate oxide is observed at even higher values of  $V_m$  (not shown). The results are repeatable shown by light gray lines. (a) A non-ferroelectric HfO<sub>2</sub> (5nm) DEFET characteristic is shown for comparison.

from 0V to  $V_m = 2.0$ , 2.5, and 3.0 V are shown in Fig. 3. Hysteresis in the transfer characteristics is clockwise for  $V_m = 2$  V, which is typical for CS trapping behavior (see Fig. 2). When compared against the non-ferroelectric DEFET, the ferroelectric device shows a larger threshold voltage and a poorer SS. As  $V_m$  is increased, the hysteresis changes direction. This is typically explained as a wakeup (or polarization) of the FE oxide followed by polarization switching. Once the polarization switching dominates, sub 60mV/dec slope is observed but only in the reverse trace of the  $V_G$  sweep. The results are reproducible in repeated measurements.

Since during the forward sweep the FE oxide becomes polarized, it should result in principle in sub 60mV/dec slope as well. We assume that progressive trapping of channel electrons during forward sweep causes a positive shift in  $V_{th}$ , which in turn results in poor SS [22]. During the reverse sweep, the depolarization field increases with decreasing  $V_G$ . In addition to that, CS electron de-trapping from oxide defect states takes place in the reverse trace. As a consequence, the steep SS in the reverse trace is observed.

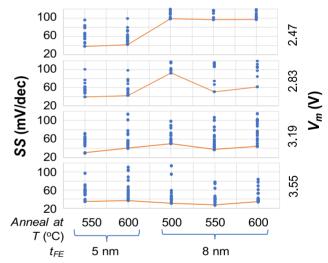

Figure 4 shows the subthreshold slope (SS) obtained in the reverse  $V_G$  trace for different oxide thicknesses, anneal temperatures of the oxide, and for different values of  $V_m$ . It is clearly noticed that as the  $V_m$  value increases, the minimum value of SS decreases below 60 mV/dec for all reported samples.

**FIGURE 4.** Subthreshold slope SS for different oxide thicknesses, anneal temperatures, and  $V_m$ . Red lines connect the minimum values at each  $V_m$ . 3nm HfZrO does not manifest steep SS in the measured range (not shown).

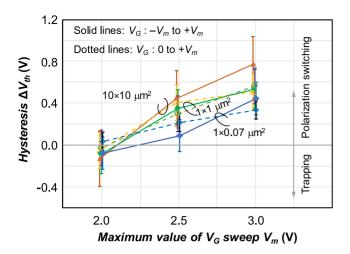

Figure 5 reports the scalability of the device—the average value of hysteresis is plotted, along with its standard deviation for different values of  $V_m$ , for different device dimensions (width × gate length). Although there is some distribution in the data, the trend clearly shows polarization switching behavior dominates over trapping behavior as  $V_m$ increases, down to  $L_g = 70$  nm.

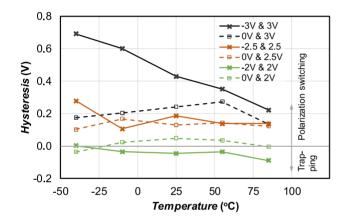

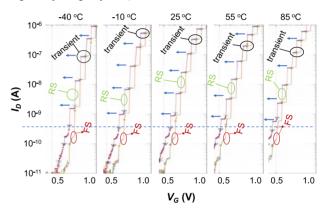

In Fig. 6 it is seen that at lower temperatures the FE behavior gets stronger. We assume that it is because fewer oxide traps are filled, as gate oxide trapping is a thermally activated process. This leads to a weaker influence of trapping phenomena over the FE behavior.

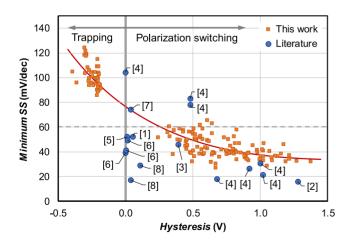

Our data also indicate a clear hysteresis vs. SS tradeoff, shown in Fig. 7. Specifically, we observe that the lower the SS value, the higher the hysteresis and vice versa. The link

**FIGURE 5.** Hysteresis of FEFET for different device dimensions as a function of  $V_m$ , documenting all device dimensions show stronger FE polarization at larger  $V_m$ .

**FIGURE 6.** Hysteresis of FEFET for different V<sub>G</sub> sweep ranges as a function of temperature, showing the FE polarization becomes stronger at lower temperature.

**FIGURE 7.** Hysteresis vs. subthreshold slope tradeoff matches well the trend observed in the literature. The line is a guide to the eye.

between SS and hysteresis could lie in  $V_m$ . We see that in order to get lower SS, higher  $V_m$  is needed. But higher  $V_m$  will result in more polarization and a higher hysteresis. We

cross check this correlation against other published works by different groups and find a similar trend.

We note that, e.g., Lee *et al.* [6] showed nearly zero hysteresis with sub-60mV/dec switching; their result, however, was found to be dependent on measurement speed. It is already established that trapping is a transient phenomenon—the longer the measurement time the more trapping occurs in the oxide. Consequently, variation of measurement speed leads to a variation of the net trapped charge and a subsequent variation of the trapping component of  $\Delta V_{th}$ . Note in Fig. 2 the trapping and depolarization give  $\Delta V_{th}$  of opposite sign. It is therefore possible that at a right measurement speed, the two components compensate each other, giving apparently zero hysteresis. In fact, with the increase in measurement speed Lee *et al.* [6] observed larger hysteresis in counter-clockwise direction (less trapping / more depolarization).

#### **B. EXTRACTION OF THE DEFECT BAND**

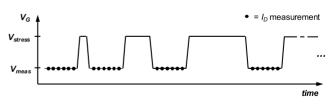

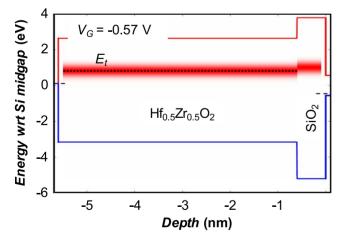

Electrically active defects such as oxygen vacancies are commonly observed in high-k oxides like HfO<sub>2</sub>, ZrO<sub>2</sub> and Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> [23]. Such defects may occur due to the imperfection of the oxide material, presence of grain boundaries, or due to the polycrystalline nature. At non-zero absolute temperature defects may be present even in a perfect crystal due the thermodynamic effects. In order to characterize the active defects in our gate oxide stack, we used a measurement scheme consisting of multiple charging ("stress") and discharging ("measurement") cycles (Fig. 8), originally developed for BTI reliability testing [14]. Briefly, the "stress" phases ( $V_G = V_{stress}$ ) with exponentially increasing durations allow to characterize the trap capture time distributions, while measuring the detrapping ("relaxion") during the "measurement" phase ( $V_G = V_{meas} \sim V_{th}$ ) allows evaluating the trap emission time distributions. Repeating the measurement at multiple Vstress voltages and temperatures then enables determining the complete trap properties, including their energy distribution in the  $Hf_{0.5}Zr_{0.5}O_2$  oxide band gap [13].

FIGURE 8. Schematic of the  $V_G$  bias sequence of trap charging ("stress") and discharging ("measurement") phases used to determine the distributions of trap properties.

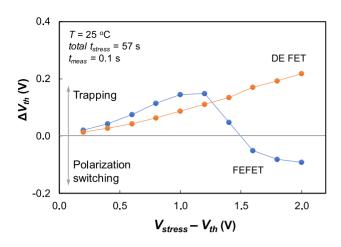

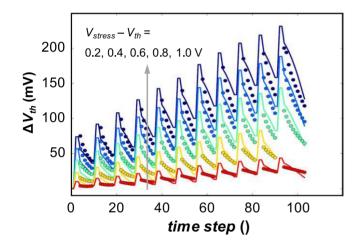

Fig. 9 shows the result of this procedure at a fixed total "stress" time and at increasing stress  $V_G$  values, for a FE HfZrO FET and for a reference HfO<sub>2</sub> dielectric DEFET. In case of the reference DEFET, only charge trapping occurs under the application of  $E_{ox}$ . Larger  $E_{ox}$  results in more trapping and consequently,  $\Delta V_{th}$  increases with the increase

**FIGURE 9.** Unlike in a reference FET with dielectric (DE) HfO<sub>2</sub> (5 nm) oxide, the threshold voltage shift  $\Delta V_{th}$  (hysteresis) in our FEFET switches sign at high  $V_G$  biases.

**FIGURE 10.** An aggregate plot of  $\triangle V_{th}$  values of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> FEFET during measurement phases vs. time steps (symbols), fitted assuming defect bands in Fig. 11 (lines) [13].

FIGURE 11. Graphical representation of extracted trap bands in FE and the interfacial SiO<sub>2</sub>.

of  $V_{stress}$ . The same trend is observed in our FEFET at lower voltages. Above  $V_{stress} - V_{th} \sim 1.2$  V,  $E_{ox}$  is high enough for the FE oxide to start polarizing during the stress phase,

FIGURE 12. During the *transient*  $I_D$ - $V_G$  measument, (a)  $V_G$  is stepped (forward sweep shown) as a function of time, while (b) at each bias value, multiple current measurements are done. (Each first measurement desigated by a larger symbol.)

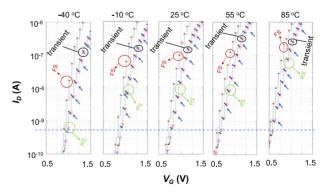

**FIGURE 13.** Forward- and reverse-sweep (FS and RS) *transient*  $I_D$ - $V_G$  characteristics showing transient  $I_D$  at every  $V_G$  step measured at different temperatures on a reference FET with 5nm thick SiO<sub>2</sub>. In the transient part,  $V_G$  is kept constant (Fig. 12). Downward triangles indicate first current measurement after each  $V_G$  step that corresponds to large symbon in Fig. 12 b. The arrows indicate the  $I_D$  transient trends during reverse sweep. Below the horizontal dotted line (sub nA current), the transients are caused by instrumentation and should be disregarded.

**FIGURE 14.** Forward- and reverse-sweep (FS and RS) *transient*  $I_D$ - $V_G$  characteristics of a FET with 8nm thick Al-HfO<sub>2</sub> measured at different temperatures. In the transient part,  $V_G$  is kept constant (Fig. 12). Drain current  $I_D$  always increases after every voltage down-step during reverse sweeps (indicated by the arrows) above the horizontal dotted line (sub nA current), consistent with CS detrapping. No steep slope is found in this wafer.

resulting in negative  $\Delta V_{th}$  during the measurement phase. The defect band properties in the FE oxide can therefore be extracted from the measurements at  $V_{stress} - V_{th} < 1.2$  V.

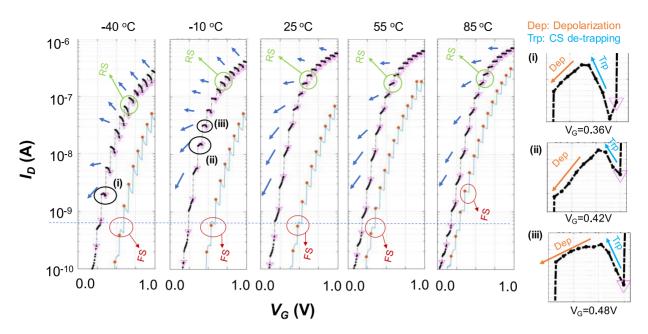

**FIGURE 15.** Forward- and reverse-sweep (FS and RS) transient  $I_D - V_G$  characteristics of a FEFET with 5nm thick HfZrO measured at different temperatures. In the transient part,  $V_G$  is kept constant (Fig. 12). Downward triangles indicate first current measurement after each  $V_G$  step that corresponds to large symbon in Fig. 12 b. s During reverse sweeps (above the horizontal dotted line indicating sub nA current) this wafer showed steep subthreshold slope. The  $I_D$  transients trend changes with the temperature (indicated by the arrows). Insets (i), (ii) and (iii) show the trend reversal of the current transient from CS detrapping to depolarization, at different current level and at two different temperatures.

TABLE 1. Parameters describing the defect band of HfZrO ferroelectric oxide.

| Parameter                                      | Value                                 |

|------------------------------------------------|---------------------------------------|

| Trap type                                      | Acceptor                              |

| <i>E<sub>t (mean)</sub></i> (w.r.t. Si midgap) | 0.83 eV                               |

| E <sub>t (sigma)</sub>                         | 0.22 eV                               |

| N <sub>t</sub>                                 | 2.6×10 <sup>20</sup> cm <sup>-3</sup> |

| R                                              | 0.32                                  |

| S (mean)                                       | 1.93 eV                               |

| S <sub>(sigma)</sub>                           | 1.21 eV                               |

Fig. 10 shows  $\Delta V_{th}$  of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> FEFET during measurement phases for varying  $V_{stress}$ . The measured data are then fitted by 2-state NMP theory incorporated into our "Comphy" tool [24] to extract the defect band properties. Both CS and GS trapping are natively considered. Details of the procedure are available elsewhere [13]. The result is shown in Fig. 11.

In addition to the defect band in the HfZrO layer, a defect band in the interfacial SiO<sub>2</sub> is also assumed in the fit. Table 1 then summarizes the parameters describing the defect band in the HfZrO layer (see Fig. 11) active at positive  $V_G$  biases (n-channel FET operation), i.e., the traps responsible for counteracting FE polarization switching in our FEFET. We note that the defect band is relatively deep in energy (close to the Si midgap), which is in agreement with the nearly linear  $\Delta V_{th}$  vs.  $V_{stress} - V_{th}$  dependence in Fig. 9 [25]

# C. TRANSIENT ID-VG MEASUREMENTS

To better understand the impact of trapping and polarization switching mechanisms on the  $I_D$ - $V_G$  sweeps, we introduce the *transient*  $I_D$ - $V_G$  measurement technique. Shown in Fig. 12, we measure ten  $I_D$  values at ~30 ms steps after every  $V_G$  step of the  $I_D$ - $V_G$  sweep. Using this technique, we therefore measure *the time dependence of*  $I_D$  *after every*  $V_G$ *step.* For *visualization purposes* we then map the measured  $I_D$  values (Fig. 12b) onto the gate bias  $V_G$  axis (Fig. 12a) using time as the common variable between them. The trends in the resulting *composite* graph (upward, flat, downward, or a combination) are then compared with the standard  $I_D$ - $V_G$ (Fig. 2) to find out which effect dominates the operating regime of the device. We next apply the *transient*  $I_D$ - $V_G$  to SiO<sub>2</sub>, Al-HfO<sub>2</sub> and HfZrO based FETs.

Figure 13 shows this *composite* plot obtained on a  $SiO_2$ based FET at different temperatures. At high  $I_D$  / high  $V_G$ levels, the transient trend is always flat, as well as independent of temperature, owing to the low trap density in SiO<sub>2</sub>. At *lower*  $I_D$  levels (~1nA to ~100nA) some upward and downward transients in the forward and reverse  $V_G$  sweeps, respectively, are observed, which we believe may be a signature of weak trapping. At the *lowest*  $I_D$  levels (~10pA to ~1nA) the transients are most likely low current measurement artefacts—they are seen in all our devices and at all measurement conditions.

In an Al-HfO<sub>2</sub> based FET, the  $I_D$  transient trend during reverse  $V_G$  sweep is always strongly upward (Fig. 14), consistent with CS detrapping. It is related to the fact that trap density in the high-k oxide is significantly higher as compared to that in SiO<sub>2</sub>.

Figure 15 then shows the same measurement on a HfZrO based FEFET. At  $-40^{\circ}$ C it is seen during the reverse sweep at low  $V_G$  that the trend is again upward in the beginning (a signature of CS de-trapping). Interestingly, we observe in

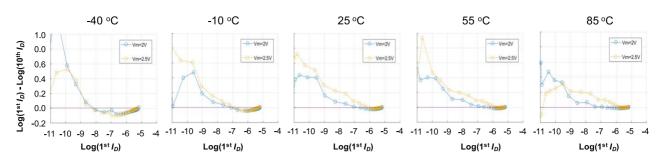

**FIGURE 16.** The 1<sup>st</sup> and the 10<sup>th</sup> measured  $I_D$  values are taken from the reverse sweeps of *transient*  $I_D$ - $V_G$  measurements. The difference of their logarithms represents the direction of the transients in Fig. 11. Positive values correspond to the transients coming from polarization switching while negative values correspond to detrapping. Results are plotted for different temperatures and  $V_m$  as a function of log ( $I_D$ ).

some transients that when some of the trapped charge get detrapped the trend switches its direction in the middle of the transient (inset of Fig. 15). *Hence there is an apparent competition between CS de-trapping and either GS trapping or FE depolarization.* Since we don't observe domination of GS trapping in Al-HfO<sub>2</sub> and we assume it is the case in HfZrO as well, we conclude the main cause must be FE depolarization. The trend reversal in the transient  $I_D$ - $V_G$  happens at low  $V_G$  because the depolarization field increases as  $V_G$  is ramped down [15].

As temperature increases, the depolarization effect becomes visible even at higher  $V_G$  values. It is because with increasing temperature the energy barrier for polarization switching goes down, which results in a decrease of coercive field [26]. Consequently, a lower depolarization field is necessary to cause the depolarization of the polarized oxide.

In Fig. 16 we plot the transient trends during the reverse sweep of  $V_G$  by plotting difference between the logarithm of the 1<sup>st</sup> and 10<sup>th</sup> measured  $I_D$  values. The positive values thus represent downward transient (depolarization) while negative values represent trapping. The crossover point from negative to positive value represents the level of current at which the trend reversal of the transient happened in Fig. 15. Figure 16 documents that as temperature increases, depolarization gets prominent at higher current values. In addition, it shows higher values of  $V_m$  lead to increased depolarization effect. This is most visible at 85°C—the depolarization occurs up to  $I_D = \sim 5 \times 10^{-8}$ A for  $V_m = 2$  V, while it occurs up to  $I_D = \sim 10^{-6}$ A for  $V_m = 2.5$  V.

# **IV. CONCLUSION**

We have reported HfZrO-based FEFETs scaled down to 70nm gate length. The devices show steep subthreshold slope in reverse  $V_G$  sweep only, along with  $V_{\text{th}}$  hysteresis. Gate oxide trapping and polarization switching greatly depends on the bias voltage range and operating temperature. Negligible effect of anneal temperature is observed. A band of active traps in the ferroelectric layer is characterized. Using our *transient*  $I_D$ - $V_G$  measurement technique we demonstrated the competition between trapping and FE behavior taking place during  $I_D$ - $V_G$  measurement. This measurement scheme thus facilitates understanding of mechanisms impacting the FEFET subthreshold slope.

# ACKNOWLEDGMENT

The authors gratefully acknowledge input from and discussions with M. Garcia Bardon, S. Clima, P. Matagne, P. Roussel, A. Verhulst, E. D. Litta Y. Xiang, S. McMitchell and J. Franco.

#### REFERENCES

- J. Jo and C. Shin, "Negative capacitance field effect transistor with hysteresis-free sub-60-mV/decade switching," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 245–248, Mar. 2016.

- [2] J. Zhou *et al.*, "Ferroelectric negative capacitance GeSn PFETs with sub-20 mV/decade subthreshold swing," *IEEE Electron Device Lett.*, vol. 38, no. 8, pp. 1157–1160, Aug. 2017.

- [3] P. Sharma et al., "Impact of total and partial dipole switching on the switching slope of gate-last negative capacitance FETs with ferroelectric hafnium zirconium oxide gate stack," in *Proc. Symp. VLSI Technol.*, 2017, pp. T154–T155.

- [4] E. Ko, J. W. Lee, and C. Shin, "Negative capacitance FinFET with sub-20-mV/decade subthreshold slope and minimal hysteresis of 0.48 V," *IEEE Electron Device Lett.*, vol. 38, no. 4, pp. 418–421, Apr. 2017.

- [5] M. Si *et al.*, "Steep-slope hysteresis-free negative capacitance MoS<sub>2</sub> transistors," *Nat. Nanotechnol.*, vol. 13, no. 1, pp. 24–28, 2018.

- [6] M. H. Lee *et al.*, "Ferroelectric Al:HfO2 negative capacitance FETs," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, 2017, pp. 23.3.1–23.3.4.

- [7] C.-J. Su *et al.*, "Ge nanowire FETs with HfZrOx ferroelectric gate stack exhibiting SS of sub-60 mV/dec and biasing effects on ferroelectric reliability," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, 2017, pp. 15.4.1–15.4.4.

- [8] J. Zhou *et al.*, "Frequency dependence of performance in Ge negative capacitance PFETs achieving sub-30 mV/decade swing and 110 mV hysteresis at MHz," in *Proc. IEEE Int. Electron Devices Meeting* (*IEDM*), 2017, pp. 15.5.1–15.5.4.

- [9] U. Schroeder *et al.*, "Impact of different dopants on the switching properties of ferroelectric hafniumoxide," *Jpn. J. Appl. Phys.*, vol. 53, no. 851, 2014, Art. no. 08LE02-1.

- [10] A. Saeidi et al., "Negative capacitance field effect transistors; capacitance matching and non-hysteretic operation," in Proc. Eur. Solid-State Device Res. Conf. (ESSDERC), Leuven, Belgium, 2017, pp. 78–81.

- [11] M. N. K. Alam *et al.*, "Investigation of ferroelectric HfZrO FET for steep slope applications," in *Proc. IEEE SOI-3D-Subthreshold Microelectron. Technol. Unified Conf.*, San Francisco, CA, USA, 2018, pp. 1–3.

- [12] T. Grasser et al., "A unified perspective of RTN and BTI," in Proc. IEEE Int. Rel. Phys. Symp., Waikoloa, HI, USA, 2014, pp. 4A.5.1–4A.5.7.

- [13] G. Rzepa et al., "Comphy—A compact-physics framework for unified modeling of BTI," *Microelectron. Rel.*, vol. 85, pp. 49–65, Jun. 2018.

- [14] B. Kaczer *et al.*, "Ubiquitous relaxation in BTI stressing—New evaluation and insights," in *Proc. IEEE Int. Rel. Phys. Symp.*, Phoenix, AZ, USA, 2008, pp. 20–27.

- [15] T. P. Ma and J.-P. Han, "Why is nonvolatile ferroelectric memory fieldeffect transistor still elusive?" *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 386–388, Jul. 2002.

- [16] S. N. Fedosov and H. V. Seggern, "Back-switching of ferroelectric polarization in two-component systems," J. Appl. Phys., vol. 96, no. 4, pp. 2173–2180, 2004.

- [17] R. R. Mehta, "Depolarization fields in thin ferroelectric films," J. Appl. Phys., vol. 44, no. 8, p. 3379, 1973.

- [18] Z. Xu, B. Kaczer, J. Johnson, D. Wouters, and G. Groeseneken, "Charge trapping in metal-ferroelectric-insulator-semiconductor structure with SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> stack," J. Appl. Phys., vol. 96, no. 3, p. 1614, 2004.

- [19] A. Daus *et al.*, "Charge trapping mechanism leading to sub-60mV/decade-swing FETs," *IEEE Trans. Electron Devices*, vol. 64, no. 7, pp. 2789–2795, Jul. 2017.

- [20] M. Toledano-Luque *et al.*, "Analytical model for anomalous positive bias temperature instability in La-based HfO<sub>2</sub> nFETs based on independent characterization of charging components," *Microelectron. Eng.*, vol. 109, pp. 314–317, Sep. 2013.

[21] C. M. Osburn and S. I. Raider, "The effect of mobile sodium ions

- [21] C. M. Osburn and S. I. Raider, "The effect of mobile sodium ions on field enhancement dielectric breakdown in SiO<sub>2</sub> films on silicon," *ECS J. Electrochem. Soc.*, vol. 120, no. 10, pp. 1369–1376, 1973.

- [22] M. Toledano-Luque *et al.*, "Fast ramped voltage characterization of single trap bias and temperature impact on time-dependent V<sub>TH</sub> variability," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3139–3144, Sep. 2014.

- [23] J. X. Zheng, G. Ceder, T. Maxisch, W. K. Chim, and W. K. Choi, "First-principles study of native point defects in hafnia and zirconia," *Phys. Rev. B, Condens. Matter*, vol. 75, no. 10, Art. no. 104112, 2007.

- [24] Comphy Version 1.0. Accessed: Nov. 2018. [Online]. Available: www.comphy.eu

- [25] J. Franco *et al.*, "Understanding the suppressed charge trapping in relaxed- and strained-Ge/SiO<sub>2</sub>/HfO<sub>2</sub> pMOSFETs and implications for the screening of alternative high-mobility substrate/dielectric CMOS gate stacks," in *Proc. IEEE Int. Electron Devices Meeting*, Washington, DC, USA, 2013, pp. 15.2.1–15.2.4.

- [26] D. Zhou *et al.*, "Electric field and temperature scaling of polarization reversal in silicon doped hafnium oxide ferroelectric thin films," *Acta Materialia*, vol. 99, pp. 240–246, Oct. 2015.

**MD. NUR KUTUBUL ALAM** received the B.Sc. and M.Sc. degrees in electrical and electronic engineering from the Khulna University of Engineering and Technology (KUET), Khulna, Bangladesh, in 2012 and 2015, respectively. He is currently pursuing the Ph.D. degree with KU Leuven in collaboration with IMEC, Belgium. He was a recipient of the Academic Gold Medal from KUET.

**BEN KACZER** received the M.S. degree in physical electronics from Charles University, Prague, in 1992, and the M.S. and Ph.D. degrees in physics from Ohio State University in 1996 and 1998, respectively. In 1998, he joined Reliability Group, IMEC, Belgium, where he is a Scientific Director. He has co-authored over 450 journal and conference papers and four patents. He was a recipient of six IRPS Best/Outstanding Paper Awards, two IPFA Best Paper Awards, and the 2011 EDS Paul Rappaport Award. He has served at various func-

tions at the IEDM, IRPS, SISC, INFOS, and WoDiM conferences. Since 2011, he has been serving on the IEEE TED Board.

**LARS-ÅKE RAGNARSSON** received the M.S. and Ph.D. degrees in electrical engineering from the Chalmers University of Technology, Gothenburg, Sweden, in 1993 and 1999. He was a Post-Doctoral Fellow with the IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, from 2000 and 2002, researching on electrical characterization of high-*k* dielectrics. Since 2002, he has been with IMEC, Leuven, Belgium, as a Principal Scientist with research focus on high-*k* dielectrics and metal gates for future technology nodes. **MIHAELA POPOVICI** received the B.Sc. and M.Sc. degrees in chemical engineering and the Ph.D. degree in materials science and engineering in 2004 from the "Politehnica" University of Timisoara, Romania. She is a Senior Researcher with the Semiconductor Technology and Systems Unit, IMEC, Belgium. She was a Post-Doctoral Fellow with the Photonic Materials and Devices Department, Philips Research, The Netherlands, for two years. She joined IMEC in 2007. Her main expertise resides in dielectric oxides and metal thin films development (ALD, CVD, and PVD), physical and electrical characterization and design of complex materials stacks with applications in microelectronic electronic devices, such as metal–insulator–metal capacitors for DRAM, ferroelectrics, and active layers mainly for RRAM, STT-MRAM, and Interconnect applications. During her career, together with the technical teams, she has demonstrated the ability to bring innovation, reflected by her patent and publication track record. She has an *H*-index of 17.

**GERHARD RZEPA** received the B.Sc. degree in electrical engineering and the Diplomingenieur degree in microelectronics from TU Wien (Vienna University of Technology), in 2010 and 2013, respectively, the Ph.D. degree in modeling of bias temperature instabilities from the Institute for Microelectronics, TU Wien, in 2018, and the Doctoral degree. He is with the Institute for Microelectronics, where he focuses on the research of oxide degradation, device variability and measuring, and modeling of related reliability

phenomena, such as bias temperature instabilities, hot carrier degradation, random telegraph noise, and stress-induced leakage currents.

**NAOTO HORIGUCHI** is the Director of CMOS device scaling program with Interuniversity Microelectronics Center (IMEC), Leuven, Belgium. He started his carrier in semiconductor device Research and Development with Fujitsu Laboratories Ltd., in 1992. From 1992 to 1999, he was engaged in device development by using semiconductor nano structures with Fujitsu Laboratories Ltd., and the University of California at Santa Barbara. From 2000 to 2006, he was engaged in 90-45 nm CMOS technology development with Fujitsu Ltd., as a Lead Integration Engineer. In 2006, he is with IMEC, where he is engaged in advanced CMOS device Research and Development together with worldwide industrial partners, universities, and research institutes. His current focus is CMOS device scaling down to 2-nm technology node and beyond. He holds over 20 international patents and authored or co-authored over 300 technical papers and international conferences.

**MARC HEYNS** received the M.S. degree in applied sciences (electronics) from the University of Leuven, Belgium, in 1979, and the Ph.D. degree from the University of Leuven in 1986. In 1986, he joined IMEC, where he became the Department Director and the Program Director responsible for a research group working on ultraclean processing technology, advanced high-gate stacks, environmentally benign processing, Ge and III/V CMOS, advanced devices, and 2-D materials. He became an IMEC-Fellow in 2001 and a Professor with the

Department of Materials Engineering, KU Leuven in 2005, where he is a Program Director of the Master on Nanoscience, Nanotechnology, and Nano-Engineering.

He has initiated and led as a Program Director various research programs with IMEC, including activities on ultraclean processing, high-k dielectrics, Ge and III-V CMOS, TunnelFETS, and graphene. His current research interests focus on "Exploratory and Beyond CMOS Technologies," including research on novel materials and devices for ultimate CMOS, nanowires, 2-D materials, topological materials, quantum computing, and spin-based devices.

**JAN VAN HOUDT** (F'14) received the Ph.D. degree from the University of Leuven. In 1999, he became responsible for Flash Memory with IMEC and as such was the driving force behind the expansion of IMEC's Memory Program. He is a Scientific Director of the Semiconductor Division. He has published 300 papers in journals and 250 conference contributions. He has filed about 70 patents and served on the committees of ten major semiconductor conferences. In 2014, he started the Ferroelectrics Program with IMEC and became a Guest Professor with the University of Leuven teaching CMOS and memory technology.