UNIVERSITY OF CALIFORNIA Los Angeles

On the Correctness of Transactional Memory Algorithms

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Mohsen Lesani

R Copyright by Mohsen Lesani 2014

### ABSTRACT OF THE DISSERTATION

#### On the Correctness of Transactional Memory Algorithms

by

Mohsen Lesani Doctor of Philosophy in Computer Science University of California, Los Angeles, 2014 Professor Jens Palsberg, Chair

Transactional Memory (TM) provides programmers with a high-level and composable concurrency control abstraction. The correct execution of client programs using TM is directly dependent on the correctness of the TM algorithms. In return for the simpler programming model, designing a correct TM algorithm is an art. This dissertation contributes to the specification, safety criterion, testing and verification of TM algorithms. In particular, it presents techniques to prove the correctness or incorrectness of TM algorithms.

We introduce a language for architecture-independent specification of synchronization algorithms. An algorithm specification captures two abstract properties of the algorithm namely the type of the used synchronization objects and the pairs of method calls that should preserve their program order in the relaxed execution.

Decomposition of the correctness condition supports modular and scalable verification. We introduce the markability correctness condition as the conjunction of three intuitive invariants: writeobservation, read-preservation and real-time-preservation. We prove the equivalence of markability and opacity correctness conditions.

We identify two pitfalls that lead to violation of opacity: the write-skew and write-exposure anomalies. We present a constraint-based testing technique and an automatic tool called Samand that finds traces of such bug patterns. Using Samand, we show that the DSTM and McRT algorithms suffer from the write-skew and write-exposure anomalies.

We present a sound program logic called synchronization object logic (SOL) that supports reasoning about the execution order and linearization order. It provides inference rules that axiomatize the properties and the interdependence of these orders and also the properties of common synchronization object types. We show that derivation of markability in SOL is a sound syntactic proof technique for opacity. We use SOL to prove the markability and hence opacity of the TL2 algorithm in PVS. The dissertation of Mohsen Lesani is approved.

Todd Millstein Glenn Reinman Hans Boehm Edward Effros Jens Palsberg, Committee Chair

University of California, Los Angeles\$2014\$

To Niloufar, Shahnaz and Mehdi

## Contents

| Li       | List of Figures vii   |                                               |    |  |  |  |  |  |

|----------|-----------------------|-----------------------------------------------|----|--|--|--|--|--|

| 1        | Introduction          |                                               |    |  |  |  |  |  |

| <b>2</b> | Syn                   | chronization Object Language                  | 4  |  |  |  |  |  |

|          | 2.1                   | Introduction                                  | 4  |  |  |  |  |  |

|          | 2.2                   | Syntax                                        | 6  |  |  |  |  |  |

|          |                       | 2.2.1 Specification                           | 6  |  |  |  |  |  |

|          |                       | 2.2.2 TM Algorithm Specification              | 9  |  |  |  |  |  |

|          |                       | 2.2.3 Extended Syntax                         | 10 |  |  |  |  |  |

|          |                       | 2.2.4 Example Specifications                  | 13 |  |  |  |  |  |

|          | 2.3                   | Semantics                                     | 29 |  |  |  |  |  |

|          |                       | 2.3.1 Execution History                       | 29 |  |  |  |  |  |

|          |                       | 2.3.2 Synchronization Object Types            | 31 |  |  |  |  |  |

|          |                       | 2.3.3 History Semantics                       | 44 |  |  |  |  |  |

| 3        | $\mathbf{TM}$         | [ Correctness                                 | 48 |  |  |  |  |  |

|          | 3.1                   | Introduction                                  | 48 |  |  |  |  |  |

|          | 3.2                   | Opacity                                       | 49 |  |  |  |  |  |

|          | 3.3                   | Markability                                   | 51 |  |  |  |  |  |

|          |                       | 3.3.1 Write-observation and Read-preservation | 51 |  |  |  |  |  |

|          |                       | 3.3.2 Marking TL2                             | 53 |  |  |  |  |  |

|          |                       | 3.3.3 The Marking Theorem                     | 54 |  |  |  |  |  |

| <b>4</b> | Testing TM Algorithms |                                               |    |  |  |  |  |  |

|          | 4.1                   | Introduction                                  | 58 |  |  |  |  |  |

|          | 4.2                   | Opacity Bug Patterns                          | 59 |  |  |  |  |  |

|          | 4.3                   | Automatic Bug Finding                         | 60 |  |  |  |  |  |

|          | 4.4                   | Experiments                                   | 65 |  |  |  |  |  |

| <b>5</b> | Syn                   | ynchronization Object Program Logic           |    |  |  |  |  |  |

|          | 5.1                   | Introduction                                  | 67 |  |  |  |  |  |

|          | 5.2                   | Simple Example                                | 68 |  |  |  |  |  |

|          |                       | 5.2.1 Algorithm Specification                 | 68 |  |  |  |  |  |

|          |                       | 5.2.2 Program Logic                           | 69 |  |  |  |  |  |

|    | 5.3  | Assertion Language                                                                                                                                          | '2<br>'6 |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|    | 5.4  |                                                                                                                                                             | 7        |

|    | 5.5  |                                                                                                                                                             | 8        |

|    |      | 0                                                                                                                                                           | '8       |

|    |      |                                                                                                                                                             | 31       |

|    |      |                                                                                                                                                             | 33       |

|    |      | J J                                                                                                                                                         | 35       |

|    | 5.6  | Soundness                                                                                                                                                   | 6        |

|    | 5.7  | Dekker Mutual Exclusion                                                                                                                                     | )7       |

| 6  | Syn  | tactic TM Correctness 10                                                                                                                                    |          |

|    | 6.1  | Client Transactions                                                                                                                                         | 3        |

|    | 6.2  | Markability                                                                                                                                                 |          |

| 7  | Veri | ification of TM Algorithms 10                                                                                                                               | -        |

|    | 7.1  | Marking TL2                                                                                                                                                 |          |

|    | 7.2  | Marking DSTM (visible reads)                                                                                                                                |          |

|    | 7.3  | Marking NORec                                                                                                                                               | 9        |

| 8  | Rela | ated Works 11                                                                                                                                               | 0        |

|    | 8.1  | Verification of Transactional Memory                                                                                                                        | 0        |

|    | 8.2  | Concurrent Program Logics                                                                                                                                   | 3        |

| 9  | Con  | clusions and Future Works 11                                                                                                                                | 6        |

| 10 | App  | pendix 11                                                                                                                                                   | 7        |

|    | 10.1 | Synchronization Object Language                                                                                                                             | 7        |

|    |      | 10.1.1 Specification $\ldots \ldots \ldots$ | 7        |

|    |      | 10.1.2 Semantics                                                                                                                                            |          |

|    | 10.2 | TM Correctness                                                                                                                                              | 3        |

|    |      | 10.2.1 The Marking Theorem                                                                                                                                  | 3        |

|    |      | 10.2.2 Marking TL2                                                                                                                                          | 8        |

|    | 10.3 | Testing TM Algorithms                                                                                                                                       | 7        |

|    |      | 10.3.1 Example: Dekker Mutual Exclusion                                                                                                                     | 7        |

|    |      | 10.3.2 Language                                                                                                                                             | 9        |

|    |      | 10.3.3 TM Algorithms in Samand                                                                                                                              | 1        |

|    | 10.4 | Synchronization Object Program Logic                                                                                                                        | 0        |

|    |      | 10.4.1 Soundness                                                                                                                                            | 0        |

|    |      | 10.4.2 Derived Rules                                                                                                                                        | 6        |

|    | 10.5 | Syntactic TM Correctness                                                                                                                                    | 8        |

|    |      | 10.5.1 Transactions                                                                                                                                         | 8        |

|    |      | 10.5.2 Markability                                                                                                                                          | 0        |

|    | 10.6 | Related Works                                                                                                                                               | 2        |

|    |      |                                                                                                                                                             |          |

## 11 Bibliography

# List of Figures

| 2.1  | $\pi_{Dekker}$ Dekker Algorithm Specification                                                                                                                                                                            | 3 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2.2  | $\pi_{TL2}$ TL2 Algorithm Specification                                                                                                                                                                                  | 5 |

| 2.3  | $\pi_{TL2Variant}$ TL2 Variant Algorithm Specification                                                                                                                                                                   | 7 |

| 2.4  | $\pi_{DSTM}$ DSTM Algorithm Specification                                                                                                                                                                                | 9 |

| 2.5  | $\pi_{DSTMVis}$ DSTM (visible reads) Algorithm Specification                                                                                                                                                             | 1 |

| 2.6  | $\pi_{McRT}$ McRT Algorithm Specification                                                                                                                                                                                | 3 |

| 2.7  | NORec NORec Algorithm Specification                                                                                                                                                                                      | 4 |

| 2.8  | TLRW Algorithm (objects) 28                                                                                                                                                                                              | 5 |

| 2.9  | TLRW Algorithm (read)                                                                                                                                                                                                    | 6 |

| 2.10 | TLRW Algorithm (write)                                                                                                                                                                                                   | 7 |

| 2.11 | TLRW Algorithm (abort and commit) 28                                                                                                                                                                                     | 8 |

| 2.12 | History Semantics $\mathbb{H}(\pi)$ of a specification $\pi = (\mathcal{T}, \mathcal{D}, \mathcal{P}) \dots \dots$ | 5 |

| 0.1  |                                                                                                                                                                                                                          | ~ |

| 3.1  | FinalStateOpaque                                                                                                                                                                                                         |   |

| 3.2  | Illustrations of Write-observation and Read-preservation                                                                                                                                                                 |   |

| 3.3  | TL2 Read-Preservation Example                                                                                                                                                                                            |   |

| 3.4  | The set of local and global reads and writes                                                                                                                                                                             |   |

| 3.5  | FinalStateMarkable                                                                                                                                                                                                       | 0 |

| 4.1  | Counterexamples                                                                                                                                                                                                          | 6 |

| 5.1  | Example Specification $\pi$                                                                                                                                                                                              | 8 |

| 5.2  | Structure Inference Rules.                                                                                                                                                                                               |   |

| 5.3  | Basic inference rules.                                                                                                                                                                                                   |   |

| 5.4  | Synchronization Object Inference Rules.                                                                                                                                                                                  |   |

| 5.5  | Classical Inference Rules                                                                                                                                                                                                |   |

| 5.6  | Derived Classical Inference Rules                                                                                                                                                                                        |   |

| 5.7  | Equivalence and Arithmetic Rules                                                                                                                                                                                         |   |

| 5.8  | Derived Equivalence and Arithmetic Rules                                                                                                                                                                                 |   |

| 5.9  | Structure Inference Rules. All of the rules have the side condition $\pi = (\mathcal{T}, \mathcal{D}, \mathcal{P})$ 82                                                                                                   |   |

| 5.10 | Derived Structure Inference Rules                                                                                                                                                                                        |   |

| 00   | Basic Inference Rules                                                                                                                                                                                                    |   |

|      | Derived Basic Inference Rules                                                                                                                                                                                            |   |

|      | Register Inference Rules.    80                                                                                                                                                                                          |   |

|      | Derived Register Inference Rules                                                                                                                                                                                         |   |

|      |                                                                                                                                                                                                                          |   |

| 0                                                                                                                                                                                                    | 89 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

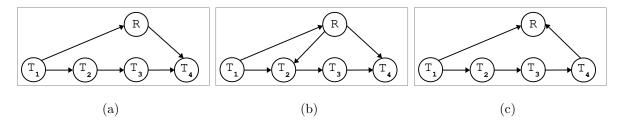

| 5.16 Derived CAS Register Inference Rules                                                                                                                                                            | 89 |

| 5.17 Preliminary definitions for Lock and TryLock Inference Rules.                                                                                                                                   | 90 |

| 5.18 Lock and TryLock Inference Rules.                                                                                                                                                               | 91 |

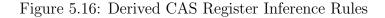

|                                                                                                                                                                                                      | 92 |

|                                                                                                                                                                                                      | 92 |

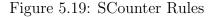

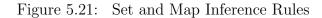

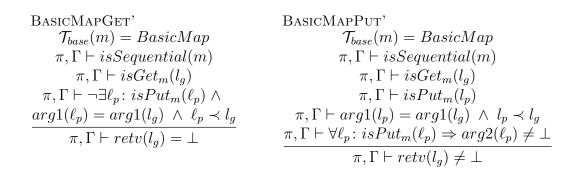

| 5.21 Set and Map Inference Rules                                                                                                                                                                     | 94 |

| 5.22 Derived Set and Map Inference Rules                                                                                                                                                             | 95 |

| $6.1$ Reads and Writes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $10$                                                                                         | 04 |

| $5.2$ is Marking Assertions $\ldots \ldots \ldots$                                   | 05 |

| 7.1 DSTM (visible reads) Preserving Reads                                                                                                                                                            | 09 |

| 10.1 Case $T \in Aborted(H) \land R \sqsubset T' \sqsubset T$                                                                                                                                        | 39 |

| $10.2 \text{ Case } T \in Aborted(H) \land T \sqsubset T' \sqsubset R \qquad \dots \qquad$   | 41 |

| $10.3 \text{ Case } T \in Committed(H) \land R \sqsubset T' \sqsubset T \qquad \dots \qquad$ | 43 |

| $10.4 \text{ Case } T \in Committed(H) \land T \sqsubset T' \sqsubset R \qquad \dots \qquad$ | 45 |

| 10.5 Updating Version Registers                                                                                                                                                                      | 47 |

| $10.6 R04 \text{ is race-free} \dots $                                                         | 50 |

| 10.7 $reg[i]$ is sequentially-written $\ldots \ldots \ldots$                         | 51 |

| 10.8 Effect-order of pre-accessors                                                                                                                                                                   | 53 |

| 10.9 Dekker Algorithm Specification                                                                                                                                                                  | 57 |

| 10.10Bug Trace for Incorrect If Condition                                                                                                                                                            | 58 |

| 10.11Bug Trace for Removed Program Order                                                                                                                                                             | 59 |

| 10.12Dekker Random Execution                                                                                                                                                                         | 59 |

| 10.13Specification of DSTM                                                                                                                                                                           | 92 |

| $10.14 Specification of TL2 \dots \dots$                                                       | 92 |

## List of Theorems

Theorem 1, Page 57 (Marking): Opacity is equivalent to Markability.

Theorem 2, Page 59 (Bug Patterns): Write-skew and write-exposure anomalies violate opacity.

Theorem 3, Page 96 (SOL Soundness): The synchronization object program logic derives valid conclusions from valid premises.

Theorem 4, Page 97 (Dekker Mutual exclusion): The Dekker algorithm provides mutual exclusion.

Theorem 5, Page 104 (Markability Soundness): A TM algorithm is opaque if the markability assertion is derivable for its specification.

Theorem 6, Page 107 (Opacity of TL2): The TL2 algorithm is opaque.

Publications during the PhD studies:

- Automatic Atomicity Verification for Clients of Concurrent Data Structures Mohsen Lesani, Todd Millstein, Jens Palsberg CAV'14 (Computer Aided Verification Conference 2014)

- Semantics-preserving Sharing Actors Mohsen Lesani, Antonio Lain AGERE'13 (Actors, Agents, and Decentralized Control Workshop 2013)

- Specifying Transactional Memories with Nontransactional Operations Mohsen Lesani, Victor Luchangco, Mark Moir WTTM'13 (Theory of Transactional Memory Workshop 2013)

- Write-observation and Read-preservation TM Correctness Invariants Mohsen Lesani, Jens Palsberg WTTM'13 (Theory of Transactional Memory Workshop 2013)

- MrCrypt: Static Analysis for Secure Cloud Computations Sai Deep Tetali, Mohsen Lesani, Rupak Majumdar, Todd Millstein OOPSLA'13 (Object-Oriented Programming, Systems, Languages & Applications Conference 2013)

- Proving Non-opacity Mohsen Lesani, Jens Palsberg DISC'13 (DIStributed Computing Conference 2013 - LNCS 8205, Transact'13 (Transactional Computing 2013)

- A Framework for Formally Verifying Software Transactional Memory Algorithms Mohsen Lesani, Victor Luchangco, Mark Moir CONCUR'12 (Concurrency Theory Conference 2013)

- Putting Opacity in its Place Mohsen Lesani, Victor Luchangco and Mark Moir WTTM'12 (Theory of Transactional Memory Workshop 2012)

- Communicating Memory Transactions Mohsen Lesani, Jens Palsberg PPoPP11 (Principles and Practice of Parallel Programming Conference 2011)

## Chapter 1

## Introduction

Transactional Memory (TM) [41, 70] provides programmers with a high level concurrency control abstraction. Programmers can simply declare certain blocks of code as transactions and the TM runtime guarantees that transactions execute in isolation. The use of TM provides atomicity, deadlock freedom, and composability [35], and increases programmer productivity compared to use of locks [64, 67]. Researchers have developed formal semantics [1, 57, 47] and a wide variety of implementations of the TM interface in software [39, 38, 18, 68, 19], hardware [32, 3], and software/hardware hybrids [5, 55, 15]. Recently, industry is adopting TM. IBM supports TM in its Blue Gene/Q processor [33], and Intel supports transactional synchronization primitives in its new processor microarchitecture Haswell [14]. The C++ transactional memory study group (SG5) is introducing transactional constructs to the C++ language.

The TM runtime takes the responsibility of managing the consistency of the shared state. Therefore, the correct execution of client programs using the TM interface is dependent on the correctness of TM algorithms. In return for the simpler programming model, designing a correct TM algorithm is an art. Algorithm designers employ different techniques to provide the TM interface efficiently. They interleave transactions as much as possible, while guaranteeing non-interleaving semantics. Thus, subtle but fast algorithms are favored over simpler ones. The subtlety of the algorithms makes them prone to intricate bugs. Thus, the correctness of TM algorithms is both a central and a formidable problem. This dissertation presents techniques to prove the correctness or incorrectness of TM algorithms. In particular, it contributes to the specification, safety condition, testing and verification of TM algorithms.

**Specification.** Precise specification of algorithms is the first step towards testing and verification of them. The current literature on synchronization and particularly TM algorithms usually presents algorithms in prose or architecture-dependent code. The effect can be unfortunate: under- and over-specification of the algorithm and therefore misunderstanding, irreproducibility and unportability.

We introduce a language for architecture-independent specification of synchronization algorithms. An algorithm specification captures two abstract properties of the algorithm namely the type of the used synchronization objects and the required program orders. The language supports the following common synchronization object types: basic register, atomic register, atomic cas register, lock, trylock, strong counter, basic set and basic map. Each method definition involves the declaration of the pairs of method calls whose order in the program should be preserved in the relaxed execution. The specifications can be studied, and verified once and for all, independently of the implementation of the synchronization objects and the memory models of the compiler and the architecture. Compilers can optimize implementations of the synchronization object types and also the number, type and position of memory fences. We specify several well-known TM algorithms in the language.

We define the semantics of specifications as a set of execution histories. We define the denotational semantics of a specification as a set of constraints that enforce both the structure of the program and the safety of the used objects. The semantics is compositional, models true concurrency and allows relaxed execution.

**Safety.** A TM algorithm should guarantee that every concurrent execution of an arbitrary set of client transactions is indistinguishable from a sequential execution of them. Safety conditions for TM such as opacity [28], VWC [44], TMS1 and TMS2 [22] define the indistinguishably criterion and the set of correct histories. Lesani et al. [51] proved that opacity is stronger than TMS1 and weaker than TMS2. Verification of TM algorithms is a formidable problem in part because the target correctness criterion is a monolithic complicated condition. Is there an intuitive decomposition of TM correctness conditions? What are the separate invariants that the TM designers should maintain? Decomposition of the correctness condition informs designers by showcasing different aspects of correctness and helps them concentrate on maintaining one aspect at a time. In addition, separation has obvious benefits of modularity and scalability for verification. In an early work, Tasiran [73] presented a decomposition of the correctness condition for a specific class of algorithms.

We present intuitive invariants for the correctness of TM algorithms. We say that a history is markable if there is a specific ordering relation called marking such that certain invariants are satisfied. We prove the equivalence of markability and opacity. At a high level, the first invariant called write-observation requires that each read operation returns the most current value and the second invariant called read-preservation requires that the location which is read is not overwritten in a certain interval.

**Testing.** Algorithm design is an iterative process of trying alternatives, fixing issues and improving the performance. A testing tool can assist algorithm designers during both the design and the maintenance of the algorithm. Manovit et al. [53] and Lourenco et al. [52] applied random testing to TM algorithms.

We identify the write-skew and write-exposure anomalies as two pitfalls that lead to non-opacity. We present a tool called Samand that automatically finds traces of such bug patterns. The tool inputs a TM algorithm, a program and a test assertion. The test assertion can be a partial correctness condition such as negation of a bug pattern. If there is an execution of the test program that violates the test assertion, Samand outputs the trace of a violating execution. Samand translates concurrent execution to constraints and employs Z3 SMT solver [17] to solve the constraints. Using Samand, we show that DSTM [39] suffers from the write-skew anomaly and McRT [68] suffers from the write-exposure anomaly. These results may be surprising because previous work [31, 30, 24] considered abstract version of DSTM and McRT and proved their correctness.

Verification. Verification of TM algorithms has been a topic of recent attention. Researchers have employed model checking, automatic invariant generation and theorem proving to verify the correctness of TM algorithms. Model checkers from Cohen et al. [11, 12], and Guerraoui et al. [29, 31, 30] were the pioneering approach to verification of TM. Subsequently, the same approach was taken by O'Leary et al. [61] and Baek et al. [4]. Model checking can automate the verification process but is either based on assumed properties about the TM algorithm or only scalable to a finite number of threads and locations or simplified algorithms. Later, Emmi et al. [24] tried to automatically infer invariants that are strong enough to entail the correctness criterion. Compliance of the algorithms with the specification can be easily checked if the proper invariants can be automatically generated.

On the other hand, this work reported resorting to simplified algorithms due to scalability issues. Later, Lesani et al. [50] presented a machine checked theorem proving framework based on I/O-automata and proved the correctness of NORec TM algorithm [16]. The framework can be employed to verify realistic algorithms but requires translation of the algorithm to a transition system and more importantly, the process involves coming up with non-trivial invariants.

Aside from modeling simplified algorithms and limited scalability, all previous works on verification of TM algorithms work with semantic models. We believe that studying TM algorithms can benefit from focusing on the syntactic specification of an algorithm, syntactic description of correct algorithm, and a deduction mechanism to reason about algorithm correctness using the structure of the algorithm and the properties of used synchronization objects.

As we review in the related works chapter, the previous works on concurrent program logics support several forms of local reasoning but do not support assertions for the execution order or the linearization order of method calls across threads. These assertions are particularly essential for reasoning about TM algorithms. A concurrent execution of a set of transactions is correct if there is an indistinguishable sequential order of the transactions. The sequential order is determined by the execution order or the linearization order of certain method calls in the transactions. We present a program logic called synchronization object logic (SOL) that supports reasoning about the execution overlap, execution order and linearization orders of method calls. It provides inference rules that axiomatize the properties and the interdependence of these orders and also axiomatize the properties of common synchronization object types. We prove the soundness of the logic. SOL derives valid conclusions from valid premises.

We define the markability assertions in SOL and prove that a TM algorithm is opaque if markability can be derived for its specification. Therefore, deriving the markability is a sound syntactic proof technique for opacity of TM algorithm specifications.

We formalize SOL in PVS [63] and use it to machine-check the markability of the well-known TM algorithm TL2 [18]. SOL is applicable beyond TM, particularly to algorithms for mutual exclusion. As evidence, we prove the mutual exclusion property of the Dekker algorithm.

In the following chapters, we first define the specification language. Then, we consider safety conditions and introduce markability. Then, we present our testing approach based on bug patterns. Finally, we introduce our logic, present the markability proof technique and use the logic to prove the markability of TM algorithms.

## Chapter 2

## Synchronization Object Language

## 2.1 Introduction

Precise specification of algorithms is an important prerequisite to understanding, testing and verification of them. The current literature on synchronization algorithms and particularly TM algorithms usually presents algorithms in architecture-dependent code or prose. The effect can be unfortunate: *under- and over-specification* of the algorithm and therefore misunderstanding, irreproducibility and unportability. We present some instances at the end of this subsection. Separation of specification and implementation is a classical design principle. In this chapter, we introduce a language for architecture-independent specification of synchronization algorithms. The language supports the common *synchronization object types*, and allows *relaxed execution*. We present the syntax and then the semantic of the language.

**Syntax.** We introduce a language for the specification of synchronization algorithms. A specification is comprised of three sections: the typing section, the definitions section, and the program section. The typing section is the type declarations of the synchronization objects that the algorithm uses. The definitions section is the definitions of the methods of the algorithm. Each method definition involves the declaration of pair of method calls whose order in the program should be preserved in the relaxed execution. The program section defines the parallel program or programs that call the defined methods.

In particular, the specification captures two abstract properties of the algorithm namely the type of the base objects and the required orders. A synchronization object type such as atomic register declares the safety and liveness properties that the objects of the type guarantee. Our language supports the following synchronization object types: basic register, atomic register, atomic cas register, lock, try-lock, strong counter, basic set and basic map. The type and its properties are abstract from the implementations of the type. Similarly, the required program order is abstract from the memory model or the fences needed to satisfy it. The specifications can be studied, and verified once and for all, independently of the implementation of the base objects and the memory models of the compiler and the architecture. Compilers can benefit from optimized implementations of synchronization object types and optimize the memory layout of the base objects. They can also optimize the number, type and position of fences to satisfy the program order.

A TM algorithm specification should define the four methods of the TM interface: init, read, write and commit that initialize the transaction, read from a location, write to a location and attempt to commit the transaction. We consider an arbitrary set of transactions as the client parallel program. We specify several well-known TM algorithms in the language.

**Semantics.** We adopt the notion of execution history [40, 28] as the representation of a concurrent execution. First, we remind execution histories and their operations and relations.

Then, we define synchronization object types. We present the semantics of linearizable and basic objects as sets of execution histories. We define abstract object types and concrete synchronization objects. We present the interface and the sequential specification of each abstract object type. For each synchronization object type, we present lemmas that characterize the properties of its execution histories.

Based on the above definitions, we define the semantics of specifications as a set of execution histories. We define the denotational semantics of a specification as a set of constraints that enforce both the structure of the program and the guarantees of the base objects. The semantics is compositional i.e. it is abstract from and can be modularly augmented with new object types. It models true concurrency i.e. it considers a pair of invocation and response events for each method call. It allows relaxed execution i.e. it supports out-of-order execution of method calls that are not specified to be ordered.

**TM Algorithm Specification Pitfalls.** Now, we present some instance of pitfalls in the specification of TM algorithms that we have encountered in the literature.

The algorithms that are tailored for specific architectures and memory models [18, 68, 19] can under- and over-specify the algorithm. Some orders of execution that are implicitly provided by one memory model may need explicit fences in other memory models. Thus, some important orders may be left unspecified. For example a subtle required order is unspecified in TL2 [18] as noted later [31]. Therefore, porting algorithms can introduce bugs. Similarly, some orders that needed fences in one memory model may be implicitly provided by another. Extra fences hinder performance.

Striving for efficiency, several objects are packed to or share the same memory location. To avoid false sharing phenomenon, objects are explicitly padded. The details of object layout can obfuscate the algorithm intents. As observed by previous work, in the original TL2 paper, "the authors maintain the version number and the lock bit of every variable in the same memory word" [31], thus, the order of checking the lock and the version of read locations is ambiguous in the commit procedure. In our specification, we treat the lock and the version as separate registers and make the orders explicit.

Imprecise specifications lead to irreproducibility. TL2 algorithm [18] and DSTM algorithm [39] are explained in prose. Therefore, rewritten specifications of it in the literature are inaccurate or incorrect. For example, there are no visible reads in the DSTM algorithm but the specifications in [31] and [24] abort the visible readers during the validate command. In [30], DSTM is specified with no dynamic object allocation while the original algorithm [39] is fundamentally based on the indirection that is obtained from dynamic creation of locator objects. In addition, there is no distinction between read and write operations in the specification. The read operation simply calls the write operation, thus a read acquires the location similar to a write. This is while readers do not acquire the location in the original algorithm. In the specification, the commit operation writes to every location that is written to during the transaction. This is while commitment is done by a single compare-and-swap in the original algorithm. As another example, TL2 algorithm [18] is based on version numbers while the specifications of TL2 in [31] and [24] replace the version number concept with the unprecedented notion of modified sets. Furthermore, there has been a typo of writing *os* instead of *ls* in the TL2 transition system in [31]. The follow up work [24] that rewrites this specification, incorrectly fixed *os* to *ws* and thus verified a different algorithm. In [30], the check that the version of the read location

is less than the read version is replaced with an equality check. This restricts the concurrency of the algorithm. A local array *lver* is introduced that is written during the read operations and checked during the commit procedure. This local array does not exist in the original algorithm.

## 2.2 Syntax

Now, we introduce the syntax of the language. We define the structure of a specification and then define a TM algorithm specification as a specific specification. To have more concise specifications, we extend the syntax with syntactic sugar. We present the specifications of Dekker mutual exclusion algorithm and TL2, TL2 variant, DSTM, DSTM (visible reads), and McRT TM algorithms.

### 2.2.1 Specification

A specification  $\pi$  is a triple  $(\mathcal{T}, \mathcal{D}, \mathcal{P})$  where  $\mathcal{T}$  is the typing of base objects,  $\mathcal{D}$  is the method definitions, and  $\mathcal{P}$  is the parallel program calling the defined methods. Let  $\Pi$  denote the set of specifications. We will define each of the components in turn.

**Typing.** We define the set of object types, as follows. An object type is either a scalar or an array type. In an array type st[], st is the scalar type of elements. A scalar type is either a basic, sequentially-consistent or linearizable type.

| $ot \in OT$  | ::= | $st \mid st[]$                                | Object Type                  |

|--------------|-----|-----------------------------------------------|------------------------------|

| $st \in ST$  | ::= | $bt \mid lt$                                  | Scalar Type                  |

| $bt \in BT$  | ::= | $\{BasicRegister, BasicSet, BasicMap\}$       | Basic Type                   |

| $ct \in SCT$ | ::= | $\{SCRegister\}$                              | Sequentially Consistent Type |

| $lt \in LT$  | ::= | ${\bf Atomic Register, Atomic CAS Register,}$ | Linearizable Type            |

|              |     | $Lock, TryLock, SCounter, SeqLock\}$          |                              |

Let  $\Phi$  denote the set of base object names  $\phi$ .

$\phi \in \Phi ::= \{lock, reg, \ldots\}$  Base Object Name

The typing  $\mathcal{T}$  is a mapping from base object names to object types. A comma-separated list of elements e is denoted as  $e^*$ .

$$\mathcal{T} ::= (\phi : ot)^*$$

Typing

A thread-local object is an array that is indexed by the current thread identifier. A thread-local type is of the form **ThreadLocal** st and is a syntactic sugar for st[].

**Definitions and Program.** We define the set of definitions  $\mathcal{D}$  and programs  $\mathcal{P}$ . Let us define the set of values and variables first.

$$\begin{array}{rcl} i,v\in Val&::=&\{1,2,\ldots\}\cup\{true,false\} & \mbox{Value} \\ x\in ProgVar&::=&\{i,r,\ldots\} & \mbox{Variable} \\ u\in U&::=&x \mid v & \mbox{Variable or Value} \\ T\in Thread&::=&\{1,2,\ldots\} & \mbox{Thread Value} \\ t\in ThreadVar&::=&\{t_1,t_2,\ldots\} & \mbox{Thread Value} \\ \tau&::=&t \mid T & \mbox{Thread Variable or Value} \\ n\in N&::=&\{read,unlock,\ldots\} & \mbox{Method Name} \end{array}$$

The set of objects are defined as follows.

$$o \in O$$

::=  $\phi \mid \phi[u]$  Shared Object

$\theta \in \Theta$  ::=  $o \mid$  **this** Object

$\phi[u]$  denotes uth element of array  $\phi$ .

Let *Label* denote the set of labels c.

$$c \in Label ::= \{doRead, doUnlock, \ldots\}$$

Label

The set of definitions and programs are defined as follows:

The definition section  $\mathcal{D}$  is a sequence of method definitions d. The method definition def  $n_t(x^*) s, r$  defines a method named n with parameters t and  $x^*$  with the body s and the declared order r. The parameter t is the current thread identifier. It is written as a subscript as it is sometimes elided when it is not needed or is evident from the context. A statement s is either a sequence, a conditional, a base object method call, a return statement or a math operation. The statements  $s_1, s_2$  and if  $b \ s \ else \ s$  are sequencing and conditional statements. A condition b is a boolean expression on variables and values. In a method call  $c \triangleright \ x = o.n_{\tau}(u^*), c$  is the label, n is the method name, o is the receiving object,  $\tau$  the thread argument,  $u^*$  are the data arguments and x is the return variable. In a return statement  $c \triangleright$  return u, c is the label and u is the returned value or variable. The semantics of the language will allow out-of-order execution of method calls. Any two labels that are left unordered by the specification may be reordered in the execution. Data and control dependencies in s impose execution order between statements. (Data and control dependencies are standard and defined more precisely in section 10.1.1.) The programmer can explicitly require additional orders for the body s of a defined method as the declared order r. The declared program order r is a binary relation on the set of labels of s. The orders imposed by locks can be declared in r.

The program section  $\mathcal{P}$  is of the form  $p_0, (p_1 || p_2 || ... || p_n)$  where  $p_0$  is the initialization program, and  $p_1, p_2, \ldots, p_n$  are the parallel programs. A sequential program p is either a sequence, a conditional or

a method call. In a method call  $c \triangleright x = n_{\tau}(u^*)$ , c is the label, n is the method name (that is defined in the method definitions),  $\tau$  is the current thread argument,  $u^*$  are the data arguments and x is the return variable. The object **this** is the object of the current specification, is the default receiver object and so is elided.

Well-formedness. Consider a specification  $\pi = (\mathcal{T}, \mathcal{D}, \mathcal{P})$  where  $\mathcal{D} = d^*$  and  $\mathcal{P} = p_0, (p_1 || p_2 || ... || p_n)$ . The specification satisfies the following well-formedness conditions that can be statically enforced. (0) The base name of every object o in  $\mathcal{P}$  is typed in  $\mathcal{T}$ . (1) Every object is initialized in the execution of  $p_0$ . (2) Every branch of every method definition ends in a return statement. (3) The thread argument of each method call is the identifier of the thread in which it is called. (4) The array access index of every thread-local object is the current thread identifier. (5) Labels are unique. The names of the defined methods are unique. (6) Every variable is (statically) bound only once in the program. (7) For each method definition, the transitive closure of its data and control dependencies and the declared orders is acyclic.

**Derived Specification.** We define the function  $basetype : OT \mapsto ST$  that maps a type to its base scalar type as follows: basetype(st) = st, and basetype(st[]) = st. We define the function base name  $basename : \Theta \mapsto \Phi$  that maps an object name to its base name as follows:  $basename(\mathbf{this}) = \mathbf{this}$ ,  $basename(\phi) = \phi$ ,  $basename(\phi[u]) = \phi$ . Similarly, we define the function index  $index : \Theta \mapsto U$  that maps an object name to its index as follows:  $index(\mathbf{this}) = 0$ ,  $index(\phi) = 0$ ,  $index(\phi[u]) = u$ .

Consider a specification  $\pi = (\mathcal{T}, \mathcal{D}, \mathcal{P})$  where  $\mathcal{D} = d^*$  and  $\mathcal{P} = p_0, (p_1 || p_2 || ... || p_n)$ . We define the function  $\mathcal{T}_{base}$  as follows:  $\mathcal{T}_{base}(o) = basetype(\mathcal{T}(basename(o)))$ . The names of methods defined in a program are unique. Thus, we define  $par1_{\pi} \colon N \mapsto ProgVar$  that maps method names to their first parameter. Similarly,  $param2_{\pi}$  and  $tpar_{\pi}$  are defined that map method names to their second parameter and current thread parameter. As the labels of a program are unique, we define the function  $obj_{\pi} \colon Label \mapsto \Theta$  that maps the label of a method call to it receiver object. Similarly, the functions  $index_{\pi}$ ,  $name_{\pi}$ ,  $thread_{\pi}$ ,  $arg1_{\pi}$ ,  $arg2_{\pi}$  and  $retv_{\pi}$  map the label of a method call to the array index of the receiver object, the name of the method, the current thread argument, the first and second argument and the return variable of the method call. Let the *execution condition* of a statement be the conjunction of all of its enclosing if or else conditions. Let the function  $cond_{\pi} \colon Label \mapsto BCond$  map the label of method calls to their execution condition. For conciseness, we treat return statements with the same notation as method calls. For a return statement, we let  $name_{\pi}$  and  $arg1_{\pi}$  map to *return* and the argument of the return statement respectively. For example, consider the following method definition.

def

$$n_t(i, x)$$

if  $(i > 1)$

if  $(x < 2)$

$c_1 \triangleright y = r[i].write_t(x),$

$c_2 \triangleright$  return 1

An if-then statement is a syntactic sugar for an if-then-else statement where the else branch is a call on a dummy object. For example above, we have  $tpar_{\pi}(n) = t$ ,  $par1_{\pi}(n) = i$ ,  $param2_{\pi}(n) = x$ ,  $obj_{\pi}(c_1) = r[i]$ ,  $index_{\pi}(c_1) = i$ ,  $name_{\pi}(c_1) = write$ ,  $thread_{\pi}(c_1) = t$ ,  $arg1_{\pi}(c_1) = x$ ,  $retv_{\pi}(c_1) = y$ ,  $cond_{\pi}(c_1) = (i > 1) \land (x < 2)$ ,  $name_{\pi}(c_2) = return$  and  $arg1_{\pi}(c_2) = 1$ .

Let Labels(s) denote the set of labels in s. Let  $Labels_{\pi}(n)$  denote the set of labels in the body of n. Let  $Returns_{\pi}(n)$  denote the set of labels of return statements in the body of n. Let  $Labels(\mathcal{P})$ denote the set of labels in  $\mathcal{P}$ . Let  $Labels(\pi)$  denote the set of labels in  $\pi$ . Let  $Calls_{\pi}(\phi, n)$  denote the set of labels of call statements where the method name n is called on the base object name  $\phi$ . Let  $PreReturns_{\pi}(c)$  denote the set of labels of the return statements before the statement labeled cin  $\pi$ . (The sets  $Calls_{\pi}(\phi, n)$  and  $PreReturns_{\pi}(c)$  are more precisely defined in section 10.1.1.)

Let  $\rightarrow_n$  denote the irreflexive transitive closure of the data and control dependencies and the declared order of n. Let the program order  $\rightarrow_{\pi}$  be the irreflexive partial order on  $Labels(\pi)$  defined as the union of the following (1) the initialization order (that orders labels of  $p_0$  before labels of parallel programs), (2) the sequential order of the sequential programs  $p_i$  (3) For each method definition n, the order  $\rightarrow_n$ .

### 2.2.2 TM Algorithm Specification

A transactional memory specification is  $\pi = (\mathcal{T}, \mathcal{D}, \mathcal{P})$  where

$$\mathcal{D} = \operatorname{def} \operatorname{init}_{t}() s_{0}, r_{0}, \qquad (2.1)$$

$$\operatorname{def} \operatorname{read}_{t}(i) s_{1}, r_{1}, \\$$

$$\operatorname{def} \operatorname{write}_{t}(i, v) s_{2}, r_{2}, \\$$

$$\operatorname{def} \operatorname{commit}_{t}() s_{3}, r_{3}, \\$$

$$d^{*}$$

$$\mathcal{P} = \operatorname{tran}_{0}, (\operatorname{tran}_{1} \parallel \operatorname{tran}_{2} \parallel ... \parallel \operatorname{tran}_{n}) \qquad (2.2)$$

Transactional memory is an object that encapsulates a set of locations. Each location i stores a value v. It has four methods  $init_t()$ ,  $read_t(i)$ ,  $write_t(i, v)$  and  $commit_t()$ . The method call  $init_t()$  initializes the transaction t. The method call  $read_t(i)$  returns the value of location i or  $\mathbb{A}$  (if the transaction is aborted). The method  $write_t(i, v)$  writes v to location i and returns ok (if the operation is completed successfully) or returns  $\mathbb{A}$  (if the transaction is aborted). The method  $commit_t()$  tries to commit transaction t and returns  $\mathbb{C}$  (if the transaction is successfully committed) or returns  $\mathbb{A}$  (if it is aborted). The three specific symbols  $\mathbb{C}$ ,  $\mathbb{A}$  and ok are returned in specification of transactional memory algorithms to denote commitment or abortion of the transaction and normal completed and are not used as values of locations.

The initializing transaction  $trans_0$  that initializes every location to zero is defined as follows:

$$trans_{0} := IL_{0} \triangleright init_{0}(); \qquad (2.3)$$

$$c_{00} \triangleright write_{0}(0,0); \\ c_{01} \triangleright write_{0}(1,0); \\ \dots \\ c_{0m} \triangleright write_{0}(m,0); \\ CL_{0} \triangleright commit_{0}()$$

Each transaction  $trans_j$   $1 \le j \le n$  is defined as follows:

$$trans_{j} := IL_{j} \triangleright init_{j}(); \qquad (2.4)$$

$$op_{j}$$

$$op_{j} := c \triangleright x = read_{j}(v_{1}, v_{2});$$

$$if (\neg(x = \mathbb{A}))$$

$$op_{j}$$

$$| c \triangleright x = write_{j}(v);$$

$$if (\neg(x = \mathbb{A}))$$

$$op_{j}$$

$$| CL_{j} \triangleright commit_{j}()$$

Note that this dissertation does not consider non-transactional accesses and publication/privatization safety.

Well-formedness. The *init* method returns ok. The *read* method does not return ok or  $\mathbb{C}$ . The *write* method does not return  $\mathbb{C}$ . The *commit* method either returns  $\mathbb{C}$  or  $\mathbb{A}$ .

$\forall c \in Returns_{\pi}(init) \colon arg1_{\pi}(c) = ok$

$\forall c \in Returns_{\pi}(read) \colon arg1_{\pi}(c) \neq ok \land arg1_{\pi}(c) \neq \mathbb{C}$

$$\forall c \in Returns_{\pi}(write) \colon arg1_{\pi}(c) \neq \mathbb{C}$$

$$\forall c \in Returns_{\pi}(commit) : arg1_{\pi}(c) = \mathbb{C} \lor arg1_{\pi}(c) = \mathbb{A}$$

In addition, it is assumed that in every execution of the transaction  $trans_0$ , all the *write* method calls return ok.

Let  $\Pi_{TM}$  denote the set of transactional memory specifications.

We define two functions initOf and commitOf that map a thread value to its initialization and commitment labels.

$$initOf(T) = IL_T$$

(2.5)

$$commitOf(T) = CL_T$$

(2.6)

### 2.2.3 Extended Syntax

The core syntax can be used to define expressive syntactic sugar.

As defined above, A thread-local type **ThreadLocal** st is a syntactic sugar for st[].

The boolean expression  $u \neq u'$  is a syntactic sugar for  $\neg(u = u')$ . The boolean expression b is a syntactic sugar for b = true. The statement **return** (u = u') is a syntactic sugar for **if** (u = u')**return** true **else return** false.

A **return** statement without the return argument is used as a syntactic sugar for a return statement that returns a dummy value. An if-then statement is a syntactic sugar for an if-then-else statement where the else branch is a call on a dummy object.

As a convenience, the definition of methods may non-recursively call other defined methods. Note that these calls can always be inlined.

We now define **foreach** statement as a syntactic sugar. The **foreach** statement iterates over sets and maps.

Consider a bounded set of type set. The following **foreach** statement executes the statement s for each member i of set.

$$c \triangleright$$

foreach  $(i \in set)$  (2.7)

s

Let b be a fresh variable name. We define sIter(s, i), the *i*th iteration, as follows:

$$sIter(s,i) = c_i \triangleright b_i = set.contains(i),$$

$$if (b_i)$$

$$sIndexed(s,i)$$

$$(2.8)$$

where sIndexed(s, i) denotes a transformation of s where every label c is replaced by  $c_i$  and every variable x that is assigned in s is replaced by  $x_i$ . The **foreach** statement is a syntactic sugar for sIters(s, 0) that is

$$sIter(s,0),$$

$$sIter(s,1),$$

$$sIter(s,2),$$

$$...$$

$$sIter(s,max)$$

$$(2.9)$$

(where *max* is the maximum value) with the following declared order

$$\forall c \in Labels(sIter(s,i)), c' \in Labels(sIter(s,i+1)): c \to c'$$

$$(2.10)$$

Similarly, consider a bounded map of type map. The following **foreach** statement executes the statement s for each mapping i to v in map.

$$c \triangleright$$

foreach  $((i, v) \in map)$  (2.11)

s

We define mIter(s, i), the *i*the iteration, as follows:

$$mIter(s,i) = c_i \triangleright v_i = map.get(i), \qquad (2.12)$$

$$if (v_i \neq \bot)$$

$$mIndexed(s,i)$$

where mIndexed(s, i) denotes a transformation of s where every label c is replaced by  $c_i$ , v is replaced with  $v_i$ , and every variable x that is assigned in s is replaced by  $x_i$ . We define mIters(s, i), the sequence of iterations starting from iteration i, as follows:

$$mIters(s,i) ::= mIter(s,i),$$

$$mIters(s,i+1)$$

(2.13)

The **foreach** statement is a syntactic sugar for mIters(0) that is

$$mIter(s,0), \qquad (2.14)$$

$$mIter(s,1), \qquad mIter(s,2), \qquad \dots$$

$$mIter(s,max)$$

(where max is the maximum value) with the following declared order

$$\forall c \in Labels(mIter(s, i)), c' \in Labels(mIter(s, i+1)): c \to c'$$

$$(2.15)$$

Now, we extend the syntax with records. A record type definition rt is defined as follows:

| $rec \in Rec$ | ::= | $\{Node, Locator,\}$            | Record Type name |

|---------------|-----|---------------------------------|------------------|

| $rt \in RT$   | ::= | $rec `{` (\phi_i : ot_i)^* `}'$ | Record Type      |

The record type named *rec* is defined as a collection of fields  $\phi_i$  of type  $ot_i$ . The set of statements is extended with the **new** and **clone** statements.

| s | ::= | •••                                               |                 |

|---|-----|---------------------------------------------------|-----------------|

|   |     | $c \triangleright x = \mathbf{new} \ rec \ (`,`)$ | New Statement   |

|   |     | $c \triangleright x = $ <b>clone</b> '('x')'      | Clone Statement |

The **new** statement creates an instance of the record type and returns a reference to it. The **clone** statement creates a clone of the record referenced by the argument and returns a reference to it. The set of objects is extended as follows

$$o \in O ::= \phi \mid \phi[u] \mid$$

Shared Object

$x.\phi \mid x.\phi[u]$

$x.\phi$  denotes the field named  $\phi$  of the record that the variable x references.

### 2.2.4 Example Specifications

As example specifications, we present Dekker algorithm and TL2, a variant of TL2, visible and invisible reads versions of DSTM and McRT TM algorithms.

### Dekker Algorithm Specification.

Dekker algorithm specified in Figure 2.1 provides mutual exclusion for two threads. It uses two atomic registers as flags. Using basic registers can lead to a race and violation of mutual exclusion. Each thread first sets its own flag and then reads the flag of the other thread. The order of writing the flag of the current thread and then reading the flag of the other thread is crucial to the correctness. Reordering these two accesses can violate mutual exclusion. A thread enters its critical region only if it finds the flag of the other thread unset. The type of the flags and the order of accesses to them are explicitly captured in the specification.

| $\mathcal{T}$ :                                                                  |                                         |                                         |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| $f_1$ : AtomicReg                                                                | gister                                  |                                         |  |  |  |

| $f_2$ : AtomicReg                                                                | gister                                  |                                         |  |  |  |

| $\mathcal{D}$ :                                                                  |                                         |                                         |  |  |  |

| def init()                                                                       | def $tryLock1()$                        | def tryLock2()                          |  |  |  |

| $W_{01} \triangleright f_1.write(0),$                                            | $W_1 \triangleright f_1.write(1),$      | $W_2 \triangleright f_2.write(1),$      |  |  |  |

| $W_{02} \triangleright f_2.write(0),$                                            | $R_2 \triangleright  x_2 = f_2.read(),$ | $R_1 \triangleright  x_1 = f_1.read(),$ |  |  |  |

|                                                                                  | <b>if</b> $(x_2 = 0),$                  | <b>if</b> $(x_1 = 0)$                   |  |  |  |

|                                                                                  | $C_{1t} \triangleright$ return true     | $C_{2t} \triangleright$ return $true$   |  |  |  |

|                                                                                  | else                                    | else                                    |  |  |  |

|                                                                                  | $C_{2f} \triangleright$ return false,   |                                         |  |  |  |

|                                                                                  | $W_1 \to R_2,$                          | $W_2 \to R_1;$                          |  |  |  |

| $\mathcal{P} =$                                                                  |                                         |                                         |  |  |  |

| $L_0 \triangleright init(),$                                                     |                                         |                                         |  |  |  |

| $L_1 \triangleright  l_1 = tryLock1()  \   L_2 \triangleright  l_2 = tryLock2()$ |                                         |                                         |  |  |  |

Figure 2.1:  $\pi_{Dekker}$  Dekker Algorithm Specification

#### TL2 Algorithm.

We specify TL2 algorithm [18] in Figure 2.2. Algorithm such as SwissTM [23] are optimizations of TL2.

Synchronization objects. TL2 algorithm uses the following synchronization objects: Value registers reg: an array of type basic register of size equal to the number of locations. Version registers ver: an array of type atomic register of size equal to the number of locations with the initial value 0. Locks *lock*: an array of type try-lock of size equal to the number of locations that are initially released. Global version clock *clock*: a strong counter with the initial value 0. Read version *rver*: a thread-local basic register. Read set *rset*: a thread-local basic set that is initially  $\emptyset$ . Write set *wset*: a thread-local basic map that is initially  $\emptyset$ . Lock set *lset*: a thread-local basic set that is initially  $\emptyset$ .

As observed by previous work, in the original paper, "the authors maintain the version number and the lock bit of every variable in the same memory word" [31], thus, the order of reading the lock and the version of read locations in the commit procedure is ambiguous. In our specification, we treat the lock and the version as separate registers and make the orders explicit.

Algorithm. TL2 is a deferred-update TM algorithm. A value that a transaction t writes to a location is buffered in the write set wset[t] at W01 and is written back to register reg[i] at C16 while t is committing. TL2 records a version in the register ver[i] for the value stored in the register reg[i]. The version register ver[i] is updated to ascending numbers at C17 after a new value is written back to reg[i] at C16. The try-lock lock[i] is used for exclusive access to location i. At commit, the lock lock[i] of each location i in the write set wset[t] is acquired at C01 to C06. (If a lock cannot be acquired, the previously acquired locks are released at C05 and the transaction is aborted.) Then, a new snapshot is read from *clock* at C07. Then, for each location in the read set rset[t], first lock[i]and then ver[i] are read at C10 and C11 and the read is validated. (If a read is not validated, the acquired locks are released at C12 and the transaction is aborted.) Finally, the values buffered in wset[t] are written back at C15 to C18. For each pair in the write set wset[t], the following three operations execute in order. First, the buffered value is written back to reg[i], then ver[i] is updated, and then lock[i] is released. In the *init* method, each transaction t reads the current snapshot version from *clock* at I01 and writes it to the read version register rver[t] at I02. The read version is read at R07 and C08 to validate the read values. To read a location i, a transaction reads ver[i], reg[i], lock[i] and again ver[i] in order at R03 - R06 and then validates the read. (If the validation fails, the transaction is aborted.) Finally, i is added to the read set rset[t] and the read value is returned.

Note that although reg[i] may be read and written by different transactions, it is declared as a basic register. The objects lock[i] and ver[i] rule out racy accesses to reg[i]. The lock lock[i] prevents concurrent writes to reg[i]. If a read from reg[i] executes concurrently with a write to it, reads from ver[i] and the subsequent checks abort the read.

| $\mathcal{T}$ :                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $reg: \mathbf{BasicRegister}[],$                                      | <i>rver</i> : ThreadLocal BasicRegister,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |