# On the Practical Design of a Sliding Mode Voltage Controlled Buck Converter

Siew-Chong Tan, Student Member, IEEE, Y. M. Lai, Member, IEEE, Martin K. H. Cheung, and Chi K. Tse, Senior Member, IEEE

Abstract—This paper presents a simple and systematic approach to the design of a practical sliding mode voltage controller for buck converters operating in continuous conduction mode. Various aspects of the design, including the associated practical problems and the proposed solutions, are detailed. A simple and easy-to-follow design procedure is also described. Experimental results are presented to illustrate the design procedure.

*Index Terms*—Buck converter, continuous conduction mode, hysteresis band, sliding mode control, variable structure system.

#### I. INTRODUCTION

S LIDING mode (SM) controllers were introduced initially for variable structure systems (VSS) [1]–[4]. Characterized by switching, dc/dc converters are inherently variable structured [5]. Therefore, it is appropriate to apply SM controllers to dc/dc converters. This is especially true for buck converters operating in the continuous conduction mode (CCM), which have measurable continuous controllable states (output voltage and its time derivative) [5], [6].

Although well known for their stability and robustness toward parameter, line, and load variations (ability to handle large transients), SM controllers are seldom used in power converters. This is mainly due to the lack of understanding in its design principle by power supply engineers [7], as well as the lack of a systematic procedure in existing literature, which can be used to develop such controllers. This can be attributed to the fact that much of the work on the subject has been reported from the control's viewpoint, rather than the circuit's viewpoint. Hence, the focus had been on the theoretical aspects of the control, while the practical aspects of the implementation are still rarely discussed [5]–[13].

Consequently, many design issues pertaining to the implementation of SM controlled converters have not been sufficiently covered. One such issue is on the design and constriction of the converter's switching frequency. Although different methods (hysteresis; constant sampling frequency; constant on-time; constant switching frequency; and limited maximum switching frequency) were proposed to limit the switching frequency [14], they fall short of a set of systematic design methods and implementation criteria.

The authors are with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hong Kong (e-mail: ensctan@ eie.polyu.edu.hk).

Digital Object Identifier 10.1109/TPEL.2004.842977

Concurrently, there was also an alternative approach of limiting the switching frequency, which is through the incorporation of a constant ramp function into the controller to determine the switching of the converter [7], [15]. The main advantage of this approach is that the switching frequency is constant under all operating conditions, and it is easily controllable through varying the ramp signal. Basically, there are two methods of implementing this constant frequency operation. The first method is to encode the ramp signal into the discontinuous SM switching function of the controller [15]. The advantage of this method is that it is straightforward and simple to implement. However, this comes at an expense of additional hardware circuitries, as well as deteriorated transient response in the system's performance caused by the superposition of the ramp function upon the SM switching function. The second method is to compare the continuous input signal (commonly termed as  $u_{eq}$ ) generated from the SM equations derived from the equivalent control method, with the ramp waveform to create the switching operation [7]. Conceptually, this is analogous to the way in which fixed switching frequency is obtained in classical PWM control schemes whereby the control signal is compared to the ramp waveform [16]. The advantage of this method over the previous method is that there is no need for additional hardware circuitries since the switching function is replaced by the PWM modulator and that transient response is not deteriorated. However, the drawback of this method is that the implementation of the equivalent control law to obtain  $u_{eq}$  requires computations that are too complicated to be implemented with analog controllers [8]. On the other hand, even though possible, the implementation of digital controllers on power converters is costly and unpopular.

Considering that these methods were introduced with the primary objective of suppressing high switching frequency [14], their disadvantages probably outweigh their advantages since this may easily be performed by controlling the hysteresis band of the SM switching function.

Hence, one objective of this paper is to introduce a mathematical model for the hysteresis band method that was originally proposed in [14], so that engineers may conveniently adopt it for the implementation of the SM controller. Nevertheless, this paper is still principally focused on introducing a simple approach that is easily applicable in the development of a sliding mode voltage controlled (SMVC) buck converter, to bridge the gap between the control principle and circuit implementation. To present a complete exposition, mathematical derivations and theoretical analyzes which extend from the work of [5] are firstly performed. Moreover, the approach is presented in a manner

0885-8993/\$20.00 © 2005 IEEE

Manuscript received August 22, 2003; revised July 30, 2004. This work was supported by a Grant provided by The Hong Kong Polytechnic University under Project G-T379. Recommended by Associate Editor P. Mattavelli.

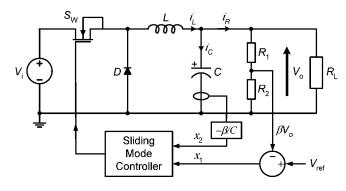

Fig. 1. Basic structure of an SMVC buck converter.

involving only a standard SMVC buck converter model and some simple guided steps and design equations. This allows designer to skip through laborious preliminary derivations when performing the controller's design.

Section II details the theoretical derivation of an ideal SMVC buck converter, the description of the problems associated with practical implementation, and the proposed solutions to these problems. Section III presents a standard converter model with a simple design procedure. In Section IV, the experimental results under various operating conditions are given. These experiments were conducted on a converter that was designed using the proposed procedure. Finally, Section V gives the conclusion to the paper.

## II. THEORETICAL DERIVATION

This section covers the theoretical aspects of the SMVC converter. Complete mathematical derivations of both the ideal and practical converter designs are presented.

#### A. Mathematical Model of Buck Converter

To illustrate the underlying principle, the state space description of the buck converter under SM voltage control, where the control parameters are the output voltage error and the voltage error dynamics (in phase canonical form) [8], is first discussed.

Fig. 1 shows the schematic diagram of an SMVC buck converter. Here, the voltage error  $x_1$  and the voltage error dynamics (or the rate of change of voltage error)  $x_2$  under CCM, can be expressed as

$$x_{1} = V_{\text{ref}} - \beta V_{\text{o}}$$

$$x_{2} = \dot{x}_{1} = -\beta \frac{dV_{\text{o}}}{dt} = \frac{\beta}{C} \left( \frac{V_{\text{o}}}{R_{\text{L}}} - \int \frac{uV_{\text{i}} - V_{\text{o}}}{L} dt \right) \quad (1)$$

where C, L,  $R_{\rm L}$  are the capacitance, inductance, and load resistance, respectively,  $V_{\rm ref}$ ,  $V_{\rm i}$ , and  $\beta V_{\rm o}$  are the reference, input, and sensed output voltage, respectively, u = 1 or 0 is the switching state of power switch  $S_{\rm W}$ . Then, by differentiating (1) with respect to time, the state space model can be obtained as

$$\begin{bmatrix} \dot{x_1} \\ \dot{x_2} \end{bmatrix} = \begin{bmatrix} 0 & 1 \\ -\frac{1}{LC} & -\frac{1}{R_{\rm L}C} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} 0 \\ -\frac{\beta V_{\rm i}}{LC} \end{bmatrix} u + \begin{bmatrix} 0 \\ \frac{V_{\rm ref}}{LC} \end{bmatrix}.$$

(2)

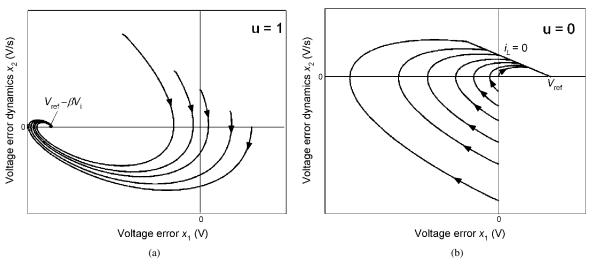

The graphical representation of individual substructures of the system with u = 1 and u = 0, for different starting  $(x_1, x_2)$ conditions, are shown in Fig. 2. It can be seen that when u = 1, the phase trajectory for any arbitrary starting position on the phase plane will converge to the equilibrium point  $(x_1 = V_{\text{ref}} - \beta V_i, x_2 = 0)$  after some finite time period. Similarly, when u = 0, all the trajectories converge to equilibrium point  $(x_1 = V_{\text{ref}}, x_2 = 0)$ . These characteristics will be exploited for the design of the SM voltage controller.

#### B. Design of an Ideal SM Voltage Controller

In SM control, the controller employs a switching function to decide its input states to the system [1]. For SM voltage controller, the switching state u can be determined from the control parameters  $x_1$  and  $x_2$  using the switching function

$$S = \alpha x_1 + x_2 = J \boldsymbol{x} \tag{3}$$

where  $\alpha$  is the control parameter (termed as sliding coefficient) to be designed;  $J = [\alpha, 1]$ ; and  $x = [x_1, x_2]^T$ . By enforcing S = 0, a sliding line with gradient  $\alpha$  can be obtained. The purpose of this sliding line is to serve as a boundary to split the phase plane into two regions. Each of this region is specified with a switching state to direct the phase trajectory toward the sliding line. It is only when the phase trajectory reaches and tracks the sliding line toward the origin that the system is considered to be stable, i.e.,  $x_1 = 0$  and  $x_2 = 0$ .

The specification of the switching state for each sector in the case of a second order system like the buck converter can be graphically performed by observing the behavior of the trajectories in Fig. 3, which is a combination of the two plots in Fig. 2. It can be observed that if the phase trajectory is at any arbitrary position above the sliding line (S = 0), e.g., point M, u = 1 must be employed so that the trajectory is directed toward the sliding line. Conversely, when the phase trajectory is at any position below sliding line, e.g., point N, u = 0 must be employed for the trajectory to be directed toward the sliding line. This forms the basis for the control law

$$u = \begin{cases} 1 = 'ON' & \text{when } S > 0\\ 0 = 'OFF' & \text{when } S < 0. \end{cases}$$

(4)

Although abiding the hitting condition [5], which states that the system trajectory must eventually reach the sliding line, the control law in (4) only provides the general requirement that the trajectories will be driven toward the sliding line. However, there is no assurance that the trajectory can be maintained on this line. To ensure that the trajectory is maintained on the sliding line, the existence condition, which is derived from Lyapunov's second method [17] to determine asymptotic stability, must be obeyed [1], [6]

$$\lim_{S \to 0} S \cdot \dot{S} < 0.$$

<sup>(5)</sup>

Thus, by substituting the time derivative of (3), the condition for SM control to exist is

$$\dot{S} = \begin{cases} J\dot{x} < 0 & \text{for } 0 < S < \xi \\ J\dot{x} > 0 & \text{for } -\xi < S < 0 \end{cases}$$

(6)

Authorized licensed use limited to: Hong Kong Polytechnic University. Downloaded on December 17, 2008 at 04:14 from IEEE Xplore. Restrictions apply

Fig. 2. Phase trajectories of the substructure corresponding to (a) u = 1 and (b) u = 0 for different starting  $(x_1, x_2)$  positions.

Fig. 3. Phase trajectories of the substructure corresponding to both u = 1 and u = 0 for different  $(x_1, x_2)$  starting positions.

where  $\xi$  is an arbitrarily small positive quantity. Substituting (2) and (4) into (6), the inequalities become

$$\lambda_1 = \left(\alpha - \frac{1}{R_{\rm L}C}\right) x_2 - \frac{1}{LC} x_1 + \frac{V_{\rm ref} - \beta V_{\rm i}}{LC} < 0$$

$$\lambda_2 = \left(\alpha - \frac{1}{R_{\rm L}C}\right) x_2 - \frac{1}{LC} x_1 + \frac{V_{\rm ref}}{LC} > 0 \tag{7}$$

where

$$\lambda_1 = J\dot{x} \quad \text{for} \quad 0 < S < \xi$$

$$\lambda_2 = J\dot{x} \quad \text{for} \quad -\xi < S < 0. \tag{8}$$

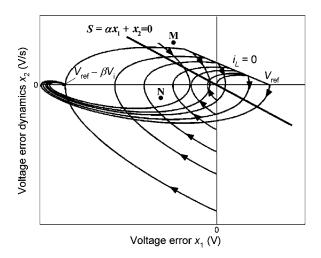

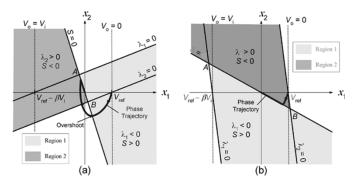

The above conditions are depicted in Fig. 4 for the two respective situations: (a)  $\alpha > 1/R_{\rm L}C$  and (b)  $\alpha < 1/R_{\rm L}C$ . In both figures, Region 1 represents  $\lambda_1 < 0$  and Region 2 represents  $\lambda_2 > 0$ . SM will only occur on the portion of the sliding line, S = 0, that covers both Regions 1 and 2. In this case, this portion is within A and B, where A is the intersection of S = 0 and  $\lambda_1 = 0$ ; and B is the intersection of S = 0 and  $\lambda_2 = 0$ . Since the phase trajectory will slide to the origin only when it touches S = 0 within AB, it will overshoot the sliding line if the trajectory landed

Fig. 4. Regions of existence of SM in phase plane: (a)  $\alpha > 1/R_{\rm L}C$  and (b)  $\alpha < 1/R_{\rm L}C$ .

outside AB [as shown in Fig. 4(a)]. This results in an overshoot in the voltage response when  $\alpha > 1/R_{\rm L}C$ . Hence, for the practical condition that  $0 \le V_{\rm o} \le V_{\rm i}$ , the system trajectory will be bounded within the region  $V_{\rm ref} - \beta V_{\rm i} < x_1 < V_{\rm ref}$ . Taking this into account, the maximum existence region will occur when  $\alpha = 1/R_{\rm L}C$ .

Furthermore, by manipulating (3), we have

$$\alpha x_1 + \dot{x}_1 = 0 \Rightarrow x_1(t) = x_1(t_0) e^{-\alpha(t - t_0)}$$

(9)

where  $t_0$  is any point in time and  $x_1(t_0)$  is the voltage error at  $t_0$ . From this, it can be understood that the choice of  $\alpha$  in the SM design is more than controlling the existence region. It also controls the dynamic response of the system with a first order time constant of

$$\tau = \frac{1}{\alpha}.$$

(10)

Hence, to ensure that  $\alpha$  is high enough for fast dynamic response and low enough to maintain a large existence region, it is proposed to set

$$\alpha = \frac{1}{R_{\rm L}C}.\tag{11}$$

It should however be noted that  $\alpha$  must be a positive quantity to achieve system stability. This can be analyzed from (7) and (9) by the substitution of a negative  $\alpha$  quantity, resulting in, respectively, a phase trajectory that moves away from the phase plane origin and an  $x_1$  that does not tend to zero.

# C. Design of a Practical SM Voltage Controller

In this section, a practical SM voltage controller is considered. The sliding line defined in the previous section is redefined to accommodate for hardware limitations. Additionally, a hysteresis band is introduced to the sliding line as a form of frequency control to suppress high frequency switching. The relationship of hysteresis band versus switching frequency of the SMVC buck converter is derived.

1) Redefinition of Sliding Line: As previously mentioned, SM controller requires the continuous assessment of the parameters  $x_1$  and  $x_2$  for its control. By substituting (1) and (9) into (3), we have

$$S = k_1 (V_{\text{ref}} - \beta V_{\text{o}}) + k_2 i_C \tag{12}$$

where  $k_1 = 1/R_{\rm L}C$  and  $k_2 = -\beta/C$ . From the equation, the terms ( $V_{\rm ref} - \beta V_0$ ) and  $i_C$  are the feedback state variables from the converter that should be amplified by gain coefficients  $k_1$  and  $k_2$  respectively, before a summation is performed. This, from a practical perspective, does generate a problem. Noting that capacitance C in power converters is usually in the microfarad ( $\mu$ F) range, its inverse term will be significantly higher than  $\beta$  and  $R_L$ . Hence, the overall gain coefficients  $k_1$  and  $k_2$ will become too high for practical implementation. If forcibly implemented, the feedback signals may be driven into saturation, thereby causing (12) to provide unreliable information for the control.

In view of that, it is simpler to reconfigure the switching function to the following description:

$$S = \frac{C}{\beta}\alpha x_1 + \frac{C}{\beta}x_2 = Qx \tag{13}$$

where  $\boldsymbol{Q} = [(C/\beta)\alpha, C/\beta]$ ; and  $\boldsymbol{x} = [x_1, x_2]^T$ . From (1) and (9), we get

$$S = \frac{1}{\beta R_{\rm L}} (V_{\rm ref} - \beta V_{\rm o}) - i_C.$$

<sup>(14)</sup>

Thus, the practical implementation of S becomes independent of C, thereby reducing the amplification of the feedback signals. With this sliding line, the conditions for SM control to exist are

$$\lambda_{1} = \left(\frac{C}{\beta}\alpha - \frac{1}{\beta R_{\rm L}}\right)x_{2} - \frac{1}{\beta L}x_{1} + \frac{V_{\rm ref} - \beta V_{\rm i}}{\beta L} < 0$$

$$\lambda_{2} = \left(\frac{C}{\beta}\alpha - \frac{1}{\beta R_{\rm L}}\right)x_{2} - \frac{1}{\beta L}x_{1} + \frac{V_{\rm ref}}{\beta L} > 0 \tag{15}$$

where

$$\lambda_1 = \boldsymbol{Q} \boldsymbol{\dot{x}} \quad \text{for} \quad 0 < S < \xi$$

$$\lambda_2 = \boldsymbol{Q} \boldsymbol{\dot{x}} \quad \text{for} \quad -\xi < S < 0. \tag{16}$$

An interesting point here is that although there is modification to the  $\lambda$  equations, the maximum existence region will still occur

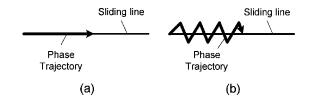

Fig. 5. Phase trajectory for (a) ideal SM operation and (b) actual SM operation with chattering.

at  $\alpha = 1/R_{\rm L}C$ . In addition, the response time is still maintained at  $\tau = 1/\alpha$ .

2) Introduction of Hysteresis Band: Ideally, a converter will switch at infinite frequency with its phase trajectory moving on the sliding line when it enters SM operation [see Fig. 5(a)]. However, in the presence of switching imperfections, such as switching time constant and time delay, this is not possible. The discontinuity in the feedback control will produce a particular dynamic behavior in the vicinity of the surface trajectory known as chattering [see Fig. 5(b)] [1]–[4].

If the chattering is left uncontrolled, the converter system will become self-oscillating at a very high switching frequency corresponding to the chattering dynamics. This is undesirable as high switching frequency will result in excessive switching losses, inductor and transformer core losses, and EMI noise issues [18]. Hence, most PWM power supplies are designed to operate with switching frequencies between 40 kHz and 200 kHz [18]. Furthermore, since chattering is introduced by the imperfection of controller ICs, gate driver, and power switches, it is difficult to predict the exact switching frequency. Hence, the design of the converter and the selection of the components will be difficult.

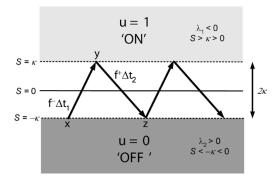

To solve these problems, the control law in (4) is redefined as

$$u = \begin{cases} 1 = \text{'ON'} & \text{when } S > \kappa \\ 0 = \text{'OFF'} & \text{when } S < -\kappa \end{cases}$$

(17)

where  $\kappa$  is an arbitrarily small value. The reason for introducing a hysteresis band with the boundary conditions  $S = \kappa$  and  $S = -\kappa$  is to provide a form of control to the switching frequency of the converter. This is a method commonly employed to alleviate the chattering effect of SM control [17]. With this modification, the operation is altered such that if the parameters of the state variables are such that  $S > \kappa$ , switch  $S_W$  of buck converter will turn on. Conversely, it will turn off when  $S < -\kappa$ . In the region  $-\kappa \leq S \leq \kappa$ ,  $S_W$  remains in its previous state. Thus, by introducing a region  $-\kappa \leq S \leq \kappa$  where no switching occurs, the maximum switching frequency of the SM controller can be controlled. This alleviates the effect of chattering. Additionally, it is now possible to control the frequency of the operation by varying the magnitude of  $\kappa$ .

3) Calculation of Switching Frequency: To control the switching frequency of the converter, the relationship between the hysteresis band,  $\kappa$ , and switching frequency,  $f_{\rm S}$ , must be known.

Fig. 6 shows the magnified view of the phase trajectory when it is operating in SM.  $f^-$  and  $f^+$  are the vectors of state variable

Fig. 6. Magnified view of the phase trajectory in SM operation.

velocity for u = 0 and u = 1, respectively. It was previously derived in [2] that

$$\Delta t_1 = \frac{2\kappa}{\nabla S \cdot \mathbf{f}^-}$$

$$\Delta t_2 = \frac{-2\kappa}{\nabla S \cdot \mathbf{f}^+} \tag{18}$$

where  $\Delta t_1$  is the time taken for vector  $\mathbf{f}^-$  to move from position x to y; and  $\Delta t_2$  is the time taken for vector  $\mathbf{f}^+$  to move from position y to z. By substituting in (18)

$$\nabla S \cdot \mathbf{f} = \sum_{i=1}^{n} \frac{\partial S}{\partial x_i} \frac{dx_i}{dt} = \frac{dS}{dt} = \dot{S}$$

(19)

where

$$\mathbf{f} = \begin{cases} \mathbf{f}^- & \text{for } u = 0\\ \mathbf{f}^+ & \text{for } u = 1 \end{cases}$$

we have

$$\Delta t_1 = \frac{2\kappa}{\dot{S}_{u=0}} = \frac{2\kappa}{\lambda_2}$$

$$\Delta t_2 = \frac{-2\kappa}{\dot{S}_{u=1}} = \frac{-2\kappa}{\lambda_1}.$$

(20)

Further substitution of (15) into (20) results in

$$\Delta t_1 = \frac{2\kappa}{\left(\frac{C}{\beta}\alpha - \frac{1}{\beta R_{\rm L}}\right)x_2 - \frac{1}{\beta L}x_1 + \frac{V_{\rm ref}}{\beta L}}$$

$$\Delta t_2 = \frac{-2\kappa}{\left(\frac{C}{\beta}\alpha - \frac{1}{\beta R_{\rm L}}\right)x_2 - \frac{1}{\beta L}x_1 + \frac{V_{\rm ref} - \beta V_{\rm i}}{\beta L}}.$$

(21)

Therefore, the time period for one cycle in which the phase trajectory moves from position x to z is equivalent to (22) shown at the bottom of the page. Since the cycle is repeated (cyclic) throughout the SM steady-state operation, the frequency of the converter when it is operating in SM can be expressed as (23) shown at the bottom of the page. Using  $\alpha = 1/R_{\rm L}C$ , the above equation becomes

$$f_{\rm S} = \frac{V_{\rm o} \left(1 - \frac{V_{\rm o}}{V_{\rm i}}\right)}{2\kappa L}.$$

(24)

Considering that  $V_i$  and  $V_o$  are nonconstant parameters consisting of respectively dc signals of  $\overline{V_i}$  and  $\overline{V_o}$  and time varying perturbations of  $\widetilde{V_i}$  and  $\widetilde{V_o}$ , we can resolve (24) into

$$f_{\rm S} = \overline{f_{\rm S}} + \widetilde{f}_{\rm S} \tag{25}$$

using small-signal approximation where

$$\overline{f_{\rm S}} = \frac{\overline{V_{\rm o}} \left(1 - \frac{V_{\rm o}}{\overline{V_{\rm i}}}\right)}{2\kappa L} \tag{26}$$

$$\widetilde{f}_{\rm S} = \frac{\widetilde{V_{\rm o}} \left( 1 - \frac{2\overline{V_{\rm o}}}{\overline{V_{\rm i}} + \widetilde{V_{\rm i}}} \right)}{2\kappa L} \tag{27}$$

with  $\overline{f_S}$  representing the steady-state (nominal cyclic) switching frequency and  $\tilde{f}_S$  representing the ac varying (perturbed) frequency of the converter. This indicates that if there are significantly small variations in the input and output voltages, i.e.,  $\overline{V_i} \gg \widetilde{V_i}$  and  $\overline{V_o} \gg \widetilde{V_o}$ , the converter will be operating at a steady-state switching frequency of  $\overline{f_S}$  with very little ac frequency perturbation, i.e.,  $\overline{f_S} \gg \widetilde{f_S}$ . Since only the nominal steady-state operating conditions are considered in the controller's design, only (26) is required when it comes to the design of the steady-state switching frequency of the converter.

#### **III. STANDARD DESIGN PROCEDURE**

A standard SMVC buck converter module is proposed in this section, along with a step by step design procedure for practical implementation. A design example is provided for illustration.

#### A. Standard SMVC Converter Model

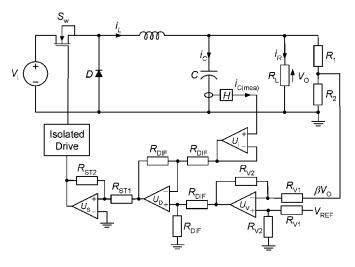

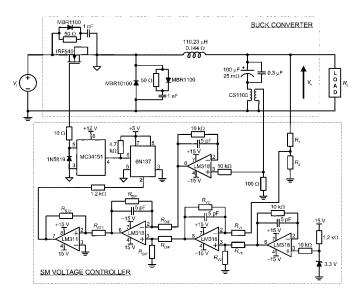

Fig. 7 shows the proposed SMVC buck converter. The SM controller comprises basically a differential amplifier circuit  $U_V$ ; a voltage follower circuit  $U_i$ ; a difference amplifier circuit  $U_D$ ; and a noninverting Schmitt Trigger circuit  $U_S$ . Similar to

$$T = \Delta t_1 + \Delta t_2 = \frac{-2\kappa V_{\rm i}}{\left[\left(\frac{C}{\beta}\alpha - \frac{1}{\beta R_{\rm L}}\right)x_2\right]^2 L + \left[\left(\frac{C}{\beta}\alpha - \frac{1}{\beta R_{\rm L}}\right)x_2\right](2V_{\rm o} - V_{\rm i}) + \frac{V_{\rm o}(V_{\rm o} - V_{\rm i})}{L}.$$

(22)

$$f_{\rm S} = \frac{1}{T} = \frac{\left[ \left( \frac{C}{\beta} \alpha - \frac{1}{\beta R_{\rm L}} \right) x_2 \right]^2 L + \left[ \left( \frac{C}{\beta} \alpha - \frac{1}{\beta R_{\rm L}} \right) x_2 \right] (2V_{\rm o} - V_{\rm i}) + \frac{V_{\rm o}(V_{\rm o} - V_{\rm i})}{L} - 2\kappa V_{\rm i}$$

(23)

Fig. 7. Standard SMVC buck converter.

TABLE I

Specifications of Buck Converter

| Description                 | Parameter     | Nominal Value |

|-----------------------------|---------------|---------------|

| Input voltage               | $V_{ m i}$    | 24 V          |

| Minimum capacitance         | $C_{\min}$    | 4 $\mu$ F     |

| Critical inductance         | $L_{ m crit}$ | 34.28 $\mu H$ |

| Desired switching frequency | $f_{ m Sd}$   | 200 kHz       |

| Load resistance             | $R_{\rm L}$   | 6Ω            |

| Desired output voltage      | $V_{ m od}$   | 12 V          |

conventional schemes, the feedback sensing network for  $V_0$  is provided by the voltage divider circuit,  $R_1$  and  $R_2$ . Additionally, a low resistance current transformer is placed in series with the filter capacitor to obtain the capacitor current,  $i_C$ .

#### B. Design Steps

The design of the buck converter is well covered in the literature [18]–[20]. Our discussion here starts with the assumption that the converter's parameters are known and are given in Table I.

These parameters are calculated on the basis that the converter is to be operated in CCM for  $V_i = 13$  V to 30 V and  $i_R = 0.5$  A to 4 A. The maximum peak to peak ripple voltage is 50 mV.

1) Step 1: The current sensing gain, H, is set at a value such that the measured capacitor current,  $i_{C(\text{mea})}$  is equal to the actual capacitor current,  $i_C$ .

2) Step 2: Setting reference voltage  $V_{ref} = 3.3 \text{ V}, \beta$  is calculated using the expression

$$\beta = \frac{V_{\text{ref}}}{V_{\text{od}}} = \frac{3.3}{12} = 0.275.$$

(28)

Also,  $R_1$  and  $R_2$  are related by

$$R_2 = \frac{\beta}{1-\beta} R_1. \tag{29}$$

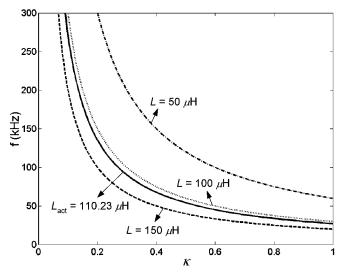

Fig. 8. Calculated  $\kappa$  values for inductances of 50  $\mu$ H, 100  $\mu$ H, 110.23  $\mu$ H (actual inductance), and 150  $\mu$ H at switching frequencies of up to 300 kHz.

Choosing  $R_1$  as 870  $\Omega$ , we get  $R_2 = 330 \Omega$ .

3) Step 3: From (14), the gain required for the amplification of the signal  $(V_{ref} - \beta V_o)$  is  $1/\beta R_L$ . Hence,  $R_{V_1}$  and  $R_{V_2}$  are related by

$$R_{\mathbf{V}1} = (\beta R_{\mathbf{L}}) R_{\mathbf{V}2}.$$

(30)

Choosing  $R_{V2} = 20 \text{ k}\Omega$ , we get  $R_{V1} = 33 \text{ k}\Omega$ . Additionally, the resistors,  $R_{\text{DIF}}$ , for the difference amplifier circuit:  $U_{\text{D}}$ , are chosen as 10 k $\Omega$ .

4) Step 4: The parameter of the hysteresis band,  $\kappa$ , can be obtained from the re-arranged form of (26), i.e.,

$$\kappa = \frac{V_{\rm od} \left(1 - \frac{V_{\rm od}}{V_{\rm i}}\right)}{2f_{\rm Sd}L} \tag{31}$$

where  $V_{\rm i}$ ,  $V_{\rm od}$ , and  $f_{\rm Sd}$  are the nominal parameters of the converter. A plot giving the calculated  $\kappa$  values for different inductances and switching frequencies is shown in Fig. 8.

The actual inductance,  $L_{act}$ , used in the design is 110.23  $\mu$ H. It should be noted that  $L_{act} \ge L_{crit}$  for CCM. Thus, substituting  $L = 110.23 \ \mu$ H into (31),  $\kappa$  is calculated as 0.136.<sup>1</sup>

5) Step 5: The setting of  $\kappa$  for the hysteresis band can be performed by adjusting the ratio of  $R_{\rm ST1}$  and  $R_{\rm ST2}$  of  $U_{\rm S}$ , using an equation derived from the mathematical description of a noninverting Schmitt Trigger (38), i.e.,

$$R_{\rm ST2} = \frac{R_{\rm ST1}(V_{\rm CC}^+ - V_{\rm CC}^-)}{2\kappa}$$

(32)

where  $V_{\rm CC}^+$  and  $V_{\rm CC}^-$  are respectively the positive and negative voltage supplies to Schmitt Trigger  $U_{\rm S}$ . Choosing  $R_{\rm ST1}$  as 110  $\Omega$ , resistor  $R_{\rm ST2}$  is set as 12 k $\Omega$ .

<sup>1</sup>The presence of hysteresis band in switching function introduces an error in the output voltage. It is important to limit the hysteresis band  $\kappa$  to a small value to minimize this error. On the other hand, if  $\kappa$  is too small, it may be very sensitive to change of  $\kappa$  (i.e., high df/d $\kappa$ ). A good value is to set  $\kappa$  in the range  $0.1 \le \kappa \le 0.2$ . Otherwise, a different inductance may be used to keep  $\kappa$  within the range.

Fig. 9. Full schematic diagram of the SMVC buck converter prototype.

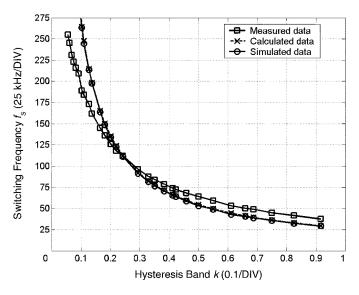

Fig. 10. Calculated, simulated, and experimentally measured average switching frequencies  $f_{\rm S}$  at nominal operating condition  $V_{\rm i} = 24$  V and  $R_{\rm L} = 6 \Omega$  for different hysteresis band  $\kappa$  settings.

## **IV. EXPERIMENTAL RESULTS**

This section evaluates the performance of the SMVC buck converter that is designed using the procedure described in Section III. The full schematic diagram of the experimental prototype is shown in Fig. 9.

# A. Verification of Design Equation

Fig. 10 shows the graphs of the converter's average switching frequency  $\overline{f_S}$  for different  $\kappa$  values at nominal operating condition  $V_i = 24$  V and  $R_L = 6 \Omega$ , that are obtained from calculation, simulation, and experiment. Specifically, the calculation is performed using the proposed design (26) and the simulation is carried out in Matlab/Simulink using the circuit expression of the proposed controller. Basically, the simulation and experimental data are in good agreement with the calculated data. The small discrepancy between the experimental data and both the calculated and simulated data is mainly due to component tolerances and finite time delay of practical circuitries. In practical development, fine tuning of  $\kappa$  is still required to achieve the desired  $\overline{f_S}$ .

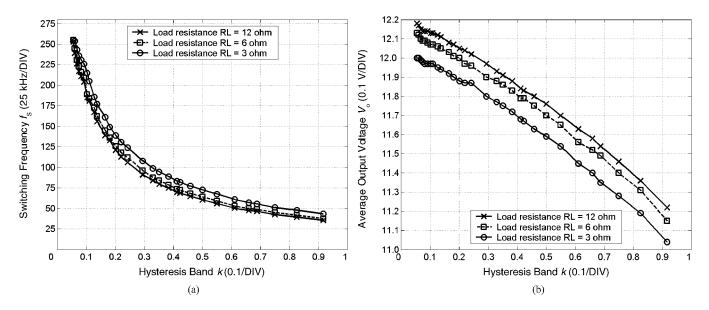

Fig. 11 shows the graphs of the measured average switching frequency  $\overline{f_S}$  and average output voltage  $\overline{V_o}$  against  $\kappa$  for load resistances  $R_L = 3$ , 6, and 12  $\Omega$ . From the figure,  $\overline{f_S}$  is notably higher with lower  $R_L$ , and  $\overline{V_o}$  is lower with lower  $R_L$ . Additionally, a major point to highlight is that at low  $\kappa$ , i.e., high switching frequency, the voltage regulation is tighter and more accurate. In our design, by setting  $0.1 \le \kappa \le 0.2$  in the design, we limit the voltage accuracy within  $\pm 0.12$  V (i.e., < 1 % of  $V_{\rm od}$ ) error.

## B. Steady-State Performance

Our experiment hereafter uses a controller that is fine-tuned to a switching frequency of 200 kHz by replacing  $R_{\rm ST2}$  with a 16 k $\Omega$  resistor, thereby setting  $\kappa = 0.1$ .

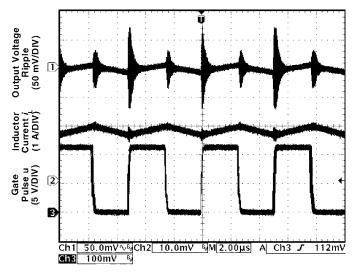

Fig. 12 shows an example of the output voltage ripple, inductor current, and switching state waveforms of the SMVC buck converter at steady-state operation. Performing to design expectation, the converter operates at an average switching frequency of  $\overline{f_{\rm S}} = 199$  kHz, with small frequency fluctuations, and the output voltage ripple  $\widetilde{V_{\rm o}}$  (without considering the ringing oscillation) is around 10 mV (i.e., < 0.1 % of  $V_{\rm od}$ ), under the nominal operating condition  $V_{\rm i} = 24$  V and  $R_{\rm L} = 6 \Omega$ .

# C. Load Variation

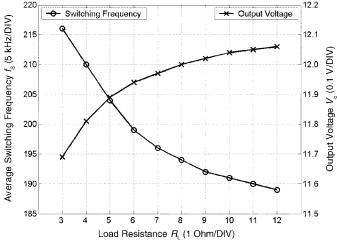

Fig. 13 gives the experimentally measured  $\overline{f_{\rm S}}$  and  $\overline{V_{\rm o}}$  for load resistance  $3 \,\Omega \leq R_{\rm L} \leq 12 \,\Omega$ . It can be concluded that voltage regulation of the converter is robust to load variation, with only a 0.37 V deviation (i.e., 3.1% of  $V_{\rm o(nominal\ load)}$ ) in  $\overline{V_{\rm o}}$  for the entire load range, i.e., load regulation  $d\overline{V_{\rm o}}/dR_{\rm L}$  averages at 0.04 V/ $\Omega$ . Additionally, the experimental readings also indicate that there is a change of switching frequency when the load vary. From the figure, the variation of switching frequency with respect to load resistance  $d\overline{f_{\rm S}}/dR_{\rm L}$  averages at  $-3.0 \,\mathrm{kHz}/\Omega$ . Theoretically, the nonlinear expression of  $df_{\rm S}/dR_{\rm L}$  can be obtained by differentiating (23) with respect to  $R_{\rm L}$ , i.e.,

$$\frac{df_{\rm S}}{dR_{\rm L}} = \frac{Lx_2^2}{\beta^2 \kappa V_{\rm i}} \left( \frac{1}{R_{\rm L}^3} - \frac{C\alpha}{R_{\rm L}^2} \right) + \frac{0.5 - \frac{V_{\rm o}}{V_{\rm i}}}{\beta \kappa R_{\rm L}^2} x_2.$$

(33)

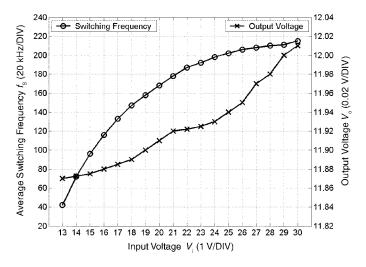

#### D. Line Variation

The experimentally measured  $\overline{f_{\rm S}}$  and  $\overline{V_{\rm o}}$  for input voltage range 13 V  $\leq V_{\rm i} \leq$  30 V are plotted in Fig. 14. It can be observed that both  $\overline{V_{\rm o}}$  and  $\overline{f_{\rm S}}$  increase with increasing  $V_{\rm i}$ . Specifically, output voltage deviation is 0.14 V (i.e., 1.2% of  $V_{\rm o(nominal\ input)}$ ) for the entire input range, i.e., line regulation  $d\overline{V_{\rm o}}/dV_{\rm i}$  averages at 8.235 mV/V. The variation of switching frequency with respect to input voltage  $d\overline{f_{\rm S}}/dV_{\rm i}$  averages at 10.176 kHz/V. Theoretically, the nonlinear expression of  $df_{\rm S}/dV_{\rm i}$  can be obtained by differentiating (24) with respect to  $V_{\rm i}$ , i.e.,

$$\frac{df_{\rm S}}{dV_{\rm i}} = \frac{V_{\rm o}^2}{2\kappa L V_{\rm i}^2}.\tag{34}$$

Fig. 11. (a) Experimentally measured average switching frequency  $\overline{f_s}$  and (b) average output voltage  $\overline{V_o}$  at  $V_i = 24$  V and  $R_L = 3$ , 6, and 12  $\Omega$  for different hysteresis band  $\kappa$  settings.

Fig. 12. Waveforms of  $V_0$ ,  $i_L$ , and u at steady-state operation under nominal operating conditions  $V_i = 24$  V and  $R_L = 6 \Omega$ .

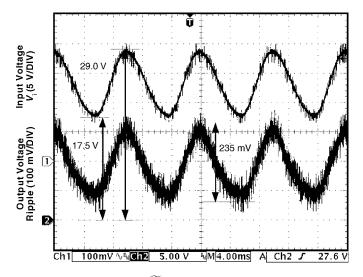

Fig. 15 shows the output voltage ripple waveform of the converter operating at nominal load when  $V_i$  is sinusoidally varied from 17.5 V to 29.0 V at a frequency of 100 Hz. This was performed to test the robustness of the converter to a slowly varying input voltage. It is found that the maximum peak to peak output voltage is around 235 mV, i.e., the input voltage ripple rejection is -33.8 dB at 100 Hz. The converter has displayed adequate control performance against audio susceptibility.

### E. $\alpha$ Variation

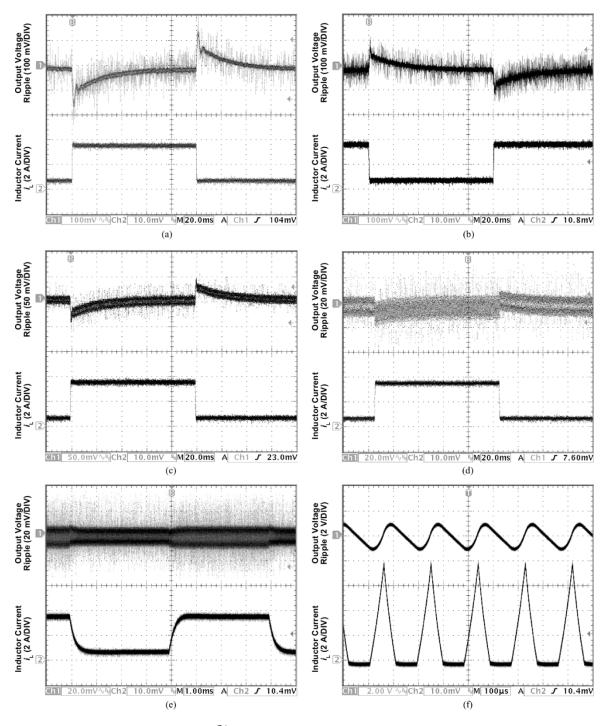

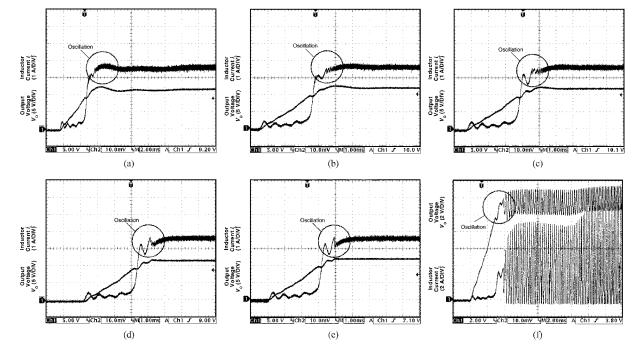

The dynamic behavior of the converter corresponding to different sliding coefficients  $\alpha$  is also investigated. Fig. 16(a)–(f) show the output waveforms of the operation with load resistance that alternates between  $R_{\rm L} = 12 \ \Omega$  and  $R_{\rm L} = 3 \ \Omega$ for the controller with sliding coefficients: (a)  $\alpha = 0.5/R_{\rm L}C$ , (b)  $\alpha = 1/R_{\rm L}C$ , (c)  $\alpha = 2/R_{\rm L}C$ , (d)  $\alpha = 10/R_{\rm L}C$ , (e)

Fig. 13. Experimentally measured values of average switching frequency  $\overline{f_{\rm S}}$  and average output voltage  $\overline{V_{\rm O}}$  for different load resistance  $R_{\rm L}$ .

$\alpha = 100/R_{\rm L}C$ , and (f)  $\alpha = 500/R_{\rm L}C$ , respectively. The results are summarized in Table II.

Noticeably, as  $\alpha$  increases, the dynamic response of the converter improves with shorter settling time and lower overshoots. This is in good agreement with our theory that dynamic response improves with increasing  $\alpha$ . However, when  $\alpha$  is too high, the converter is unstable [see Fig. 16(f)]. This is due to the distortion of the control signal caused by the saturation of amplified feedback signal [refer to the discussion related to (12)].

Fig. 17(a)–(f) show the output waveforms of the startup operation for the controller with the same set of sliding coefficients. The purpose is to examine the oscillatory behavior of the response due to  $\alpha$ , which exercises direct influence on the existence region in the control. Consistent with theory, the degree of oscillation increases with the increasing  $\alpha$ . Since the magnitude of the oscillations will be high for heavy loads, the effect of oscillation due to  $\alpha$  should be taken into consideration when designing high power converters.

Fig. 14. Experimentally measured values of average switching frequency  $\overline{f_{\rm S}}$  and average output voltage  $\overline{V_{\rm o}}$  for different input voltage  $V_{\rm i}$ .

Fig. 15. Waveforms of  $V_i$  and  $\widetilde{V_o}$  under the operating condition whereby  $V_i$  is sinusoidally varied from 17.5 V to 29 V at a frequency of 100 Hz, and  $R_{\rm L} = 6 \ \Omega$ .

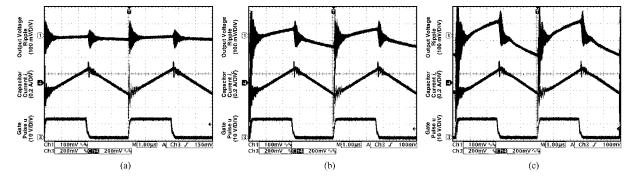

#### F. ESR Variation

The converter is also subjected to an ESR variation test. The idea is to investigate the effect of the output capacitor's ESR on the switching behavior of the converter. Fig. 18(a)–(c) illustrates the experimental waveforms of the converter with the same output capacitance, for different ESR values ( $25 \text{ m}\Omega$ ,  $125 \text{ m}\Omega$ , and  $225 \text{ m}\Omega$ ), operating under nominal load conditions  $V_i = 24 \text{ V}$  and  $R_L = 6 \Omega$ . As expected, output voltage ripples are higher with larger values of ESR. However, the variation of ESR does not influence the behavior of capacitor current. In all cases, the peak-to-peak capacitor current remains at 0.36 A, while the average switching frequency is at around 200 kHz. Hence, it is evident that output capacitor's ESR has little influence on the switching frequency.

### V. FURTHER DISCUSSION

This section discusses the merits and drawbacks of the proposed standard SMVC converter as compared to conventional current mode and voltage mode converters. Suggestions to alleviate the various drawbacks are also provided.

#### A. Advantages

The main advantage of the SMVC converter is the simplicity in the controller's design and implementation. Unlike conventional current mode and voltage mode controllers which require special techniques (e.g., pole placement method) to estimate their controllers' gain parameters, the SM voltage controller's parameters can be precisely calculated from simple mathematical equations.

Furthermore, since the SMVC controller is designed from the large-signal converter model, it is stable and robust to large parameter, line, and load variations. This is also a major advantage over conventional current mode and voltage mode controllers which often fail to perform satisfactorily under parameter or large load variations because they are designed from the linearized small-signal converter models [21].

#### B. Disadvantages

One major disadvantage of the proposed SMVC converter is that it has a nonzero steady-state voltage error. This is due to the adoption of the phase canonical form in the design, which makes the controller a proportional-derivative (PD) type of feedback controller [21], and the presence of hysteresis band in the switching function, which being nonzero in its average value also introduces an error in the output voltage [5].

Another disadvantage of the proposed converter is that its steady-state switching frequency is affected by the line and load variations (refer to Figs. 13 and 14). For line variation, this can be understood from (26) where with preset design parameters L,  $\kappa$ , and  $\overline{V_{o}}$ , a deviation in the input supply,  $\overline{V_{i}}$ , will result in a change in the steady-state dc switching frequency,  $\overline{f_{\rm S}}$ . Specifically,  $\overline{f_{\rm S}}$  increases as  $\overline{V_{\rm i}}$  increases. For load variation, the change in switching frequency is caused by two components. First, it is due to the imperfect feedback loop that causes a small steady-state error in the output voltage which in turn causes small deviation of the switching frequency from its nominal value [see (26)]. Second, it is due to the mismatch between the nominal load and operating the load. This can be understood from (23) where with preset control parameter  $\alpha =$  $1/R_{L(nom)}C$  for a certain nominal load  $R_{L(nom)}$ , a change in operating load  $R_{\rm L}$  from its nominal value will lead to a frequency not given by (24).

## C. Possible Solutions

The steady-state voltage error can easily be eliminated by converting the controller into a PID-type through the introduction of an integrator to process the voltage error signal [5], [15]. Such controllers are well-known and will not be discussed in this paper.

One possible method of maintaining the switching frequency against line variation is by introducing an adaptive feed-forward hysteresis band control that varies the hysteresis band  $\kappa$  with the change of  $V_i$ . Practically, this can easily be performed

Fig. 16. Experimental waveforms of output voltage ripple  $\hat{V}_{\alpha}$  and inductor current  $i_{L}$  under step load change that alternates between  $R_{L} = 12 \Omega$  and  $R_{L} = 3 \Omega$  for controller with sliding coefficients (a)  $\alpha = 0.5/R_{L}C$ , (b)  $\alpha = 1/R_{L}C$ , (c)  $\alpha = 2/R_{L}C$ , (d)  $\alpha = 10/R_{L}C$ , (e)  $\alpha = 100/R_{L}C$ , and (f)  $\alpha = 500/R_{L}C$ .

by imposing a variable power supply,  $V_{\rm CC}^+$  and  $V_{\rm CC}^-$ , which changes with  $V_{\rm i}$  variation, to power the Schmitt Trigger circuit [see (40)].

An adaptive feedback controller that varies the parameter,  $\alpha$ , with the change of load  $R_{\rm L}$ , can be incorporated to maintain the switching frequency of the converter against load variation. The idea is to adaptively maintain the operating status at  $\alpha = 1/R_{\rm L}C$  for all load conditions. Such system has been proposed in [22] to improve system's performances. Here, it is suggested as a means to also maintain the validity of (24) so

that  $f_{\rm S}$  becomes independent of  $R_{\rm L}$ . Hence, the effect of frequency variation caused by the mismatch between the nominal and the operating load is eliminated. Additionally, with better regulated steady-state output voltage with the adaptive feedback control scheme [22], the issue of switching frequency deviation due to the variation of the output voltage is also alleviated.

Details of the design and derivation of such adaptive feedforward and feedback control schemes will be addressed in the subsequent paper.

| TABLE II                                                                                           |          |

|----------------------------------------------------------------------------------------------------|----------|

| Dynamic Behavior of the Experimental SMVC Converter for Different $\alpha$ Settings Under Step Lo. | D CHANGE |

| Sliding Coefficient Setting                                                                                    | Maximum Overshoot/Undershoot Voltage Ripple   | Steady-State Settling Time |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------|

| $\alpha = \frac{0.5}{R_{\rm L}C} \Rightarrow R_{\rm V1} = 33 \text{ k}\Omega; R_{\rm V2} = 10 \text{ k}\Omega$ | $\pm 150$ mV (±1.25 % of $V_{\rm od})$        | 80 ms                      |

| $lpha = rac{1}{R_{ m L}C} \Rightarrow R_{ m V1} = 33 \;  m k\Omega; \; R_{ m V2} = 20 \;  m k\Omega$          | $\pm 100$ mV ( $\pm 0.83~\%$ of $V_{\rm od})$ | 60 ms                      |

| $\alpha = \frac{2}{R_{\rm L}C} \Rightarrow R_{\rm V1} = 33 \text{ k}\Omega; R_{\rm V2} = 40 \text{ k}\Omega$   | $\pm 50$ mV ( $\pm 0.41$ % of $V_{ m od}$ )   | 40 ms                      |

| $\alpha = \frac{10}{R_{\rm L}C} \Rightarrow R_{\rm V1} = 33 \text{ k}\Omega; R_{\rm V2} = 200 \text{ k}\Omega$ | $\pm 20$ mV ( $\pm 0.17~\%$ of $V_{ m od}$ )  | 20 ms                      |

| $\alpha = \frac{100}{R_{\rm L}C} \Rightarrow R_{\rm V1} = 33 \text{ k}\Omega; R_{\rm V2} = 2 \text{ M}\Omega$  | $\pm 1$ mV ( $\pm 0.08$ % of $V_{ m od}$ )    | 1 ms                       |

| $\alpha = \frac{500}{R_{\rm L}C} \Rightarrow R_{\rm V1} = 33 \text{ k}\Omega; R_{\rm V2} = 10 \text{ M}\Omega$ | $\pm 1$ V ( $\pm 8.33$ % of $V_{ m od}$ )     | Instable                   |

Fig. 17. Experimental waveforms of output voltage  $V_{\alpha}$  and inductor current  $i_{\rm L}$  under nominal operating conditions  $V_{\rm i} = 24$  V and  $R_{\rm L} = 3 \Omega$  for controller with sliding coefficient (a)  $\alpha = 0.5/R_{\rm L}C$ , (b)  $\alpha = 1/R_{\rm L}C$ , (c)  $\alpha = 2/R_{\rm L}C$ , (d)  $\alpha = 10/R_{\rm L}C$ , (e)  $\alpha = 100/R_{\rm L}C$ , and (f)  $\alpha = 500/R_{\rm L}C$  during startup.

Fig. 18. Experimental waveforms of output voltage ripple  $\widetilde{V_{\alpha}}$ , capacitor current  $i_C$ , and the generated gate pulse u for SMVC converter with 100  $\mu$ F filter capacitor of (a) ESR = 25 m  $\Omega$ ; (b) ESR = 125 m  $\Omega$ ; and (c) ESR = 225 m  $\Omega$ , at constant load resistance  $R_{\rm L} = 6 \Omega$ .

## VI. CONCLUSION

A detailed analysis of the design principle of a SMVC buck converter is presented. The discussion takes into consideration the practical aspects of the converter. The sliding line for an ideal controller is redefined to meet practical limitations. A hysteresis band is introduced to the sliding line to the solve the problem of chattering. The relationship between the hysteresis band and the switching frequency is derived. To facilitate implementation, a standard SM converter module is introduced. Design guidelines are provided in a simple step by step manner. The experimental results are presented to verify the converter design and procedure.

## APPENDIX I DERIVATION OF SMALL-SIGNAL MODEL OF SWITCHING FREOUENCY RELATIONSHIP WITH HYSTERESIS BAND

The variables  $V_i$ ,  $V_o$ , and  $f_S$  from (24) are first separated into their steady-state and small-signal terms

$$V_{i} = \overline{V_{i}} + \widetilde{V_{i}}$$

$$V_{o} = \overline{V_{o}} + \widetilde{V_{o}}$$

$$f_{S} = \overline{f_{S}} + \widetilde{f_{S}}.$$

(35)

Substituting (35) into (24), we have

$$f = \frac{(\overline{V_{o}} + \widetilde{V_{o}})\left(1 - \frac{\overline{V_{o}} + \widetilde{V_{o}}}{\overline{V_{i}} + \widetilde{V_{i}}}\right)}{2\kappa L}$$

$$= \frac{\overline{V_{o}} + \widetilde{V_{o}} - \frac{\overline{V_{o}}^{2} + 2\overline{V_{o}}\widetilde{V_{o}} + \widetilde{V_{o}}^{2}}{\overline{V_{i}} + \widetilde{V_{i}}}}{2\kappa L}.$$

(36)

Since the output voltage ripple is very small, i.e.,  $V_0$  is very small, the cross term of  $V_0$  can be neglected. Hence (36) becomes

$$f = \frac{\overline{V_{o}} + \widetilde{V_{o}} - \frac{\overline{V_{o}}^{2} + 2\overline{V_{o}}\widetilde{V_{o}}}{\overline{V_{i}} + \widetilde{V_{i}}}}{2\kappa L}.$$

(37)

From (37), the steady-state equation and the small-signal equation can be obtained as given in (26) and (27).

### APPENDIX II

# DERIVATION OF VARIABLE POWER SUPPLY DESCRIPTION FOR SCHMITT TRIGGER IN FEEDFORWARD HYSTERESIS BAND CONTROL

The description of a noninverting Schmitt Trigger is expressed as

$$2\kappa = \frac{R_{\rm ST1}}{R_{\rm ST2}} (V_{\rm CC}^+ - V_{\rm CC}^-).$$

(38)

Substituting this into (31), we have

$$V_{\rm CC}^{+} - V_{\rm CC}^{-} = \frac{R_{\rm ST2}}{R_{\rm ST1}} \frac{V_{\rm od}}{f_{\rm Sd}L} \left[ 1 - \frac{V_{\rm od}}{V_{\rm i}} \right].$$

(39)

Considering that both  $V_{\rm CC}^+$  and  $V_{\rm CC}^-$  must be balanced when powering the Schmitt Trigger, the power supply description should be

$$V_{\rm CC}^{+} = \frac{1}{2} \frac{R_{\rm ST2}}{R_{\rm ST1}} \frac{V_{\rm od}}{f_{\rm Sd}L} \left[ 1 - \frac{V_{\rm od}}{V_{\rm i}} \right]$$

$$V_{\rm CC}^{-} = -\frac{1}{2} \frac{R_{\rm ST2}}{R_{\rm ST1}} \frac{V_{\rm od}}{f_{\rm Sd}L} \left[ 1 - \frac{V_{\rm od}}{V_{\rm i}} \right].$$

(40)

#### REFERENCES

- V. Utkin, J. Guldner, and J. X. Shi, *Sliding Mode Control in Electro*mechanical Systems. London, U.K.: Taylor and Francis, 1999.

- [2] V. Utkin, Sliding Modes in Control Optimization. Berlin, Germany: Springer-Verlag, 1992.

- [3] C. Edwards and S. K. Spurgeron, Sliding Mode Control: Theory and Applications. London, U.K.: Taylor and Francis, 1998.

- [4] W. Perruquetti and J. P. Barbot, *Sliding Mode Control in Engineering*. New York: Marcel Dekker, 2002.

- [5] G. Spiazzi and P. Mattavelli, "Sliding-mode control of switched-mode power supplies," in *The Power Electronics Handbook*. Boca Raton, FL: CRC Press LLC, 2002, ch. 8.

- [6] R. Venkataramanan, A. Sabanoivc, and S. Cuk, "Sliding mode control of dc-to-dc converters," in *Proc. IEEE Conf. Industrial Electronics, Control Instrumentations (IECON)*, 1985, pp. 251–258.

- [7] V. M. Nguyen and C. Q. Lee, "Indirect implementations of sliding-mode control law in buck-type converters," in *Proc. IEEE Applied Power Electronics Conf. Expo (APEC)*, vol. 1, Mar. 1996, pp. 111–115.

- [8] —, "Tracking control of buck converter using sliding-mode with adaptive hysteresis," in *Proc. IEEE Power Electronics Specialists Conf.* (*PESC*), vol. 2, Jun. 1995, pp. 1086–1093.

- [9] S. K. Mazumder, A. H. Nayfeh, and A. Borojevic, "Robust control of parallel dc-dc buck converters by combining integral-variable-structure and multiple-sliding-surface control schemes," *IEEE Trans. Power Electron.*, vol. 17, no. 3, pp. 428–437, May 2002.

- [10] J. Mahdavi, A. Emadi, and H. A. Toliyat, "Application of state space averaging method to sliding mode control of pwm dc/dc converters," in *Proc. IEEE Conf. Industry Applications Society (IAS)*, vol. 2, Oct 1997, pp. 820–827.

- [11] L. Martinez-Salamero, J. Calvente, R. Giral, A. Poveda, and E. Fossas, "Analysis of a bidirectional coupled-inductor Cuk converter operating in sliding mode," *IEEE Trans. Circuits Syst. I*, vol. 45, no. 4, pp. 355–363, Apr. 1998.

- [12] H. Sira-Ramirez, "Sliding motions in bilinear switched networks," *IEEE Trans. Circuits Syst.*, vol. 34, no. 8, pp. 919–933, Aug. 1987.

- [13] H. Sira-Ramirez and M. Rios-Bolivar, "Sliding mode control of dc-to-dc power converters via extended linearization," *IEEE Trans. Circuits Syst. I*, vol. 41, no. 10, pp. 652–661, Oct 1994.

- [14] B. J. Cardoso, A. F. Moreira, B. R. Menezes, and P. C. Cortizo, "Analysis of switching frequency reduction methods applied to sliding mode controlled dc-dc converters," in *Proc. IEEE Applied Power Electronics Conf. Expo (APEC)*, Feb. 1992, pp. 403–410.

- [15] P. Mattavelli, L. Rossetto, G. Spiazzi, and P. Tenti, "General-purpose sliding-mode controller for dc/dc converter applications," in *Proc. IEEE Power Electronics Specialists Conf. (PESC)*, Jun. 1993, pp. 609–615.

- [16] D. M. Mitchell, DC-DC Switching Regulator Analysis. New York: Mc-Graw-Hill, 1998.

- [17] J. J. E. Slotine and W. Li, "Sliding control," in *Applied Nonlinear Control*. Englewood Cliffs, NJ: Prentice -Hall, 1991, ch. 7.

- [18] H. W. Whittington, B. W. Flynn, and D. E. Macpherson, Switched Mode Power Supplies : Design and Construction, 2nd ed. New York: Wiley, 1997.

- [19] E. Rogers, "Understanding buck power stages in switch mode power supplies," in *Mixed Signal Products*: Texas Instruments, 1999.

- [20] K. H. Billings, Switchmode Power Supply Handbook, 2nd ed. New York: McGraw-Hill, 1999.

- [21] V. S. C. Raviraj and P. C. Sen, "Comparative study of proportional-integral, sliding mode, and fuzzy logic controllers for power converters," *IEEE Trans. Ind. Applicat.*, vol. 33, no. 2, pp. 518–524, Mar./Apr. 1997.

- [22] S. C. Tan, Y. M. Lai, M. K. H. Cheung, and C. K. Tse, "An adaptive sliding mode controller for buck converter in continuous conduction mode," in *Proc. IEEE Applied Power Electronics Conf. Expo (APEC)*, Feb. 2004, pp. 1395–1400.

Siew-Chong Tan (S'00) received the B.Eng. (with honors) and M.Eng. degrees in electrical and computer engineering from the National University of Singapore, Singapore, in 2000 and 2002, respectively, and is currently pursuing the Ph.D. degree at Hong Kong Polytechnic University, Hong Kong.

His research interests include motor drives and power electronics.

**Y. M. Lai** (M'92) received the B.Eng. degree in electrical engineering from the University of Western Australia, Perth, Australia, in 1983, the M.Eng.Sc. degree in electrical engineering from University of Sydney, Sydney, Australia, in 1986, and the Ph.D. degree from Brunel University, London, U.K., in 1997.

He is an Assistant Professor with Hong Kong Polytechnic University, Hong Kong, and his research interests include computer-aided design of power electronics and nonlinear dynamics.

Martin K. H. Cheung received the B.Eng. (with honors) degree and the M.Phil. degree in electronic engineering from the Hong Kong Polytechnic University, Hong Kong, in 2000 and 2003, respectively.

He is currently a Project Assistant in the Department of Electronic and Information Engineering, Hong Kong Polytechnic University. His main research interests include RF circuit design and switch-mode power supplies design.

Chi K. Tse (M'90–SM'97) received the B.Eng. (with first class honors) degree in electrical engineering and the Ph.D. degree from the University of Melbourne, Australia, in 1987 and 1991, respectively.

He is presently a Professor with Hong Kong Polytechnic University, Hong Kong, and his research interests include nonlinear systems and power electronics. He is the author of *Linear Circuit Analysis* (London, U.K.: Addison-Wesley 1998) and *Complex Behavior of Switching Power Converters* (Boca Raton: CRC Press 2003), coauthor of *Chaos-Based*

*Digital Communication Systems* (Heidelberg, Germany: Springer-Verlag, 2003), and co-holder of a U.S. patent. He is an Associate Editor for the *International Journal of Systems Science*. Since 2002, he has been appointed as Guest Professor by the Southwest China Normal University, Chongqing, China.

Dr. Tse received the L.R. East Prize from the Institution of Engineers, Australia, in 1987, the IEEE TRANSACTIONS ON POWER ELECTRONICS Prize Paper Award in 2001, the President's Award for Achievement in Research (twice), and the Faculty's Best Researcher Award. He was an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS PART I—FUNDAMENTAL THEORY AND APPLICATIONS, from 1999 to 2001, and since 1999, he has been an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS.