# On the road towards robust and ultra low energy CMOS digital circuits using sub/near threshold power supply

Citation for published version (APA):

Pu, Y. (2009). On the road towards robust and ultra low energy CMOS digital circuits using sub/near threshold power supply. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR652086

DOI:

10.6100/IR652086

Document status and date:

Published: 01/01/2009

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 24. Aug. 2022

# On the Road towards Robust and Ultra Low Energy CMOS Digital Circuits Using Sub/Near Threshold Power Supply

# **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 23 september 2009 om 10.00 uur

door

Yu Pu

geboren te Chengdu, China

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. J. Pineda de Gyvez en prof.dr. H. Corporaal

Copromotor:

prof.dr. Y. Ha

On the Road towards Robust and Ultra Low Energy CMOS Digital Circuits Using Sub/Near Threshold Power Supply

/ by Yu Pu. - Eindhoven: Eindhoven University of Technology, 2009.

A catalogue record is available from the Eindhoven University of Technology Library ISBN 978-90-386-1976-7

**NUR 959**

Trefw.: digitale CMOS schakelingen / voedingsspanning onder de drempelspanning / ultra lage energie / parallelle architectuur.

Subject headings: digital CMOS circuit / sub-threshold / ultra low energy / parallel architecture.

# On the Road towards Robust and Ultra Low Energy CMOS Digital Circuits Using Sub/Near Threshold Power Supply

## Committee:

prof.dr. J. Pineda de Gyvez (promotor, NXP Research Eindhoven)

prof.dr. H. Corporaal (promotor, TU Eindhoven)

prof.dr. Y. Ha (co-promotor, National University of Singapore)

prof.dr. R.H.J.M. Otten (TU Eindhoven)

prof.dr. Y. Lian (National University of Singapore)

prof.dr. P. Girard (LIRMM, France)

The work in this thesis is supported by NXP Research Eindhoven.

© NXP Semiconductors 2009. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Printing: Printservice Eindhoven University of Technology

# **Abstract**

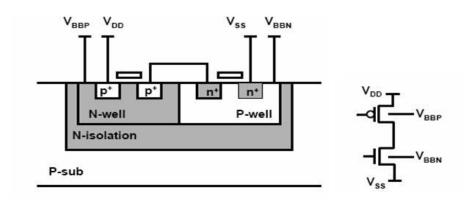

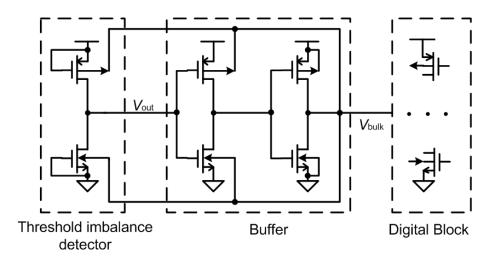

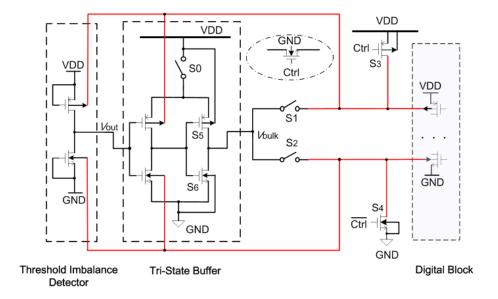

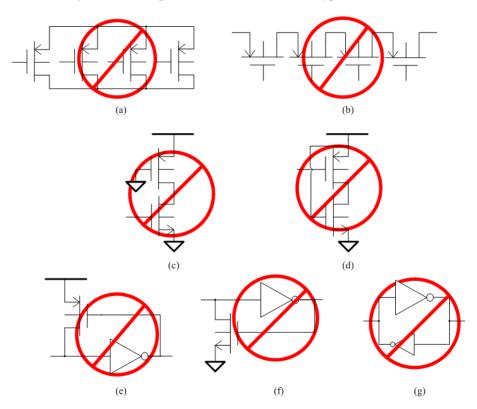

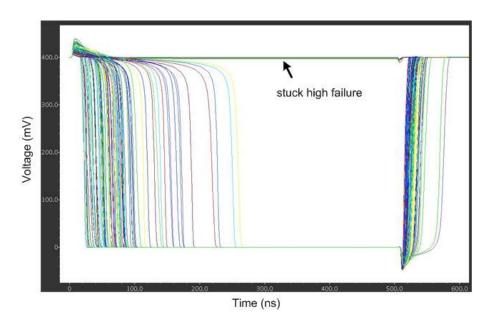

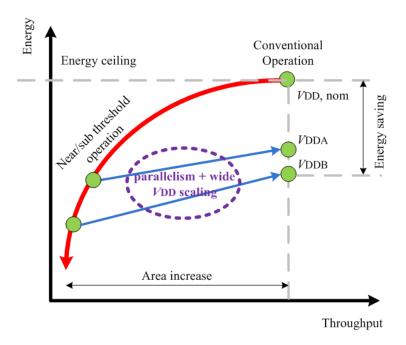

Voltage scaling is one of the most effective and straightforward means for CMOS digital circuit's energy reduction. Aggressive voltage scaling to the near or sub-threshold region helps achieving ultra-low energy consumption. However, it brings along big challenges to reach the required throughput and to have good tolerance of process variations. This thesis presents our research work in designing robust near/sub-threshold CMOS digital circuits. Our work has two features. First, unlike the other research work that uses subthreshold operation only for low-frequency low-throughput applications, we use architectural-level parallelism to compensate throughput degradation, so a medium throughput of up to 100MB/s suitable for digital consumer electronic applications can be achieved. Second, several new techniques are proposed to mitigate the yield degradation due to process variations. These techniques include: (a) Configurable  $V_T$  balancer to control the  $V_T$  spread. When facing process corners in the sub-threshold, our balancer will balance the  $V_T$ of p/nMOS transistors through bulk-biasing. (b) Transistor sizing to combat  $V_T$  mismatch between transistors. This is necessary if the circuit needs to be operated with very deep sub-threshold supply voltage, i.e., below 250mV for 65nm CMOS standard  $V_T$  process. (c) Improving sub-threshold drivability by exploiting the  $V_T$  mismatch between parallel transistors. While the  $V_T$ mismatch between parallel transistors is notorious, we proposed to utilize it to boost the driving current in the sub-threshold. This interesting approach also suggests using multiple-finger layout style, which helps reducing silicon area considerably. (d) Selection procedure of the standard cells and how they were modified for higher reliability in the sub-threshold regime. Standard library cells that are sensitive to process variations must be eliminated in the synthesis flow. We provided the basic guideline to select "safe" cells. (e) The method that turns risky ratioed logic such as latch and register into non-ratioed logic.

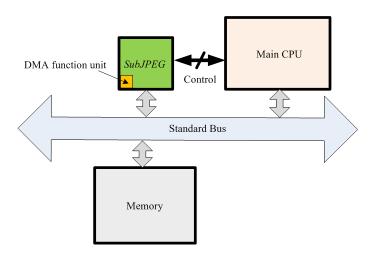

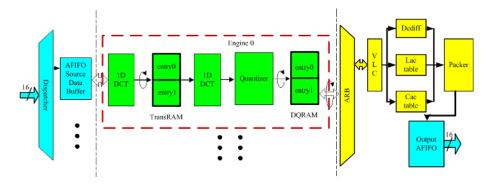

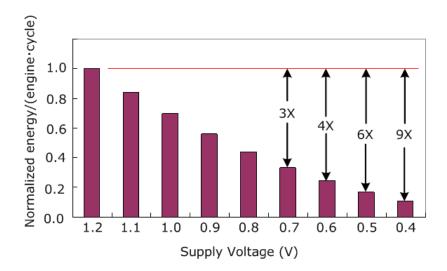

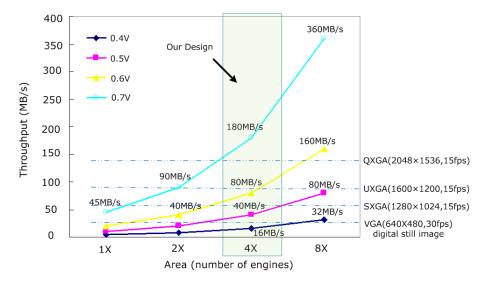

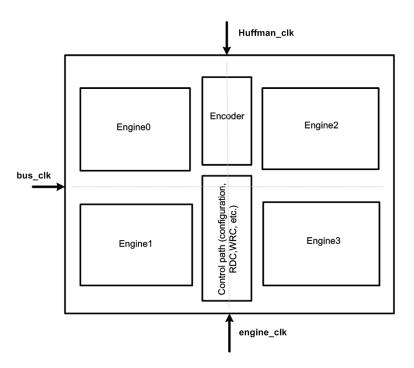

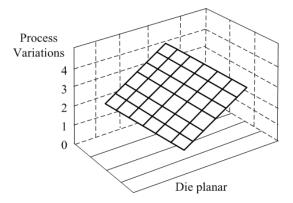

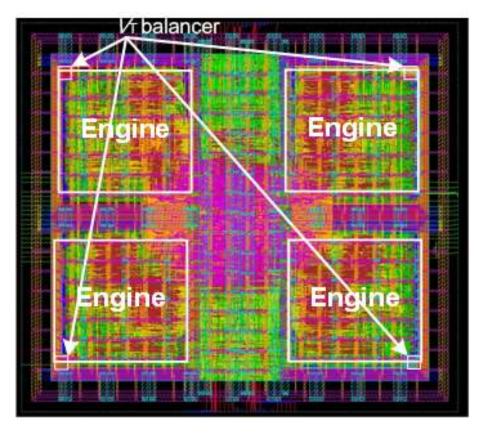

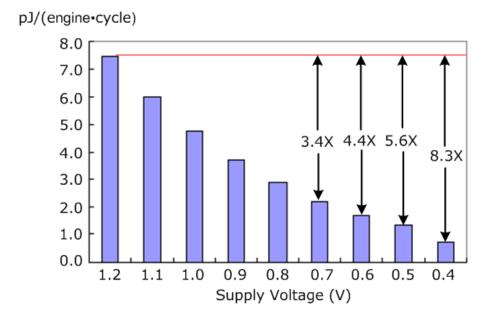

SubJPEG, an ultra low-energy multi-standard JPEG encoder co-processor with

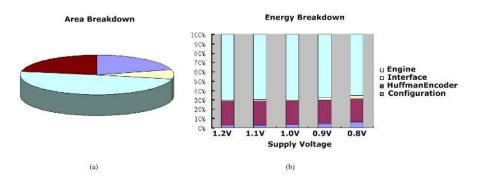

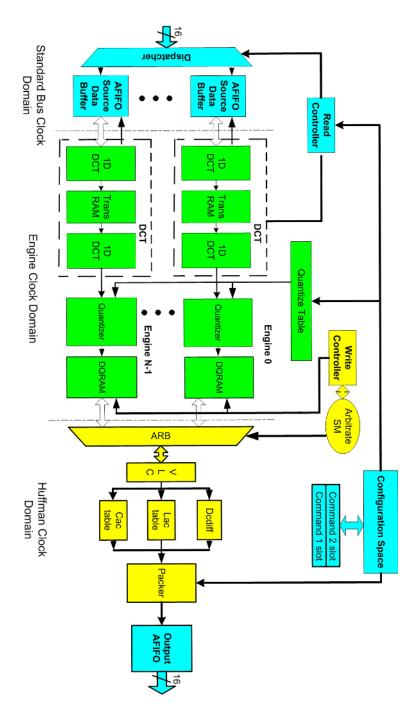

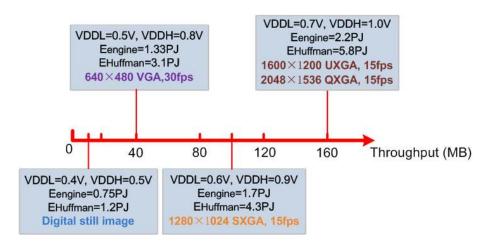

a sub/near threshold power supply has been designed and implemented to demonstrate all these ideas. This 8-bit resolution DMA based co-processor has multiple power domains and multiple clock domains. It uses 4 parallel DCT-Quantization engines in the data path. Instruction-level parallelism is also used. All the parallelism is implemented in an efficient manner to minimize the associated area overhead. Details about this co-processor architecture and implementation issues are covered in this thesis. The prototype chip is fabricated in TSMC 65nm 7-layer Low-Power Standard  $V_T$  CMOS process. The core area is  $1.4 \times 1.4$  mm<sup>2</sup>. Each engine has its own  $V_T$  balancer. Each  $V_T$  balancer is  $25 \times 30 \mu \text{m}^2$ . The measurement results show that our  $V_T$  balancer has very good balancing effect. In the sub-threshold mode the engines can operate with 2.5MHz clock frequency at 0.4V supply, with 0.75pJ energy per cycle per single engine for DCT and Quantization processing, i.e. 0.75pJ/(engine-cycle). This leads to 8.3× energy/(engine-cycle) reduction when compared to using a 1.2V nominal supply. In the near-threshold regime the energy dissipation is about 1.1pJ/(engine-cycle) with a 0.45V supply voltage at 4.5MHz. The system throughput can meet 15fps 640×480 pixel VGA compression standard. By further increasing the supply, the test chip can satisfy multi-standard image encoding. Our methodology is largely applicable to designing sound/graphic and other streaming processors.

# Acknowledgements

By this opportunity, I would like to express my gratitude and appreciation to everyone who has helped to make this thesis possible.

Sincere appreciation first goes to my supervisor prof.dr. José Pineda de Gyvez, for his guidance, support, encouragement during my PhD study. José is the most well-informed and hardworking IC specialist I have met. He has made an incredible huge effort in coaching me. His constructive criticisms have surely led to a much higher quality of this research work. I also thank him very much for giving me the valuable opportunity to work in NXP Research Eindhoven for over two years. I will never forget the attitude he taught me: working hard for glory.

I would like to thank prof.dr. Henk Corporaal, for many inspiring and in-depth discussions over these years. Henk opened my mind for problem formulation at the initial uncertain phase of my PhD time. His expertise in processor architecture is a key to the successful outcome of this research.

I would like to thank prof.dr. Ha Yajun, for bringing me into the joint PhD program and offering me the freedom to follow my ideas wherever they led. I also highly appreciate his careful reviewing my scientific papers and providing valuable feedback.

The other members in my doctorate committee, prof.dr. Ralph Otten, prof.dr. Lian Yong and prof.dr. Patrick Girard, are specially appreciated for reading the thesis, giving in-depth comments and participating in my PhD defense.

My PhD time in TU/e and NUS would not have been so amazing without the presence of many colleagues: Marja, Rian, Sander Stuijk, Akash Kumar, Hu Hao, He Yifan, Tang Yongjian, Yu Yikun, Deng Wei, Yu Jianghong, Yu Rui,

He Lin, Cen Ling, Hu Yingping, Tian Xiaohua, Wei Ying, Zou Xiaodan, Kine Lynn, Chen Xiaolei and Lee Cheesing. I wish them all the best.

I will never forget my friends in the "office of glory" in the Mixed-Signal Circuit and System Group of NXP Research Eindhoven: Maurice Meijer, Leo Sevat, Cas Groot, Agnese Bargagli-stoffi. I could not progress my project without their wise help and encouragement. I also thank Jan Stuyt and Jos Huisken for their kind and helpful support during my short staying in IMEC.

I am deeply indebted to my parents Pu Yicheng and Liu Guilan, my wife Sophie Lin Lei, for their constant love, support, and patience. I am really lucky to be a member of such a wonderful family.

Finally, I owe gratitude to all of the friends who are always there for me. The friendship will last forever in my heart. Particularly, I thank Andy Chen Hao for his generous help and encouragement when I was at the painful phase of designing the *SubJPEG* prototype chip.

# **Contents**

| 1 | Intr | ntroduction                                                                  |    |  |

|---|------|------------------------------------------------------------------------------|----|--|

|   | 1.1  | Voltage Scaling for Low-Power Digital Circuits                               | 1  |  |

|   | 1.2  | Practical Limitation of Voltage Scaling                                      | 4  |  |

|   | 1.3  | Related Sub-threshold Work                                                   | 6  |  |

|   | 1.4  | Contributions of This Work                                                   | 7  |  |

|   | 1.5  | Thesis Organization                                                          | 10 |  |

| 2 | Syst | em Level Analysis                                                            | 11 |  |

|   | 2.1  | Sub-threshold Modeling                                                       | 11 |  |

|   |      | 2.1.1 Sub-threshold Current Model                                            | 11 |  |

|   |      | 2.1.2 Sub-threshold Propagation Delay Model                                  | 16 |  |

|   |      | 2.1.3 Sub-threshold Energy Model                                             | 17 |  |

|   | 2.2  | Optimum Energy-per-Operation (EPO)                                           | 18 |  |

|   | 2.3  | Parallelism for Fixed Throughput                                             | 19 |  |

|   | 2.4  | Statistical Noise Margin Estimation for Sub-threshold Combinational Circuits | 22 |  |

|   |      | 2.4.1    | Estimating gate noise margin with rectified equivalent resistance model  | 23 |

|---|------|----------|--------------------------------------------------------------------------|----|

|   |      | 2.4.2    | Estimating statistical output noise margin with affine arithmetic model  | 29 |

|   |      | 2.4.3    | Experimental results                                                     | 31 |

| 3 | Phys | sical Le | vel Effort                                                               | 35 |

|   | 3.1  | Adapti   | ve $V_T$ for Process Spread Control in Sub/Near Threshold                | 35 |

|   | 3.2  | Gate S   | izing Considering $V_T$ Mismatch in Deep Sub-threshold                   | 43 |

|   | 3.3  | •        | Ving Drivability by Exploiting $V_T$ Mismatch between clized Transistors | 48 |

|   | 3.4  | Sub-th   | reshold Library Cell Selection                                           | 52 |

|   | 3.5  | Turnin   | g Ratioed Logic into Non-ratioed Logic                                   | 54 |

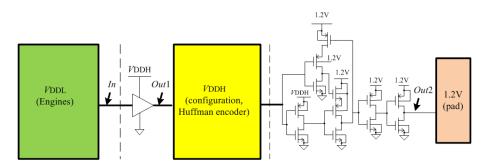

|   | 3.6  | Capaci   | tive-based Level Shifter (CBLC)                                          | 54 |

| 4 | Desi | gn of th | ne SubJPEG Co-processor                                                  | 59 |

|   | 4.1  | Design   | Flow Overview                                                            | 59 |

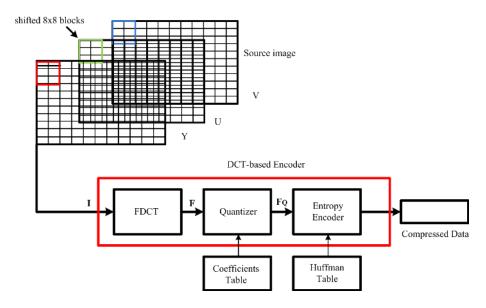

|   | 4.2  | JPEG 1   | Encoding Standard                                                        | 61 |

|   | 4.3  | SubJP    | EG Architecture                                                          | 65 |

|   |      | 4.3.1    | Design challenge                                                         | 65 |

|   |      | 4.3.2    | SubJPEG Macro-Architecture                                               | 66 |

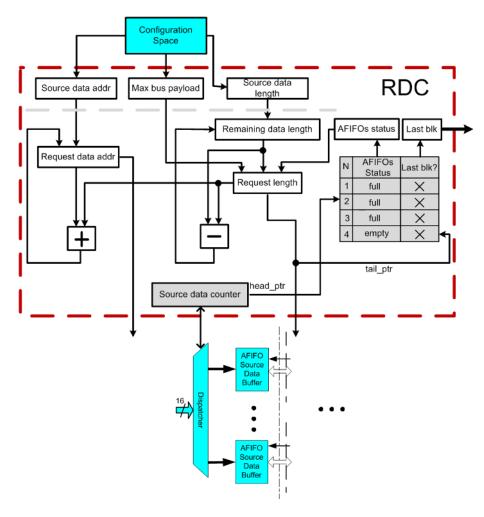

|   |      | 4.3.3    | Control Path Design                                                      | 68 |

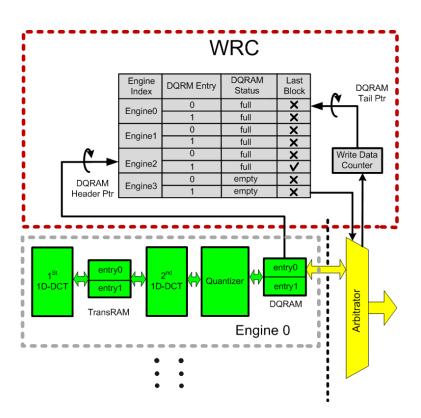

|   |      | 4.3.4    | Data Path Design                                                         | 76 |

|   | 4.4  | Implen   | nentation Issues                                                         | 79 |

|     |         | 4.4.1    | Logic Design                           | 79  |

|-----|---------|----------|----------------------------------------|-----|

|     |         | 4.4.2    | Physical Design                        | 81  |

|     | 4.5     | Fabrica  | ation and Packaging                    | 85  |

|     | 4.6     | Perform  | mance Evaluation                       | 85  |

| 5   | Cone    | clusions | , Future Work and Discussions          | 95  |

|     | 5.1     | Conclu   | sions                                  | 95  |

|     | 5.2     | Future   | Work                                   | 97  |

|     | 5.3     | Discus   | sions: Are we ready for sub-threshold? | 97  |

| Bib | oliogr  | aphy     |                                        | 101 |

| Glo | ossar   | y        |                                        | 109 |

| Sai | menv    | atting   |                                        | i   |

| Cu  | rricu   | lum Vit  | ae                                     | iii |

| Lis | st of F | Publicat | ions                                   | v   |

| Rea | ader'   | s Notes  |                                        | vii |

# **List of Figures**

| 1.1  | Applicable throughput range of this work and other work                                   | 9  |

|------|-------------------------------------------------------------------------------------------|----|

| 2.1  | Sources of leakage current                                                                | 12 |

| 2.2  | Calibrated transistor current model and SPICE simulation for 65nm S $V_T$ nMOS transistor | 15 |

| 2.3  | Illustration of the simulated transistor                                                  | 16 |

| 2.4  | Normalized driving current variability arising from different variation sources           | 17 |

| 2.5  | Dynamic/Leakage/Total energy per operation and the optimal $V_{DD}$ in $SV_T$ process     | 19 |

| 2.6  | Total EPO and the optimal $V_{DD}$ points for $SV_T$ and $HV_T$ process                   | 20 |

| 2.7  | Normalized EPO at different $\mathcal{V}_{DD}$ for the same throughput $\ \ .$            | 21 |

| 2.8  | (a) Cell schematic (b) Inverter (c) Equivalent model                                      | 24 |

| 2.9  | Noise margin generated from Spectre Simulator vs from Equation 2.23                       | 26 |

| 2.10 | Noise margin by definition and by this work                                               | 27 |

| 2.11 | $3\sigma$ range of noise margin generated from Spectre Simulator vs from Equation 2.23    | 28 |

| 2.12 | Noise margin uncertainty propagation with AA model                                        | 29 |

| 33<br>36<br>38 |

|----------------|

|                |

| 38             |

|                |

| 39             |

| 40             |

| 40             |

| 42             |

| 43             |

| 44             |

| 49             |

| 51             |

| 52             |

| 53             |

| 55             |

| 56             |

|                |

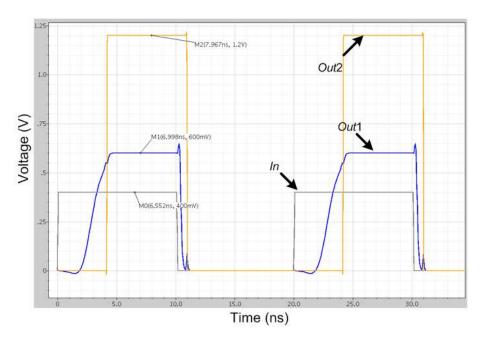

| 3.15 | Capacitive-based level converter (CBLC)                                       | 58  |

|------|-------------------------------------------------------------------------------|-----|

| 3.16 | Waveforms of the CBLC ( $V_{DDL}$ =400mV and $V_{DDH}$ =800mV)                | 58  |

| 4.1  | Sub-threshold design flow                                                     | 60  |

| 4.2  | JPEG encoder processing steps                                                 | 62  |

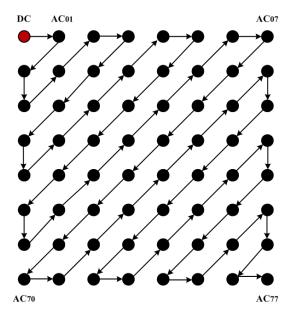

| 4.3  | AC zig-zag sequence                                                           | 64  |

| 4.4  | Design challenge                                                              | 66  |

| 4.5  | (a) Area (b) energy breakdown for conventional JPEG encoder                   | 67  |

| 4.6  | The functionality of <i>SubJPEG</i> in the system                             | 67  |

| 4.7  | SubJPEG processor diagram                                                     | 69  |

| 4.8  | Configuration space overview                                                  | 70  |

| 4.9  | Read controller diagram                                                       | 71  |

| 4.10 | Pseudo code algorithm for RDC                                                 | 73  |

| 4.11 | Write controller diagram                                                      | 74  |

| 4.12 | Pseudo code algorithm for WRC                                                 | 75  |

| 4.13 | Data path diagram                                                             | 77  |

| 4.14 | Normalized energy per cycle for each engine [energy/(engine·cycl 78           | e)] |

|      | Area vs. throughput for the engines and possible real-time image applications | 79  |

| 4.16 | 2-stage level-shifting scheme in <i>SubJPEG</i>                               | 80  |

| 4.17 | Simulation of the 2-stage level-shifting scheme (0.4V to 0.6V to 1.2V)        | 80  |

| 4.18 | SubJPEG floorplan                                                             | 81  |

|      |                                                                               |     |

| 4.19 | Gradient process variations                                                                   | 82 |

|------|-----------------------------------------------------------------------------------------------|----|

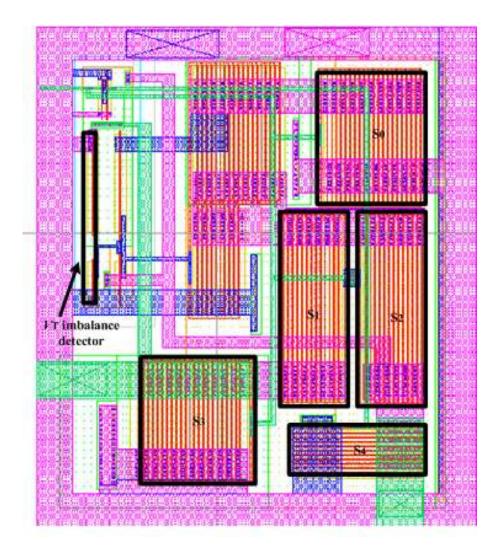

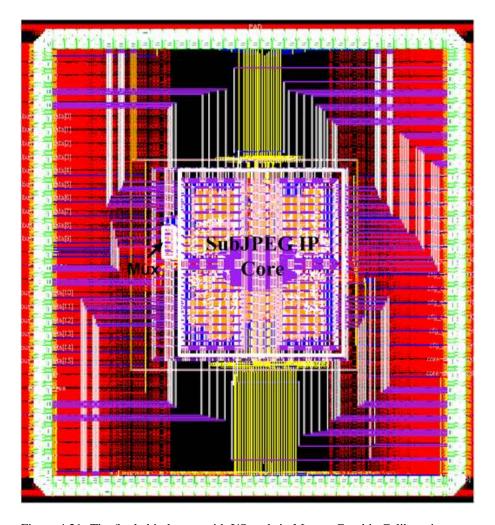

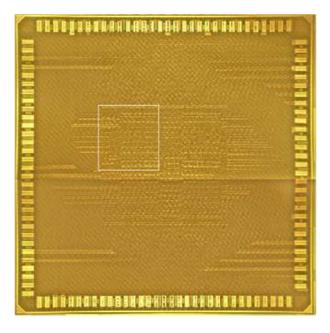

| 4.20 | The layout of $SubJPEG$ IP core integrated with the $V_T$ balancers in Cadence Encounter view | 83 |

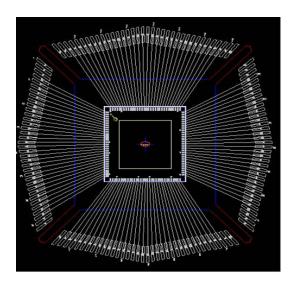

| 4.21 | The final chip layout with I/O pads in Mentor Graphic Calibre view                            | 84 |

| 4.22 | Prototype chip micrograph                                                                     | 85 |

| 4.23 | Pin-out bonding diagram                                                                       | 86 |

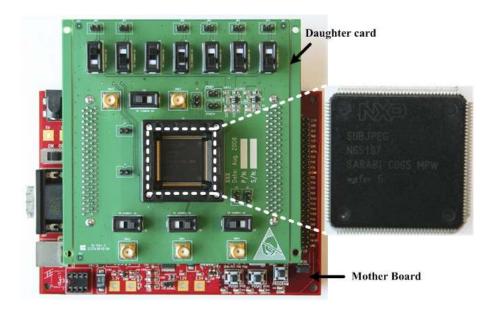

| 4.24 | Testing boards                                                                                | 86 |

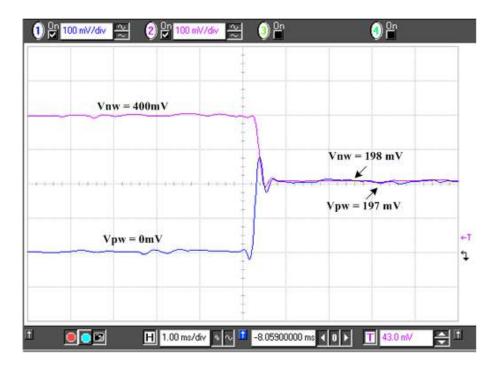

| 4.25 | Measurement results of switching on the $V_T$ balancer                                        | 87 |

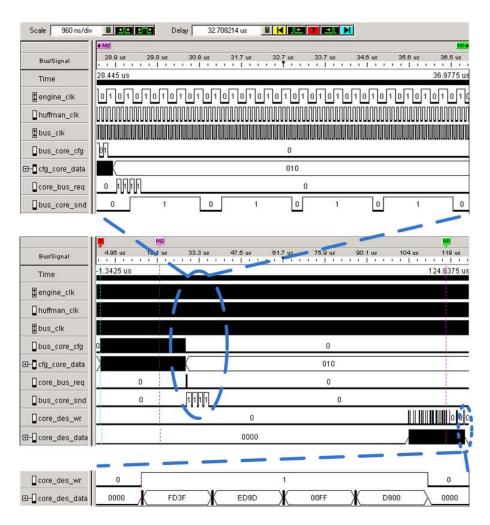

| 4.26 | Measurement results from logic analyzer: (a)(c) are zoomed in results of (b)                  | 88 |

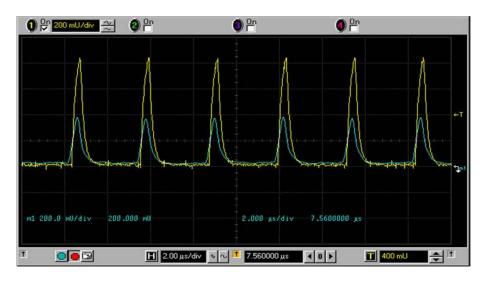

| 4.27 | Pulse trains from engines at $V_{DDL} = 400 \text{mV}$ and $V_{DDL} = 800 \text{mV}$          | 89 |

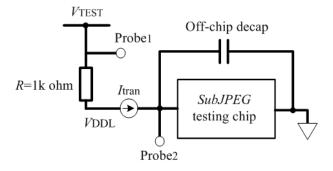

| 4.28 | Transient current measurement scheme                                                          | 89 |

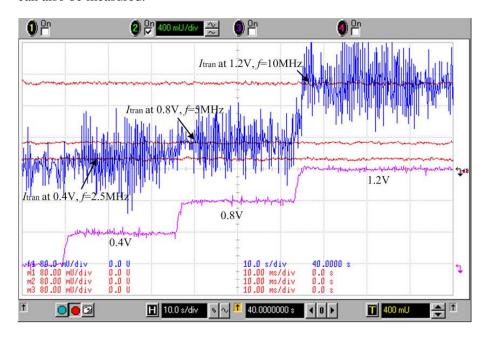

| 4.29 | Transient and average current at (0.4V, 2.5MHz), (0.8V, 5MHz) and (1.2V, 10MHz)               | 90 |

| 4.30 | Energy per cycle for each engine [pJ/(engine-cycle)]                                          | 91 |

| 4.31 | System energy and throughput                                                                  | 92 |

# **List of Tables**

| 1.1 | Summary of low-power digital techniques                                                                        | 3  |

|-----|----------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Biomedical and sensor applications                                                                             | 5  |

| 1.3 | Summary of existing sub-threshold work                                                                         | 8  |

| 2.1 | Parameters for 65nm CMOS S $V_T$ process                                                                       | 14 |

| 2.2 | Estimated statistical noise margin from Cadence Spectre Monte-Carlo DC simulation and the new approach         | 31 |

| 2.3 | Estimated statistical noise margins as $\%$ of $V_{DD}$                                                        | 32 |

| 3.1 | Minimum supply voltage for an inverter in 65nm CMOS                                                            | 42 |

| 3.2 | $\lg(I_{eff}/I_{idle})$ for a 2-input NAND                                                                     | 45 |

| 3.3 | Gate size normalized to minimum gate size vs. $V_{DD}$ (functional yield = 99.9% and 99.7%, 65nm CMOS process) | 46 |

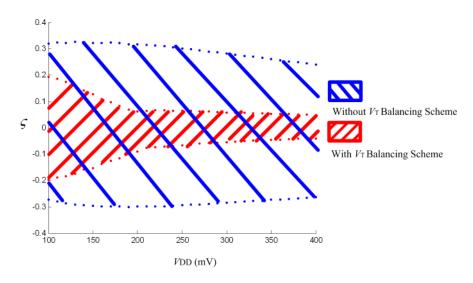

| 3.4 | Mean frequency, mean energy/cycle of ringo ( $L_d = 31$ , with and without $V_T$ balancing scheme)             | 48 |

| 3.5 | Mean and standard deviation of driving current                                                                 | 50 |

| 4.1 | Some DP-CP interactive signals in RDC                                                                          | 72 |

| 4.2 | Some DP-CP interactive signals in WRC                                                                          | 73 |

| 4.3 | Memory design choices                             | 77 |

|-----|---------------------------------------------------|----|

| 4.4 | Register files used in <i>SubJPEG</i> data path   | 77 |

| 4.5 | System throughput and possible image applications | 91 |

# **Chapter 1**

# Introduction

It is the time for the semiconductor industry to play a part in dealing with the global energy bottleneck and climate change that face our society. In this chapter, we will first overview the CMOS low-power digital design techniques. Then the practical limitation for aggressive voltage scaling is stated. Following that we will review the existing sub-threshold works. Finally, the contributions of this work and the organization of this thesis are presented.

# 1.1 Voltage Scaling for Low-Power Digital Circuits

As early as in the 1970s, Gordon Moore had observed that the number of transistors on a silicon die doubled every 18 months (Moore's law) [1]. It is reported that for the last two decades the CMOS technology has been conventionally scaled to provide 30% smaller gate delay with 30% smaller dimensions each year [2] [3], and an ever-increasing amount of Intellectual Property (IP) cores are integrated on a single System-on-Chip (SoC). The practice today is that, while the number of transistors integrated in a chip doubles approximately every two years, the capacity density of battery doubles only every ten years. As a result, the energy bottleneck becomes crucial to many consumer electronic applications. Taking an MP3 player as an example, consumers are strongly calling for new MP3 players with lower price but much longer playing time. In addition to the energy problem, the heat also becomes an issue. If the released heat from chips cannot be removed quickly, the whole sys-

tem performance becomes very instable. It is then inevitable to use special IC packaging and more advanced cooling techniques that support quick heat removal, which will increase product cost remarkably. Therefore, exploring the design methodology for low energy, "green" sub-micron circuits is of very great importance.

Targeting at broad and complex applications, SoCs normally integrate RF and analog modules such as transceivers, Phase (or Delay)-Locked-Loops (PLLs or DLLs), A/D-D/A converters, and digital modules such as multiple processors, memories, etc. The design trend has been to put more and more functionalities to digital modules for two reasons. First, modern Electronic Design Automation (EDA) tools support almost full automation of digital design flow. Integration of a large variety of processing functionalities into digital modules is much easier than into analog modules. Second, compared to analog signal processing, digital signal processing (DSP) is superior due to better noise immunity, smaller silicon area and less power consumption. Therefore, the digital modules are generally the dominant power consumer on a SoC.

The total power dissipation of a digital system is composed of the dynamic power, the leakage power and the short-circuit power. The dynamic power results from charging and discharging loading capacitances. It is often the dominant power consumer. The leakage power results from imperfect switch-off of nMOS/pMOS transistors. It is due to the current conducted even without any switching activity. Since millions of transistors are often integrated in a single SoC nowadays, the contribution of leakage power to the total power also becomes significant. The leakage current is sensitive to thermal conditions as its absolute value increases in an exponential fashion with the increasing temperature, so its significance can further increase if the released heat cannot be removed quickly. The short-circuit power dissipation is due to direct-path current when the nMOS and the pMOS transistors are conducting simultaneously during non-ideal rise/fall times. It only contributes a minor fraction (<5%) of the total power dissipation.

Table 1.1 summarizes many low-power digital circuit techniques [52] [53] . These techniques are categorized by their level in the design hierarchy. To achieve low power, it needs a wide collaboration of designers from each level hierarchy. In general, these techniques trade-off flexibility, performance and silicon area for power. Among these techniques, the most straightforward and effective means are to scale the supply voltage  $V_{DD}$  along with the operating frequency. As  $V_{DD}$  scales, not only does the dynamic power reduce quadrati-

Table 1.1: Summary of low-power digital techniques

| Design hierarchy               | Reported low-power digital techniques                                                                                   |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Algorithm level                | using more efficient DSP algorithms to eliminate un-<br>necessary computations and reduce the number of<br>computations |

|                                | 1. ISA extension, e.g., ASIP                                                                                            |

|                                | 2. scenario based mapping, rescheduling, etc.                                                                           |

| Mapping and architecture level | <ol> <li>preserving data correlation and reference locality, reducing memory access</li> </ol>                          |

| Mapping and areintecture level | 4. common expression elimination, pre-computation, etc.                                                                 |

|                                | 5. using suitable pipelining and parallelism, enabling low supply voltage/frequency                                     |

|                                | 1. multiple supply voltages (MSV)                                                                                       |

|                                | 2. dynamic voltage scaling (DVS)                                                                                        |

| 0 4 1 1                        | 3. dynamic voltage-frequency scaling (DVFS)                                                                             |

| System level                   | 4. multiple clock domains                                                                                               |

|                                | 5. dynamic/variable $V_T$ (adaptive body biasing)                                                                       |

|                                | 6. sleep and power down modes                                                                                           |

|                                | 1. power gating, clock gating                                                                                           |

|                                | 2. logic sizing and logic re-structuring                                                                                |

| Circuit level                  | 3. adiabatic logic circuits                                                                                             |

|                                | 4. low power SRAM, DRAM, etc.                                                                                           |

|                                | 5. power-efficient DC-DC converters                                                                                     |

|                                | multiple threshold CMOS (MTCMOS)                                                                                        |

| Device level                   | 2. low temperature CMOS (LTCMOS)                                                                                        |

| Device level                   | 3. Silicon-on-Insulator (SOI)                                                                                           |

|                                | 4. low power packaging                                                                                                  |

cally, the leakage current also reduces super-linearly due to the drain-induced barrier-lowering (DIBL) effect. In this way, the total power dissipation can be reduced considerably. In addition to power savings,  $V_{DD}$  scaling mitigates the transient current, hence lowering the notorious ground bounce noise (Ldi/dt). This also helps to improve the performance of sensitive analog circuits on the chip, such as the delay-lock loop (DLL), which is crucial for the correct functioning of complex digital circuits.

In the techniques listed in Table 1.1, multiple supply voltages (MSV), dynamic voltage scaling (DVS), and dynamic voltage-frequency scaling (DVFS) are three means of voltage scaling. MSV is a static approach, which provides different supply voltages to different power domains. DVS and DVFS are two adaptive approaches. Both of them exploit the variation in processor utilization: lowering the frequency and voltage when the processor is lightly loaded, and running at maximum frequency and voltage when the processor is heavily executing. They have been widely deployed for commercial microprocessors, achieving significant power savings [4,5,6,7,8].

# 1.2 Practical Limitation of Voltage Scaling

For applications requiring ultra-low energy dissipation, such as wireless "motes", sensor networks [10], in-vivo biomedicine (such as hearing aids, pace-makers, implantable device) [11] and wrist-watch computation [12], the techniques in Table 1.1 are not powerful enough. Table 1.2 lists some more biomedical and sensor applications that fall in this category. For each application, the associated sampling rates (in Hz) and the sample precision (in bits per sample) are also listed. Ideally, these applications should be self-powered, relying on scavenging energy from the environment, or at least be sustained by a small battery for tens of years. Such a stringent energy budget constrains the total system computation power to less than a hundred microwatts, which poses a great challenge to modern CMOS digital design.

Unlike analog circuit design where lowering the supply voltage to the subthreshold region is generally avoided because of the low values of the driving currents and the exceedingly large noise, CMOS digital logic gates can work seamlessly from full  $V_{DD}$  to well below the threshold voltage  $V_T$ . Theoretically, operating digital circuits in the near/sub-threshold region ( $V_{GS} < V_T$ ) can help obtaining huge energy savings. Therefore, sub-threshold techniques

Table 1.2: Biomedical and sensor applications

|                         |                     | G 1 (* 134.)               |

|-------------------------|---------------------|----------------------------|

| Application             | Sample rate (in Hz) | Sample precision (in bits) |

| Body temperature        | $0.1 \sim 1$        | 8                          |

| Heart rate              | $0.8 \sim 3.2$      | 1                          |

| Blood pressure          | $50 \sim 100$       | 8                          |

| EEG                     | $100\sim200$        | 16                         |

| EOG                     | $100\sim200$        | 16                         |

| ECG                     | $100\sim250$        | 8                          |

| Breathing sounds        | $100\sim5\text{K}$  | 8                          |

| EMG                     | $100\sim5\text{K}$  | 8                          |

| Audio (hearing aids)    | $15\sim44K$         | 16                         |

| Ambient light level     | $0.017\sim 1$       | 16                         |

| Atmospheric temperature | $0.017 \sim 1$      | 16                         |

| Ambient noise level     | $0.017\sim 1$       | 16                         |

| Barometric pressure     | $0.017\sim 1$       | 8                          |

| Wind direction          | $0.2 \sim 100$      | 8                          |

| Seismic vibration       | $1 \sim 10$         | 8                          |

| Engine temperature      | $100 \sim 150$      | 16                         |

| Engine pressure         | $100\sim150$        | 16                         |

provide a potential solution for the ultra-low energy applications. They may also be applicable to applications with bursty characteristics, e.g., microprocessors which infrequently require high performance and most of the time it only makes sense to have a near-standby mode [13] [14].

However, the design rules provided by foundries normally set 2/3 of the full  $V_{DD}$  as the lower bound for  $V_{DD}$  scaling in deep sub-micron processes. Taking the Samsung's DVFS Design Technology [9] and the TSMC design rule as examples, the constraint of  $V_{DD}$  for digital circuits designed in CMOS 65nm Standard  $V_T$  Process is in the  $0.8\mathrm{V} \sim 1.2\mathrm{V}$  range. The reasoning behind the lower constraint is twofold. First, as  $V_{DD}$  scales, the driving capability of transistors reduces accordingly. Because most electronic consumer applications need operating frequencies in the range of tens of MHz to reach

certain throughput, which might not be fulfilled with aggressive  $V_{DD}$  scaling,  $2/3\ V_{DD}$  is tested to be a safe lower bound. Second, digital circuits become particularly sensitive to process variations when  $V_{DD}$  scales below  $2/3\ V_{DD}$ . Process variations are likely to cause malfunctioning, and both the timing yield and functional yield tremendously decrease. As a result,  $2/3\ V_{DD}$  is generally chosen to maintain adequate margin to prevent high yield loss and to keep quality to the industry standard. Obviously, this limitation has prevented further power/energy reduction from voltage scaling. To safely evade this limitation and to enable wide range voltage scaling from the nominal supply to the near/sub threshold region is a goal to be achieved in this work.

## 1.3 Related Sub-threshold Work

In recent years, some design techniques for operating digital circuits in the sub-threshold region  $(V_{GS} < V_T)$  have been explored. Table 1.3 summarizes and categorizes the existing energy-efficient techniques that take advantage of sub-threshold operation. Most of these works are from the M.I.T sub-threshold circuit group headed by Professor Anantha Chandrakasan, in association with Texas Instruments. As can be seen from Table 1.3, the existing sub-threshold works span many different levels of abstraction. On the system level, some research has been done to model the characteristics of sub-threshold circuits, including current, delay, energy, variations, etc. Based on these models, the performance of a given sub-threshold system, the optimal energy point and the possible energy savings can be obtained. On the physical level, researchers have made effort to develop circuit styles for logic that can operate in the sub-threshold. The authors in [19] provide a closed-form solution for sizing transistors in a stack and introduce a new logical effort suitable to subthreshold design. Traditional logic families like domino [60], pass transistor logic, pseudo nMOS [61] have also been considered for their usefulness in sub-threshold regime. In addition, sub-threshold on-chip SRAM architectures and circuits have been explored, as later it is found that SRAMs were the energy consumption bottleneck for micro-processors at ultra-low voltages. Some very interesting prototype chips which function in the sub-threshold, have been presented. Among these chips, the most famous are the 180mV FFT processor in 180nm CMOS process designed by Alice Wang in 2004 [33] [34]. This is the first digital processor working in the sub-threshold. Ben Calhoun had designed the 256kb 10-T dual port SRAM in 65nm CMOS process [24] . It had been improved to 8-T dual port SRAM by Naveen Verma in 2007 [29] [30]. A sensor node processor having both sub-threshold logic and SRAMs is presented by University of Michigan [31][32]. It claims the highest energy savings. Recently, M.I.T group and Texas Instruments had jointly announced the newest sub-threshold MSP430 DSP processor with integrated DC-DC [38] [39].

It is also worth mentioning some effort that has been made to create the "perfect" transistor for sub-threshold operation. Optimized MOSFET [62] [63] , SOI MOSFET [64] [65] , double gated MOSFET [66] may gain increasing popularity for their usage in sub-threshold design. SOI MOSFETs have much steeper subthreshold slope and more resistance to short-channel effects. [66] proposed to use double gated MOSFET in sub-threshold due to its steep sub-threshold slope and a small gate capacitance. In addition, MTCMOS, VTC-MOS, dual/multiple  $V_T$  partitioning are also claimed to benefit sub-threshold design.

However, the downsides of these existing works are still the considerable performance loss at ultra-low supply voltages and yield loss due to the effects of process variations.

## 1.4 Contributions of This Work

The major contributions of this work include:

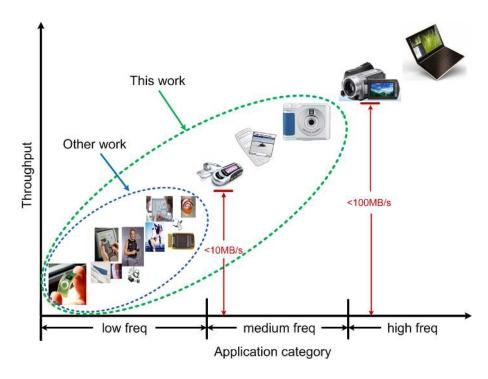

- Although operating in the sub-threshold renders huge energy savings, it

is believed only suitable for low-speed applications because the drivability is very small. This work explores the possibility to use architecturelevel parallelism to compensate for throughput degradation. Through

efficient parallelism, sub/near threshold techniques are extended to lowenergy and medium throughput applications, such as mobile image processing. Figure 1.1 shows the applicable throughput range of this work

and the other work.

- Little attention has been given in previous art to the sub/near threshold circuit's yield. This work makes an effort to increase the reliability of sub/near threshold circuits. We propose a novel, configurable  $V_T$  balancer to balance the  $V_T$  between nMOS and pMOS transistors. Our  $V_T$

Table 1.3: Summary of existing sub-threshold work

| Category                   | Existing sub-threshold work                                                                                                                                                                                                                                                                                                 |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sub-threshold modeling     | [15] [16] [17] [18]: built up the analytical models for sub-threshold current, delay, energy and variations                                                                                                                                                                                                                 |  |

| Sub-threshold logic design | [19] [20] [21] [22] [60] [61] : explored sub-threshold logic cells                                                                                                                                                                                                                                                          |  |

| Sub-threshold memory       | [23] [24] : 256kb 10-T dual-port SRAM in 65nm CMOS [25] : 512×13b dual-port SRAM in 180nm CMOS [26] : 480kb 6-T dual-port SRAM in 130nm CMOS [27] [28] : 2kb 6-T single-port SRAM in 130nm CMOS [29] [20] : 256kb 8-T dual-port SRAM in 65nm CMOS                                                                           |  |

| Sub-threshold processors   | [31] [32]: 2.6pJ/inst 3-stage pipelined sensor node processor in 130nm CMOS [33] [34]: 180mV FFT processor in 180nm CMOS [35] [36]: 0.4V UWB baseband processor in 65nm CMOS [37]: 85mV 40nW 8×8 FIR filter in 130nm CMOS [38] [39]: 2-stage pipelined micro-controller with embedded SRAM and DC-DC converter in 65nm CMOS |  |

Figure 1.1: Applicable throughput range of this work and other work

balancer helps increasing both the functional yield and timing yield.

- ullet In addition to the  $V_T$  balancer, other sub-threshold physical level approaches including transistor sizing, utilizing parallel transistor  $V_T$  mismatch to improve drivability, selecting reliable library cells for logic synthesis, turning ratioed logic into non-ratioed logic, and level shifter design, are addressed in this thesis.

- To estimate noise margins, minimum functional supply voltage, as well as the functional yield in the sub-threshold, this work proposes a fast, accurate and statistical method based on *Affine Arithmetic* (AA). This method has an accuracy of 98.5% w.r.t. to transistor-level Monte Carlo simulations, but the running time is much shorter.

- SubJPEG, a state-of-the-art ultra-low energy multi-standard JPEG encoder co-processor is designed and implemented to demonstrate these ideas. This 1.4×1.4mm<sup>2</sup> 8-bit resolution DMA based co-processor chip is fabricated with TSMC 65nm 7-layer standard V<sub>T</sub> CMOS process. It contains 4 parallel DCT-Quantization engines, 2 voltage domains and 3

clock domains. For DCT and quantization operation, this co-processor dissipates only 0.75pJ energy per single engine in one clock cycle, when using a 0.4V power supply at the maximum 2.5MHz in the sub-threshold mode, which leads to 8.3× energy reduction compared to using the 1.2V nominal supply. In the near-threshold mode the engines can operate with 4.5MHz frequency at 0.45V, with 1.1pJ energy per engine in one cycle. The overall system throughput then still meets 640×480 15fps VGA compression requirement. By further increasing the supply voltage, the prototype chip can satisfy multi-standard image encoding. To our best knowledge, *SubJPEG* is the largest, sub/near threshold system so far.

## 1.5 Thesis Organization

This thesis is organized into five chapters. Chapter 1 presents the background of voltage scaling, reviews the related previous art about sub-threshold techniques and states the contributions that have been made by this thesis. In Chapter 2, many aspects of a sub-threshold system modeling, including current, delay, energy, variability and optimum  $V_{DD}$  are analyzed. The feasibility to compensate for throughput degradation by using architecture-level parallelism is also explored. An EDA approach for fast noise margin estimation for deep sub-threshold combinational circuits is introduced at the end of this chapter. Chapter 3 presents the physical level effort we have made to improve sub-threshold circuit's yield. In Chapter 4, the design of SubJPEG prototype chip is presented in detail. Finally, the conclusions, future work and discussions are given in Chapter 5.

# Chapter 2

# **System Level Analysis**

o quickly analyze the performance of a sub-threshold system, in this chapter we present the sub-threshold modeling, including current, delay, energy and variability. The optimum  $V_{DD}$ , at which the energy per operation is the lowest, is analyzed. The feasibility to compensate for throughput degradation by using architecture-level parallelism is also discussed. Finally, an EDA approach for fast sub-threshold noise margin estimation is introduced.

# 2.1 Sub-threshold Modeling

#### 2.1.1 Sub-threshold Current Model

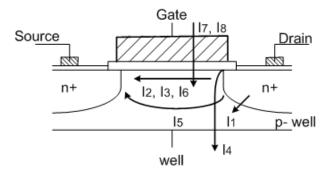

Sub-threshold design exploits leakage current as the driving current. We should first understand where the leakages come from. Figure 2.1 illustrates the leakage currents of a short channel device [54]. These leakage sources include:

## a) pn Junction Reverse Bias Current (I<sub>1</sub>)

A reverse bias pn junction leakage involves two key components. One is minority carrier diffusion/drift near the edge of depletion region and the other is due to electron-hole pair generation in the depletion region of the reverse bias junction.  $I_1$  is a non-significant contributor to total leakage current.

Figure 2.1: Sources of leakage current

#### b) Sub-threshold Leakage (I<sub>2</sub>)

Sub-threshold conduction current between source and drain in a MOS transistor occurs when gate voltage is below  $V_T$ . Sub-threshold conduction is dominated by the diffusion current. The carriers move by diffusion along the surface. Weak inversion conduction dominates modern device off state leakage, especially when low  $V_T$  processes are used.

## c) Drain -Induced Barrier Lowering - DIBL (I<sub>3</sub>)

In a short-channel device, the source-drain potential has a strong effect on the band bending over a significant portion of the device. As a result, the threshold voltage and consequently the sub-threshold current of short-channel device vary with the drain bias. The barrier of a short-channel device reduces along with the increase of drain voltage, which causes a lower threshold voltage and a higher sub-threshold current. This effect is referred as Drain–Induced Barrier Lowering (DIBL).

### d) Gate -Induced Drain Leakage - GIDL (I<sub>4</sub>)

Gate-Induced Drain Leakage (GIDL) is due to high field effect in the drain junction of MOS transistor. When the gate is biased to cause an accumulation layer at the silicon surface, the silicon surface under the gate has almost the same potential as the p-type substrate.

## e) Punch Through (I<sub>5</sub>)

Punch-through occurs when drain and source depletion regions approach each other and electrically "touch" in the channel. Punch-through is a space-charge condition that allows channel current to exit deep in the sub-gate region.

## f) Narrow Width Effect (I<sub>6</sub>)

Transistor  $V_T$  in non-trench isolated technologies increases for geometric gate widths on the order of  $0.5\mu m$ . No narrow width effect is observed when transistor sizes exceed significantly  $0.5\mu m$ .

### g) Gate Oxide Tunneling (I<sub>7</sub>)

Reduction of gate oxide thickness results in increase in field across the oxide. The high electric field coupled with low oxide thickness results in tunneling of electrons from substrate to gate and from gate to substrate through gate oxide, resulting in gate oxide tunneling current. Gate oxide tunneling current could surpass weak inversion and DIBL as a dominant leakage in the future as oxide get thin enough.

#### h) Hot Carrier Injection (I<sub>8</sub>)

In a short channel transistor, because of high electric field near the Si/SiO2 interface, electrons and holes can gain sufficient energy from the electric field to cross the interface potential barrier, and enter into the oxide layer. This effect is known as hot carrier injection.

Among the leakage currents, sub-threshold leakage  $(I_2)$  and DIBL  $(I_3)$  are the source of leakage used as driving current in the sub-threshold design. Conventionally, this driving current of an nMOSFET is modeled by

$$I_{D} = \begin{cases} WI_{0}e^{\frac{(V_{GS} - V_{T} - \gamma V_{SB} + \eta V_{DS})}{nU}} (1 - e^{-\frac{V_{DS}}{U}}) & (V_{GS} < V_{T}) \\ WKI_{0}(V_{GS} - V_{T})^{\beta} & (V_{GS} \ge V_{T}) \end{cases}$$

(2.1)

where K is a constant intrinsic to the process,  $\beta$  is the velocity saturation effect factor, n is the sub-threshold swing factor,  $\eta$  is the DIBL coefficient, W is the transistor width. U is the so-called thermal voltage kT/q, which is around 26mV at room temperature.  $I_0$  is the zero-threshold leakage current for a unit width transistor. Typical values for the parameters in a 65nm Standard  $V_T$  CMOS process are given in Table 2.1. Please note the slight discontinuity at  $V_{GS}=V_T$  in the model. Equation (2.1) clearly indicates a super-linear decrease of sub-threshold driving current due to  $V_{DD}$  scaling, since  $V_{GS}$  is often considered approximately equal to  $V_{DD}$  in analysis.

Although the current model in equation (2.1) is well-known for its simplicity for back-of-the-envelope mathematic manipulations, we found it inadequate to

Table 2.1: Parameters for 65nm CMOS  $SV_T$  process

| $\overline{n}$ | η    | γ    | $V_T$ |

|----------------|------|------|-------|

| 1.37           | 0.03 | 0.33 | 0.41  |

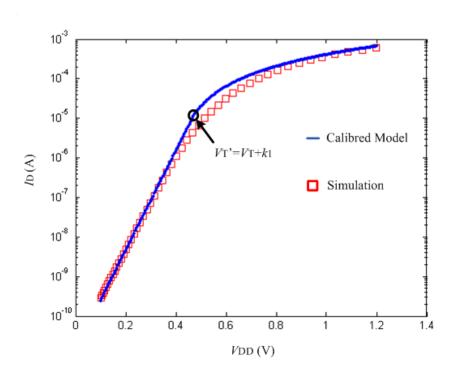

capture device characteristics for very deep submicron CMOS technology. To keep the simplicity but improve the accuracy, we have calibrated this transregional model, which is described by:

$$I_{D} = \begin{cases} WI_{0}e^{\frac{(V_{GS} - V_{T} - k_{1} - \gamma V_{SB} + \eta V_{DS})}{nU}} (1 - e^{-\frac{V_{DS}}{U}}) & (V_{GS} < V_{T} + k_{1}) \\ WKI_{0}(V_{GS} - V_{T})^{\beta} & (V_{GS} \ge V_{T} + k_{1}) \end{cases}$$

$$(2.2)$$

where  $k_1$  is a constant parameter obtained with a Levenberg–Marquardt algorithm (LMA) through curve fitting. If we define

$$V_T' = V_T + k_1 (2.3)$$

Then equation (2.2) becomes equation (2.4),

$$I_{D} = \begin{cases} W I_{0} e^{\frac{(V_{GS} - V'_{T} - \gamma V_{SB} + \eta V_{DS})}{nU}} (1 - e^{-\frac{V_{DS}}{U}}) & (V_{GS} < V'_{T}) \\ W K I_{0} (V_{GS} - V_{T})^{\beta} & (V_{GS} \ge V'_{T}) \end{cases}$$

$$(2.4)$$

Figure 2.2 compares this calibrated transistor current model with a SPICE simulation model for an nMOSFET in a CMOS 65nm Low Power Standard  $V_T(\mathrm{LP}-\mathrm{S}V_T)$  technology. As shown, the model provides very good accuracy with respect to the SPICE simulation. The largest deviation occurs when  $V_{DD}$  is in the vicinity of  $V_T'$ , which is about 0.48V in our case.

Figure 2.2: Calibrated transistor current model and SPICE simulation for 65nm  $\mathrm{S}V_T$  nMOS transistor

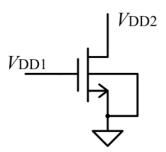

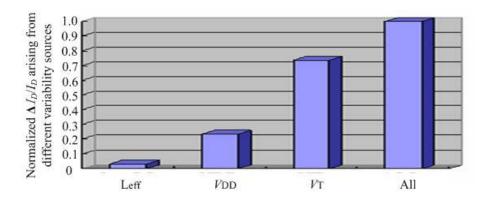

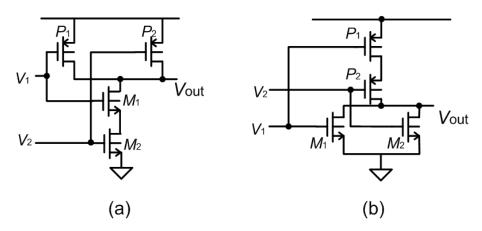

In super-threshold design, the supply voltage  $V_{DD}$ , the geometric  $L_{eff}$  and the threshold  $V_T$ , are the major variability sources. It is necessary to investigate how each of them contribute to the total current variation in the subthreshold. We take an nMOS transistor whose aspect ratio is  $0.4\mu\text{m}/0.065\mu\text{m}$ , and connect its gate to  $V_{DD1}$  and its drain to  $V_{DD2}$ , respectively. Its bulk and source are connected to  $G_{ND}$ , as shown in Figure 2.3. We assume that  $V_{DD1}$ =0.9 $V_{DD2}$  and  $V_{DD2}$ = $V_{DD}$ . The parameters that are varied to compute the envelope are  $L_{eff}$  ( $\pm 5\%$  variation),  $V_T$  ( $\pm 10\%$  variation) and  $V_{DD2}$  ( $\pm 10\%$  variation). In Figure 2.4 the sensitivity  $\Delta I_D/I_D$  arising from each different variability source is normalized to that arising from all variability sources at  $V_{DD}$  =200mV. It is clear that threshold voltage variation is the dominant criminal for sub-threshold current variation due to its exponential correlation, and therefore becomes our major enemy. In contrast, the other two variation sources have relatively small impact, which can be mitigated by designing with narrow margins.

Figure 2.3: Illustration of the simulated transistor

## 2.1.2 Sub-threshold Propagation Delay Model

To model the sub-threshold propagation delay, we assume  $C_{load}$  the load capacitance of a FO4 inverter and  $I_d$  the average driving current of a FO4 inverter.  $L_d$  is the logic depth which represents how many inverters are chained to mimic the critical path delay. The propagation delay of a characteristic inverter  $T_q$  can be derived as

$$T_q = C_{load} V_{DD} / I_d (2.5)$$

and the critical path delay is

$$T_{cp} = L_d T_q \tag{2.6}$$

Figure 2.4: Normalized driving current variability arising from different variation sources

The maximum operating frequency of the chip is then calculated,

$$f \max = \frac{1}{T_{cp}} \tag{2.7}$$

## 2.1.3 Sub-threshold Energy Model

Instead of using power as the metric, we use energy-per-operation (EPO) in our study since it is the real metric to battery life. Dynamic energy and leakage energy are the two major sources of energy dissipation in CMOS digital circuits. The dynamic energy per operation is

$$E_{dynamic} = \alpha C V_{DD}^2 \tag{2.8}$$

where  $\alpha$  is the average switching activity factor of all the output nodes, C is the total capacitance of all the output nodes,  $V_{DD}$  is the supply voltage.

The off-state leakage current  $I_l$  of a digital block is dominated by the zero subthreshold leakage [40] .  $I_l$  can be modeled by letting  $V_{GS}$ =0 and  $V_{DS}$ = $V_{DD}$  in equation (2.2) , i.e.

$$I_{l} = W I_{0} e^{\frac{(-V_{T}' - \gamma V_{SB} + \eta V_{DD})}{nU}} (1 - e^{-\frac{V_{DD}}{U}})$$

(2.9)

Thus, the leakage energy per operation can be obtained as

$$E_{leakage} = I_l V_{DD} T_c (2.10)$$

where  $T_c$  is the operating cycle time. The total EPO of a digital circuit is

$$EPO = E_{dynamic} + E_{leakage} = \alpha C V_{DD}^2 + I_l V_{DD} T_c$$

(2.11)

### 2.2 Optimum Energy-per-Operation (EPO)

Above analysis shows that, as voltage scales, the dynamic energy reduces. However, because of the increased delay, the leakage energy increases. Therefore, whether the total EPO increases or decreases is uncertain. In fact, there is an optimum-energy supply voltage point, operating at which offers the best EPO. Theoretically, this point can be solved by

$$\partial \text{EPO}/\partial V_{DD} = 0$$

(2.12)

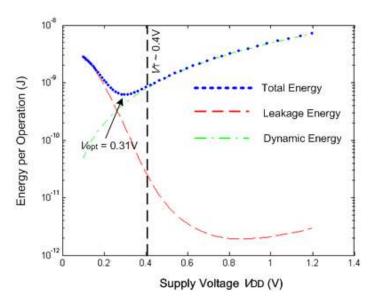

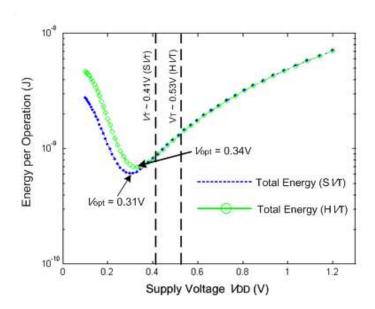

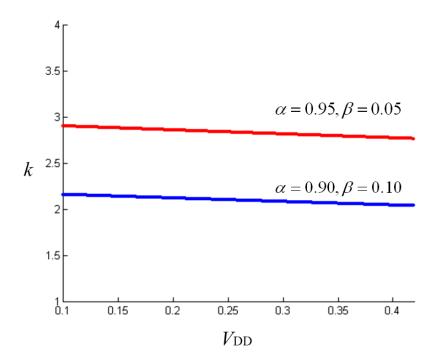

This optimum voltage point can also be obtained experimentally. Let us introduce a baseline processor which is based on [55] from NXP. This real milliongate baseline processor is fabricated in a CMOS 65nm Low Power Standard  $V_T$  (LP-S $V_T$ ) technology. The average switching activity factor  $\alpha$  is 0.12, the total switching capacitance for the entire block is 4.9nF, the nominal  $V_{DD}$  is 1.2V, average  $V_T$  of pMOS and nMOS is 0.41V, off-state leakage  $I_l$  is 648 $\mu$ A and  $L_d$  = 24. This baseline processor is supposed to run at its maximum speed, i.e.,  $T_c$ = $T_{cp}$ . Figure 2.5 shows how the dynamic, leakage and total energy of the baseline processor vary when  $V_{DD}$  scales. The simulated optimal  $V_{DD}$  point  $V_{opt}$  is indicated. Since nowadays high  $V_T$  (HV $_T$ ) processes are a popular option for low power digital design, a simulation has also been carried for the same block implemented through a HV $_T$  processe. Figure 2.6 compares the total energy per operation for SV $_T$  and HV $_T$  processes. The behavior of these curves is similar.

As indicated by Figure 2.5 and Figure 2.6, the optimal energy operating supply voltage  $V_{opt}$  is in the sub-threshold region. Further lowering  $V_{DD}$  below  $V_{opt}$  does not yield any additional energy benefits. We also analyzed some other circuits, and found that their  $V_{opt}$  is normally greater than 0.3V. This suggests not scaling the  $V_{DD}$  to the very deep sub-threshold level but to stay at the

weak sub-threshold or near threshold region. In fact, only for a digital block with extremely high switching density, there is a need to scale its  $V_{DD}$  into very deep sub-threshold region. In addition, we observe that using the  $\mathrm{H}V_T$  process raises the EPO with 13% as compared to the  $\mathrm{S}V_T$  process. Therefore, the  $\mathrm{S}V_T$  process is selected for our research.

Figure 2.5: Dynamic/Leakage/Total energy per operation and the optimal  $V_{DD}$  in  $SV_T$  process

### 2.3 Parallelism for Fixed Throughput

The circuit throughput degrades when  $V_{DD}$  scales. To maintain a fixed throughput, parallel processing units can be used. We assume that the computation tasks of individual units are independent, meaning that no performance penalty due to data or control dependencies is incurred from parallelism. This assumption is largely suitable for applications such as sound/graphic and other streaming processing, though there are still some sequential parts. Ideally, for a fixed  $V_{DD}$ , the degree of parallelism does not affect the EPO whereas a larger throughput can be obtained simply by using more parallelized units. However, in reality the multiplexer and de-multiplexer circuits also contribute to increased overhead in the EPO. To take this overhead into account, the area

Figure 2.6: Total EPO and the optimal  $V_{DD}$  points for  $SV_T$  and  $HV_T$  process

and timing are approximated in equations (2.13), (2.14), and (2.15),

$$Area = Area_{baseline} \times M^p \tag{2.13}$$

$$T_{overhead} = \log_2 M \times FO4 \tag{2.14}$$

$$T_{\rm c} = T_{baseline} + T_{overhead}$$

(2.15)

where M is the associated degree of parallelism, and  $\rho$  is the area growth factor which indicates that the circuit area grows super-linearly with M. In our simulation, we choose  $\rho$ =1.1 [56] . Referring to equation (2.11), the area overhead affects C and  $I_l$ , while the timing overhead affects  $T_c$ .

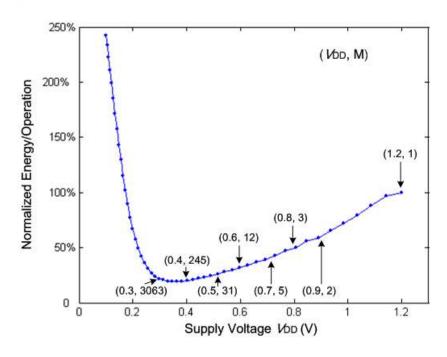

Figure 2.7 shows the normalized EPO for different values of  $V_{DD}$ , with the same throughput as that of the baseline processor operating at the nominal 1.2V supply voltage. The necessary degrees of parallelism for a few  $V_{DD}$  points are annotated in the plot. As shown, compared to operating at the 1.2V

nominal  $V_{DD}$ , we could obtain  $5\times$ ,  $4\times$ ,  $3\times$  EPO reduction when  $V_{DD}$  is at 0.4V, 0.5V, 0.6V, respectively. At first glance it is unwelcome to see the associated 245, 31 and 12 parallel widths, which implies an impossibly large silicon area. In addition, the larger the circuit's area, the more likely are defects, and so will fail to achieve commercially viable yields. However, it should be noted that in the analysis we assume the baseline processor is operating at its maximum speed, which is about 300MHz. For some consumer electronic applications which only need up to a few tens of MHz, the associated parallel width can become much smaller and thus more affordable. For applications that only run at KHz $\sim$ MHz range frequencies, such as sensor networks, biomedical instrumentations and audio processors, operating at the  $V_{opt}$  is possible and there is not even a need to use parallel paths.

Figure 2.7: Normalized EPO at different  $V_{DD}$  for the same throughput

# 2.4 Statistical Noise Margin Estimation for Sub-threshold Combinational Circuits

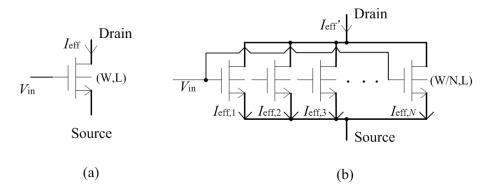

When designs are moving from the super-threshold to the sub-threshold domain, the effective-to-idle current ratio  $(I_{eff}/I_{idle})$  diminishes rapidly. Accordingly, the available noise margin, defined as the difference between  $V_{OH}$ and  $V_{OL}$ , is reduced. This may lead to a failure of the decoding logic values. Manufacturing variability further worsens circuit robustness. Therefore, guaranteeing sufficient output noise margins becomes a unique and important issue for sub-threshold designs. Targeting at a fixed  $V_{DD}$ , prior art [19] -[22] relies on device sizing as a means of ensuring enough noise margins for individual cells. This is because larger devices reduce the  $V_T$  mismatch [47]. This methodology neglects correlations between gates and results in a pessimistic estimation of the output's noise margin. For instance, a gate that outputs higher  $V_{OL}$  (lower  $V_{OH}$ ) can tolerate higher  $V_{IL}$  (lower  $V_{IH}$ ) from its preceding gate. Ignoring inter-cell correlations results in an overestimation of the minimum  $V_{DD}$  and device sizes, thus an increase of power/energy consumption. It would be also convenient for the designers to know the minimum functional  $V_{DD}$  in the design time. Unfortunately, nowadays this information is obtained only through post-silicon testing, such as the 180mV FFT processor [33] [34] and the 85mV FIR filter [37], etc.

Theoretically, using Monte-Carlo DC simulations to extract the noise margin can solve these problems. Based on the extracted noise margin information, the designer can improve the robustness of the circuitry by means of gate resizing, buffer insertion, logic restructuring, etc. It also helps to estimate the minimum functional  $V_{DD}$ . In this way, the imposed additional area and power overhead are prevented. However, this is at the cost of a much longer design time. Usually, the design flow requires multiple iterations between noise margin extraction and circuit tuning. In our experience, spending tens of hours to extract the noise margins of a benchmark circuit composed of only thousands of logic gates is quite common. Therefore, exploring an approach that can promptly estimate the noise margin, minimum functional  $V_{DD}$  and the functional yield for a given circuit, taking into consideration the impact of process variations and inter-cell correlations, is of great importance.

This section introduces a novel noise margin extraction methodology for subthreshold combinational circuits. Our methodology has the following features. First, instead of performing slow transistor-level DC simulations, we propose

## 2.4. STATISTICAL NOISE MARGIN ESTIMATION FOR SUB-THRESHOLD COMBINATIONAL CIRCUITS

a fast gate-level noise margin modeling approach based on a new equivalent resistance model. We use curve-fitting to calibrate our model, so that the estimation results can perfectly match the results simulated from transistor level DC simulations. In analogy to the Elmore delay model for timing analysis, the gate-level model renders reasonably good accuracy, but is computationally much more efficient compared to its transistor-level counterpart. Second, we introduce the Affine Arithmetic (AA) approach to symbolically traverse the whole circuit from its inputs to outputs. Applying AA helps to model correlations of noise margins among cells. Besides, as the noise margins of the final outputs are expressed in the affine form, their statistical spread can be extracted. In this way, the minimum functional  $V_{DD}$ , as well as the functional yield of a circuit can be estimated. Our approach iterates only once per input vector, hence the running time can be reduced by several orders compared to the MC simulation. Experimental results show that our approach has 98.5% accuracy using MC simulations as a reference, but can reduce the running time by several orders of magnitude.

## 2.4.1 Estimating gate noise margin with rectified equivalent resistance model

As aforementioned, we first propose a gate-level noise margin model and show how to calibrate it to improve the estimation accuracy. Recall the models of the sub-threshold current for nMOS and pMOS transistors given in Section 2.1,

$$I_{nMOS} = I_{0n}e^{\frac{(V_{GS} - V'_{Tn} + \eta V_{DS} - \gamma V_{SB})}{nU}} (1 - e^{-\frac{V_{DS}}{U}})$$

(2.16)

$$I_{pMOS} = I_{0p} e^{\frac{-(V_{GS} - V'_{Tp} + \eta V_{DS} - \gamma V_{SB})}{nU}} (1 - e^{\frac{V_{DS}}{U}})$$

(2.17)

To estimate the noise margin of a cell at gate-level, we introduce an *equivalent resistance* model into the DC analysis. The resistance is the derivative of the drain-to-source voltage  $V_{DS}$ , with respect to the drain-to-source current, at the DC point  $V_{DS} = 0$ . Ignoring for the moment body effects, we can approximate the equivalent resistances of nMOS and pMOS transistors as

$$R_{nMOS} = (I_{0n})^{-1} U e^{-(V_{in} - V'_{T_n})/nU}$$

(2.18)

$$R_{pMOS} = (I_{0p})^{-1} U e^{(V_{in} - V_{DD} - V'_{Tp})/nU}$$

(2.19)

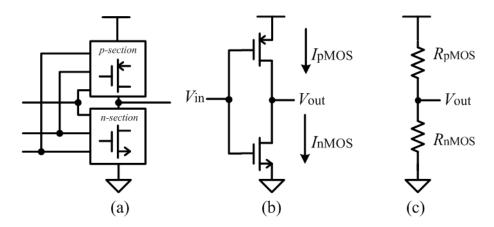

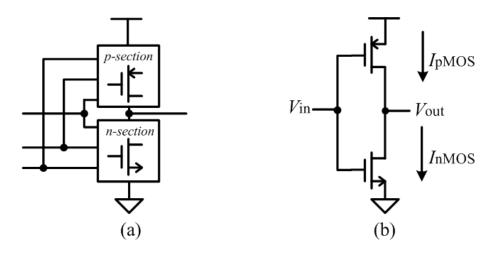

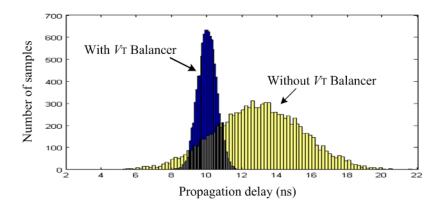

A typical digital cell consists of a p-section with a common node tied to an n-section (see Figure 2.8(a)). Let us start the analysis with a CMOS inverter (Figure 2.8(b)). Its equivalent resistance model is shown in Figure 2.8(c).

Figure 2.8: (a) Cell schematic (b) Inverter (c) Equivalent model

Assuming  $I_{0n} = I_{0p}$ , we can obtain the output voltage of the inverter,

$$V_{out} = \left\{ 1 + e^{\left[2V_{in} - (V_{DD} + V'_{Tn} + V'_{Tp})\right]/nU} \right\}^{-1} V_{DD}$$

(2.20)

If we define

$$x = (V'_{Tn} + V'_{Tp})/2 (2.21)$$

then Equation (2.20) can be expressed by

$$V_{out} = \left\{ 1 + \left[ e^{(V_{in} - x - V_{DD}/2)/nU} \right]^2 \right\}^{-1} V_{DD}$$

(2.22)

The above analysis may have lost validity as we neglected the body effect and assumed  $I_{0n} = I_{0p}$ . To fix the accuracy, we intentionally insert a parameter  $\lambda$  into (2.22) for calibration,

$$V_{out} = \left\{ 1 + \left[ e^{\lambda + (V_{in} - x - V_{DD}/2)/nU} \right]^2 \right\}^{-1} V_{DD}$$

(2.23)

where  $\lambda$  can be extracted through *nonlinear least square curve-fitting* from actual simulated results. Figure 2.9 gives the noise margin estimated by the

## 2.4. STATISTICAL NOISE MARGIN ESTIMATION FOR SUB-THRESHOLD COMBINATIONAL CIRCUITS

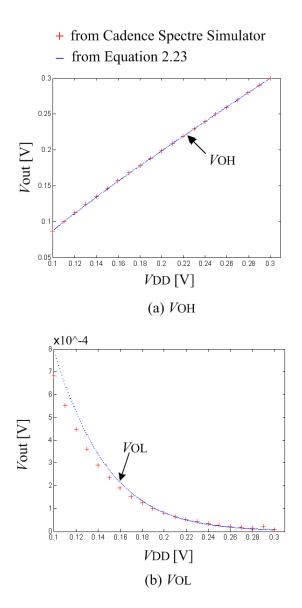

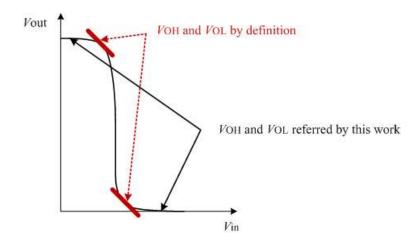

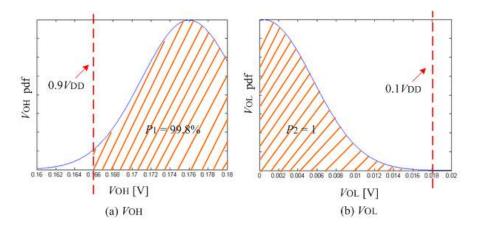

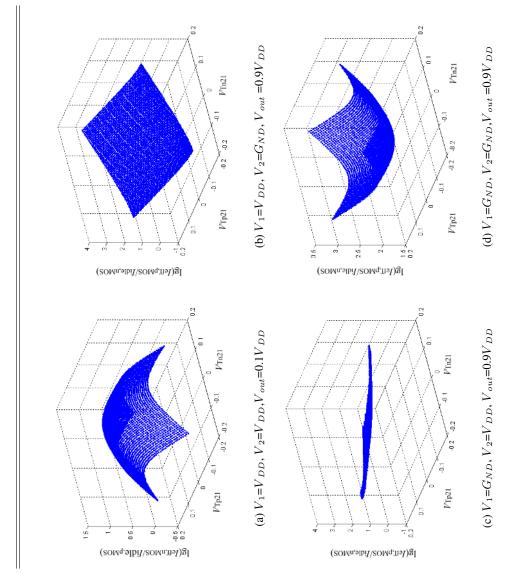

Cadence Spectre Simulator and from Equation (2.23), for an inverter with Wp/Wn=0.28 $\mu$ m/0.2 $\mu$ m in 65nm CMOS process under typical technology (TT) when  $V_{DD}$  is swept in the sub-threshold region. By textbook definition, the  $V_{OL}$  and  $V_{OH}$  are the two operational points of the inverter where  $d(V_{out})/d(V_{in})$  = -1. The  $V_{OL}$  and  $V_{OH}$  referred by this work are the steady high and low voltage output values, which are slightly different from the textbook definition values (Figure 2.10). Please note that the vertical axes in Figure 2.9 have different scales for each plot. As shown, both results perfectly match each other after curve-fitting.

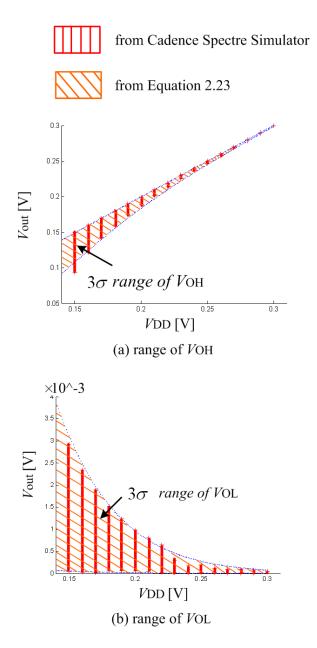

Next, we show how to incorporate process variations in our model. It is already shown in Section 2.1 that  $V_T$  variation is the dominant malefactor for the sub-threshold noise margin due to its exponential correlation with the sub-threshold current. The  $V_T$  mismatch of paired transistors also causes a wide range of sub-threshold current shifts [41] . In our model, the  $V_T$  variation is reflected on the variation of x. As  $V_{Tn}$  and  $V_{Tp}$  are normally distributed, x is also normally distributed, i.e.,  $x \sim N(\mu_x, \sigma_x^2)$ . Parameters  $\mu_x$  and  $\sigma_x$  are primarily dependent on the size of the transistors, and can also be characterized through transistor level simulations. Figure 2.11 shows the  $3\sigma$  range of  $V_{OL}$  and  $V_{OH}$  obtained from Cadence Spectre Simulator and from our model. Once again, the results simulated from the transistor level model and our new model perfectly coincide. An observation from the two plots is that the variation of  $V_{OH}$  is much larger than that of  $V_{OL}$  due to the fact that the nMOS transistor can be much leakier than the pMOS transistor.

A similar analysis can be carried out for other static digital gates. For an N-input gate, we found that its output voltage can be approximately expressed as a function,

$$V_{out} = f(V_{in}, X, V_{DD})$$

(2.24)

where  $V_{in}$  denotes the set of N inputs' voltages, and X is the set that contains N normally distributed variables corresponding to the different inputs. For example, the output voltages of an N-input NAND and an N-input NOR gate can be expressed in Equations (2.25) and (2.26), respectively,

$$V_{out,nand} = \left\{ 1 + \left[ \sum_{i=1}^{N} \left[ e^{\lambda i - (V_{in.i} - X_i - V_{DD}/2)/nU} \right] \right]^{-2} \right\}^{-1} V_{DD} \quad (2.25)$$

Figure 2.9: Noise margin generated from Spectre Simulator vs from Equation 2.23

Figure 2.10: Noise margin by definition and by this work

$$V_{out,nor} = \left\{ 1 + \left[ \sum_{i=1}^{N} \left[ e^{\lambda i + (V_{in.i} - X_i - V_{DD}/2)/nU} \right] \right]^2 \right\}^{-1} V_{DD}$$

(2.26)

where  $V_{in..i}$  is the voltage of the  $i^{th}$  input and  $V_{in..i} \in V_{in}$ ,  $X_i$  relates to the  $V_T$  values of a pair of nMOS and pMOS transistors which have the same input, and  $X_i \in X$ , and  $X_i \sim N(\mu_{x_i}, \sigma_{x_i}^2)$ .  $\lambda_i$  is the  $i^{th}$  fitted parameter. The noise margin model for each type of gate, including the pre-characterized constants  $\mu_{x_i}, \sigma_{x_i}, \lambda_i(\forall i)$ , can be embedded in a library file of the EDA tool.

Estimating the cell's noise margin with its equivalent resistance model renders reasonably good accuracy, and provides a much simpler expression when compared to the transistor-level model. The new noise margin model performs well at the gate-level, and avoids the need for solving a transistor-level matrix, hence tremendously reduces the computation intensity for the EDA software. However, if the statistical noise margins at the outputs are to be extracted, Monte-Carlo DC analysis is still needed. To totally eliminate using Monte-Carlo simulations, we introduce the *Affine Arithmetic* model for efficient computation and propagation of noise margins.

Figure 2.11:  $3\sigma$  range of noise margin generated from Spectre Simulator vs from Equation 2.23

## 2.4.2 Estimating statistical output noise margin with affine arithmetic model

The Affine Arithmetic (AA) model is used for example in bit-width estimation and probabilistic error analysis ([42] -[45]). In the AA model, an uncertain variable x is expressed as

$$x = C_0 + \sum_{i}^{N} C_i \varepsilon_i \tag{2.27}$$

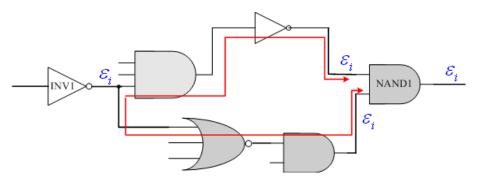

where  $C_0$  is the *central value* of the affine form of x,  $\epsilon_i$  is an independent *noise symbol* multiplied by its corresponding *coefficient*  $C_i$ . All *noise symbols* denote independent and identically-distributed variables. AA is very suitable for symbolic propagation. This is because if the operands are in AA form, the results of the arithmetic operations, such as addition, subtraction, multiplication, are also in AA form. Furthermore, AA is capable of carrying correlation information. Along a propagation path, one *noise symbol*  $\epsilon_i$  may contribute to the uncertainties of two or more variables. When these variables are combined, the uncertainties may also be combined so that their correlations are taken into consideration. This property is especially useful for our case. As shown in Figure 2.12, the variation term  $\epsilon_i$  in the noise margin expression at the output of INV1, will re-converge at the inputs of NAND1, and will proceed to the output of NAND1. In this way, the final results can be more accurately estimated.

Figure 2.12: Noise margin uncertainty propagation with AA model

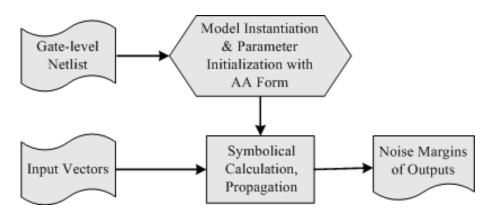

Figure 2.13 shows the statistical noise margin estimation flowchart of this work. The new approach takes 3 steps:

### 1. Model Instantiation & AA form Initialization

Figure 2.13: Noise margin estimation flowchart

Given the synthesized gate-level netlist, we instantiate each gate with the noise margin model described in Section 2.4.1. Each parameter in X is initialized and stored in AA form, i.e.

$$X_{i,k} = X_{0i,k} + C_{i,k}\varepsilon_{i,k} \tag{2.28}$$

where  $X_{i,k}$  denotes the  $i^{th}$  variable in the set X of the  $k^{th}$  gate.  $\varepsilon_{i,k}$  is a unique and independent noise symbol associated with that variable and  $\varepsilon_{i,k} \sim N(0,1)$ .

#### 2. Symbolical Calculation and Propagation

For each input-vector, the program traverses the whole circuit from the inputs to the outputs in the *forward* direction, such that the voltage of each edge in the graph is annotated with a calculation result expressed in AA form. However, symbolic propagation would cause a range explosion when encountering special functions such as *exponential* and/or *power functions*, resulting in difficulty to maintain AA propagation. We solve this problem by approximating (2.24) linearly using a first order Taylor expansion, so that the output voltage of each gate is expressed as

$$V_{out} = V_{out,0} + \sum_{\forall i} \left[ \partial f / \partial V_{in\_i} \right]_0 \Delta V_{in\_i} + \sum_{\forall i} \left[ \partial f / \partial X_i \right]_0 \Delta X_i$$

(2.29)

where  $V_{out,0}$ ,  $[\partial f/\partial V_{in..i}]_0$ ,  $[\partial f/\partial X_i]_0$  are the values calculated at the *central values* of the variables in the  $V_{in}$  and X sets of that gate.

### 3. Output Noise Margin Estimation

## 2.4. STATISTICAL NOISE MARGIN ESTIMATION FOR SUB-THRESHOLD COMBINATIONAL CIRCUITS

Table 2.2: Estimated statistical noise margin from Cadence Spectre Monte-Carlo DC simulation and the new approach

| Bench | Sim   | 150mV    |          | 180mV    |          | 210mV      |          | RunningTime  |

|-------|-------|----------|----------|----------|----------|------------|----------|--------------|

| -mark | Silli | $V_{OL}$ | $V_{OH}$ | $V_{OL}$ | $V_{OH}$ | $V_{OL}$ ' | $V_{OH}$ | /InputVector |

| C880  | MC    | 2.4%     | 84.6%    | 1.2%     | 92.2%    | 0.3%       | 96.2%    | > 10 hours   |

| C000  | New   | 2.9%     | 85.4%    | 1.1%     | 93.7%    | 0.4%       | 97.4%    | 0.08sec      |

After calculation and propagation, the voltage at the output (s) of a circuit can be expressed as (2.30),

$$V_{output} = V_{output,0} + \sum_{\forall (i,k)} \eta_{i,k} \varepsilon_{i,k}$$

(2.30)

Recall that each  $\varepsilon_{i,k}$  in (2.30) is an independent *noise symbol* and  $\varepsilon_{i,k} \sim N(0,1)$ .  $\eta_{i,k}$  is the corresponding accumulated coefficient. According to probability theory, the sum of these independent normally distributed terms is also normally distributed, so we can have

$$V_{output} \sim N(V_{output,0}, \sum_{\forall (i,k)} \eta_{i,k}^2)$$

(2.31)

Therefore, the mean value and variance of the output voltage can be easily obtained such that the statistical output noise margin can be estimated.

### 2.4.3 Experimental results

To prove the strength of our methodology, experiments have been conducted using the ISCAS combinational benchmark circuits. All simulations were performed for a CMOS 65nm Standard  $V_T$  (S $V_T$ ) technology from NXP. The benchmark circuits are synthesized to netlists with minimum size logic gates. We do not use gates that have more than 4 stacked transistors or 4 paralleled transistors, as sub-threshold design seldom exploits these gates due to severe robustness degradation [please refer to Chapter 3]. Our new approach was implemented in C++, and ran on a PC with Intel Pentium 1.86GHz and 1G RAM. To validate the new model, we performed transistor-level DC Monte-Carlo simulations for benchmark C880, and compared the results with those

from our approach. The MC simulation was carried out with Cadence Spectre Simulator running on a HP UNIX server. The simulations ran for 2000 trials. Table 2.2 gives the simulation results. Here,  $V_{OL}$ ' ( $V_{OH}$ ') is defined as the maximum (minimum) value among all the outputs'  $3\sigma$  values of  $V_{OL}$  ( $V_{OH}$ ), normalized w.r.t.  $V_{DD}$ . As shown, our approach can predict the output noise margin with less than 1.5% deviation. However, the transistor-level DC MC simulation for benchmark C880 required more than 10 hours running time for one input vector, while the new approach only needed about 0.1 seconds! Our methodology reduces the design time for the output noise margin of a circuit by several orders of magnitude.

Table 2.3: Estimated statistical noise margins as % of  $V_{\rm DD}$

| Bench |           | 150mV    |            | 180        | 180mV    |          | mV       | RunningTime |  |

|-------|-----------|----------|------------|------------|----------|----------|----------|-------------|--|

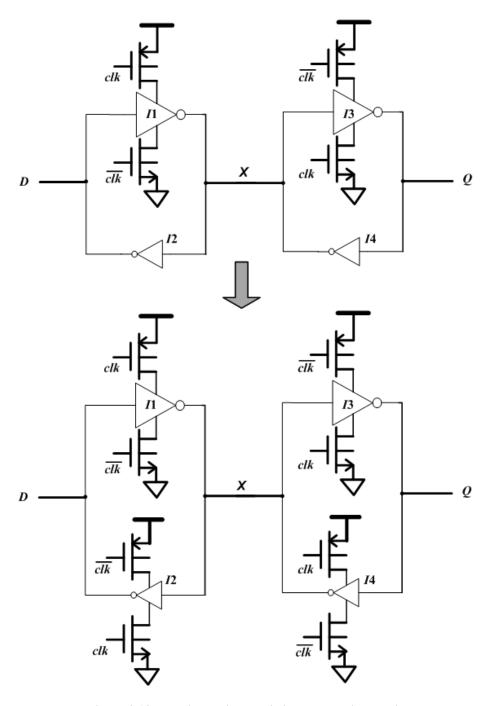

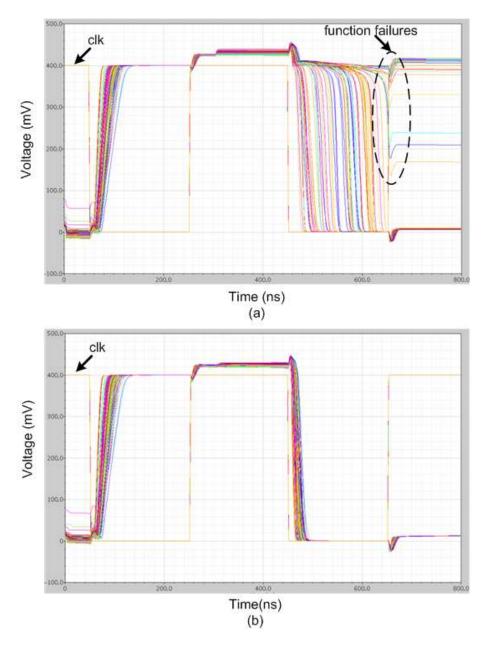

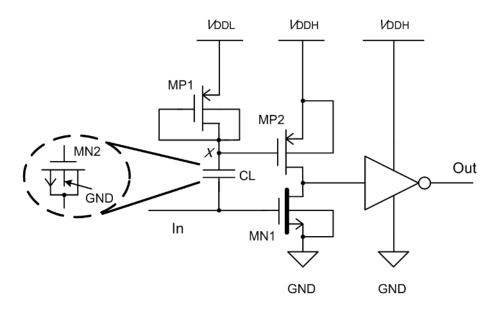

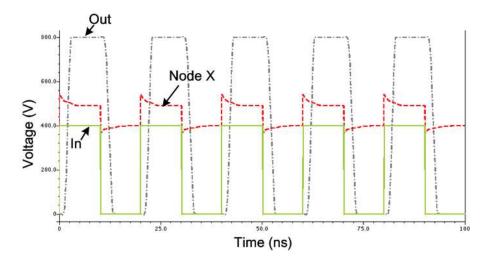

| -mark |           | $V_{OL}$ | $V_{OH}$ ' | $V_{OL}$ ' | $V_{OH}$ | $V_{OL}$ | $V_{OH}$ | (sec)       |  |