## OPTICAL TOKENS IN MANY-CORE PROCESSORS

by

Dana M. Vantrease

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctorate of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN-MADISON

2010

## **ACKNOWLEDGMENTS**

This thesis would not have been possible without the support of my family, friends, and colleagues over the past eight years.

I am grateful to my advisor, Mikko Lipasti, for being a great advisor, teacher, and role model. His wisdom, guidance, and weekly doses of encouragement have been crucial to maintaining my research momentum. Through example, he has taught me the value of balancing work and life (a skill that has undoubtedly kept me sane). I am also thankful to my thesis committee members for their objective feedback: Professor Mark Hill, Professor David Wood, Professor Leon McCaughan, and Professor Parameswaran Ramanathan. My research and presentation skills have improved over the years thanks to Mark Hill's critiques, which are some of the toughest, most concise, and best critiques I have ever received. Also, I admire David Wood, for his youthful enthusiasm and great wisdom.

I would like to thank my team of collaborators at Hewlett-Packard Laboratories for giving my research real traction. I would especially like to thank: My mentor, Nathan Binkert, who guided me, taught me some valuable coding skills, and brought me much-needed fro-yo during paper deadlines; Marco Fiorentino, for patiently explaining the physics of nanophotonics; Professor Al Davis, for propping me up and believing that I am one "rocking dudette;" Jung Ho Ahn and Matteo Monchiero, for simulator help; Nidhi Agarwal, for bringing my attention to the internship and lending a sympathetic ear when my pet chicken died; Moray McLaren, for being a wonderful manager; and Norm Jouppi, for giving me the opportunity to work with such a great team.

The friends and colleagues I have met during graduate school have really made the experience rewarding. I would like to thank the many who helped to maintain the UW-architecture community through their efforts in organizing Reading Group, Affiliates, Architecture Lunch, Architecture Seminar, and Architecture Beer. Thanks to all of my lab-mates for making lab a fun (and geeky) place to work, especially to Mitch Hayenga for the shop-talk and for being a fellow fast-talker; to Atif Hashmi and Andy Nere for lending their problem solving skills and mostly avoiding me during rubber band shoot-outs; Erika Gunadi for defense advice; Natalie Enright-Jerger for keeping dibs on me; Gordon Bell for keeping the cluster alive; Jason Cantin for not allowing me to drop out; and Trey Cain for pumping good tunes while burning the midnight oil. I spent my early years in the Computer Sciences building and returned there often. I would like to thank Luke Yen for being my qual study-buddy; Dan Gibson for the enjoyable conversations and a memorable kayaking trip; Matt Allen for great presentation critiques and habanero chili; Yasuko Watanabe and Polina Dudnik for showing the world how awesome female architects can be; Mike Marty for making conferences

more fun (+Google Wave Invite #1); Phillip Wells for being a great Reading Group moderator (+Google Wave Invite #2); Jayaram Bobba for helping with Graduates Anonymous; All of my CS polar plunge teams for keeping me cold in February.

Last but not least, I thank Kenley Maddux, for sticking with me and giving me his unwaivering support. I also thank my ma, pa, and siblings for believing in me and so much more.

# **TABLE OF CONTENTS**

|    |                   |                                                                                                                                                            | Page                                      |

|----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| LI | ST O              | OF TABLES                                                                                                                                                  | vi                                        |

| LI | ST O              | OF FIGURES                                                                                                                                                 | vii                                       |

| Al | BSTR              | ACT                                                                                                                                                        | ix                                        |

| 1  | Intr              | roduction                                                                                                                                                  | 1                                         |

|    | 1.1               | The Many-Core Era                                                                                                                                          | 1<br>1<br>2<br>2<br>3<br>3<br>4<br>4<br>4 |

|    | 1.3               | 1.2.1.3 Atomic Coherence: Photonic Assisted Decoupling of Races from Coherence  1.2.2 Relation to Previously Published Work  Dissertation Structure        | 5<br>5<br>6                               |

| 2  | Bac               | ekground                                                                                                                                                   | 7                                         |

|    | 2.1               | Global Communication Technology in Many-Core Processors  2.1.1 Electricity in Copper Wires                                                                 | 7<br>7<br>8<br>8<br>9                     |

|    | 2.2<br>2.3<br>2.4 | Silicon Photonics  2.2.1 Devices  2.2.2 Challenges  2.2.2.1 Device Considerations  2.2.2.2 System Considerations  Alternative Global Technologies  Summary | 10<br>10<br>13<br>13<br>15<br>16<br>17    |

| 3  | Rela              | ated Work                                                                                                                                                  | 18                                        |

|    | 3.1               | Optical Interconnect Control                                                                                                                               |                                           |

|   |            |                                              | Page       |

|---|------------|----------------------------------------------|------------|

|   |            | 3.1.1.1 Topology Approaches                  | 20         |

|   |            | 3.1.1.2 Access Policies                      | 20         |

|   |            | 3.1.2 Flow Control                           | 22         |

|   |            | 3.1.3 Fairness                               | 22         |

|   | 3.2        | Cache Coherence Complexity                   | 23         |

|   |            | 3.2.1 Cache Coherence                        | 23         |

|   |            | 3.2.2 Evolution of Protocol Complexity       | 24         |

|   |            | 3.2.3 Ordering Techniques                    | 24         |

|   |            | 3.2.4 Protocol Verification Methods          | 28         |

|   |            |                                              |            |

| 4 | Me         | thodology                                    | 29         |

|   | 4.1        | Optical Assumptions                          | 29         |

|   |            | 4.1.1 Area                                   | 29         |

|   |            | 4.1.2 Latency                                | 29         |

|   |            | 4.1.3 Power                                  | 29         |

|   | 4.2        | Simulation                                   | 31         |

|   |            | 4.2.1 Workloads                              | 31         |

|   |            | 4.2.1.1 Descriptions of Workloads            | 31         |

|   |            | 4.2.1.2 Running of Workloads                 | 31         |

|   |            | 4.2.2 System Setup                           | 33         |

|   |            | 4.2.2.1 Components                           | 33         |

|   |            | 4.2.2.2 Configuration                        | 38         |

|   | 4.3        | Summary                                      | 40         |

| _ | 0          |                                              | 41         |

| 5 | Opi        | tical Tokens                                 | 41         |

|   | 5.1        | Overview                                     | 41         |

|   | 5.2        | Token Inject and Detect                      | 44         |

|   | 5.3        | Fixed-Injector and Variable-Injector Systems | 44         |

|   | 5.4        | Token Clocking and Refresh                   | 45         |

|   | 5.5        | Latency                                      | 45         |

|   | 5.6        | Power                                        | 47         |

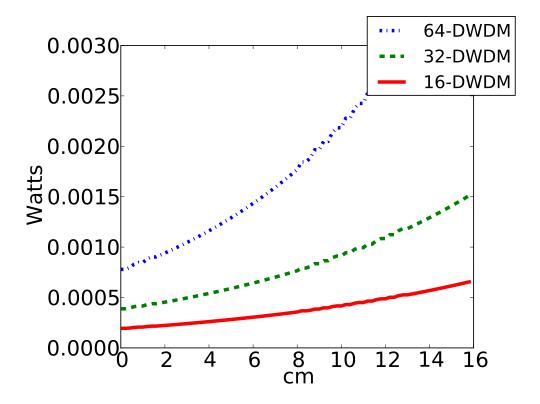

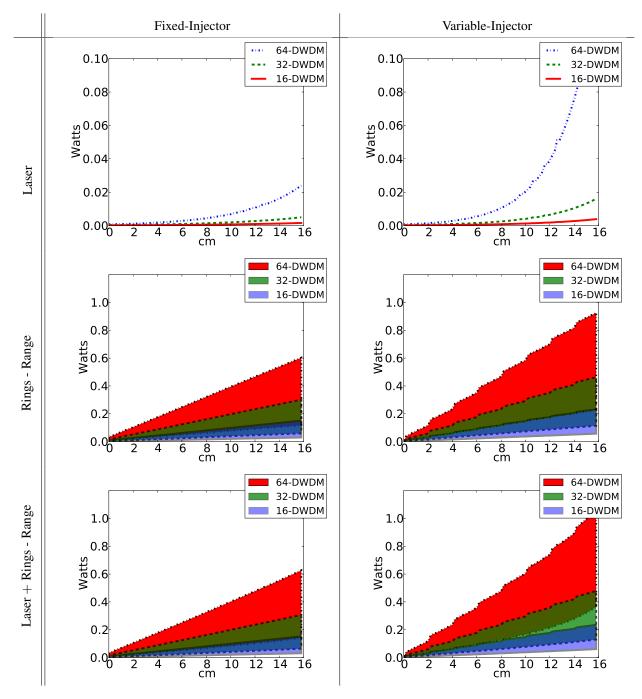

|   |            | 5.6.1 Laser Power                            | 47         |

|   |            | 5.6.2 Ring Power                             | 50         |

|   |            | 5.6.3 Laser and Ring Power                   | 52         |

|   | 5.7        | Comparison To Traditional Token Rings        | 52         |

|   | 5.8        | Summary                                      | 52         |

| 6 | Pho        | otonic Interconnect Control                  | 54         |

|   | <i>(</i> 1 | Photonia Control                             | <i>5</i> 1 |

|   | 6.1        | Photonic Control                             | 54         |

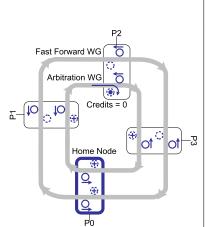

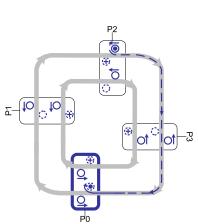

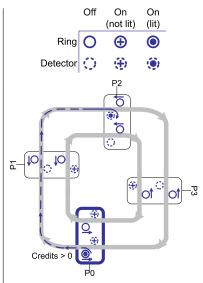

|   |            | 6.1.1 Arbitration                            | 56         |

|   |            | 6.1.1.1 Token Channel                        | 56         |

|   |            | 6.1.1.2 Token Slot                           | 56         |

|   |            | 6.1.2 Flow Control (FC)                      | 58         |

|   |            | 6.1.3 Fairness                               | 59         |

|   |            | 6 1 3 1 Fair Token Channel                   | 59         |

|    |       |                                                            | Page  |

|----|-------|------------------------------------------------------------|-------|

|    |       | 6.1.3.2 Fair Token Slot                                    | . 61  |

|    |       | 6.1.4 Multiple Channel Control                             |       |

|    | 6.2   | Evaluation                                                 |       |

|    |       | 6.2.1 Experimental Setup                                   |       |

|    |       | 6.2.2 Results                                              |       |

|    |       | 6.2.2.1 Performance                                        | . 67  |

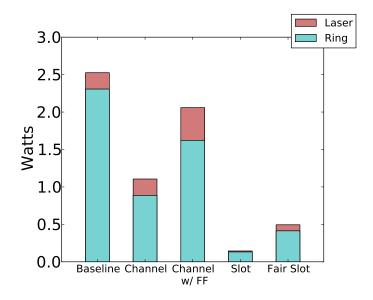

|    |       | 6.2.2.2 Power                                              | . 69  |

|    | 6.3   | Discussion                                                 | . 74  |

|    |       | 6.3.1 Timing Assumptions                                   | . 74  |

|    |       | 6.3.2 Supporting Prioritization                            | . 76  |

|    | 6.4   | Summary                                                    | . 76  |

| 7  | Ato   | nic Coherence                                              | . 77  |

|    | 7.1   | Introduction                                               | . 77  |

|    | 7.1   | Atomic Coherence                                           |       |

|    | 1.2   | 7.2.1 Atomic Coherence Definition and Discussion           |       |

|    |       | 7.2.2 Enforcing Atomicity with Mutexes                     |       |

|    |       | 7.2.3 Complexity Implications of Atomic Coherence          |       |

|    |       | 7.2.4 Performance Implications of Atomic Coherence         |       |

|    |       | 7.2.4.1 Performance Pitfalls                               |       |

|    |       | 7.2.4.2 Performance Opportunities                          |       |

|    | 7.3   | A Photonic Atomic Substrate                                |       |

|    | 7.4   | Evaluation                                                 |       |

|    |       | 7.4.1 Experimental Setup                                   |       |

|    |       | 7.4.2 Results                                              |       |

|    |       | 7.4.2.1 Complexity                                         |       |

|    |       | 7.4.2.2 Performance                                        | . 91  |

|    |       | 7.4.2.3 Complexity-Effective Performance                   | . 94  |

|    |       | 7.4.2.4 Power                                              |       |

|    |       | 7.4.2.5 Sensitivity Analysis                               | . 94  |

|    |       | 7.4.2.6 Performance Optimization Results                   |       |

|    | 7.5   | Discussion                                                 | . 97  |

|    |       | 7.5.1 Other Opportunities for Aggressive Coherence         | . 97  |

|    |       | 7.5.2 Relation to Token Coherence                          | . 97  |

|    |       | 7.5.3 Data-Race-Free                                       | . 99  |

|    |       | 7.5.4 Memory Consistency Implications                      | . 99  |

|    | 7.6   | Summary                                                    | . 100 |

| 8  | Sun   | nary and Reflections                                       | . 101 |

|    | 8.1   | Summary                                                    | . 101 |

|    | 8.2   | Reflections                                                |       |

|    | 0.2   | 8.2.1 Speculation Freedom                                  |       |

|    |       | 8.2.2 Applicability of Contributions to Other Technologies |       |

| LI | IST O | REFERENCES                                                 | . 104 |

# LIST OF TABLES

| Table |                                     |      | Page |  |

|-------|-------------------------------------|------|------|--|

| 2.1   | Definition of Optical Symbols       | . 13 | 3    |  |

| 3.1   | Cache Coherence Complexity Taxonomy | . 2  | 7    |  |

| 4.1   | Optical Device Power Consumption    | . 30 | 0    |  |

| 4.2   | Benchmarks                          | . 34 | 4    |  |

| 4.3   | System Configurations               | . 38 | 8    |  |

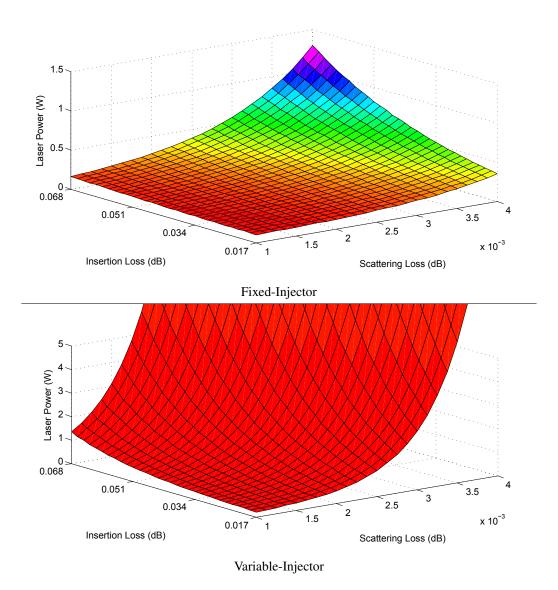

| 5.1   | Ring Resonator Losses               | . 50 | 0    |  |

# LIST OF FIGURES

| Figu | ure .                                                                     | Page |

|------|---------------------------------------------------------------------------|------|

| 1.1  | Optical Token Overview                                                    | . 4  |

| 1.2  | Atomic Coherence Overview                                                 | . 5  |

| 2.1  | Approaches to On-Chip Photonic Integration                                | . 9  |

| 2.2  | A Ring Resonator's Interaction with Light                                 | . 10 |

| 2.3  | Nanophotonic Building Blocks                                              | . 11 |

| 2.4  | 3D Stacking                                                               | . 16 |

| 3.1  | Optical Interconnect Topologies                                           | . 19 |

| 3.2  | Protocol Finite State Machines                                            | . 25 |

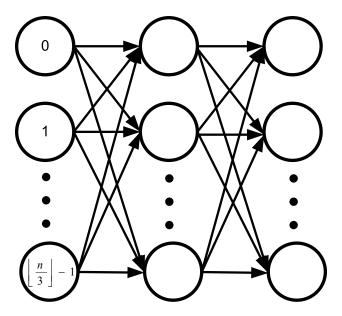

| 4.1  | Neural Network Example                                                    | . 32 |

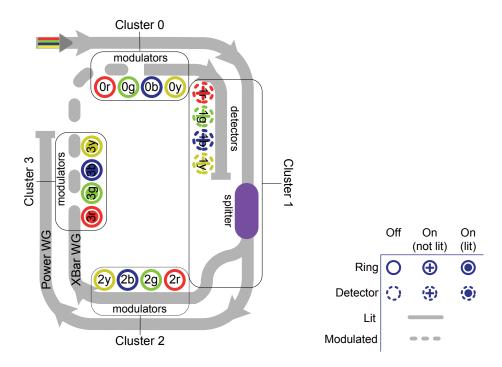

| 4.2  | Four Wavelength Corona-like Data Channel                                  | . 35 |

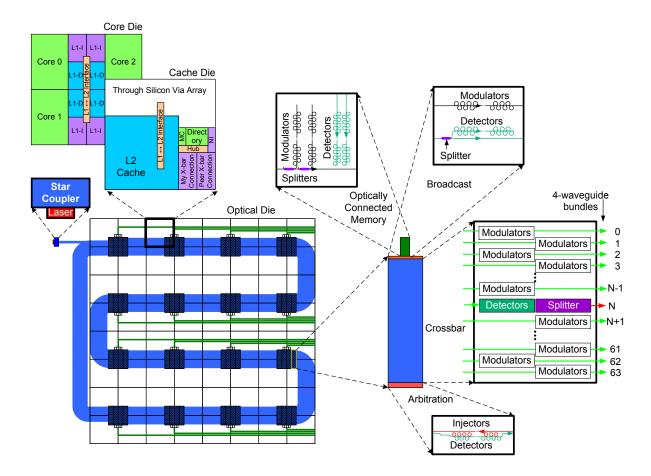

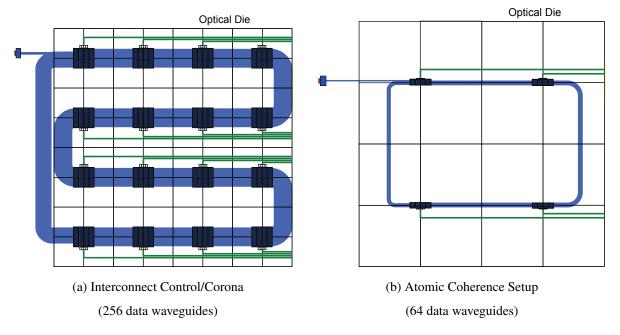

| 4.3  | Corona's Interconnect Layout                                              | . 36 |

| 4.4  | Data Interconnects Used in Evaluation                                     | . 39 |

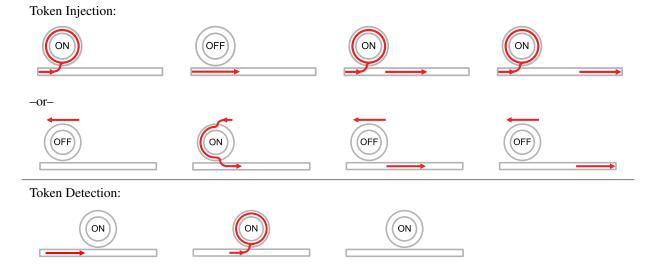

| 5.1  | Optical Token Injection and Detection                                     | . 42 |

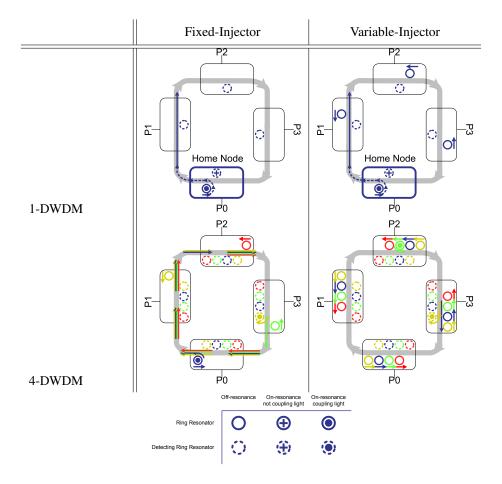

| 5.2  | Fixed-Injector And Variable-Injector Token Systems                        | . 43 |

| 5.3  | Optical Token Dateline                                                    | . 46 |

| 5.4  | Optical Token Scalability                                                 | . 46 |

| 5.5  | Laser Power as Function of Distance on a Straight Waveguide with No Rings | . 48 |

| 5.6  | Token Power Results                                                       | . 49 |

| 5.7  | Laser Power Sensitivity to Scattering and Insertion Losses                | . 51 |

| 5.8  | Traditional Token Ring Vs Optical Tokens                                  | . 53 |

| 6.1  | Multiple Writer Single Reader Topology                                    | . 55 |

| Figur | re                                                                      | Page |

|-------|-------------------------------------------------------------------------|------|

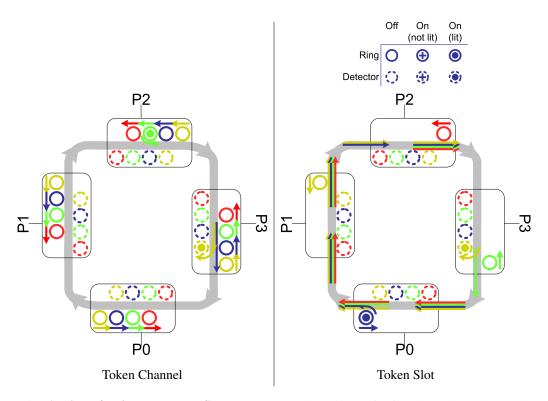

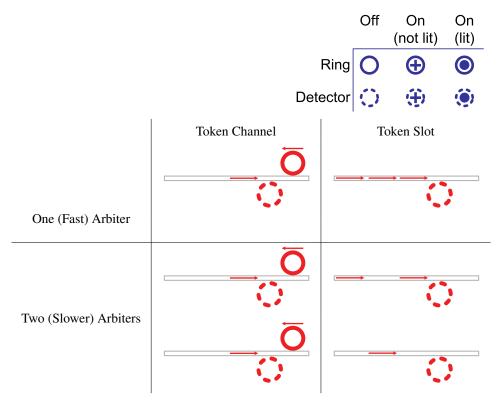

| 6.2   | Token Channel                                                           | 57   |

| 6.3   | Token Slot                                                              | 57   |

| 6.4   | Token Channel with Fast Forwarding                                      | 60   |

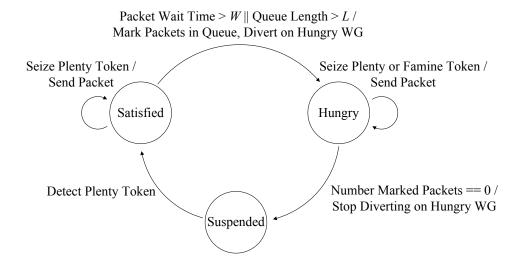

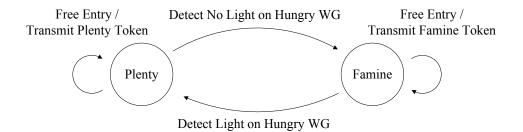

| 6.5   | Fair Slot Finite State Machine                                          | 62   |

| 6.6   | Fair Slot Implementation                                                | 63   |

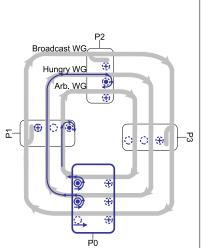

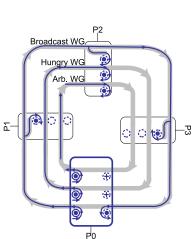

| 6.7   | Arbiters for 4-channel MWSR                                             | 66   |

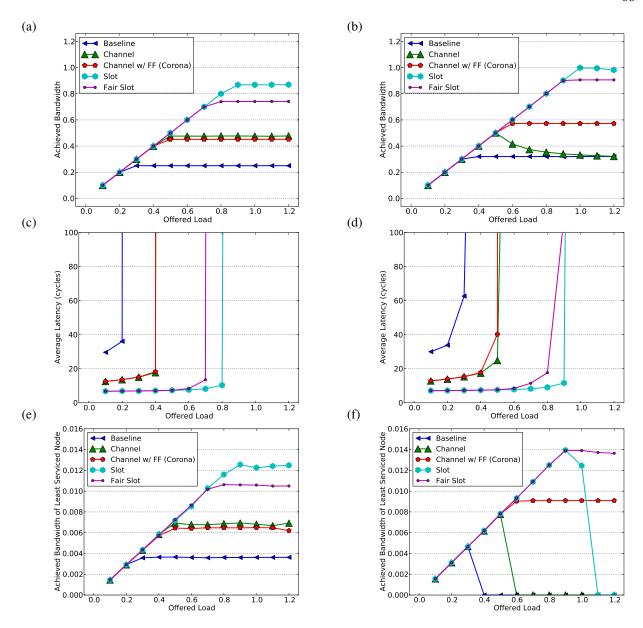

| 6.8   | Synthetic Workloads: Bandwidth, Latency, and Worst Service for Arbiters | 68   |

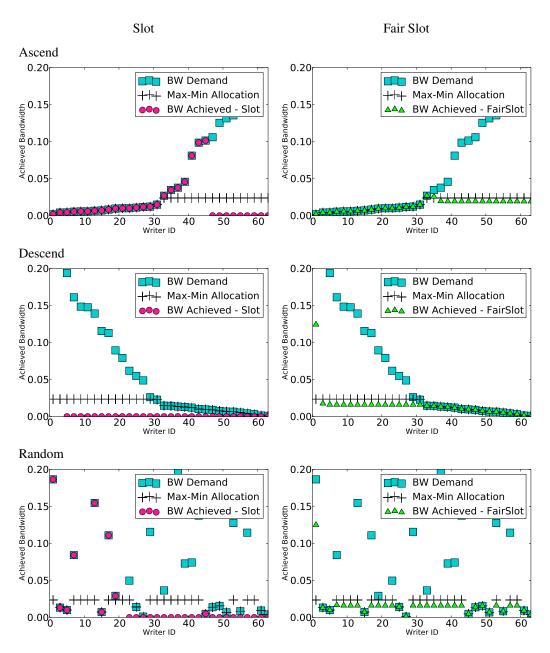

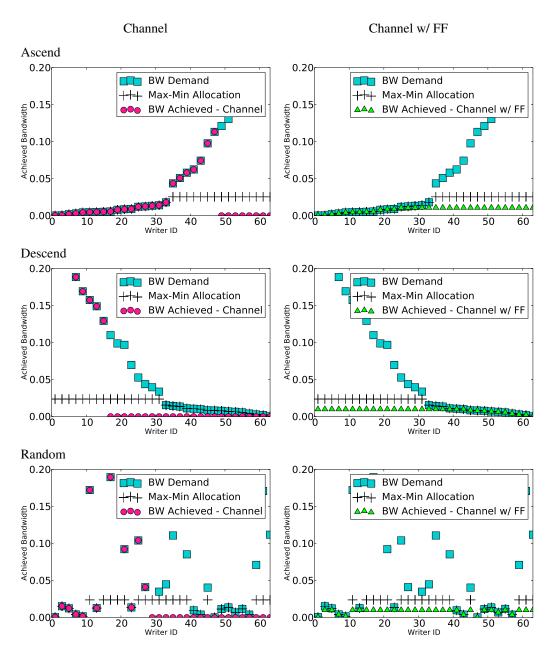

| 6.9   | Max-Min Token Slot Results                                              | 70   |

| 6.10  | Max-Min Token Channel Results                                           | 71   |

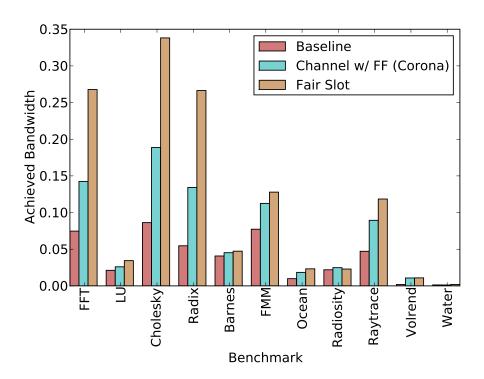

| 6.11  | SPLASH-2 Workloads: Achieved Bandwidth for Arbiters                     | 72   |

| 6.12  | Arbiter Power                                                           | 73   |

| 6.13  | Layout of Multiple Arbiters                                             | 75   |

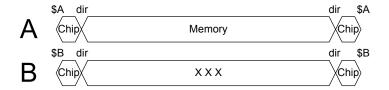

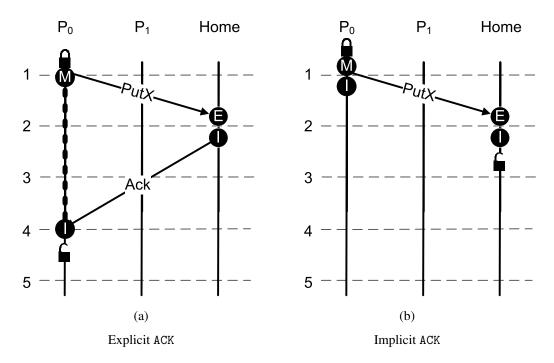

| 7.1   | SGI-Origin Writeback Race                                               | 80   |

| 7.2   | Parallel and Serial Miss Timing Diagrams                                | 83   |

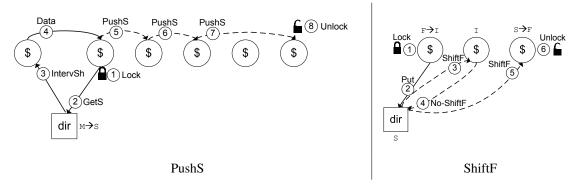

| 7.3   | PushS and ShiftF Overview                                               | 84   |

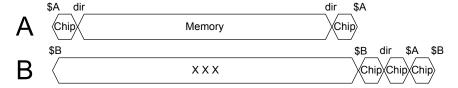

| 7.4   | Implicit Acknowledgements in Atomic Coherence                           | 86   |

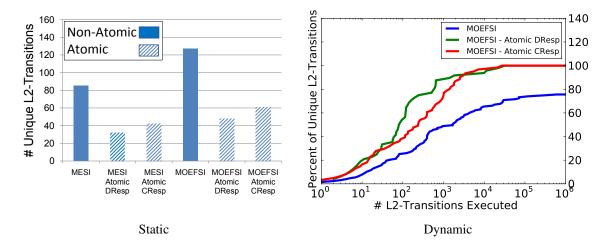

| 7.5   | Complexity analysis for Atomic Coherence                                | 89   |

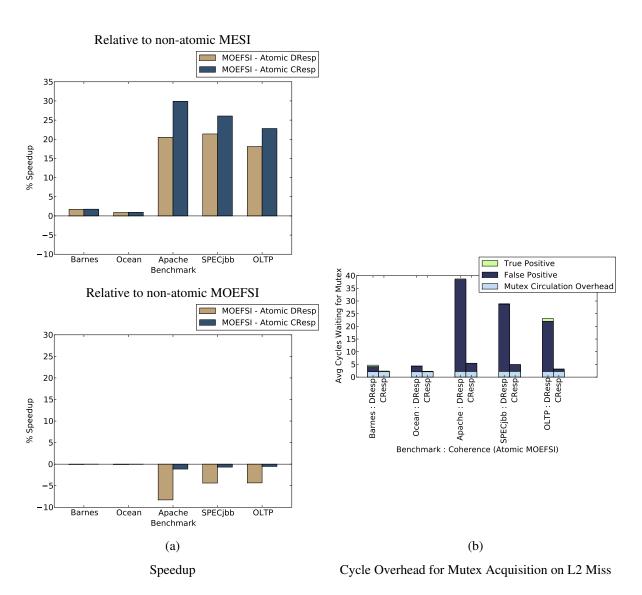

| 7.6   | Performance and Overhead for Atomic Coherence                           | 92   |

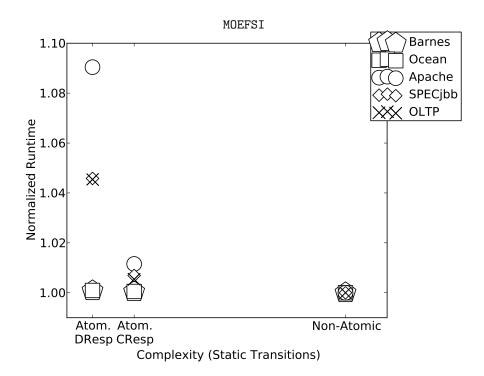

| 7.7   | Complexity Vs Normalized Runtime                                        | 93   |

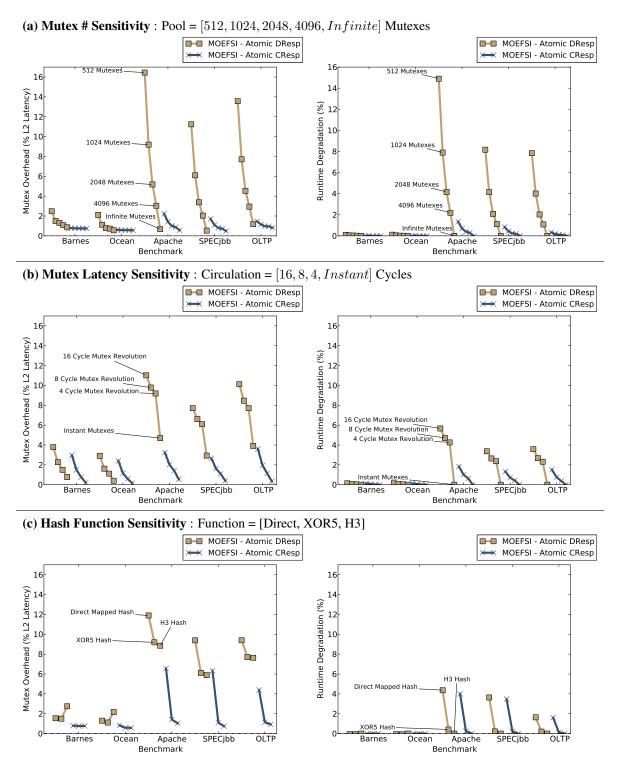

| 7.8   | Sensitivity Study for Atomic Coherence                                  | 95   |

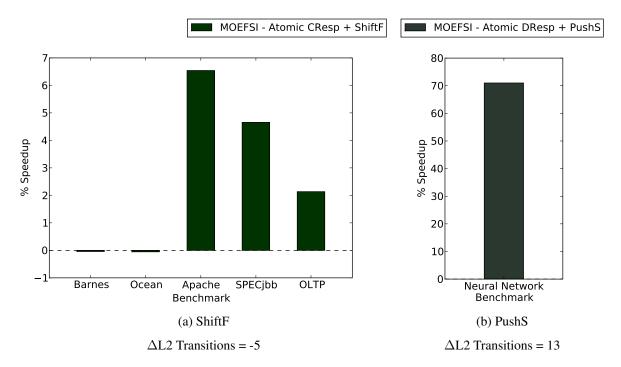

| 7.9   | Atomic Coherence Optimizations' Speedup                                 | 96   |

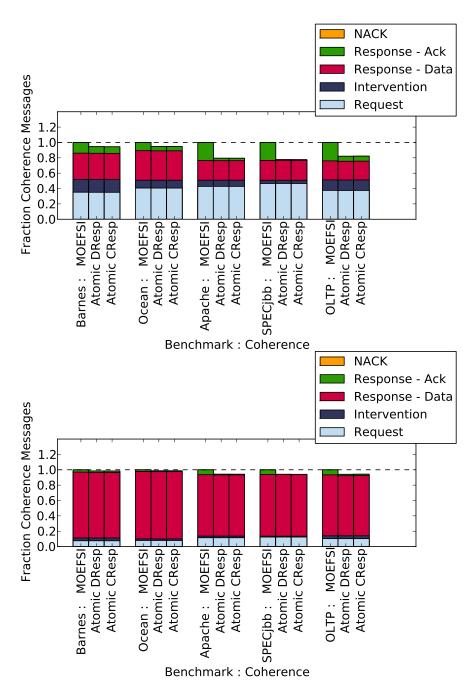

| 7.10  | Atomic Coherence Traffic Breakdown for MOEFSI                           | 98   |

## **ABSTRACT**

As core count grows, demand for high-bandwidth, low-latency on-chip interconnects increases. While fast transmission of raw bits is one necessary property of future high performance interconnects, it is not sufficient; interconnects must also manage coordination of shared entities, such as resources and data. This thesis uses nanophotonics to perform many-core coordination that enhances system performance and decreases complexity.

Many have advocated silicon-based nanophotonics for future many-core data communication. It is my goal to show its applicability to other many-core needs, namely many-core coordination. The same optical properties that benefit data communication may benefit many-core coordination: low cross-chip latencies, high bandwidth, and low power consumption. However, to take full advantage of these benefits, it will be necessary to accommodate the technology's limitations. One limiter is repeater inefficiency. Converting an optical signal to and from the electrical domain is relatively slow and also power-inefficient. Thus, it is in the interest of performance to keep the signal in optical form from source to destination.

I propose *optical tokens* as a way to manage coordination while coping with repeater inefficiencies. In most cases, our optical tokens can be passed from any interested party to any other interested party with no repeats, thus allowing for flexible communication at speed-of-light propagation. When a token is viewed as usage rights for a resource, it becomes a fast traveling mutex.

I show two applications of optical tokens. The first application employs optical tokens in the arbiters of an optical data interconnect. The data interconnect is fast and requires fast arbitration for high utilization. Also, like the optical tokens, it avoids repeating data transmissions. These complimentary repeater-less designs allow a token to maintain pace with its associated bandwidth allocation and achieve very high utilization. I further extend the proposal to support flow control and fairness.

The second application employs optical tokens to address cache coherence protocol complexity. Cache coherence protocol complexity arises from the presence of concurrency races, which though rare, must be detected and resolved. My proposal, called Atomic Coherence, simplifies protocols by serializing potential races before they issue to the interconnect. Without races, sophisticated protocols are substantially easier to design, debug, and validate. Race serialization comes at some cost to performance, but is kept to a minimum with low-latency optical tokens.

## Chapter 1

## Introduction

The multi-core era has arrived. Duo- and quad- core systems are commonplace. Researchers are bracing for tens, even hundreds, of cores on a single chip [1]. For a long time we thought in terms of housing a single core on a chip; now a chip can house an entire neighborhood of interconnected cores and memories. With this new landscape, we must carefully consider interaction between all parts to achieve a balanced high-performance system.

The chip's parts work together to perform three main duties: computation, communication, and storage. In theory, gains in computational potential are governed by Moore's law [2]. In reality, these gains can only be realized with a communication system capable of keeping the computational units fed with data. Unfortunately, Moore's law does not directly improve communication, making communication the bottleneck in systems of multiple cores.

Thus, to continue reaping the benefit's of Moore's law, our future processors need to support powerful computation and powerful communication. Part of our pursuit must be to improve the communication technology, so that raw data can travel from source to destination more quickly and in larger volume. We must also pursue strategies in effective use of the technology, so that we may achieve high channel utilization and efficiently meet cache coherency and memory consistency contracts.

Finally, we cannot forget that parallel software will be what ultimately unlocks the performance of future many-core processors. So far, the burden of parallelizing software has fallen largely on the programmer, who must reason about difficult things, such as finding parallelism, non-determinism, and parallel performance tuning. Future hardware must ease the programmer's job.

#### 1.1 The Many-Core Era

## 1.1.1 Many-Core Computation

Since the early 1960s, Moore's law has driven processor performance by doubling the maximum number of on-chip transistors every 18 months. During much of this time, chip architects efficiently translated their increased transistor budgets into single-threaded performance. However, the time came that larger budgets resulted in diminishing returns; the architects simply had more transistors than a single thread could use. With little progress being made on single-threaded performance, architects turned to multi-threaded performance.

Taking a divide and conquer approach to the plethora of transistors, monolithic single-core designs began to be replaced with multi-core designs (2-8 cores) [3, 4]. Now, multi-core has started to give way to many-core (8+ cores) [5, 6]. These many-core designs have simpler cores than their predecessors, choosing to emphasize higher aggregate throughput over any single core's throughput [7, 8]. Simpler cores also translate to lower aggregate power. Only transistors that can efficiently benefit performance are built into a core; many architecturally advanced techniques, like out-of-order issue, speculative execution, and large instruction windows, have been stripped away.

Simply organizing transistors into simple cores is not enough to realize the performance potential of Moore's law. Arguably, the biggest problem facing many-core processors is usability. Programs must be written that can harness the parallelism. Unfortunately, programming parallel applications is hard to reason about and even harder to optimize. Fortunately, many people across systems, compilers, and architecture are working hard on this problem. The other major problem facing many-cores is how to connect the cores to provide efficient communication. We discuss the needs of many-core communication next.

### 1.1.2 Many-Core Communication

#### 1.1.2.1 Communication Uses

In many-cores, communication is used for data transfer, cache coherence, and synchronization.

**Data Transfer.** Communication is necessary to transfer data between cores.

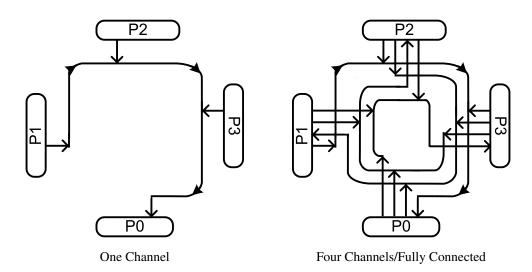

The many-core data interconnect, or Network on Chip (NoC), must meet the needs of its many simple (or light-weight) cores. These new light-weight cores have different needs than their heavy-weight predecessors. Regarding bandwidth, a light-weight core requires less memory bandwidth; it executes less aggressively and generates requests less frequently. Regarding latency, a light-weight core is more latency sensitive; it is unable to overlap as many (if any) misses and will expose the miss serialization latency. A light-weight core, then, requires the interconnect to provide data with low latency but also at low bandwidth. However, when assessed as a system, the bandwidth supply must be increased to satisfy all cores. In the end, although demands of a single core have decreased, the aggregate demands on the interconnect have not. Future many-cores will require an interconnect with high bandwidth and low latency.

Caches can help these demands by keeping copies of data near the cores. When the data is not cached locally, it must be retrieved from another on-chip cache or from memory. Retrieving from another cache is likely faster than retrieving from memory, but some extra latency may be necessary if the system enforces cache coherence. Cache coherence provides a coherent flat view of memory in the presence of replicated data.

**Cache Coherence** Communication also serves cache coherence protocols, which manage replicated data to maintain a consistent view of memory.

Coherence approaches fall into two camps: snoopy and directory. Generally speaking, directory protocols are viewed as the scalable solution for many-cores while snoopy protocols serve smaller core-counts. In a directory protocol, each miss visits the directory. The directory supplies information about the cached state of the block, such as its state and its sharing set. If the directory allows, there can be as many sharers as caches. To track the sharers precisely incurs an overhead that increases proportionally with the number of caches. Furthermore, when the number of sharers is large (as large as the number of caches), either invalidating or updating these sharers can be quite costly for latency and bandwidth. Addressing these overheads is necessary if future many-cores are expected to provide cache coherence.

**Synchronization** Finally, in a system of large scale concurrency, communication can help to synchronize coordination between two or more entities. Program threads synchronize executions with barriers or locks. Hardware synchronizes for ordering at memory fences and for arbitrating shared resources.

In many-core systems, synchronization needs to scale to many participants. Many-cores considering hardware synchronization methods can take a lesson from Symmetric Multi-processors (SMPs), where dedicated hardware barriers have been around for a long time [9, 10, 11]. Hardware barriers can be quite heavy weight, as exemplified by Cray's choice to abandon its barrier network between the T3D and T3E [12]. However, we believe that if synchronization methods were more light-weight, they could be used more often, by programmer and hardware alike, to manage massive concurrency.

#### 1.1.2.2 Technology's Effect on Communication Architectures

An interconnect should use the technology at hand to build the best communication network possible. To stay competitive, the interconnect must constantly adapt to changes in technology. For example, global wires have become more costly, in term of latency and power. Interconnects have adapted by replacing global interconnects with short point-to-point interconnects that "route packets not wires" [13]. Communication systems have also adapted by putting an extra emphasis on creating locality [14, 15].

The emergence of a new interconnect technology, like nanophotonics, has different challenges and opportunities than electronics, offering new design exploration. Its benefits, which become pronounced when communicating across distances greater than 20 micrometers [16] have fueled a re-emergence in bus, crossbar, and other global interconnect research [17, 18, 19]. Furthermore, this research aims to show how nanophotonics can allow for low-cost coordination that improves many-core performance and complexity.

#### 1.2 Thesis Contributions

This thesis investigates how nanophotonics can benefit many-core performance through the use of light-weight optical tokens.

#### 1.2.1 Contributions

We contribute *optical tokens* as a way to exploit silicon-based nanophotonic technology for low-latency, low-power, and high-bandwidth mutual exclusion. We also show how optical tokens provide low-latency interconnect arbitration and allow for high-performing simple cache coherence protocols.

## 1.2.1.1 Optical Tokens

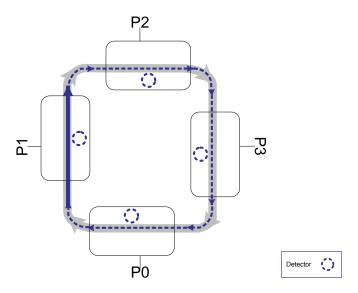

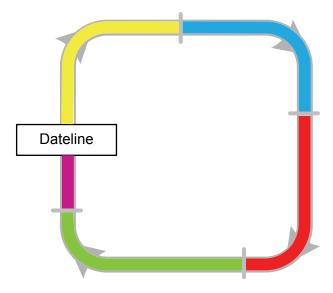

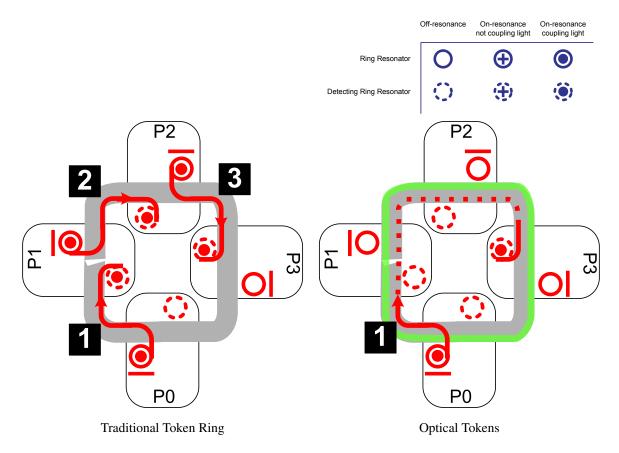

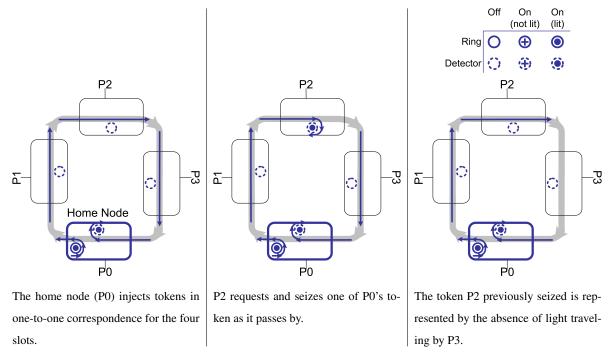

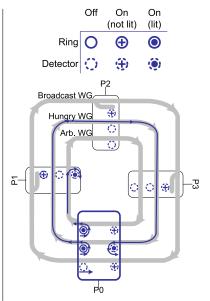

Figure 1.1 **Optical Token Overview.** The token (solid line) circulates around the ring's path (dotted line) without repeat. Any detector may seize the token as it passes.

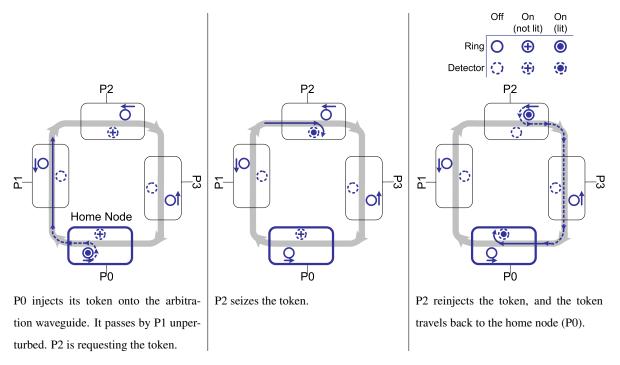

Optical tokens are a low-latency low-power way to enforce mutual exclusion. Each token symbolizes a resource, either physical or virtual. Tokens circulate around a ring-shaped interconnect and are rarely repeated. The circulation of a token is shown in Figure 1.1.

When a node seizes a token, it has exclusive rights to the corresponding resource. When a node releases the token, it releases its rights to the resource.

Because the token is rarely repeated, we can achieve speed-of-light mutual exclusion that scales with the length of the ring instead of the number of nodes.

## 1.2.1.2 Photonic Arbitration, Flow Control, and Fairness

We use optical tokens to provide arbitration for optical data interconnects.

Optical tokens allow for a distributed approach to arbitration that is able to keep pace with the data interconnect. Unlike prior token proposals, our optical tokens are not repeated at non-requesting nodes; only requesting nodes receive the token. This allows for very low-latency arbitration that allows for a full matching of sources to destinations every cycle without pipelining the arbiter.

We further provide simple optical extensions that allow for flow control and enforce fair arbitration. Our arbiters exploit optics to simultaneously achieve low latency, high utilization, and fairness.

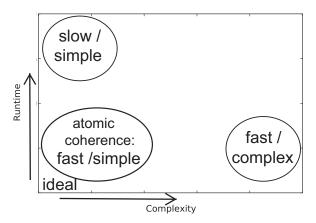

Figure 1.2 **Atomic Coherence Overview.** Complexity Versus Runtime. Most modern protocols fall into the "fast/complex" region while older protocols fall into the "slow/simple" region. The goal of Atomic Coherence is to approach the axis-intersection with "fast/simple" protocols.

#### 1.2.1.3 Atomic Coherence: Photonic Assisted Decoupling of Races from Coherence

We use our optical tokens to resolve races in cache coherence protocols.

Atomic Coherence is a way to reduce the complexity of specifying, designing, and verifying cache coherence protocols. Atomic Coherence decouples race resolution from coherence protocol processing, leading to protocols that only need to follow expected, mostly sequential paths to satisfy requests for coherence permissions and data. This eliminates all unexpected, complex, and difficult-to-verify race transitions from the protocol state machine. By doing so, it aims to strike a balance between complexity and performance, as shown in Figure 1.2.

Atomic Coherence uses address-mapped optical tokens to provide mutual exclusion and atomicity to outstanding coherence transactions. Independent requests are allowed to proceed in parallel, but races are serialized at token acquisition.

## 1.2.2 Relation to Previously Published Work

This thesis encompasses work that has appeared in two conference publications and one workshop publication:

• Corona: System Implications of Emerging Nanophotonic Technology (ISCA '08). We use a Corona-like data interconnect to evaluate our work in Section 6 and Section 7. The Corona paper was written during an internship I had at Hewlett-Packard Labs and was co-authored by Robert Schreiber, Matteo Monchiero, Moray

McLaren, Norman P. Jouppi, Marco Fiorentino, Al Davis, Nathan Binkert, Raymond G. Beausoleil, and Jung Ho Ahn.

- Light Speed Arbitration and Flow Control for Nanophotonic Interconnects (MICRO '09). This thesis presents the findings of this MICRO paper. It also presents solutions for pipelining and prioritizing arbitration. The paper was co-authored by Nathan Binkert, Robert Schreiber, and Mikko Lipasti.

- Nanophotonic Barriers (PICA '09). The fair arbiter we propose in Section 6 uses an optical wired-OR to detect when a node has not been serviced fairly. This wired-OR functionality was inspired by the wired-OR nanophotonic barrier we presented in 2009 at the Workshop on Photonic Interconnects and Computer Architecture (Held in Conjunction MICRO-42). It was co-authored with Nathan Binkert, Al Davis, Mikko H. Lipasti, and Robert Schreiber.

#### 1.3 Dissertation Structure

Chapter 2 presents background information on electrical and nanophotonic technologies as applied to on-chip interconnects. Chapter 3 discusses the prior work related to this thesis. Chapter 4 describes the methods and experimental setups used in our evaluation. Optical Tokens are a recurring theme that are detailed in Chapter 5. Their application to arbitration and cache coherence are presented in Chapters 6 and 7, respectively. Finally, Chapter 8 concludes the thesis.

## **Chapter 2**

## **Background**

This chapter presents an overview of global communication in many-core processors. Global communication is useful to future many-core chips. The number of cycles it takes to get from chip edge to chip edge is growing with each technology generation, making communication latencies highly variable. This non-uniformity means programmers must increasingly pay attention to locality. However, if global communication was fast and plentiful, we could ease programmer burdens. And, as this thesis shows through optical technology, we can also improve system throughput and reduce complexity.

We give an overview of two technologies for global communication, one electrical and one optical in Section 2.1. In Section 2.2, we flush out the details of our technology-of-choice, which uses silicon waveguides and silicon ring resonators.

#### 2.1 Global Communication Technology in Many-Core Processors

## 2.1.1 Electricity in Copper Wires

Copper resistance/capacitance (RC) lines are used in on-chip interconnects. The effective rise time  $\tau$  of a simple RC wire depends on its resistance, capacitance, and length, as characterized by the formula [20]:

$$au pprox R_l C_l l^2$$

$R_l = ext{Resistance per unit length}$   $C_l = ext{Capacitance per unit length}$   $l = ext{length}$

As we approach the many-core era, diminishing feature sizes will put pressure on wires to scale down. Simple three-dimensional wire scaling causes  $R_l$  to grow quadratically, for resistance is inversely proportional to the quadratically shrinking cross-sectional area. Local wires may effectively counteract  $R_l$ 's increase with reduced l. Global wires, on the other hand, span an absolute (or nearly absolute) distance l, allowing the growth of  $R_l$  to dictate performance. Reducing  $R_l$  by inversely scaling wires is possible [21] but is not bandwidth efficient, requires many metal layers, and may cause significant cross talk [22].

Increasing global wire delay may also be combatted with the insertion of repeaters to break up long lines. Repeaters allow delay to grow linearly, rather than quadratically, with distance, but also consume power and area [23]. Thus, a fundamental tradeoff exists, between wire length and repeater count. This tradeoff can be used to determine the optimal repeater size and spacing to achieve a minimum delay [24]. The minimum delay is effectively fixed around 20 ps/mm for global wires (corresponding to 1 mW/mm) through 2017 [25, 26].

Global wires are valuable to inter-core communication, but, to be useful, global wire delay must be kept to a minimum. Designs that try to minimize this latency, by either inversely scaling wires or not scaling them at all, do so with increasing costs. At the end of the day, transistors are scaling, making global wires appear relatively slower, bulkier, and more power-hungry.

## 2.1.2 Light in Free-Space and Silicon Waveguides

Silicon nanophotonics is an interesting alternative for global communication. It has properties useful to global communication, such as low-loss high-speed long-distance dense communication. And, unlike wires, it does not suffer from resistive loss physics.

Optics has traditionally had high termination costs, which, for a long time, could only be amortized over long distances. These costs have begun to decrease, allowing cost-effective communication at smaller distances. Recently, optics has become viable for HPC processor-to-processor interconnects [27]. Intra-processor optics may soon be possible since the successful demonstrations of individual CMOS-friendly nano-scale devices [28, 29]. However, to be ultimately successful, the technology needs to move from laboratory demonstrations to reliable, cheap, and high-yield manufacturables.

#### 2.1.2.1 Background

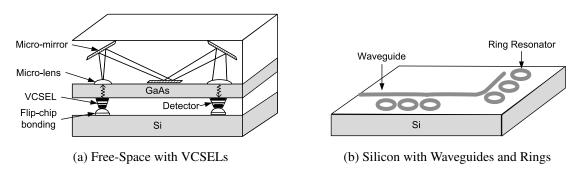

Although the focus of this dissertation is silicon photonics with waveguides and ring resonators, free-space photonics is another approach being pursued in on-chip interconnects [30].

Free-Space optics employs Vertical-Cavity Surface-Emitting Lasers (VCSELs) that are built into a Gallium Arsenide (GaAs) wafer and emit light perpendicular to the chip plane. The light travels in free-space, interacting with lenses and/or mirrors, until it reaches the detector. VCSELs allow for a single optical package, but require non-silicon materials, such as GaAs.

A silicon waveguide-based approach uses an all-silicon process on-chip. Light is routed and manipulated on-chip with silicon waveguides and ring resonators. However, because purely silicon lasers have not been realized (silicon has poor gain due to its indirect band gap [31]), the laser must originate off-chip. Figure 2.1 shows examples of VCSEL and silicon waveguide systems.

Figure 2.1 Approaches to On-Chip Photonic Integration

## 2.1.2.2 Properties

Both VCSEL and ring resonator technologies promise low latency, low loss, and high bit density communication systems.

**Low Latency.** The propagation speed of light (c) in photonic interconnects is simply dependent on the speed of light in the given material as determined by the refractive index of the material:  $c \approx c_0/3$  for silicon and  $c \approx c_0$  for free-space integration.

**Low Losses.** An optical signal can have small losses over long distances. A signal in free-space experiences very little loss. Silicon waveguides experience more losses due to light scattering between the waveguide walls; currently on the order of 2.5 dB/cm [32] but predicted to approach 0.3-1.0 dB/cm [33].

**High Bit Density.** Bit density is the transmission rate divided by transmission medium's width. It depends on the clocking speed, pitch size, and the degree of wavelength multiplexing.

Already, free-space and silicon modulation methods have exceeded 10 GHz speeds [29, 34]. These speeds should be sufficient for designs targeting 2017 [35, 19, 36], because they meet (or exceed) predictions for processor frequency in the next decade [37]. Thus, we can assume 10 GHz speeds for our bit density calculations.

Free-space optics have pitch determined by the  $20\mu m$  device-to-device spacing of the VCSELs [34]. Clocked at 10 GHz, free-space systems have the potential to achieve 0.5 (Gb/sec)/ $\mu m$  density, which is comparable to future electrical interconnects [38].

Silicon waveguide pitch is chosen in a way that is appropriate for the mode size and minimizes cross-talk [25]. A 0.5  $\mu$ m wide waveguide might have a 3.5  $\mu$ m pitch [26]. Clocked at 10 GHz, the bit density is 2.85 (Gb/sec)/ $\mu$ m. Multiplexing multiple wavelengths on this waveguide with Dense Wave Division Multiplexing (DWDM) increases this

Figure 2.2 A Ring Resonator's Interaction with Light. The light is either diverted by the ring (top) or passes by (bottom).

value linearly. Thus, a 64-DWDM estimate would increase this density to 183 (Gb/sec)/ $\mu$ m. For a rough comparison with electronics, a 15 mm repeated wire at 32 nm has densities up to ~1.5 (Gb/sec)/ $\mu$ m [39]..

#### 2.2 Silicon Photonics

To capture the performance potential of optics, we need efficient physical components to transport, modulate, and detect the laser power. Continued advancements in physical design are promising steps towards realizing full photonic integration, but many challenges remain at the device and system level.

In this section we turn our focus to silicon photonics. All of our proposals leverage silicon nanophotonics to quickly transmit optical tokens (see Chapter 5). Alternative on-chip optical options, like VCSEL-based designs, are omitted because of current incompatibility with optical tokens.

#### 2.2.1 Devices

Below I provide functional descriptions of the nanophotonic building blocks. An interconnect consists of a power source, transmission medium, and operating devices. Nanophotonic transmission works by electrically or thermally altering the refractive index of material, which in turn alters the path of the light.

Power Source - Laser. All power comes from an off-chip multi-wavelength Si/III-V evanescent laser, which

uses a silicon-waveguide laser cavity wafer-bonded to a III-V gain medium and has precisely controlled frequency spacings [40]. One advantage of using this type of laser is that if only one of the frequency channels is

servo-locked to an on-chip standard cavity, then all of the other frequency modes will track the controlled mode.

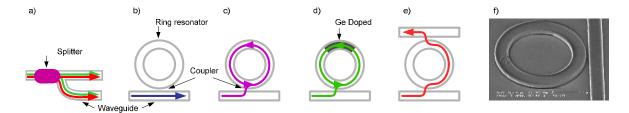

Figure 2.3 **Nanophotonic Building Blocks (Top View).** (a) **Splitter.** The passive splitter splits a fraction of the light, across all wavelengths, and couples it to the bottom waveguide. It is fundamental to distributing power and broadcasting. (b) **Off-resonance Ring.** The ring resonator is coupled to a waveguide through evanescent coupling. Off-resonance wavelengths are transmitted through. (c) **Diverter.** A resonant wavelength is coupled in the on-resonance ring and eventually gets attenuated by losses. (d) **Detector.** A resonant wavelength is coupled in the ring and absorbed by a Ge doped portion of the ring. (e) **Injector.** A resonant wavelength in the input (lower) waveguide is coupled into the ring and out through the output (top) waveguide. (f) SEM image of a 3  $\mu$ m diameter resonator ring. Image courtesy of Qianfan Xu, HP Labs Palo Alto. (Figure appears in [19])

Another advantage is that any temperature change in the environment will cause approximately the same refractive index shift in the laser cavity and the silicon waveguides and resonators that form the DWDM network. This simplifies wavelength locking. A wavelength locking scheme that is robust against temperature changes is one of the key implementation challenges for a DWDM network-on-chip.

- Transmission Medium Waveguides. Waveguides made of crystalline silicon (refractive index ~3.5) and silicon oxide (refractive index ~1.45) contain and route the light. The waveguides are typically  $\approx 0.5 \ \mu m$  in width.

- Operating Devices Splitters, Ring Resonators. The devices described below operate either on all wavelengths in a waveguide or single out a specific wavelength.

**Splitter.** A broadband splitter is a passive device that transfers a fraction of the laser's power, across all wavelengths, between two diverging waveguides as shown in Figure 2.3(a). The unsplit portion is unaffected by the splitter.

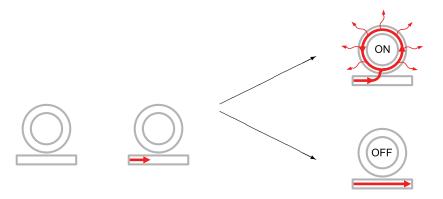

Ring Resonator. A ring resonator, as photographed in Figure 2.3(f), is a switch built from a small ( $\approx 3\mu m$  diameter) ring-shaped waveguide that is wavelength specific. As Figure 2.2 shows, an on-resonance ring resonator removes the majority of the resonant wavelength from the waveguide it is coupled to, while an off-resonance ring resonator removes a negligible amount. The ring is brought into and out of resonance when the ring's electrical charge or temperature are adjusted, which adjusts the ring's index of refraction.

Below I describe how resonators can be configured to perform the tasks of diversion, detection, and injection. Diversion, for instance can be used to modulate data. By quickly bringing the resonator in and out of resonance, the presence of light, or its absence, is transmitted down the waveguide to encode 0s and 1s. The modulated data is wave pipelined, or latch-less. The three flavors of ring resonator are as follows:

- Diverter. When a ring resonator is coupled next to a waveguide, the light circulates within the ring and eventually dissipates through scattering imperfections of the ring (Figure 2.3(c)).

- Detector. When a ring resonator is doped with Germanium (Ge), the wavelength goes through a photoelectric conversion as it circulates in the ring, translating the signal into the electrical domain (Figure 2.3(d)).

- Injector. When an on-resonance ring resonator is coupled between two parallel waveguides, a specific wavelength is injected from one transmission waveguide to the other (Figure 2.3(e)).

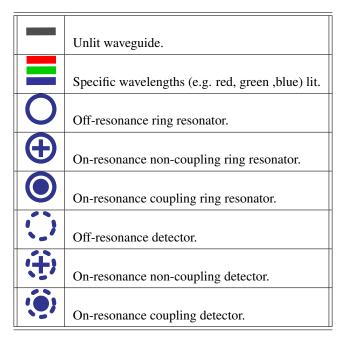

The figures contained in this dissertation follow some conventions that we lay out in Table 2.1 Note that a ring resonator, either germanium doped or not, can be in one of three states:

• A ring resonator can be off-resonance (empty circle).

Table 2.1 Definition of Optical Symbols

- A ring resonator can be on-resonance and *not coupling* any light (because no light is present) (cross in circle).

- A ring resonator can be on-resonance and *coupling* light (because light is present) (filled circle).

#### 2.2.2 Challenges

Despite the great progress silicon nanophotonics has made in recent history, many challenges remain.

#### 2.2.2.1 Device Considerations

**Ring Resonators.** Below we describe ring resonator challenges regarding capacitance, thermal variation, fabrication precision, and area.

- Capacitance. To realize the latency and power benefits of optical transmission, we must efficiently perform

optical-to-electrical (OE) and electrical-to-optical (EO) conversions. A well integrated ring resonator with low

capacitance is important to realize speed while achieving acceptable power consumption [39]. Advancements

in analog amplifiers, positively affected by transistor scaling, can also help improve the conversion efficiency.

- Thermal Sensitivity. A ring resonator's dimensions determine its coupling wavelength. To resonate with a very high extinction ratio, the ring must be an integral number of half-wavelengths in circumference. However, the circumference of the ring can change with temperature by  $\approx 0.11$  nm/K, causing a mismatch in resonance [41].

The mismatch can be dynamically compensated for with local circuitry controlling the silicon temperature [42]. Depending on the range of temperatures experienced by the rings, this circuitry can be expensive.

- Fabrication. It may also be necessary to compensate for size variation that results from fabrication error. Although a ring resonator is a few microns in diameter, only a few nanometers may separate two adjacent wavelengths in a given free spectral range. High-resolution lithography may obtain such precision, as recently demonstrated by the telecom industry with ≈ 1.8±0.1 nm wavelength spacing for ring resonators [43]. More precision will be needed for smaller 0.45 nm targets (as discussed below). In the case that the lithography cannot meet such stringent requirements, the same methods used for thermal tuning may be applied to correct for fabrication.

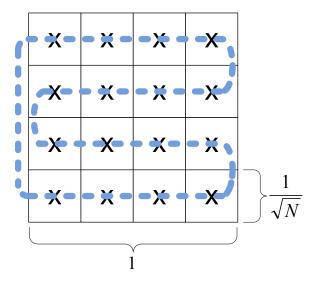

- Area. Each ring resonator operates at a different wavelength and is sized according to its operating wavelength.

The laser's spectral range and degree of DWDM largely determine the wavelength spacing, which in turn determines a ring resonator's size. The fabrication precision can also play a role in a ring's dimensions, as described below.

The gain spectrum of the laser, divided by the degree d of DWDM, indicates the maximum spacing between adjacent wavelengths. All wavelengths are equally spaced. A typical semiconductor laser has a spectral range of 30-40 nm [40]. We calculate that an aggressive DWDM design with d=64 and a laser with a spectral range of 30 nm would then require  $\lambda$  spacing on the order of 0.47 nm.

Because a ring resonates when an integral number of wavelengths (n) fit in its circumference, the minimum circumference difference between two wavelength adjacent rings  $(\lambda_i, \lambda_{i+1})$  is 0.47nm and the minimum diameter difference  $(\Delta d = d_{i+1} - d_i)$  is a mere 0.15 nm. This minimum occurs when n = 1, and is uncomfortably small for even advanced lithography (on the magnitude of a few atoms). Fortunately, the  $\Delta d$  between  $\lambda$ -adjacent rings grows linearly with n. Thus, the value of n should be large enough to tolerate lithography variation between adjacent rings.

The value of n should also be set so that a given ring resonator only resonates with one frequency. <sup>1</sup> In other words, if a ring closely obeys  $d_i \mod \lambda_i = 0$ , all other  $\lambda_j$ 's, where  $j \neq i$ , must obey  $d_i \mod \lambda_j \neq 0$ . This may also play a role in limiting the spectral range to  $[\lambda_0 * n, \lambda_0 * (n+1))$ .

This work assumes a laser with a spectral range of [1300 nm, 1320 nm], and 64 DWDM. Wavelengths have 80 GHz spacing (0.45 nm). Given the above considerations, ring resonators are between 3.5  $\mu$ m and 4.0  $\mu$ m in diameter and have a value of n around 32 for any given ring resonator.

<sup>&</sup>lt;sup>1</sup>This work assume single wavelength-selective ring-resonators. Ring resonators that resonate across multiple frequencies are also possible with larger sized rings [44].

So, while transistor sizes are largely determined by the technology scale, ring resonator dimensions are largely determined by the coupling wavelength. Ring sizes may shrink with improvements in wavelength, but improvements are limited; estimates indicate that rings start losing effectiveness at radii  $< 1.5 \mu m$  [28].

**Laser.** The off-chip laser supplies a continuous source of power for all on-chip communication. Thus, the laser is a static cost and provisioned for the maximum amount of concurrent communication. When the interconnect is not at maximum utilization, which is the common case, then the unused portion of laser power is wasted. The degree of this waste depends on the interconnect architecture.

**Waveguides.** It is important that the silicon waveguides have minimal propagation losses. Propagation losses occur when light scatters off of rough side-walls, which are formed with dry-etching into the resist mask [31]. Continued research into high-quality fabrication using e-beam lithography or oxidation techniques can minimize roughness [45, 46]. If necessary, laser power can be increased to compensate for such losses.

#### 2.2.2.2 System Considerations

Up until now, we have only looked at single devices. To build a nanophotonic interconnect, we must consider the system issues that arise when many devices are integrated. Below we consider system issues of power, layout, and error rate.

**Power.** The laser and the ring resonators are the major contributors to system power.

The laser power must be large enough to overcome losses due to waveguide crossings, waveguide curves, light scattering, device insertions, and signal conversions [47]. Losses incurred along the length of the waveguide can be especially dramatic, because they compound. One such loss, incurred by slight attenuation when a signal passes by an off ring resonator, determines the scalability of our proposals (discussed more in Section 5.6 Page 5.6). Generally speaking, designers should be cautious of implementing a waveguide with many crossings, many tight bends, or many off-resonance rings.

Ring resonators are the other major power contributor. Power is applied to the ring resonator to trim it (hold it off-resonance), bias it (bring it on-resonance), or modulate it (quickly alternate its resonance). The power a ring consumes depends on its state (see Table 4.1 Page 30 for power quantities). We calculate system ring power by assuming each ring operates independently.

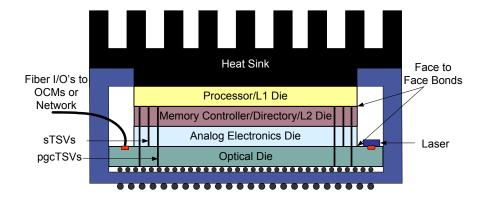

**Layout.** These photonic devices, with the exception of the off-chip optical power source, are built in a silicon layer, which may be integrated with CMOS electronics. Already, manufacturers of transceivers for telecom applications have begun integrating silicon photonics and electronics in the same die [48].

Figure 2.4 An Example of 3D Stacking

Prior work has advocated both same-die and separate-die integration of optical components [49, 50, 51, 49]. Monolithic integration has less interfacing overhead and higher yield than 3D stacking, but requires the optical components, which are relatively large, to consume active die area. 3D stacking, on the other hand, follows trends of future interconnects occupying separate layers and allows the CMOS and photonic processes to be independently optimized. The optical layer need not have any transistors, consisting only of patterning the waveguides and rings, diffusion to create the junctions for the modulators, germanium for the detectors, and a metalization layer to provide contacts between layers. An example of what 3D stacking might look like is shown in Figure 2.4.

Our optical token proposals are evaluated in systems with a separate optical die but are light-weight enough that they could feasibly be integrated onto the same die as the electronics.

**Cost.** The economics of fabrication are key to the eventual success of nanophotonics. Currently, wires are very cheap and optics very expensive. For nanophotonics to succeed, many devices must be fabricated cheaply and reliably.

#### 2.3 Alternative Global Technologies

Transmission lines and radio frequency are alternative technologies for global communication.

**Transmission Lines.** Transmission lines are a promising solution that avoid the issues RC wires experience by having delay dominated by inductive impedance rather than resistive impedance. In other words, they use wave transmission signalling rather than voltage signalling. Delays near the speed of light have been demonstrated for cross-chip interconnects [52]. Transmission lines do not need repeaters, but consume more area than even the widest global wires [53].

**Radio Frequency.** Radio frequency (RF), like transmission lines, also use transmission of waves to signal. Unlike transmission lines, but similar to photonic waveguides, several frequencies may share the same (metal) waveguide with Frequency Division Multiple Access (FDMA).

RF devices are larger than optical devices but, unlike optics, do benefit from scaling with technology. Estimates for the inductor, which consumes a dominant portion of the transceiver area, is  $50\mu\text{m} \times 50\mu\text{m}$  at 20 GHz [54].

Finally, RF suffers from electromagnetic interference (EMI) and must be shielded for reliability. On the other hand, optics is immune to EMI.

## 2.4 Summary

This chapter began with a discussion of electrical wire challenges and ended with a discussion of silicon photonic challenges. While both technologies have significant challenges ahead, silicon photonics is a young technology that has been making significant progress. We are hopeful researchers can sustain, or even improve, this rate of progress.

In the middle of the chapter we described how the basic nanophotonic building blocks work. With waveguides, ring resonators, and a laser, we have all the components necessary to build our proposals.

## **Chapter 3**

## **Related Work**

This chapter summarizes the architectural work related to this dissertation. Section 3.1 discusses interconnect control and Section 3.2 discusses cache coherence.

## 3.1 Optical Interconnect Control

So far, architects have mostly advocated on-chip optics for global data transmission, transferring zeros and ones from a source to a destination. Optical data interconnects have the potential to provide high frequency, high bandwidth, global communication while consuming modest power. However, to realize the potential, a few requirements must be met:

- 1. The interconnect's global nature requires a means to setup communication for cross-chip source-destination pairs.

- 2. The interconnect's speed and high bandwidth allow for single-cycle messages, but also requires fast reconfiguration.

Nearly every global data channel will need adjustments on nearly every cycle.

Frequent cross-chip reconfiguration may be possible with electronic control, but faces distinct challenges because global communication in electronics is expensive and needs to be segregated into local decision domains [55]. We believe optical tokens have the opportunity to meet control needs at a global scale.

## 3.1.1 Optical Transmission Fidelity

If in-flight data transmissions may collide, they must either be restricted from doing so, or else the collisions must be detected and recovered. Below we discuss how optical interconnects have prevented collisions with physical topology and access policies.

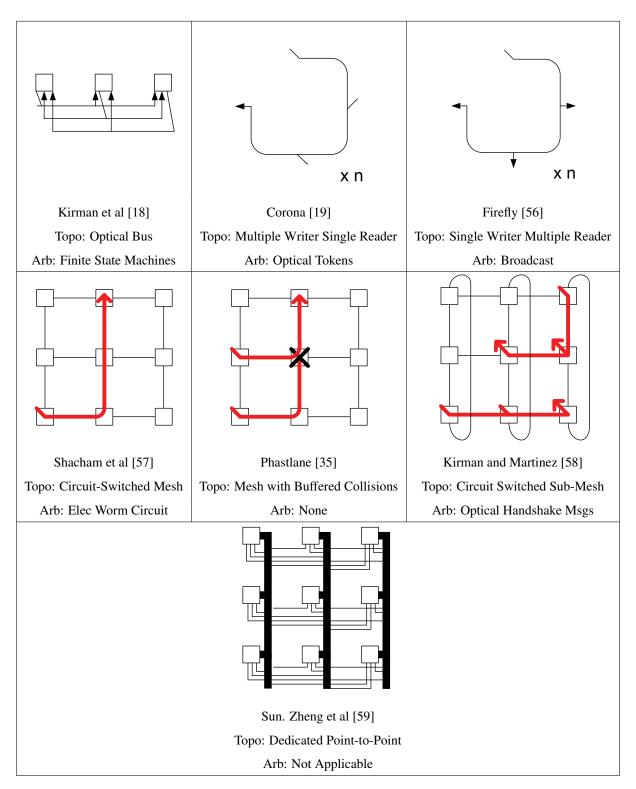

Figure 3.1 Optical Interconnect Topologies (Topo) and Arbitration Policies (Arb).

## 3.1.1.1 Topology Approaches

The easiest way to avoid transmission collisions is to build a topology where they do not exist. Providing dedicated channels between every source-destination pair achieves this, as proposed by Sun Microsystems' point-to-point network [59]. Their approach allows a non-blocking topology with no per-packet setup time, but it is also restricts flexible use of bandwidth and requires  $n^2$  channels. Topologies consisting of master-slave channels, where there is only one writer but may be many readers, also avoid write collisions [56]. Such single-writer-multiple-reader (SWMR) channels avoid writer-collisions but need a way to avoid reader-collisions. Reader-collisions are a problem in optics, caused by the ring-resonators having a destructive-read effect on the signal. The only proposal to avoid such reader collisions uses heavy-weight broadcast messages that instruct a single reader to activate its detectors [56].

Topologies that allow for multiple writers (or multiple masters) on a channel are susceptible to writer collisions and are the focus of Chapter 6. The topologies we study support channels with many writers, allowing for a potentially large collision problem (but also high channel utilization through sharing). If the channel only supports a small number of writers, the collision problem is not so large and the channel is less vulnerable to collisions (but also less utilizable). Kirman and Martinez use the latter approach [58]. In their design, a subset of nodes share a channel and optical messages are exchanged to configure the channel for a source-destination pair. The source-destination may communicate until the channel is reconfigured for a new pair. They find reconfigurations happen rarely for scientific workloads, and their approach has comparable throughput to prior proposals.

Finally, topologies that have intersecting channels (e.g. meshes) can have routing collisions when two or more messages are simultaneously routed onto the same physical channel. Joshi et. al [50] propose at an optical Clos network that always buffers a packet before sending it on, thereby avoiding contention for an output port. Shacham et. al [57] pro-actively avoid collisions in a mesh by requiring a circuit be set up between a source and destination before transmitting. They rely on long-lasting circuits to recover the setup latency. Phastlane [35] also uses a mesh, but reacts to collisions at the router, buffering all but one of the collisions. If buffers are not available, the message is dropped. Their design also requires a very aggressive router in addition to optical and electrical circuits with picosecond delay.

Figure 3.1 shows the variety of optical topologies discussed above.

#### 3.1.1.2 Access Policies

Collisions may also be avoided with access policies that either restrict or permit a source from transmitting. Some common access approaches include:

**Time/Frequency Division Multiplexing.** Multiplexing avoids collisions by restricting a source to a certain dimension of the transmission space. In time division multiplexing (TDMA), a source may only transmit 1 out of every n network cycles, where n is determined by the number of possible source-destination pairs. In frequency division

multiplexing (FDMA), a source and destination communicate exclusively over a fixed set of frequencies. Both TDMA and FDMA have been proposed for optical NoCs [18, 59].

**Bipartite Matching.** Matching protocols create collisionless source-destination pairs by solving an instance of the bipartite matching problem [60]. The problem input is a set of edges (requests) that connect two sets of vertices (sources and destinations). The output is a set of matchings, represented by a subset of the input edges.

In a centralized one level bus [61], there is at most one match at a time (one source wins the bus). In crossbars, there can be many simultaneous matchings (many sources to many destinations). Crossbar matching is most widely used in router chips, like Tiny Tera [62], but can also found in high performance computing chips, like the DEC EV7 [63, 64]. The goal of a matching is to provide as many matches as possible with low latency [65].

Maximal matching, whereby the matching cannot be extended by adding another pair, requires interaction between the sources and destinations [63]. Maximal matching can be achieved by optically communicating all arbitration information to-and-from a centralized arbiter, as proposed by Minkenberg et. al [66] and Krishnamurthy, Franklin, & Chamberlain [67]. It can also be achieved in a distributed manner, as proposed by Qiao and Melhem [68] for SMPs. Requesting nodes send optical pulses downstream while detecting pulses that may be coming from an upstream requester. At the end of an arbitration, a successful requester detects no light (no requesters) from upstream.

**Token Protocols.** Token protocols have been used for a long time in distributed systems to provide mutually exclusive access to channels [69, 70, 71]. A node that seizes a token is guaranteed a mutually exclusive allocation of the bandwidth; no other node's data transmission will collide with it. Token protocols are naturally distributed and allow for continual resource arbitration. While token protocols work on any physical topology, they work best on a ring topology.

In optics, Ha and Pinkston [72] and Kodi and Louri [73], have advocated token-based protocols to arbitrate for optical SMP data interconnects. Their proposals process tokens electrically at each node by converting the optical signal to an electrical signal, processing the token, and converting it back to an optical signal. Repeating the token at every node is mandatory. Similarly, Marsan et. al [74] propose a collisionless arbitration strategy for optical LAN and MAN rings that relies on inspecting message slot headers, a technique analogous to requesting tokens. In Section 6, we show the latency of repeating a token cannot be tolerated in optical NoCs which are highly sensitive to latency. We argue that on-chip optical interconnects will likely have repeat-free transmission and will benefit most from repeat-free tokens.

The token protocols we propose use optical tokens to minimize token repeats. The protocols work best on many-writer interconnects that physically resemble the ring or bus topology, like [18, 19, 74, 75]. Our proposals are not directly applicable to meshes, like Shacham et. al's [57] and Cornell's Phastlane [35].

#### 3.1.2 Flow Control

Optical interconnects are fast and have the potential to fill buffers at the destination quickly. The rate of data flow must either be throttled to guarantee the destination always has a buffer for an incoming transmission, or may be unrestricted with a buffer-overflow/retransmission mechanism in place.

To keep the system in a steady state, the rate that a node services its buffers should be greater than or equal to the rate that the buffers are filled. For some topologies, the buffer fill-rate can be very high (even scaling with the number of nodes), making buffer overflows very likely. For example, Sun's dedicated optical channels [59] and Firefly's SWMR channels [56] allow for a node to potentially receive from all on-chip nodes at once.

Such bursty behavior can overwhelm buffers and cause undesirable thundering herds [76] in the face of retransmission. For other topologies, where the peak receive bandwidth is fixed under scaling of nodes, buffer flow is still an issue that may be caused by queueing back ups. Irrespective of topology, throttling the flow can improve bandwidth utilization by avoiding failed transmissions due to receive buffer overflows.

The most common approach to flow control is credit based [77]. Each buffer is associated with a credit, and only a node that seizes a credit may seize the corresponding buffer. Our proposal, as well as a similar proposal [75], uses credit-based flow control and circulates the credits optically. We only evaluate designs with flow control.

#### 3.1.3 Fairness

Finally, the interconnect must guarantee management such that all nodes make forward progress. The ring topology has daisy-chain ordering. In Chapter 6, we find that a node's position on the ordered ring can impact the service it receives.

Many ring arbitration schemes in LAN systems have had to address issues of access fairness when a node's location on the ring matters. Metaring [78] uses a so-called SAT(isfied) token that travels upstream, against traffic, and refreshes transmission quotas at each hop. Starving nodes hold the SAT token, causing other nodes to exhaust their quotas, and eventually guaranteeing the starving node is serviced. Other approaches use fairness epochs that operate in a "stop-and-go" fashion [79, 80]. These methods aim to over time balance the varying bandwidth needs of nodes, but adjust the needs too slowly for unpredictably dynamic and fine grain on-chip communication.

We overcome ring-ordering issues by providing a means for an under-serviced node to communicate that it is starving. Elsewhere, Flexishare [75] also encountered unfairness problems with its optical channels. The authors solved Flexishare's unfairness with a two-pass scheme, where only a single node could be serviced on the first pass and if unused, any node could be serviced on the second pass. Although very similar to our scheme, their scheme guarantees a lower bound on service while our scheme comes very close to providing max-min service, a harder service guarantee (see Section 6.1.3 on page 59 for more discussion of max-min). A lower bound sets the minimum service a node will receive, but makes no statement about the service received above this bound. Flexishare enforces

the minimum service on the first pass, but the second pass still suffers from daisy-chain ordering. Our max-min goal, on the other hand, states that service above this bound should be equally distributed across all the nodes.

## 3.2 Cache Coherence Complexity

More cores mean more caches. Caches improve performance because they allow for low-latency access to data by keeping copies of the data near the cores. However, in the presence of many caches, systems must keep a consistent view of memory. Cache coherence protocols do just this by managing reads and writes to shared memory locations, usually at the granularity of a block. Given a memory location, a protocol should deliver read values that can be interleaved into a total order of writes to that same location. Unfortunately, as we describe below, cache coherence protocols have become more complex over time, which motivates our Atomic Coherence work (Chapter 7).

#### 3.2.1 Cache Coherence

Hardware often implements cache coherence, allowing for performance benefits over software. Hardware implementations need no involvement from the compiler and programmer, allowing for a flat-view of memory.

There are two major approaches to how blocks are maintained under replication. In the *update* approach, all copies of a block may be *updated* when a processor alters (writes) any one copy. In the *invalidate* approach, all copies, except the one being altered, must first be evicted from the caches before the remaining lone copy is written. The update approach allows reading and writing of a shared block. It has the advantage of propagating writes for subsequent use by the sharers, but also consumes extra bandwidth and makes write atomicity difficult.

Whether or not an update or invalidate approach is used, there is still an issue of finding sharers so that they may be updated or invalidated. The sharers may be found with snoops, a directory, or a combination of the two [81]. Snoops are messages that probe every cache for copies and take appropriate action on the block. Snooping protocols work well for small systems, but do not scale to large systems because the bandwidth to a cache and the number of snoops that a cache must process in a given cycle scales with N. Directory protocols are more scalable by only probing caches that have the block. Requests can look in the directory to find an entry containing sharer information. The main drawback to directories is that the directory introduces a level of indirection, which adds latency. Another drawback that has been receiving recent attention [82] is that directories are limited by their metadata, which must scale with N for precise tracking of sharers. And while imprecise tracking reduces metadata overhead [83, 84, 85], it sacrifices precision of the sharing set.

Regardless of the approach taken to managing caches, there are complexity issues that arise due the concurrent nature of caches operating independently. We discuss complexity issues next.

### 3.2.2 Evolution of Protocol Complexity

The literature usually represents cache coherence protocols as state machines with events that cause atomic transitions between stable states (e.g., M, S, I) [86]. In early bus-based machines, these *stable transitions* could be accomplished atomically, since the bus, once allocated, was held until the transition completed and prevented the initiation of any other concurrent transitions. Such blocking shared buses made it easy to provide coherence, since arbitration for the shared resource implicitly specified a total order for all memory references. The buses atomically serialized all racing requests, enabling a trivial construction of a coherent system-wide interleaving of reads and writes to a common address.

Unfortunately, performance concerns soon forced designers to abandon blocking shared buses, adopting non-blocking buses and other high performance interconnects instead [88]. Such interconnects separate a request from its associated responses, freeing the bus in the interim to deliver other commands and providing much higher utilization and bandwidth. However, coherence transitions can no longer be accomplished atomically, but must instead be decomposed into a series of *split transitions*. Split transitions correspond to the completion of various steps of the end-to-end state transition (e.g. request, coherence response, data response). This is an unavoidable result of exposing greater concurrency in the processor-memory interconnect.

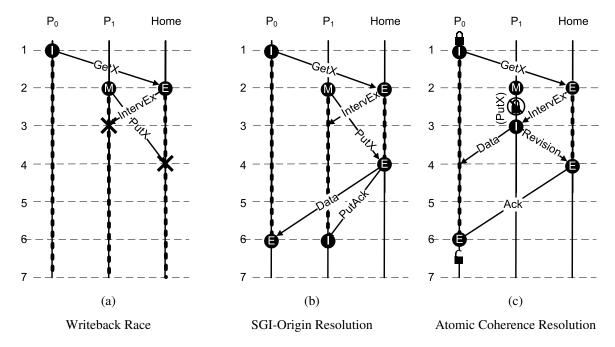

Unfortunately, absent arbitration for a single shared resource, split transition protocols are no longer immune to races between conflicting requests to the same addresses. Coherence guarantees require that protocols adapt to provide a means for detecting and resolving these interconnect-induced races. If the race is detected after two or more nodes in the system have initiated conflicting coherence state transitions, the protocol must include additional *race transitions* to correctly resolve the situation. The result is an explosion of state-event space, adding complexity to the protocol but also adding performance.

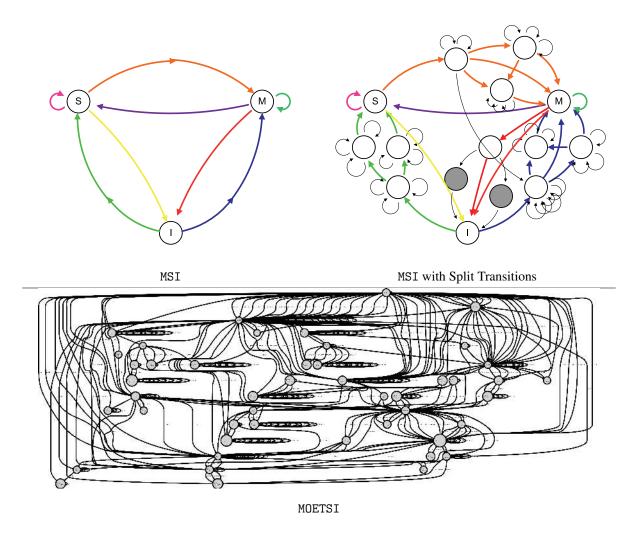

Figure 3.2 shows an example of the state-explosion for a simple MSI protocol while Figure 3.2 shows the state-explosion for a more complex MOETSI protocol. More complicated protocols have even larger state explosions; the Cray-X1 has been reported to have as many 214 million reachable states [89]. As the figures show, many races result in self-transitions (returning to the same state). For brevity, the figure does not show that each self-transition may take one of many actions (e.g. buffer, NACK, ACK, etc). Also, the figures only show valid state-event pairs. When designers specify the protocol, they must figure out from all possible state-event pairs, which pairs are valid and require specification. Reasoning about valid versus invalid state-pairs can be difficult in the presence of races.

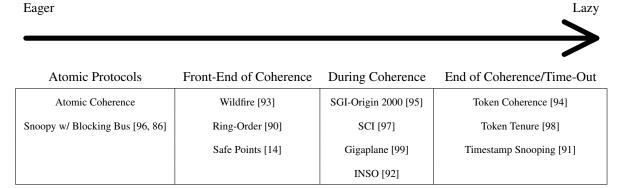

## 3.2.3 Ordering Techniques

There are many techniques for establishing and maintaining coherence request order. Once an order has been created, the order must be obeyed and non-atomic interleavings must be dealt with.

Figure 3.2 **Protocol Finite State Machines. Top: MSI Protocol.** The left figure shows a high-level view of the MSI protocol. The right figure flushes out all of MSI's state transitions, most of which are race transitions. Gray states represent those states which only exist to resolve races (the writeback race). **Bottom: MOETSI** [87] protocol is an example of a protocol more sophisticated (and more complex) than MSI (above)

**In-Network Ordering.** An interconnect topology which establishes message order may help to reconcile racing requests. For example, buses, and to some extent rings [90], have topological ordering points that place messages in a global order. Once a race has been detected, the established order can be used to resolve the race accordingly. For unordered topologies, like the mesh, order can be built into the topology with techniques such as Timestamp Snooping [91] or In-Network Snoop Ordering (INSO)[92].

**Ordering Points.** Alternatively, directories, which are topology-agnostic, can establish order at the directory entry.

A directory that only services one request to block B at a time and delays all other requests to B is called a blocking directory (e.g. Wildfire [93]). Races are serialized at the directory by either queueing the request or NACKing the request. A request can only proceed past the directory when the directory becomes unblocked (the prior request has completed). Blocking protocols have fewer race transitions because they detect and resolve races early-on at the directory.

Blocking protocols sacrifice some concurrency by serializing requests at the directory. They also can lead to deadlock if blocking is employed at more than one level of the memory hierarchy. A hierarchical blocking protocol can be made deadlock-free by altering the protocol such that some blocking states become non-blocking states. Marty and Hill call these non-blocking states *safe points* in their two-level hierarchy [14]. Safe points must handle any action from the second-level at any time. The fewer safe points a protocol has, the more it resembles a blocking protocol and the simpler it is. A protocol that has few (or no) safe points is highly concurrent but also suffers from state-space explosion.

**Token-Based Ordering.** Finally, Token Coherence [94] is an order-less coherence strategy that uses greedy methods to maintain order; the requester that obtains the necessary number of tokens may proceed. In scenarios where two or more requests race for the tokens, requesters could deadlock waiting for each other's tokens. Token Coherence uses time-outs to detect these races and orders them with a *persistent request*. A persistent request preempts other conflicting requests, thereby breaking the deadlock and ordering racing requests. Token Coherence has no pre-preemptive mechanism to prevent or manage races, requiring it to resort to reactive methods (e.g. persistent requests and broadcast) to resolve races. In contrast, Atomic Coherence eagerly resolves races before requests are allowed to become active.