has done research in graph theory and network analysis and synthesis. Mr. Tanaka is a member of the Institute of Electronics and Communication Engineers of Japan.

Tokyo, Japan.

Chiaki Hishinuma was born in Tokyo, Japan, on December 18, 1947. He received the B.E., M.E., and Ph.D. degrees in electrical engineering from Keio University, Yokohama, Japan, in 1970, 1972, and 1975, respectively.

From 1970 to 1975, he was engaged in research at Keio University, mainly on network theory, graph theory, and computer systems. In April 1975, he joined the Electrical and Communication Laboratory, Nippon Telegraph and Telephone Public Corporation,

Dr. Hishinuma is a member of the Institute of Electronics and Communication Engineers of Japan and the Information Processing Society of Japan.

Shinsaku Mori was born on August 19, 1932, in Kagoshima, Japan. He received the B.E., M.E., and Ph.D. degrees in electrical engineering from Keio University, Yokohama, Japan, in 1957, 1959, and 1965, respectively.

Since 1957, he has been engaged in research at Keio University mainly on nonlinear circuit theory and communication engineering. He is now an Associate Professor of Keio University.

Dr. Mori is a member of the Institute of Electronics and Communication Engineers of Japan and the Institute of Electrical Engineers of Japan.

Optimal Design of Nonlinear DC Transistor Circuits Without Solving Network Equations

S. R. K. DUTTA, STUDENT MEMBER, IEEE, AND MATHUKUMALLI VIDYASAGAR, MEMBER, IEEE

Abstract-A method is described for the optimization of nonlinear dc circuits. A performance index is defined to measure the difference. between the desired and the actual specifications. The novel approach taken here is to treat the network equations as equality constraints on the design parameters. The constrained optimization problem is then converted to an unconstrained one by a penalty function technique. A straightforward method is given for computing all the gradients needed during the optimization, given only the topology of the network and the branch relationships. This makes the algorithm easily amenable to a package program.

# I. INTRODUCTION

DECENTLY, methods have been given for the K computer-aided design of several types of nonlinear dc circuits [1]-[4]. A great deal of the computation time for such a design is spent on the nonlinear circuit analyses [6], making any design algorithm efficiency dependent on the efficiency of the analysis algorithm.

Manuscript received March 29, 1974; revised August 5, 1974 and January 28, 1975. This work was supported by the National Research Council of Canada under Grant A-7790. The authors are with the Department of Electrical Engineering, Concordia University, Montreal, Canada.

In this paper a method is proposed for nonlinear dc optimization without solving network equations. This is achieved by treating the network equations as equality constraints on the parameters. A penalty function is defined to transform the constrained problem into a sequential unconstrained problem [7], [8], which is then solved by an algorithm due to Morrison [7], with an improvement proposed by Kowalik et al. [8]. This particular algorithm is found to be the most suitable one for the present problem.

# **II. PROBLEM FORMULATION**

# Performance Index

Given a design specification in terms of the various voltages and currents appearing in the circuit, an error term is associated with each of them. Such a term measures the difference between the actual and the desired values. The overall performance index may be written as

$$f = \sum_{i=1}^{N_{V}} \left[ W_{V_{i}}(V_{i} - \hat{V}_{i}) \right]^{2} + \sum_{j=1}^{N_{I}} \left[ W_{I_{j}}(I_{j} - \hat{I}_{j}) \right]^{2} \quad (1)$$

where  $V_i$ ,  $I_j$  are the actual voltages and currents, and  $\hat{V}_i$ ,  $\hat{I}_j$  are the corresponding specified values;  $N_V$ ,  $N_I$  are the number of voltage and current specifications, respectively, while  $W_{V_i}$ ,  $W_{I_j}$  are the positive scaling parameters. If  $\hat{V}_j \neq 0$ , the parameter  $W_{V_i}$  is chosen as  $W_{V_i} = \hat{W}_{V_i} ||\hat{V}_i|$ where  $\hat{W}_{V_i}$  is another scaling parameter. This has the effect of normalizing the corresponding error term in (1). Similar considerations apply to  $W_{I_j}$ . Let the network equations be defined by g = 0. Then the optimization problem can be stated as: minimize f subject to the constraint g = 0.

A set of transistor parameters and source excitation values may be called an "environmental condition." The performance function of (1) yields a design under a nominal environmental condition; however, it can easily be extended to include several such conditions simultaneously such that the bias point fluctuation is minimized (worst case design). A performance function like (1) is then defined for each environmental condition, and the overall performance function is the algebraic sum of all such functions. To minimize power dissipation, terms of the type  $W_p I_p V_p$  are added to f in (1) for each power supply, where  $W_p$  is a weighting factor used to have a tradeoff between the accuracy of specified voltage and current, and the power consumption.

### DC Transistor Model

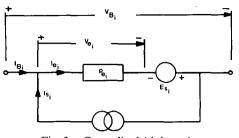

For the formulation of nodal equations the Ebers-Moll transistor model [6] replaces the transistors. Such a model for an n-p-n transistor is shown in Fig. 1.

# **III. MODIFIED MORRISON'S ALGORITHM**

The original problem is converted to an unconstrained problem by replacing the constraints by a penalty function, as follows. Define

$$F_{i}(\mathbf{x}) = [f(\mathbf{x}) - M_{i}]^{2} + \sum_{j} k_{j} [g_{j}(\mathbf{x})]^{2}, \quad \text{where } k_{j} \ge 0.$$

(2)

The algorithm below is given in [8].

a) Start with an estimate  $M_1$  with  $f(\bar{x})$ , the optimum value of  $f_1 \ge M_1$ , i.e., start with an optimistic guess for  $M_1$ . Let i = 1.

b) Minimize  $F_i(x)$ , and let  $x_i$  be the resulting solution. Define

$$F_{i0} = [f(\mathbf{x}_i) - M_i]^2 + \sum_j k_j [g_j(\mathbf{x}_i)]^2.$$

c) Let

$$M_{i+1} = M_i + F_{i0}^{1/2}.$$

(3)

d) If  $M_{i+1} = M_i$ , stop. Otherwise go back to b), with  $i \leftarrow i + 1$ . The basis for the algorithm is that if  $M_1$  is an optimistic guess, then  $M_i$  is an optimistic guess for all *i*, and  $M_i$ 's converge monotonically to  $f(\bar{\mathbf{x}})$  under some mild conditions on f and g.

Calling M as the Morrison parameter, Kowalik *et al.* [9] have given an improved scheme for updating the parameter. It is given by

$$N_{i+1} = N_i + F_i / \left( F_i - \sum_j k_j g_j^2 \right)^{1/2}$$

(4)

where N is the new Morrison parameter. Comparing (4) with (3) it may be seen that  $N_i \ge M_i$  for all *i*, so that the

Fig. 1. Ebers-Moll model for n-p-n transistor.

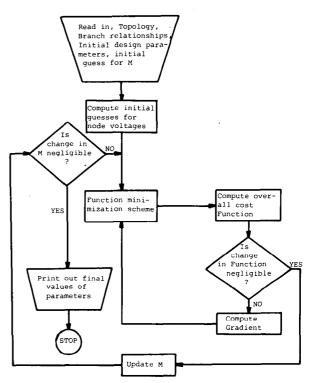

Fig. 2. Flowchart of design algorithm.

$N_i$ 's converge faster than  $M_i$ 's. Since f as defined in (1) is always nonnegative, any negative number may be chosen as the initial guess for N.

In case of dc design of transistor circuits, g(x) is taken to be the set of network equations while f is the performance index. The penalty augmented function is thus given by

$$F = (f - N)^{2} + k \sum_{i} g_{i}^{2}$$

(5)

where k is a scaling factor.

#### Flow Chart of the Algorithm

A flow chart based on Morrison's algorithm applicable to our design problem is given in Fig. 2.

#### IV. COMPUTATION OF GRADIENTS

Let x be a vector of the design parameters. Differentiating the penalty augmented function F in (4) with respect to x,

Fig. 3. Generalized *i*th branch.

we have

$$\frac{\partial F}{\partial x} \triangleq \nabla F$$

$$= 2(f - M)\frac{\partial f}{\partial x} + 2k\left(\frac{\partial g}{\partial x}\right)^T g \qquad (6)$$

where, from (1)

Ć

$$\frac{\partial f}{\partial x} = 2 \sum_{i=1}^{N_V} W_{V_i}(V_i - \hat{V}_i) \frac{\partial V}{\partial x} + 2 \sum_{j=1}^{N_I} W_{I_j}(I_j - \hat{I}_j) \frac{\partial I_j}{\partial x}.$$

(7)

Computation of  $\partial f/\partial x$  in (7) involves the computation of  $\partial V_i/\partial x$  and  $\partial I_j/\partial x$  which is straightforward and is therefore not described here. To derive  $\partial g/\partial x$  in (6) we proceed as follows.

Without any loss of generality all the controlled sources in a linear lumped network can be assumed to be voltage controlled current sources. Assuming a generalized *i*th branch to be as shown in Fig. 3, the different branch parameters for the whole network may be expressed in vector form as follows:

- $p_e \rightarrow$  branch element "parameter" vector

- $V_e \rightarrow$  element voltage vector

- $I_e \rightarrow$  element current vector

- $E_s \rightarrow$  voltage source vector

- $I_s \rightarrow$  current source vector

- $I_B \rightarrow$  branch current vector

- $V_B \rightarrow$  branch voltage vector.

$I_e$ ,  $E_s$ , and  $I_s$  may now be expressed as functions of  $V_e$  and  $p_e$  as  $I_e = f_1(V_e, p_e)$ ,  $E_s = f_2(V_e, p_e)$ , and  $I_s = f_3(V_e, p_e)$ . From Fig. 3,  $I_B = I_e - I_s = f_4(V_e, p_e)$ , and Kirchhoff's current law (KCL) yields  $AI_B \triangleq g = 0$ .

Gradient with Respect to the Node Voltages

The penalty term is given by

$$\sum_{j} g_{j}^{2} = \boldsymbol{g}^{T} \boldsymbol{g}$$

$$\triangleq \boldsymbol{P}.$$

Denoting the node voltage vector by  $V_n$ , Kirchhoff's voltage law (KVL) yields,  $V_B = A^T V_n$ . However,  $V_e = V_B + E_s = A^T V_n + E_s$ , and hence  $g = A f_4 (A^T V_n + E_s, p_e)$ . Differentiating P with respect to  $V_n$ , we have

$$\frac{\partial P}{\partial V_n} = 2A \left[ \frac{\partial f_4(V_e, p_e)}{\partial V_e} \right]_{V_e = A^T V_n + E}^T \left( A^T + \frac{\partial E_s}{\partial V_n} g \right). \quad (8)$$

In case of each branch current source and each branch voltage source being controlled by a single parameter or a single voltage source, (8) can be considerably simplified. Specifically, suppose the sources in the *i*th branch depend only on  $V_{e_j}$  and  $p_{e_j}$ . Then  $I_{e_i}$ ,  $E_i$ , and  $I_i$  can be expressed as,  $I_{e_i} = f_1(V_{e_j}, p_{e_j})$ ,  $I_i = f_2(V_{e_j}, p_{e_j})$ , and  $I_i = f_3(V_{e_j}, p_{e_j})$ . Note that this situation prevails in the dc transistor model in Fig. 1. Furthermore,  $\partial E_s/\partial V_n = 0$ , and (8) becomes

$$\frac{\partial P}{\partial V_n} = 2AJ^T A^T g \tag{9}$$

where the Jacobian J is given by

$$J = \frac{\partial f_4(V_e, p_e)}{\partial V_e} \bigg|_{V_e = A^T V_n + E_s}$$

(10)

Thus the Jacobian is the same as the branch admittance matrix of a transistor ac equivalent circuit, where the diodes are replaced by equivalent conductances given by

$$G_j = \frac{I_s q}{kT} \exp\left(\frac{q}{kT} V_{e_j}\right).$$

Denoting the branch conductance matrix by  $Y_B$ ,  $\partial P / \partial V_n = 2AY_B^T A^T g = 2Y^T g$ , where Y is the nodal admittance matrix of the new network. Note that  $Y_a = Y^T$ , where  $Y_a$  is the nodal admittance matrix of the linearized adjoint network [5].

# Gradients with Respect to the Design Parameters

Differentiating (1) with respect to  $p_e$ , we have

$$\frac{\partial g}{\partial p_e} = A \left. \frac{\partial f_4(V_e, p_e)}{\partial p_e} \right|_{V_e = A^T V_n + E_s}.$$

(11)

However, when the design parameters are lumped conductances,  $f_4$  becomes  $f_4(V_e, Y_e)$  and (11) may be simplified as follows.

Let the incidence matrix A be partitioned as  $A = [A_1 | A_2]$ , where the columns of  $A_1$  correspond to the conductances to be optimized, and those of  $A_2$  to the remaining branches. Accordingly, the linearized branch admittance matrix  $Y_b$  is partitioned as

$$Y_{b} = \begin{bmatrix} Y_{b_{11}} & Y_{b_{12}} \\ Y_{b_{21}} & Y_{b_{22}} \end{bmatrix}$$

where  $Y_{b_{11}}$  is diagonal. Therefore,

$$\frac{\partial P}{\partial \boldsymbol{p}_e} = 2 \frac{\partial}{\partial \boldsymbol{Y}_e} \{ \boldsymbol{A}_1 \boldsymbol{Y}_{b_{11}} (\boldsymbol{A}_1^T \boldsymbol{V}_n + \boldsymbol{E}_s) \}^T \boldsymbol{g}.$$

(12)

Gradient with Respect to an Independent Voltage Source

Let

$$\frac{\partial P}{\partial E_s} = 2A \left. \frac{\partial f_4(V_e, Y_e)}{\partial E_s} \right|_{V_e = A^T V_n + E_s} \cdot g$$

$$= 2A J_1 g \tag{13}$$

where the Jacobian  $J_1$  is the branch admittance matrix of the branches involving the independent voltage sources as parameters, with the other admittances set to zero.

TABLE I

| Para-                                       | 1   | Final           |                      |                      |                      |                        |

|---------------------------------------------|-----|-----------------|----------------------|----------------------|----------------------|------------------------|

| meters                                      |     | 1               | Run 2                | Run 3                | Run 4                | Values                 |

| G1                                          |     | 0 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.218×10 <sup>-3</sup> |

| G2                                          |     | o <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.218×10 <sup>-3</sup> |

| G3                                          |     | o <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.666×10 <sup>-3</sup> |

| G4                                          | 6   | o <sup>−3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.1×10 <sup>-3</sup> | 0.625×10 <sup>-3</sup> |

| <sup>6</sup> 5                              | ¢   |                 | 0.1                  | 0.1                  | 0.1                  | 0.578×10 <sup>-1</sup> |

| v <sub>1</sub>                              |     |                 | 15.5                 | 15.5                 | 15.5                 | 15.659                 |

| v <sub>2</sub>                              |     |                 | -0.5                 | -0.5                 | -0.5                 | -0.640                 |

| v <sub>3</sub>                              | · - |                 | -17.5                | -17.5                | -17.5                | -17.323                |

| v <sub>4</sub>                              |     |                 | -17.6                | -17.6                | -17.8                | -17.982                |

| v <sub>5</sub>                              |     |                 | 15.0                 | 15.0                 | 15.0                 | 15.0                   |

| v <sub>6</sub>                              |     |                 | 15.5                 | 15.5                 | 15.5                 | 15.659                 |

| v <sub>7</sub>                              |     | ·               | 16.5                 | 16.5                 | 16.5                 | 16.5                   |

| CPU<br>Time                                 |     |                 | 4.2<br>s             | 4.7<br>s             | 3.5<br>s             |                        |

| No. of<br>Fletcher-<br>Powell<br>iterations |     |                 | 39                   | 44                   | 33                   |                        |

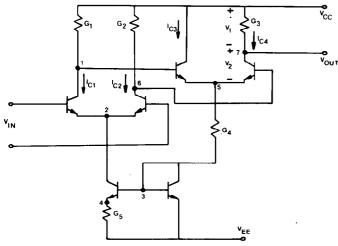

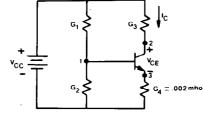

Fig. 4. Two-stage operational amplifier example.

# V. EXAMPLES

Due to shortage of space only two examples are presented to illustrate the effectiveness of the approach, which are taken from [1]. It is found that the convergence to the desired optimum occurs readily if the initial node voltage values are chosen in the neighborhood of the feasible region. To do this the transistors are replaced by a model without the collector-to-base diode and the corresponding current source in Fig. 1. Whenever a voltage between two nodes is given as a design specification, a voltage source equal to the specified value is connected between the nodes. For each collector current specification, the base-toemitter diode is replaced by a voltage source equivalent to the voltage drop in the diode. The other diodes in the circuit are replaced by voltage sources of magnitudes in the feasible range (say,  $0V \le V_{be} \le 0.6$  V), taking care that the KVL is also satisfied. The resultant modified network which may

|                                             |                     | TABLE II            |                     |                       |

|---------------------------------------------|---------------------|---------------------|---------------------|-----------------------|

| Para-<br>meters                             |                     | Final               |                     |                       |

| meters                                      | _Run 1              | Run 2               | Run 3               | Values                |

| Gl                                          | .1×10 <sup>-3</sup> | .1×10 <sup>-4</sup> | .1×10 <sup>-4</sup> | .949×10 <sup>-5</sup> |

| G2                                          | .1×10 <sup>-3</sup> | .1×10 <sup>-4</sup> | .1×10 <sup>-3</sup> | .706×10 <sup>4</sup>  |

| G3                                          | .1×10 <sup>-3</sup> | .1×10 <sup>-3</sup> | .1×10 <sup>-3</sup> | .184×10 <sup>-3</sup> |

| v <sub>1</sub> <sup>(1)</sup>               | 1.1                 | 1.5                 | 1.0                 | 1.08                  |

| v <sub>2</sub> <sup>(1)</sup>               | 5.6                 | 6.0                 | 5.5                 | 5,43                  |

| v <sub>3</sub> <sup>(1)</sup>               | 0.6                 | 1.0                 | 1.0                 | 0.42                  |

| v <sub>1</sub> <sup>(2)</sup>               | 1.1                 | 1.0                 | 1.0                 | 0.76                  |

| v2(2)                                       | 5.6                 | 6.0                 | 5.5                 | 5.43                  |

| v <sub>3</sub> <sup>(2)</sup>               | 0.6                 | 1.0                 | 1.0                 | 0.44                  |

| CPU<br>Time                                 | 2.4<br>S            | 2.8<br>s            | ' 2.6<br>s          |                       |

| No. of<br>Fletcher-<br>Powell<br>iterations | 44                  | 50                  | 47                  |                       |

Fig. 5. One transistor biasing circuit example.

be termed the "modified network," is then analysed and the node voltages thus obtained are taken as the initial node voltage values for the algorithm. The examples are run on a CDC 6400 computer available, using the optimization algorithm due to Fletcher and Powell [9] as in [1]. The termination criterion is  $N_{i+1} - N_i \le 10^{-15}$ .

# Example 1—Gain Stages for Operational Amplifier

The circuit is shown in Fig. 4. The adjustable parameters are the five conductances  $G_1$  to  $G_5$ . The bias point specifications are as follows:  $I_{c_1} = 0.5 \text{ mA}$ ,  $I_{c_2} = 0.5 \text{ mA}$ ,  $I_{c_3} = 1.0 \text{ mA}$ ,  $I_{c_4} = 1.0 \text{ mA}$ ,  $E_1 = 1.5 \text{ V}$ , and  $E_2 = 1.5 \text{ V}$ . The final results are shown in Table I. In Run 1 the initial guesses for the node voltages are found by analyzing the modified network; while in Runs 2 to 4 the initial values are varied slightly from that in Run 1. In all the runs the network equations are satisfied to the order of  $10^{-18}$ .

# Example 2—Single Transistor Stage: Two Environmental Conditions

The circuit to be designed is shown in Fig. 5. It is desired to have minimum deviation in the bias point at two environmental conditions, while minimizing power dissipation. The desired operating point is:  $I_c = 1 \text{ mA}$ , and  $V_{c_E} = 5 \text{ V}$ ; with the designable conductances being  $G_1$  to  $G_3$ . The transistor

parameters at the two environmental conditions are as follows. Condition 1:  $\beta_F = 25$ ; condition 2:  $\beta_F = 100$ ; while  $\beta_R = 5$ ,  $I_{C_S} = 10^{-14} A$ , and  $I_{E_S} = 10^{-14} A$  for both conditions. The results are shown in Table II where the superscripts denote the environmental conditions. The network equations are satisfied to the order of  $10^{-18}$ . The specified voltages and currents are realized as follows:

$$V_{c_E}^{(1)} - 5 = 0.95 \times 10^{-2}$$

$$V_{c_E}^{(2)} - 5 = -0.25 \times 10^{-2}$$

$$I_c^{(1)} - 1 = 0.62 \times 10^{-6}$$

$$I_c^{(2)} - 1 = 0.61 \times 10^{-6}.$$

The power dissipations are 0.926 mW and 0.928 mW at the two operating points. The final values of the modified Morrison's parameter N is of the order of  $10^{-5}$ .

# VI. DISCUSSION

It has been found by the authors that if the initial guess for the node voltage values are in the neighborhood of the ones obtained by analyzing the modified network as mentioned in Section 5, convergence is fast. Justification for the final design is based on the fact that the design specifications are realized as the vector q(x) of the KCL equations becomes zero. However, in reality it is a vector of very small numbers. Since the various currents in the circuits are of the order of milliamperes, to make the second term in (5)of the same order as the first term  $(f - M)^2$ , one should normalize the KCL equations with respect to the Euclidean norm of the current vector.

#### REFERENCES

- [1] R. I. Dowell and R. A. Rohrer, "Automated design of biasing circuits," *IEEE Trans. Circuit Theory*, vol. CT-18, pp. 85-89, circuits," Jan. 1971.

- [2] M. A. Murray-Lasso and W. D. Baker, "Computer design of multi-stage bias circuits," in *Proc. Allerton Conf. Circuits and Systems Theory*, pp. 557–563, Oct. 1967.

[3] A. J. Broderson, S. W. Director, and W. A. Bristol, "Simultaneous

- automated ac and dc design of linear integrated circuit amplifiers," IEEE Trans. Circuit Theory, vol. CT-18, pp. 50-58, Jan. 1971.

- [4] S. W. Director, "Computer-aided design of linear integrated circuit

- amplifiers, "in *Proc. IEEE Int. Symp. Circuit Theory*, 1973. [5] S. W. Director and R. A. Rohrer, "The generalized adjoint network

- and network sensitivities," IEEE Trans. Circuit Theory, vol. CT-16, pp. 318-323, Aug. 1969.

- [6] D. A. Calahan, Computer-Aided Network Design. New York: McGraw-Hill, 1972.

[7] D. D. Morrison, "Optimization by Least Squares," SIAM J. Numer. Anal., pp. 83-88, vol. 5, no. 1, Mar. 1968.

- [8] J. Kowalik, M. R. Osborne, and D. M. Ryan, "A new method for constrained optimization problems," in Operations Research, The Journal of the Operations Research Society of America, pp. 973–983, vol. 17, 1969.

- [9] R. Fletcher and M. J. D. Powell, "A rapidly convergent descent method for optimization," *Comput. J.*, vol. 6, pp. 163-168, July 1963.

S. R. K. Dutta (S'73) received the B.Sc. (Eng.) degree in electronics and communication engineering from the Bihar Institute of Technology (B.I.T.), Sindri, India, in 1966, and the M.Sc. degree in electrical engineering from the University of Calgary, Alberta, Canada, in 1971. In 1971, he was awarded a post-graduate scholarship by the National Research Council of Canada for doctoral studies in electrical engineering at Concordia University, Montreal, Canada. Presently, he

is working towards a D.Eng. degree in electrical engineering at Concordia University.

From 1966 to 1968, he was an Assistant Professor of Electronics and Communication Engineering at B.I.T. From 1968 to 1970, he was a Teaching Assistant in the Department of Electrical Engineering, University of Calgary, and since 1971, he has been a part-time lecturer in the Department of Computer Science, Concordia University. His current research interests are in the fields of computer-aided circuit analysis and optimization, and active filter design.

Mathukumalli Vidyasagar (M'75) was born on September 29, 1947, in Guntur, Andhra Pradesh, India. He received the B.S., M.S., and Ph.D. degrees, all in electrical engineering, from the University of Wisconsin, Madison, in 1965, 1967, and 1969, respectively. During 1965-1967, he held the Frank Rogers Bacon Fellowship.

He taught at Marquette University, Milwaukee, Wisconsin, during the year 1969-1970. Since 1970, he has been with the Department

of Electrical Engineering, Concordia University (formerly Sir George Williams University), Montreal, Canada, where he is at present an Associate Professor. During the academic year 1972-1973, he was a Visiting Assistant Professor with the System Science Department, University of California, Los Angeles, and during the summer of 1973, he was a Visiting Assistant Research Engineer with the Electronics Research Laboratory, University of California, Berkeley. He is a coauthor of the book Feedback Systems: Input-Output Properties (New York: Academic Press, 1975). His current research interests are system theory, stability, and optimization.