# Optimal Design of Repetitive Controller for Harmonic Elimination in PWM Voltage Source Inverters

Sufen Chen, Y. M. Lai, Siew-Chong Tan, and Chi K. Tse Department of Electronic and Information Engineering The Hong Kong Polytechnic University, Hong Kong SAR, China Chen.Sufen@polyu.edu.hk, enymlai@polyu.edu.hk, ensctan@polyu.edu.hk, encktse@polyu.edu.hk

Abstract— This paper presents an analysis of the application and optimal design of the repetitive controller for eliminating harmonic distortion in pulse-width modulation voltage source inverter systems. A method of analyzing the repetitive control system from the frequency response viewpoint is introduced. Based on this method, a systematic way of optimizing the design of the system is proposed. Specifically, the closed-loop repetitive controller is modified by including a zero-magnitudeand-phase compensator and a lead-lag compensator to improve the stability and tracking accuracy of the inverter system. It is shown both analytically and by simulations that the harmonics in the inverter's output voltage can be effectively eliminated with the improved repetitive controller.

#### I. INTRODUCTION

The pulse-width modulation (PWM) voltage source inverter (VSI) is extensively employed in AC power conditioning systems. When operated with nonlinear or periodic loads, the output voltage of these systems contains significant harmonic distortion if they are not properly controlled. Although conventional proportional-integral-derivative (PID) controllers that are widely used in the VSI can reduce such harmonic distortion, the control effort is still unsatisfactory for many critical applications. This is expected since in VSI systems with the PID control, the loop gain of the system's transfer function at locations of the fundamental frequency and its integral multiples, is often too small to effectively eliminate the periodic errors. Hence, there remains a significant amount of harmonic distortion, i.e., a high total harmonic distortion (THD) level in such systems.

Theoretically, the elimination of the THD would mean that the steady-state tracking of the periodic signal must be perfectly accurate. To do this, control approaches specialized for achieving precise tracking of periodic signal have to be incorporated. One approach commonly chosen for this purpose is the repetitive control (RC) [1]–[3]. The basic operating principle of the RC is to observe the system's periodic signals for one cycle period, and then to generate in the next cycle period a corresponding compensating signal to ensure precise tracking of these signals [3]. From a frequency viewpoint, the RC performs superior error cancelation for periodic signals by presenting a large magnitude of the loop gain at the fundamental frequency and its integral multiples. This can be recognized as a form of *period-based integral control*. Starting from 1980's, RC has been introduced to address the problem of large THD in inverter systems [4]. Various improved repetitive controllers were later explored to enhance the harmonic performance of the inverters [5]–[7]. Literature survey concludes that although the effectiveness of RC as applied to inverter has been demonstrated, thorough analysis and synthesis of the repetitive controller for the inverter system have not been reported.

In view of this, in this paper, we present a detailed study of the RC as applied to the harmonic elimination of the VSI from a frequency response viewpoint. In the discussion, the working principle of the RC, its stability constraints, the accuracy of the periodic error cancelation, and the trade-off between stability and accuracy are carefully addressed. Detailed analysis and synthesis of the control system for the VSI are provided. We also present a systematical design methodology which includes the proposal of a zero-magnitude-and-phase compensator to achieve a precise low-frequency compensation while providing sufficient robustness at high frequencies, and a lead-lag compensator to balance the stability and tracking accuracy at low frequencies. The validity of applying repetitive control in inverters are demonstrated.

## II. VOLTAGE SOURCE INVERTER MODEL

#### A. Analytical Model of the PWM dc/ac VSI

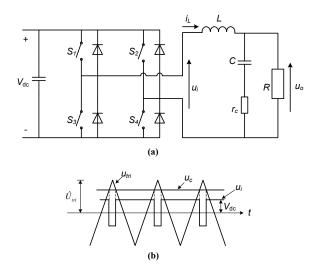

Fig. 1(a) shows a single-phase full bridge inverter with an LC filter. Assuming a resistive load, the dynamics of the inverter can be described as

$$\begin{bmatrix} \dot{u}_o \\ \dot{i}_L \end{bmatrix} = \begin{bmatrix} -\frac{L+RCr_c}{RCL+r_cCL} & \frac{R}{RC+r_cC} \\ -\frac{1}{L} & 0 \end{bmatrix} \begin{bmatrix} u_o \\ i_L \end{bmatrix} + \begin{bmatrix} \frac{Rr_c}{RL+r_cL} \\ \frac{1}{L} \end{bmatrix} u_i, \quad (1)$$

where  $u_o$  is the output voltage;  $i_L$  is the inductor current; R, L, C and  $r_c$  are the values of the load resistance, inductance, capacitance and the equivalent series resistance (ESR) of the capacitor, respectively; and  $u_i$  is the PWM voltage pulses of magnitude  $V_{\rm dc}$  or  $-V_{\rm dc}$  as shown in Fig. 1(b).

For the amplitude modulation ratio  $m_a = \hat{u}_c(t)/\hat{U}_{tri} < 1$ , the PWM voltage pulses  $u_i$  can be modeled in the averaged time-continuous form

$$u_i(t) = V_{\rm dc} \times \frac{u_c(t)}{\hat{U}_{tri}} = M u_c(t), \tag{2}$$

Fig. 1. Single-phase inverter. (a) Main circuit of inverter. (b) PWM waveform for  $u_i$

where  $u_c(t)$  is the control signal with amplitude  $\hat{u}_c(t)$ ;  $U_{tri}$  is the amplitude of the triangular carrier; and  $M = V_{dc}/\hat{U}_{tri}$  is the modulating gain.

By choosing  $\hat{U}_{tri} = 1$  and substituting (2) into (1), the transfer function of the averaged linearized model of the PWM inverter can be derived as

$$G_p(s) = \frac{U_o(s)}{U_c(s)} = \frac{b_1 s + b_2}{s^2 + a_1 s + a_2},$$

(3)

where

$$b_1 = \frac{V_{dc}Rr_c}{RL+r_cL}, \quad b_2 = \frac{V_{dc}R}{RCL+r_cCL}, \\ a_1 = \frac{L+RCr_c}{RCL+r_cCL}, \quad a_2 = \frac{R}{RCL+r_cCL}.$$

(4)

#### B. Control Problem Formulation

In practical inverters, disturbances from nonlinear loads and nonlinearities such as dead-time delay will introduce some low order harmonics, which cannot be removed by a general LC filter and lead to a high THD level in the waveform. To achieve a high-quality output voltage, it is necessary to design a controller that can eliminate the low order harmonics, i.e., to achieve a low THD, with a satisfactory dynamic performance.

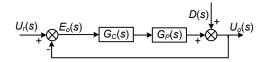

Fig. 2. Closed-loop control of voltage source inverter.

The closed-loop control of the output voltage of a singlephase inverter is depicted in Fig. 2, where  $U_r(s)$  is the reference signal, D(s) is the disturbances,  $G_p(s)$  is the inverter, and  $G_c(s)$  is the closed-loop controller. The tracking error of the system due to periodic input  $U_r(s)$  and disturbances D(s)is given by

$$E_0(s) = \frac{U_r(s) - D(s)}{1 + G_c(s)G_p(s)},$$

(5)

and the closed-loop transfer function of the control system is

$$H(s) = \frac{G_c(s)G_p(s)}{1 + G_c(s)G_p(s)}.$$

(6)

Typically, PID controller is adopted to realize the output voltage control. For higher precision, a specific controller dealing with harmonics is necessary. Repetitive controller is one such controller.

#### III. REPETITIVE CONTROL FUNDAMENTAL

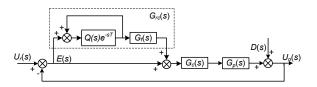

Fig. 3. Plug-in repetitive control system.

Fig. 3 presents the plug-in type of repetitive control system, obtained from the PID closed-loop control system described in Fig. 2 by incorporating a plug-in RC component into the system. To illustrate the tracking response of the RC scheme, the system tracking error, in terms of the tracking error  $E_0(s)$  of the original system without RC, is given by:

$$E(s) = E_0(s) \times \frac{1 - Q(s)e^{-sT}}{1 - [1 - G_f(s)H(s)]Q(s)e^{-sT}}.$$

(7)

where T is the period of the reference signal. Assuming that the system given in equation (6) is asymptotically stable and the stability condition

$$\left| [1 - G_f(s)H(s)]Q(s) \right| < 1, \quad s = j\omega, \quad \text{for all } \omega$$

(8)

is complied, then equation (7) can be expressed as the sum of a geometric progression as shown in (9).

Theoretically, by setting  $1 - G_f(s)H(s) = 0$  and  $1 - Q(jk\omega_0)e^{-jk\omega_0T} = 0, k = 0, 1, 2, \cdots$ , where  $\omega_0 = 2\pi/T$ , we can ensure that the steady-state tracking error converges to zero at the occurrence of every harmonic. From equation (9), it can be seen that  $[1 - G_f(s)H(s)]Q(s)e^{-sT}$  is the common ratio of the geometric progression. Hence, it can be regarded as an error convergence index.

However, due to the physical non-idealities of the system, such an ideal design condition is practically impossible. Instead, it is more appropriate to consider the design condition:

$$1 - G_f(s)H(s) \approx 0 \tag{10}$$

and

$$1 - Q(jk\omega_0)e^{-jk\omega_0T} \approx 0, \tag{11}$$

and for harmonics limited to a certain frequency bandwidth.

## IV. Analysis and Design of Repetitive Controller for VSI

## A. Analysis of Harmonic Elimination

This part of the analysis employs the frequency characteristic of the control system's loop gain.

$$E(s) = E_0(s)[1 - Q(s)e^{-sT}] \left\{ 1 + [1 - G_f(s)H(s)]Q(s)e^{-sT} + [1 - G_f(s)H(s)]^2Q^2(s)e^{-2sT} + \cdots \right\}$$

=  $E_0(s) \left\{ 1 - G_f(s)H(s)Q(s)e^{-sT} - G_f(s)H(s)[1 - G_f(s)H(s)]Q^2(s)e^{-2sT} - G_f(s)H(s)[1 - G_f(s)H(s)]^2Q^3(s)e^{-3sT} + \cdots \right\}$  (9)

1) Characteristic of the PID control: For the control system depicted in Fig. 2, which has a loop gain

$$T_{pid}(s) = G_c(s)G_p(s), \tag{12}$$

its PID controller is typically designed in this manner: a lowfrequency inverted zero to be added at  $f_l$  to enlarge the lowfrequency loop gain; a median-frequency zero to be added at  $f_z$  to increase the phase margin in the vicinity of the crossover frequency  $f_c$ ; a high-frequency pole (or poles) to be included at  $f_p$  to provide necessary high-frequency loopgain roll off(s) for rejecting system noises and uncertainties in practical systems. Hence, the transfer function of such a PID controller can be expressed as

$$G_{c}(s) = G_{d} \frac{(1 + \frac{\omega_{l}}{s})(1 + \frac{s}{\omega_{z}})}{1 + \frac{s}{\omega_{p}}},$$

(13)

where  $G_d$  is the DC gain,  $\omega_l = 2\pi f_l$ ,  $\omega_z = 2\pi f_z$ , and  $\omega_p = 2\pi f_p$ . Recall that the reference input signal and external disturbances of the VSI are typically periodic. This calls for a high requirement on the system's loop gain at the periodic frequencies. However, since it is difficult to design the PID controller to provide a suitably high gain at these frequencies, significant errors exist at the fundamental frequency and its integral multiples, especially in the range below the crossover frequency  $f_c$ . This results in a high THD level.

2) Characteristic of the RC: To reduce the level of the THD, a repetitive controller can be included to the inverter system (see Fig. 3), and the system's loop gain is changed to

$$T_{rc}(s) = \left[1 + \frac{G_f(s)Q(s)e^{-sT}}{1 - Q(s)e^{-sT}}\right] \times G_c(s)G_p(s), \quad (14)$$

The following explanation describes how  $G_f(s)$  and Q(s) in (14) can be designed to perform harmonic elimination in the system.

First of all, according to (8) and (10),  $G_f(s)$  is a zeromagnitude-and-phase compensator for transfer function H(s). Thus, the intuitive way of designing this compensator is to make  $G_f(s) = 1/H(s)$ . However, as indicated in (14),  $G_f(s)$  should have a limited magnitude at high frequencies to ensure a low loop gain above the crossover frequency. Additionally, since there are always some parameter drifts in the system, such as variation of ESR of filter capacitor etc., while the frequency response below the crossover frequency is relatively stable, it becomes instable at high frequencies. Therefore, it is necessary to include additional pole(s) to the compensator  $G_f(s)$  to ensure system robustness above the crossover frequency. Hence, we propose  $G_f(s)$  to be designed in the form:

$$G_f(s) = \frac{1}{H(s)} \times \frac{p}{s+p},$$

(15)

where p is a pole above crossover frequency, to realize both zero-magnitude-and-phase tracking in low frequency band and

high frequency stability. Note that the additional pole(s) will not affect the normal operation of the system in the low frequency range.

Secondly, careful observation of (11) reveals that Q(s) should be unity while (8) indicates that Q(s) should be less than unity at high frequencies because  $1 - G_f(s)H(s)$  tends to unity as  $H(s) \rightarrow 0$  at high frequencies. This requirement is further supported by (14). Since the parameter Q(s) with close to unity magnitude tends to boost the loop gain to extremely high magnitude at periodic frequencies, it is necessary to diminish its value to reduce the overall system loop gain in the high frequency range. To satisfy the imposing requirements, a low pass filter:

$$Q(s) = \frac{e^{\tau s}}{\frac{s^2}{\omega_q^2} + \frac{2\xi s}{\omega_q} + 1},$$

(16)

as given in [8] is adopted. Here, the damping ratio  $\xi = 0.707$ is chosen to ensure a flat magnitude characteristic and a quasi-linear phase shift characteristic within its bandwidth. The time advance  $\tau$  is selected to equal the effective time delay of the denominator term, i.e.,  $2\xi/\omega_q$ , so that the low pass filter achieves unity magnitude and zero phase shift at low frequencies. A larger value of the bandwidth  $\omega_q$  improves accuracy, but degrades system robustness. The selection of  $\omega_q$ should ensure that the magnitude of  $[1 - G_f(s)H(s)]Q(s)$  is less than 1 (or 0 dB).

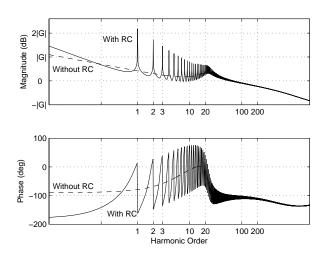

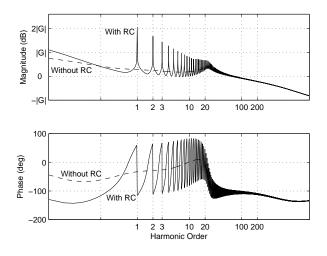

Based on the selected parameters for  $G_f(s)$  and Q(s), loop gain (14) and its Bode plot in Fig. 4 indicate that in low frequency range, the loop gain can be uplifted to very high values at the desired periodic frequencies  $k\omega_0$ , while kept low at high frequencies. However, the improvement in the loop gain at  $k\omega_0$  is achieved at the expense of a small degradation in the loop gain at non-harmonic frequencies. This is reflected in (14), which shows that the term  $1 + \frac{G_f(s)Q(s)e^{-sT}}{1-Q(s)e^{-sT}}$  will be less than unity at some intermediate frequencies where the disturbances of inverter are rare.

As for the transient state performance of the system, this can be viewed in two parts: the PID controller undertakes the response to the transient change of the system, which mainly depends on the bandwidth of the PID control system; while the response to error cancelation is dependent on the repetitive controller, denoted by the error convergence index  $[1-G_f(s)H(s)]Q(s)e^{-sT}$ . This can be understood from Fig. 3. It can be seen that with a direct channel from the feedback comparison point to the input of PID controller, the plug-in repetitive controller will not hinder the fast response of PID control to the system's transience.

#### B. Further Improvement of the VSI performance

A careful inspection of Fig. 4 shows that there is still an inherent defect with the present RC system, that is, there

Fig. 4. Bode plot of the overall system loop gain.

are discontinuous phase changes at locations of the harmonic frequencies. At the fundamental frequency, the margin between phase angle and  $-180^{\circ}$ , known as the phase angle margin, is rather small and it gets even smaller as the frequency approaches DC. Now, considering that in the VSI, the fundamental signal is the main component of both the input and disturbances, and that DC signal exists when the system is DC biased [7], the aforementioned issues become a significant problem in the stable control of the output. Although the stability problem at low frequencies is introduced by the repetitive controller, a modification of the PID controller can be performed to achieve stability, without degrading the tracking accuracy of the system.

From the phase plot in Fig. 4, it can be observed that the system with the repetitive controller has a maximum  $\pm 90^{\circ}$  phase fluctuation at harmonic frequencies, centered at that of the PID-inverter system. Hence, at low frequencies, if the phase of the PID-inverter system can be improved to  $-45^{\circ}$ , the overall system's phase at those points would reach  $-135^{\circ}$ , i.e.,  $45^{\circ}$  phase angle margin.

Such an improvement can be easily realized by incorporating a lead-lag compensation into the PID controller, which modifies the PID controller to

$$G_{cm}(s) = G_d \frac{(1 + \frac{\omega_l}{s})(1 + \frac{s}{\omega_z})}{1 + \frac{s}{\omega_p}} \times \prod_{i=1}^n \frac{1 + \frac{\alpha_i}{\omega_i}s}{1 + k_i \frac{\alpha_i}{\omega_i}s}, \quad (17)$$

where

$$\frac{1 + \frac{\alpha_i}{\omega_i}s}{1 + k_i \frac{\alpha_i}{\omega_i}s} \tag{18}$$

is a general phase-lead compensator with  $k_i < 1$ , or phase-lag compensator with  $k_i > 1$ . The number of individual compensators n, the compensated frequencies  $\omega_i$ , and parameters  $k_i$  and  $\alpha_i$ , are determined as required.

According to (14), a change in the PID-inverter loop gain  $G_c(s)G_p(s)$  will cause a corresponding variation in  $T_{rc}(s)$ . However, since the RC action still tends to make  $T_{rc}(s)$  go infinitely high at  $k\omega_0$ , the overall system loop gain with the modified PID controller will still maintain the same profile as that in the system in Fig. 4. This is reflected in Fig. 5, in which a phase angle margin larger than  $45^{\circ}$  at low frequencies is achieved, with the magnitudes at harmonic frequencies still remaining very high. Furthermore, with the error convergence index  $[1-G_f(s)H(s)]Q(s)e^{-sT}$  unchanged, the error convergence rate will not be affected by the modification of the PID controller.

Fig. 5. Improved system's loop gain with the modified PID controller.

#### C. Design of Repetitive Controller for VSI

Based on the analysis and adopted initiatives, a strategy is proposed for the design of the repetitive controller for the VSI:

*Step 1*: Optimal design of PID controller. The parameters of PID controller (13) are selected according to the conventional PID design principle to achieve optimal control performances.

Step 2: Modifying the PID controller. To ensure the stability of the RC system at low frequencies, lead-lag compensators are inserted to the PID controller to introduce at least  $135^{\circ}$ phase angle margin at DC (very close to DC) and 50 Hz.

Step 3: Design of the zero-magnitude-and-phase compensator  $G_f(s)$ . The selection of p in (15) should make  $G_f(s)$ fully compensate the H(s) within the system bandwidth, and remain at a limited magnitude above the crossover frequency.

Step 4: Construction of the low pass filter Q(s). The bandwidth  $\omega_q$  should be as high as possible while complying the stability margin between  $[1 - G_f(s)H(s)]Q(s)$  and 0 dB.

## V. SIMULATION RESULTS AND DISCUSSION

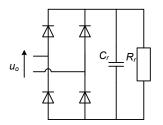

In this section, the performances of the VSI control system discussed in Section IV is evaluated. To illustrate the advantages, the PID controller and the PID-repetitive controller are applied to the same VSI for comparative purposes. The tracking performance is tested with both the resistive load and the nonlinear load (see Fig. 6). The parameters of the system is given in Table I in the Appendix.

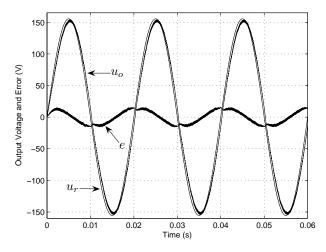

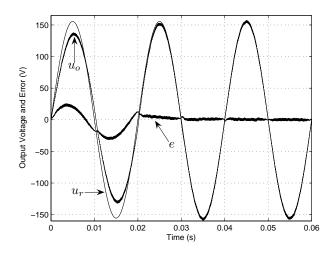

Figs. 7 and 8 show respectively the output voltage and the output voltage error waveforms of the VSI under the rated resistive load, with and without the repetitive control. It can be seen from Fig. 7 that a distinct periodic steady-state error exists in the inverter with the PID control. This is attributed

Fig. 6. Rectifier load serving as a nonlinear load.

to the incapability of the PID control in tracking the periodic reference input signal. On the other hand, Fig. 8 shows that with the PID-RC, the output voltage error decays rapidly to a negligible level within the first two cycles of the periodic signal.

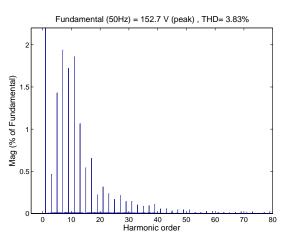

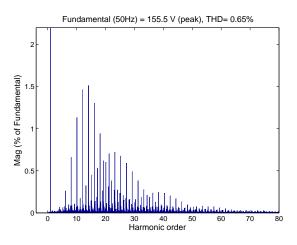

Figs. 9 and 10 show the harmonic spectrums of the output voltage under a rectifier load with the PID control and the PID-RC, respectively. Most harmonic components caused by nonlinear load occurs at the odd multiples of the fundamental frequency. It is also clearly illustrated that the THD with the RC (0.65%) in Fig. 10 is much lower than that without the RC (3.83%) in Fig. 9, and that the fundamental voltage is closer

Fig. 7. Output voltage  $u_o$ , reference voltage  $u_r$ , and output voltage error e of the VSI under resistive load with PID control.

Fig. 8. Output voltage  $u_o$ , reference voltage  $u_r$ , and output voltage error e of the VSI under resistive load with PID-RC.

Fig. 9. Harmonic spectrum of the VSI under rectifier load with PID control.

Fig. 10. Harmonic spectrum of the VSI under rectifier load with PID-RC.

to the reference. The improvement is credited to the harmonic elimination function of the RC.

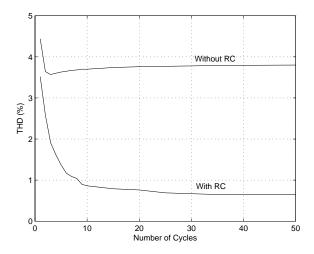

In Fig. 11, it is shown that the RC exhibits a great influence on the THD history of the output voltage under the rectifier load. It is found that the THD in the repetitive control system converges quickly to a low level, resulting in much lower values than that of the system without the RC in the steady state. The THD in the RC system declines significantly within ten cycles.

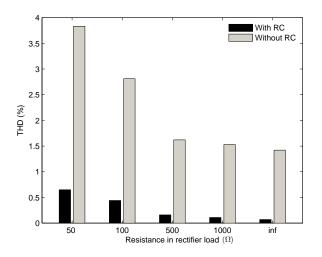

Fig. 12 shows a comparison of the THD under a rectifier load with different resistance values, with and without RC. The characteristic of suppressing THD under the nonlinear load is examined. Both systems show better THD restraints under lighter load, and the RC displays a remarkable influence on THD suppression under each load condition in comparison with the system without the RC. It is demonstrated that the RC does improve the THD performance of the system over a wide load range.

#### VI. CONCLUSION

This paper gives a detailed analysis of the harmonic elimination features of a repetitive controller and how it can effectively improve the total harmonic distortion performance of voltage source inverters. An analysis of the system from

Fig. 11. Influence of RC on THD of output voltage under rectifier load.

Fig. 12. THD of output voltage under different resistance values of rectifier load.

the frequency response viewpoint shows that there is a tradeoff between the stability and tracking accuracy properties of the repetitive control system. The proposed zero-magnitudeand-phase compensator allows optimal compensation in low frequency range while maintaining good system robustness at high frequencies. The lead-lag compensator improves the repetitive control system's stability without degrading the tracking accuracy at low frequencies. It is demonstrated both theoretically and through simulations that the repetitive control is useful for eliminating harmonic distortion in voltage source inverters.

## APPENDIX

The key parameters of the VSI are summarized in Table I. The conventional PID controller is

$$G_c(s) = \frac{(1.409e-6)s^2 + (9.097e-3)s + 13.84}{(6.139e-6)s^2 + s}$$

The modified PID controller is

$$G_{cm}(s) = \frac{(2.005e-9)s^3 + (1.32e-5)s^2 + 0.02137s + 2.561}{(8.099e-9)s^3 + (1.325e-3)s^2 + 1.008s + 6}$$

TABLE I System Parameters

| DC link voltage $V_{dc}$         | 250 V                |

|----------------------------------|----------------------|

| Switching frequency $f_s$        | 10 kHz               |

| Reference sine frequency $f$     | 50 Hz                |

| Reference voltage $U_{r(rms)}$   | 110 V                |

| Filter inductance L              | 1 mH                 |

| Filter capacitance $C$           | $20 \ \mu F$         |

| ESR of filter capacitor $r_c$    | $50 \text{ m}\Omega$ |

| Resistive load R                 | 25 Ω                 |

| Rectifier load capacitance $C_r$ | $330 \ \mu F$        |

| Rectifier load resistance $R_r$  | 50 Ω                 |

The zero magnitude and phase compensator is

$$G_f(s) = \frac{1}{H(s)} \times \frac{1e6}{s + 1e6}$$

where H(s) is the closed-loop transfer function with  $G_{cm}(s)$ . The low pass filter is

$$Q(s) = \frac{e^{0.0002s} \times 7070^2}{s^2 + 2 \times 0.707 \times 7070 \times s + 7070^2}$$

#### REFERENCES

- M. Nakano and S. Hara, "Microprocessor-based repetitive control," in *Microprocessor-Based Control Systems*, N. K. Sinha, Ed. Dordrecht: Reidel Publ. Co., 1986.

- [2] C. Y. Li, D. C. Zhang, and X. Y. Zhuang, "Theory and applications of the repetitive control," in *Proc. SICE Annual Conference*, Sapporo, Japan, Agu. 2004, pp. 27–34.

- [3] W. S. Yao and M. C. Tsai, "Analysis and estimation of tracking errors of plug-in type repetitive control systems," *IEEE Trans. Autom. Control*, vol. 50, no. 8, pp. 1190–1195, Aug. 2005.

- [4] T. Haneyoshi, A. Kawamura, and R. G. Hoft, "Waveform compensation of PWM inverter with cyclic fluctuating loads," *IEEE Trans. Ind. Appl.*, vol. 24, no. 4, pp. 582–589, Jul.–Aug. 1988.

- [5] K. Zhou, D. Wang, and K. S. Low, "Periodic errors elimination in CVCF PWM DC/AC converter systems: repetitive control approach," *IEE Proc.-Control Theory Appl.*, vol. 147, no. 6, pp. 694–700 Nov. 2000.

- [6] Y. Ye, K. Zhou, B. Zhang, D. Wang, and J. Wang, "High-performance repetitive control of PWM DC – AC converters with real-time phase-lead FIR filter," *IEEE Trans. Circuits Syst. II*, vol. 53, no. 8, pp. 768–772, Aug. 2006.

- [7] K. Zhang, Y. Kang, J. Xiong, and J. Chen, "Direct repetitive control of PWM inverter for UPS purpose," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 784–792, May. 2003.

- [8] K. Srinivasan and F. R. Shaw, "Analysis and design of repetitive control systems using the regeneration spectrum," ASME J. Dynam. Syst. Meas. Control, vol. 113, no. 2, pp. 216–222, Jun. 1991.