# Optimal microscale water cooled heat sinks for targeted alleviation of hotspot in microprocessors

Chander Shekhar SHARMA <sup>1</sup>, Manish K. TIWARI <sup>2</sup>, Dimos POULIKAKOS <sup>1,\*</sup>

\* Corresponding author: Tel.: +41 44 632 27 38; Fax: +41 44 632 11 76; Email: dpoulikakos@ethz.ch 1: Department of Mechanical and Process Engineering, ETH Zurich, 8092 Zurich, Switzerland 2: Department of Mechanical Engineering, University College London (UCL), Torrington Place, London WC1E 7JE, UK

Abstract Hotspots in microprocessors arise due to non-uniform utilization of the underlying integrated circuits during chip operation. Conventional liquid cooling using microchannels leads to undercooling of the hotspot areas and overcooling of the background area of the chip resulting in excessive temperature gradients across the chip. These in turn adversely affect the chip performance and reliability. This problem becomes even more acute in multi-core processors where most of the processing power is concentrated in specific regions of the chip called as cores. We present a 1-dimensional model for quick design of a microchannel heat sink for targeted, single-phase liquid cooling of hotspots in microprocessors. The method utilizes simplifying assumptions and analytical equations to arrive at the first estimate of a microchannel heat sink design that distributes the cooling capacity of the heat sink by adapting the coolant flow and microchannel size distributions to the microprocessor power map. This distributed cooling in turn minimizes the chip temperature gradient. The method is formulated to generate a heat sink design for an arbitrary chip power map and hence can be readily utilized for different chip architectures. It involves optimization of microchannel widths for various zones of the chip power map under the operational constraints of maximum pressure drop limit for the heat sink. Additionally, it ensures that the coolant flows uninterrupted through its entire travel length consisting of microchannels of varying widths. The resulting first design estimate significantly reduces the computational effort involved in any subsequent CFD analysis required to fine tune the design for more complex flow situations arising, for example, in manifold microchannel heat sinks.

**Keywords:** Microchannels, Hotspot-targeted cooling, Electronics cooling, Hotspots

### 1. Introduction

Moore's law has driven the performance increase in microprocessors over the last many decades (Moore, 1965). However, the inability to follow the Dennard scaling for supply voltage while downscaling the transistor has progressively increased chip heat dissipation densities (Dennard et al., 2007). This in-turn has shifted the focus of heat transfer community from air cooling to single and two-phase liquid cooling to maintain chip reliability (JEDEC, 2010; Sharma et al., 2012). Starting with the seminal work of Tuckerman and Pease (Tuckerman and Pease, 1981), extensive research has been done on liquid cooling including investigations on traditional microchannel (TMC) heat sinks and manifold microchannel (MMC) heat sinks. In TMC heat sinks, the coolant enters the heat transfer structure through a single inlet and leaves through a single outlet (Lee et al., 2005). In MMC heat sinks, the coolant circulates through multiple and alternating inlet and outlet slot nozzles thus improving the heat transfer at comparatively lower pressure drops. (Copeland et al., 1997; Escher et al., 2010; Kermani et al., 2009; Ryu et al., 2003; Sharma et al., 2013).

Most of the research on liquid cooling of chips has focused on maximum junction temperature  $(T_{J,max})$  reduction under uniform heat flux dissipation conditions. However, it is also necessary that the chip temperature is spatially as uniform as possible (i.e. approaching the isothermal chip condition). Large temperature gradients increase thermal stresses in the chip to substrate or heat sink

interface, reduce electronic reliability in regions of high temperature and create circuit imbalances in CMOS devices (JEDEC, 2010). A few studies have focused on reducing temperature non-uniformity across the microprocessor  $\left(\Delta T_{J,max} = T_{J,max} - T_{J,min}\right)$ ; however, under a uniform chip heat flux map (Barrau et al., 2010; Hetsroni et al., 2002; Rubio-Jimenez et al., 2012).

The large increase in chip heat flux dissipation in the last decade has resulted in an industry-wide shift towards multicore microprocessors (Esmaeilzadeh et al., 2012). In a typical multicore microprocessor, the heat flux dissipation in the cores (termed as hotspots) is multiple times higher than the rest of the chip (termed as background) thus increasing the criticality of chip temperature compared non-uniformity as microprocessors. A few single phase liquid cooling approaches have been proposed in the past for preferential cooling of hotspots (termed as hotspot-targeted cooling) with varying degree of success (Brunschwiler et al., 2009; Lee and Garimella, 2005; Lee et al., 2013)

Embedded liquid cooling (ELC), in which the coolant is circulated through microchannels etched into the backside of the chip, is an effective approach to target the hotspots. ELC compares favorably against conventional backside attached cooling which suffers from high resistance due to thermal interface material (TIM) (Dang et al., 2006; Etessam-Yazdani et al., 2008; Mingyuan and Huang, 2007).

In this paper, we propose a one-dimensional model for estimation of a novel; single-phase liquid-cooled, hotspot targeted microchannel heat sink for modern day microprocessors. The model provides a computationally efficient method to quickly obtain hotspot-targeted microchannel and flow rate distributions. The model is formulated as a generalized design method and is applicable to ELC as well as conventional heat sinks on one hand and TMC as well as MMC heat sinks on the other.

## 2. Analytical design method

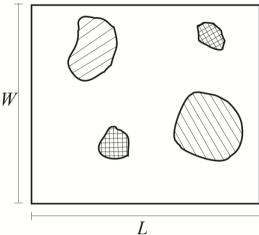

Consider an arbitrary microprocessor power map as shown in Fig.1. In the figure, each shaded area represents a region dissipating a different level of heat flux that is multiple times higher than that dissipated in the unshaded area (background).

**Figure 1:** An arbitrary non-uniform power map with regions of high heat flux

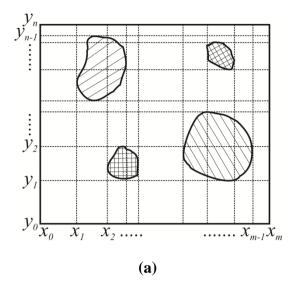

This power map can be discretized such that each cell of the discretized map encompasses an area of nearly constant heat flux. Figure 2(a) illustrates the coarsest level of discretization for the power map in Fig. 1 and Fig. 2(b) illustrates the (i,j)<sup>th</sup> cell and the nomenclature adopted in this work for the discretized power map.

The discretization can be refined depending upon the desired resolution of the calculated temperature map. However, the highest degree of refinement is limited by the following constraint:

$$\Delta y_i \ge w_{c,max} + w_{w,max} \tag{1}$$

With the flow direction as shown in Fig. 2(b), the average coolant temperature in the (i,j)<sup>th</sup> cell is given by Eq.(2) and the average junction temperature, assuming negligible heat spreading, is obtained in Eq.(3) below:

$$T_{f,(i,j)} = T_{f,in} + \sum_{k=1}^{j-1} \frac{Q_{(i,k)}^{"} \Delta y_i \Delta x_k}{\varphi_i \, m \, cp_f} + \frac{Q_{(i,j)}^{"} \Delta y_i \Delta x_j}{2\varphi_i \, m \, cp_f}$$

(2)

$$T_{J,(i,j)} = T_{f,(i,j)} + Q''_{(i,j)}R_{\lambda} + Q''_{(i,j)}R''_{\alpha,(i,j)}$$

(3)

where,  $\mathbf{R}_{\lambda}$ , the total conduction resistance between junctions and base of microchannels,

**Figure 2: (a)** Discretization of the power map **(b)**  $(i,j)^{th}$  cell of the discretized power map

is given by summation of all the conduction resistances in series (such as those of silicon chip thickness, TIM and heat sink base):

$$\mathbf{R}_{\lambda} = \sum_{l} \frac{\Delta z_{l}}{\lambda_{l}} \tag{4}$$

$R_{\alpha,(i,j)}^{"}$  is the convective resistance for heat transfer to the coolant. Accounting for the fin resistance and assuming adiabatic fin tops,  $R_{\alpha,(i,j)}^{"}$  is given by (Escher et al., 2010):

$$R''_{\alpha,(i,j)} = \frac{w_{c,(i,j)} + w_{w,(i,j)}}{\alpha_{(i,j)}w_{c,(i,j)} + 2\alpha_{(i,j)}h_c\gamma_{(i,j)}}$$

(5)

where  $\gamma_{(i,j)}$ , the fin efficiency, is given by:

$$\gamma_{(i,j)} = \frac{\tanh(mh_c)}{mh_c}, m = \sqrt{\frac{2\alpha_{(i,j)}(w_{w,(i,j)} + h_c)}{\lambda_w w_{w,(i,j)} h_c}}$$

(6)

and  $\alpha_{(i,j)}$ , the heat transfer coefficient can be calculated as:

$$\alpha_{(i,j)} = \frac{Nu_{D,(i,j)}\lambda_f}{D_{c,(i,j)}} \tag{7}$$

$D_{c,(i,j)}$  is an equivalent length scale for the microchannel cross-section and its definition depends upon the form of correlation available for  $Nu_{D,(i,j)}$ .

With these thermal characteristics of the heat sink in place, the design of the hotspottargeted heat sink involves determination of geometrical parameters  $w_{c,(i,j)}, w_{w,(i,j)}$  and operational parameters m,  $\varphi_i$  such that,  $T_{J,max}$ , as well as chip wide temperature gradient  $\Delta T_{J,max}$  are minimized, while satisfying the following constraints

$$\begin{aligned} & w_{c,min} \leq w_{c,(i,j)} \leq w_{c,max} \\ & w_{w,min} \leq w_{w,(i,j)} \leq w_{w,max} \\ & \Delta P \leq \Delta P_{limit} \end{aligned} \tag{8}$$

The geometrical and operational design parameters are determined by separately considering the three terms in Eq. (3) as discussed in the following subsections.

#### **2.1 Determination of** $\varphi_i$

The first step in minimizing  $T_{J,max}$  and  $\Delta T_{J,max}$  is minimization of bulk resistance that drives the increase in coolant temperature  $T_{f,(i,j)}$  (the first term in Eq. (3) and given by Eq.(2)). This is achieved by equalizing the fluid temperature rise  $T_{f,(i,m)} - T_{f,in}$  for all n rows. This gives, n equations in n unknown variables  $\varphi_i$ :

$$\sum_{i=1}^{n} \varphi_{i} = 1$$

for  $i = 2$  to  $n$

$$\frac{\Delta y_{i}}{\varphi_{i}} \left( \sum_{k=1}^{m-1} Q_{(i,k)}^{"} \Delta x_{k} + \frac{Q_{(i,m)}^{"} \Delta x_{m}}{2} \right) =$$

$$\frac{\Delta y_{1}}{\varphi_{1}} \left( \sum_{k=1}^{m-1} Q_{(1,k)}^{"} \Delta x_{k} + \frac{Q_{(1,m)}^{"} \Delta x_{m}}{2} \right)$$

(9)

With  $\varphi_i$  determined as above,  $T_{f,(i,j)}$  in

Eq. (3) are fixed. The second term  $Q_{(i,j)}^{"}R_{\lambda}$  is fixed for a given power map and cooling architecture. Hence, only the convective resistance term  $Q_{(i,j)}^{"}R_{\alpha,(i,j)}^{"}$  can be controlled which leads to determination of the channel widths  $w_{c,(i,j)}$  as explained in the following subsection.

# 2.2 Determination of $w_{w,(i,j)}$ and $w_{c,(i,j)}$

The channel wall widths  $w_{w,(i,j)}$  can be independently fixed such that the overall pressure drop is minimized as below:

$$w_{w,(i,j)} = w_{w,min} \tag{10}$$

As a result, the distribution of junction temperatures  $T_{J,(i,j)}$  is determined only by the distribution of channel widths  $w_{c,(i,j)}$  through the convective resistance term in Eq.(3). This term is minimized under the following condition:

$$Q''_{(i,j)}R''_{\alpha,(i,j)} = Q''_{max}R''_{\alpha,min} = Q''_{min}R''_{\alpha,max}$$

(11) where the minimum convective resistance  $R''_{\alpha,min}$  can be fixed as below:

$$R_{\alpha,min}^{"} = \frac{w_{c,min} + w_{w,min}}{\alpha_{max} w_{c,min} + 2\alpha_{max} h_c \gamma_{min}}$$

(12)

Eqs. (11), (5) and (10) result in nm-1 non-linear equations for nm-1 unknowns  $w_{c,(i,j)}$ :

$$\frac{w_{c,(i,j)} + w_{w,min}}{\alpha_{(i,j)}w_{c,(i,j)} + 2\alpha_{(i,j)}h_c\gamma_{(i,j)}} = \frac{Q''_{max}R''_{\alpha,min}}{Q''_{(i,j)}} \quad (13)$$

with  $\gamma_{(i,j)}$  and  $\alpha_{(i,j)}$  given by Eqs. (6) and (7).

Since the channel widths change along flow direction, it is important that the coolant flows uninterrupted in every row (i.e. does not run into a wall). This is ensured by simply modifying  $w_{c,(i,j)}$  values from Eq. (13) such that the microchannel pitch in any  $(i,j)^{th}$  cell  $w_{c,(i,j)} + w_{w,min}$  is related to the pitches in adjacent upstream and downstream cells,  $w_{c,(i,j-1)} + w_{w,min}$  and  $w_{c,(i,j+1)} + w_{w,min}$ , through integral multiples.

## **2.3 Determination of** m

The only design parameter that remains to

be determined is the total coolant flow rate m. m can be determined such that the maximum pressure drop in the microchannels does not violate the pressure drop constraint in Eq. (8) i.e.

$$\max_{i} \left( \Delta P_i \right) \le \Delta P_{limit} \tag{14}$$

Pressure drops  $\Delta P_i$  can be expressed in terms of Fanning friction factor, as below:

$$\Delta P_i = \sum_{j=1}^{m} \frac{2\mu (f \operatorname{Re}_D)_{(i,j)} \Delta x_j}{D_{c,(i,j)}^2} \left( \frac{\dot{\varphi_i m p_{(i,j)}}}{\rho_f \Delta y_i A_{c,(i,j)}} \right) (15)$$

where  $p_{(i,j)} = w_{c,(i,j)} + w_{w,min}$  is the microchannel pitch and  $A_{c,(i,j)} = w_{c,(i,j)}h_c$  is the channel cross-sectional area. Equations (14) and (15) determine highest allowable m.

#### **2.4** Coolant distribution according to $\varphi_i$

Since the pressure drops  $\Delta P_i$  are bound to be different, the flow distribution  $\varphi_i$  can only be realized if the flow resistances of all parallel n rows are equal. This can be achieved by introducing additional resistances in all rows such that:

$$\Delta P_i + \Delta P_i^* = \max_i (\Delta P_i) = \Delta P_{limit}$$

(16)

where  $\Delta P_i^*$  is the pressure drop due to the additional flow resistance introduced in the i<sup>th</sup> row. This is a key idea in our approach to hotspot targeted cooling.

The additional resistances can be flow throttling zones either in the manifold that supplies the coolant or within the microchannel structure itself in the form of fine channels. In the latter case, however, it has to be ensured that the flow throttling channels do not interrupt the flow as discussed in section 2.2. Additionally, the throttling zones have to be positioned such that the enhanced cooling caused by the microchannels does not affect  $\Delta T_{I,max}$ . Note that  $\Delta P_i^* = 0$  for the i<sup>th</sup> row with  $\Delta P_i = \max_i (\Delta P_i)$ . Similar to Eq.(15),  $\Delta P_i^*$  can also be expressed as below:

$$\Delta P_i^* = \frac{2\mu \left(f \operatorname{Re}_D\right)_i^* L_i^*}{\left(D_i^*\right)^2} \left(\frac{\varphi_i m}{\rho_f A_i^* N_i^*}\right)$$

(17)

where the superscript '\*' indicates geometrical and operational parameters for the flow throttling zone.

#### 2.5 Developed flow assumption

For traditional heat sinks, the flow can be assumed to be fully developed inside the microchannels. Hence,  $\mathbf{w}_{c,(i,j)}$  values

determined by Eq. (13) are independent of m and the heat sink design is completed in a single iteration.

### 2.7 Developing flow

In more complex flow geometries such as MMC sinks, the flow inside the microchannels is developing for a large part of the channel length. In this case, the heat transfer coefficients  $\alpha_{(i,j)}$  and hence the microchannel

widths  $w_{c,(i,j)}$  are no longer independent of m. This necessitates the following recursive procedure to determine the optimal geometrical and operational parameters: (a) Assume m (b) determine  $w_{c,(i,j)}$  using Eq. (13) (c) revise channel widths to ensure uninterrupted flow (d) check the pressure drop constraint in Eq. (14). If the inequality (14) is satisfied, then increase m and repeat steps (a)-(d). These steps are repeated till the highest m is reached that satisfies the constraint (14).

# 3. Exemplar design for an arbitrary power map cooled by TMC heat sink

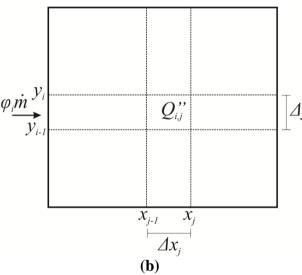

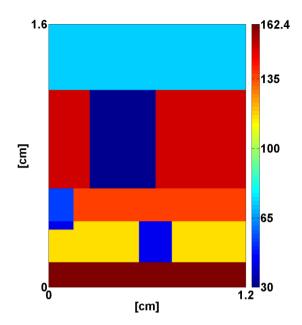

In this section, we illustrate the use of the one-dimensional model to design a hotspot targeted embedded TMC structure. We consider a highly non-uniform power map shown in Fig. 3.

The coolant is assumed to be water with the constant properties:  $\rho_f$ = 998.2 kg/m<sup>3</sup>,  $\mu_f$  = 0.001 Pa.s, and  $cp_f$  = 4180 J/kgK. The thermal conductivity of Silicon is also assumed to be

constant ( $\lambda_l = 150 \text{ W/mK}$ ). Following design constraints have been adopted,  $w_{c,min} = w_{w,min} = 30 \text{ } \mu\text{m}$ ,  $\Delta P_{limit} = 0.5 \text{ } \text{bar}$ . The unetched chip thickness  $\Delta z_l$  and microchannel height  $h_c$  are 225  $\mu$ m and 300  $\mu$ m respectively. Flow is assumed to be fully developed and the correlations for Nu and f Re, for rectangular channels, are adopted from Shah and London (Shah and London, 1978). These correlations are defined in terms of hydraulic diameter; hence:

$$D_{c,(i,j)} = \frac{2w_{c,(i,j)}h_c}{\left(w_{c,(i,j)} + w_{w,min}\right)}$$

$$D_i^* = \frac{2w_{c,i}^*h_c}{\left(w_{c,i}^* + w_{w,i}^*\right)}$$

(18)

where  $w_{c,i}^*$  and  $w_{c,i}^*$  are channel and wall widths of the flow throttling channels.

Using the coarsest level of discretization similar to Fig.2, and following the sections 2.1 and 2.2, we obtain a set of non-linear system of equations for  $w_{c,(i,j)}$  (Eq.(13)) that is solved using MATLAB. The  $w_{c,(i,j)}$  values so obtained are modified to ensure uninterrupted coolant flow (refer section 2.2). The resulting hotspottargeted  $w_c$  distribution is shown in Fig. 4.

**Figure 3:** An exemplar non-uniform power map with heat flux dissipation in W/cm<sup>2</sup>.

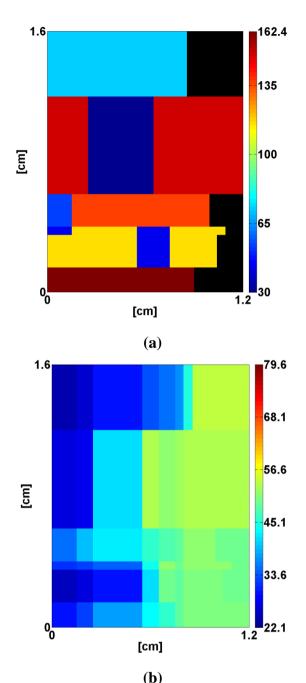

**Figure 4:**  $w_c$  distribution for the power map in Fig. 3

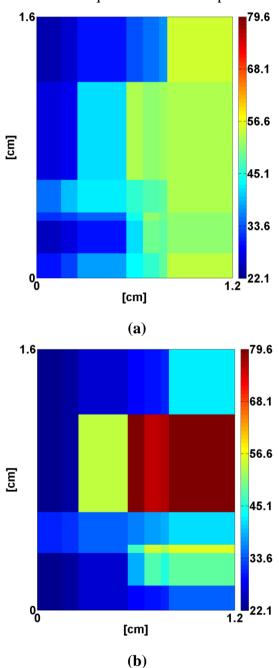

The  $\Delta P_{limit}$  constraint limits  $\dot{m}$  to 1.17 g/s (0.07 l/min). Figure 5(a) shows the temperature map of the chip corresponding to the hotspot targeted microchannel structure at 0.07 l/min. The performance of the optimal design is compared against a base case consisting of uniformly fine, embedded microchannels ( $w_c = 30 \mu m$ ) and uniform flow distribution. The base case performance for the same pumping power as the design in Fig. 4 is shown in Fig. 5(b).

Figure 5 illustrates that, as compared to the base case, hotspot-targeted design reduces  $T_{J,max}$  from 79.6°C to 55.3°C and  $\Delta T_{J,max}$  from 57.5°C to 31.4°C - an improvement of 45%.

Following section 2.4, the pressure equalization is achieved by introducing flow throttling zones in the microchannel The structure. throttling zones positioned towards the coolant outlet and are formed by merging every two channels in each row into a fine microchannel of 30 um width, i.e.  $w_{ai}^* = 30$ μm  $w_{w,i}^* = 2(w_{c,(i,m)} + w_{w,min}) - w_{c,i}^*$ Throttling zone lengths  $L_i^*$  are obtained using Eq.(16). Figure 6(a) shows the microchannel structure along with flow throttling zones in black color. Figure 6(b) shows the temperature map for the complete design which clearly shows that the additional cooling from the throttling zones does not adversely affect the performance of the hotspot targeted design.

In future work, this design approach will be validated against results from experiments on embedded liquid cooled test chips.

Figure 5 Temperature maps (a): hotspottargeted design (b) base case. The same temperature scale for both the figures illustrates reduction in  $T_{J,max}$  and  $\Delta T_{J,max}$ .

Coolant flows from left to right.

Figure 6(a): Throttling zones towards coolant outlet (compare with Fig. 4) (b) Temperature map for the design shown in **Fig.6(a)** (compare with **Fig. 5(a)**)

#### 4. Conclusions

A 1-dimensional model for quick design of a single-phase, liquid cooled, hotspot-targeted microchannel heat sink has been presented. The model is a generalized method for developed design developing flow situations encountered in TMC and MMC heat sinks respectively, for arbitrary chip power maps for serial and multicore microprocessors and for conventional as well as embedded cooling. The potential of the model has been demonstrated for a non-uniform chip power map cooled by an embedded TMC structure.

#### **Nomenclature**

cross-sectional area of each parallel  $A_i^*$ flow path in the throttling zone (m<sup>2</sup>)

Dequivalent cross-sectional length scale (m)

total coolant flow (kg/s) m

microchannel height (m)

i, j, kindices

length of throttling zone in i<sup>th</sup> row (m)  $L_i^*$

number of rows and columns in the n, mdiscretized power map

$N_{i}^{*}$ number of parallel flow paths in throttling zone

Nusselt number defined for D  $Nu_D$

heat flux in the  $(i,j)^{th}$  cell  $(W/m^2)$  $Q_{i,i}^{"}$

pressure drop (Pa)  $\Delta P$

conduction resistance (m<sup>2</sup>K/W)  $R_{\lambda}$

convection resistance (m<sup>2</sup>K/W)  $R_{\alpha}$

junction temperature (K)  $T_{J}$

coolant temperature (K)  $T_f$

microchannel width (m)  $w_c$

$w_w$

$\Delta z_I$

microchannel wall width (m) thickness of l<sup>th</sup> layer (m) heat transfer coefficient (W/m<sup>2</sup>K) α

fraction of *m* directed into the i<sup>th</sup> row  $\varphi_i$

fin efficiency γ

$\lambda_f, \lambda_w$  fluid and solid thermal conductivities in heat sink (W/mK)

thermal conductivity of lth layer in heat  $\lambda_{l}$ transfer path from junctions microchannel base (W/mK)

### References

IBM Unveils New POWER7 Systems To Manage Increasingly Data-Intensive Services. http://www-

03.ibm.com/press/us/en/pressrelease/29315.ws

Barrau, J., Chemisana, D., Rosell, J., Tadrist, L., Ibañez, M., 2010. An experimental study of a new hybrid jet impingement/micro-channel cooling scheme. Applied Thermal Engineering 30, 2058-2066.

Brunschwiler, T., Rothuizen, H., Paredes, S., Michel, B., Colgan, E., Bezama, P., 2009. Hotspot-adapted Cold Plates to Maximize System Efficiency, 15th International Workshop on Thermal Investigations of ICs and Systems, 2009. THERMINIC 2009., pp. 150-156.

Copeland, D., Behnia, M., Nakayama, W., 1997. Manifold Microchannel Heat Sinks: Isothermal Analysis. IEEE Trans Compon Pack Technol., Part A 20, 96-102.

Dang, B., Bakir, M.S., Meindl, J.D., 2006. Integrated Thermal-fluidic I/O Interconnects for an On-chip Microchannel Heat Sink. IEEE Electron Device Lett. 27, 117-119.

Dennard, R.H., Cai, J., Kumar, A., 2007. A Perspective on Today's Scaling Challenges and Possible Future Directions. Solid-State Electron. 51, 518-525.

Escher, W., Michel, B., Poulikakos, D., 2010. A Novel High Performance, Ultra Thin Heat Sink for Electronics. Int. J. Heat Fluid Flow 31, 586-598.

Esmaeilzadeh, H., Blem, E., Ren, #233, Amant, e.S., Sankaralingam, K., Burger, D., 2012. Power Limitations and Dark Silicon Challenge the Future of Multicore. ACM Trans. Comput. Syst. 30, 1-27.

Etessam-Yazdani, K., Asheghi, M., Hamann, H.F., 2008. Investigation of the Impact of Power Granularity on Chip Thermal Modeling Using White Noise Analysis. IEEE Trans Compon Pack Technol. 31, 211-215.

Hetsroni, G., Mosyak, A., Segal, Z., Ziskind, G., 2002. A Uniform Temperature Heat Sink for Cooling of Electronic Devices. Int. J. Heat Mass Transfer 45, 3275-3286.

JEDEC, 2010. Failure Mechanisms and Models for Semiconductor Devices, in: JEDEC (Ed.), pp. 1-9,68-72.

Kermani, E., Dessiatoun, S., Shooshtari, A., Ohadi, M.M., 2009. Experimental investigation of heat transfer performance of a manifold microchannel heat sink for cooling of concentrated solar cells, Electronic Components and Technology Conference, 2009. ECTC 2009. 59th, pp. 453-459.

Lee, P.-S., Garimella, S.V., 2005. Hot-Spot

Thermal Management With Flow Modulation in a Microchannel Heat Sink, ASME International Mechanical Engineering Congress and Exposition ASME, Orlando, Florida, USA, pp. 643-647.

Lee, P.-S., Garimella, S.V., Liu, D., 2005. Investigation of Heat Transfer in Rectangular Microchannels. Int. J. Heat Mass Transf. 48, 1688-1704.

Lee, Y.J., Lee, P.S., Chou, S.K., 2013. Hotspot Mitigating With Obliquely Finned Microchannel Heat Sink---An Experimental Study. IEEE Trans Compon Pack Technol. 3, 1332 - 1341.

Mingyuan, Z., Huang, Z.R., 2007. Design of On-Chip Microchannel Fluidic Cooling Structures, Electronic Components and Technology Conference, 2007. ECTC '07. Proceedings. 57th, pp. 2017-2023.

Moore, G.E., 1965. Cramming More Components Onto Integrated Circuits. Electronics 38, 114-117.

Rubio-Jimenez, C.A., Kandlikar, S.G., Hernandez-Guerrero, A., 2012. Numerical Analysis of Novel Micro Pin Fin Heat Sink With Variable Fin Density. IEEE Trans. Compon. Pack. Technol. 2, 825-833.

Ryu, J.H., Choi, D.H., Kim, S.J., 2003. Three-dimensional Numerical Optimization of a Manifold Microchannel Heat Sink. Int. J. Heat Mass Transf. 46, 1553-1562.

Shah, R.K., London, A.L., 1978. Laminar flow forced convection in ducts. Academic Press, New York.

Sharma, C.S., Tiwari, M.K., Michel, B., Poulikakos, D., 2013. Thermofluidics and Energetics of a Manifold Microchannel Heat Sink for Electronics With Recovered Hot Water as Working Fluid. Int. J. Heat Mass Transfer 58, 135-151.

Sharma, C.S., Zimmermann, S., Tiwari, M.K., Michel, B., Poulikakos, D., 2012. Optimal Thermal Operation of Liquid-cooled Electronic Chips. Int. J. Heat Mass Transfer 55, 1957-1969.

Tuckerman, D.B., Pease, R.F.W., 1981. High-Performance Heat Sinking for VLSI. IEEE Electron Device Lett. 2, 126-129.