# Optimization of OFET Performance with Pentacene as Organic Material

Abhishek Singh<sup>1</sup>, Manish Kumar Singh<sup>2\*</sup>

<sup>1,2\*</sup>Electronics Engineering Department, Harcourt Butler Technical University, Kanpur, UP, INDIA-208002

\*Corresponding author's e-mail: manish.rs.mst14@iitbhu.ac.in

Abstract— Pentacene is widely used in organic transistors as an organic semiconductor material. The conductivity of pentacene is enhanced in recent days, which helps in improving the device characteristics of organic transistors providing additional benefit of low-cost and flexible devices. Modeling and simulation of such devices are constructive in analyzing device characteristics. Here, in this paper modeling and simulation of four different configurations of organic transistor – two on the basis of the bottom gate and two on the basis of the top gate – is done in order to analyze the transfer and output characteristics. Off current of  $10^{-15}$  A, and low subthreshold swing of 0.347 V/decade was observed.

Keywords— Flexible electronics, finite element modeling, top gate configuration, bottom gate configuration, organic transistors.

#### 1. Introduction

Technology is enhancing at a rapid pace, and miniaturization of the devices is also done to build more compact products and to increase a more significant number of transistors on integrated circuits (ICs). Organic electronics have emerged in the last decade, and it has opened a new field of flexible electronics enabling a higher level of miniaturization compared to conventional electronics. Devices made in organic electronics provide certain extra features compared to conventional electronics such as – processing at low-temperatures, low cost, mechanical flexibility, high compatibility with various flexible substrates – glass, paper, plastic, and so on [1-6]. Here in this work, a comparison of organic transistors is made depending on various geometries of the organic transistors.

An organic transistor consists of organic semiconductor (OSC) material as an active layer material where channel formation takes place. Output current is modulated by varying the voltages applied across – source, drain and gate; thus, it's also known as the voltage-controlled current device. These transistors work in the accumulation mode of operation, and channel formation takes place due to the accumulation of the charges in the OSC material when the gate voltage above the threshold is applied. On the basis of, electrodes location with respect to OSC material and position of gate terminal in the device, these are classified into the top gate and bottom gate configuration devices [7-9].

Various OSC material that can be used in organic field effect transistors are - Tetracene, Anthracene, Rubrene, Fullerene, Pentacene, graphene and so on. Different materials provide variation in properties such as compatibility level with various substrates. lab processability, environmental stability, mobility and so on [8]. Pentacene is lab processable, highly stable, provides high compatibility with flexible substrates and novel material like graphene, and has high hole mobility and due to these properties, it has been taken as active layer material here in modelling different device structures. Graphene can also be used as OSC material to obtain maximum current in the milliampere range and enhanced on/off ratio. Graphene is highly compatible with pentacene and it can be used along with pentacene forming hybrid OSC material [10-11].

### 2. Structure of Device

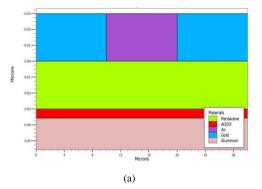

Organic transistor or Organic field effect transistor (OFET) having gate terminal at bottom of device is known as bottom gate configuration of organic transistor. When, drain & source electrodes are placed at top of OSC material then it's known as top contact bottom gate device and when the drain & source electrodes are placed at the bottom of OSC material then it's known as bottom contact bottom-gate organic transistor.

In a similar way OFET having gate at top of device is known as top gate configuration and based on the location of drain & source electrodes with respect to OSC material; it is also further divided into top contact and bottom contact. Two-dimensional modulated device structure of all the four different device structure is shown below in figure 1.

# Asian Journal of Convergence in Technology ISSN NO: 2350-1146 I.F-5.11

Figure 1. Modulated two-dimensional device structures (a) Bottom gate top contact (BGTC), (b) Bottom gate bottom contact (BGBC), (c) Top gate top contact (TGTC), and (d) Top gate bottom contact (TGBC).

Modeling and simulation of these different device structures are done using SILVACO ATLAS TCAD tool, it consists of various models and here in this work Poole-Frenkel mobility model was used in tool. Pentacene was used as the active layer material in these organic transistors, and Aluminium dioxide ( $Al_2O_3$ ) was taken as the dielectric material. Various parameters of modeling are listed in Table 1, and device specifications are listed in Table 2 [12-16].

| TABLE 1. | VARIOUS | PARAM | IETERS | OF | MODEL | ING A | AND |

|----------|---------|-------|--------|----|-------|-------|-----|

|          |         | SIMU  | ATION  |    |       |       |     |

| Parameters                                                               | Values                             |

|--------------------------------------------------------------------------|------------------------------------|

| Effective density of states in conduction $(N_c)$ & valence $(N_v)$ band | $1 \times 10^{21} \text{ cm}^{-3}$ |

| Bandgap at 300K                     | 2.8 eV                             |

|-------------------------------------|------------------------------------|

| Doping concentration                | $7 \times 10^{17}  \text{cm}^{-3}$ |

| Permittivity of pentacene           | 4.0                                |

| The work function of Au (Source &   | 5.1                                |

| Drain)                              |                                    |

| Al work function (Gate)             | 4.28                               |

| Poole-Frenkel factor (hole)         | $7.75 	imes 10^{-5}$               |

|                                     | eV(cm/V) <sup>1/2</sup>            |

| Zero field activation energy (hole) | $1.79 \times 10^{-2} \text{ eV}$   |

TABLE 2. VARIOUS DEVICE DIMENSIONS USED IN THE

BOTTOM-GATE CONFIGURATION

| <b>Dimensional Parameters</b>      | Values |  |  |

|------------------------------------|--------|--|--|

| Drain & source electrode thickness | 30 µm  |  |  |

| Gate electrode thickness           | 20 µm  |  |  |

| Length of channel                  | 10 µm  |  |  |

| Width of channel                   | 220 µm |  |  |

| Organic semiconductor thickness    | 30 nm  |  |  |

| Dielectric thickness               | 5.7 nm |  |  |

The transfer curve and output curve of the modeled device were obtained, and comparison was made for both the top and bottom gate configuration of devices.

# 3. Results and Discussion

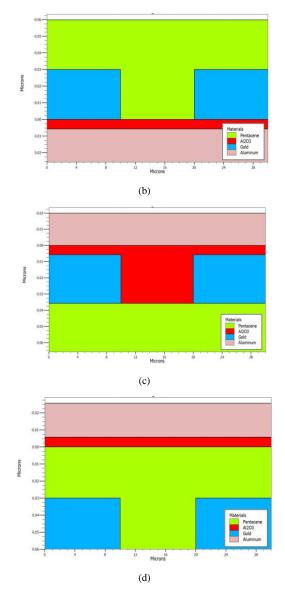

# 3A. Bottom gate configuration

Gate voltage was swept from 0V to -20V to obtain the transfer curve of both the device structures. The output curve was obtained by varying drain voltage from 0V to -20V and gate voltage variation from 0V to -10V having a step size of -2.5V. These curves are shown in figure 2.

2

## Asian Journal of Convergence in Technology ISSN NO: 2350-1146 I.F-5.11

Figure 2. Electrical characteristics curves for bottom gate device configuration where BGTC is bottom gate top contact and BGBC is bottom gate bottom contact, (a) Transfer Curve, and (b) Output curve.

It can be seen clearly from figure 2 that curves obtained for both the configurations are approximately the same, but a slight variation is observed in both the curves and bottom gate bottom contact shows better results compared to bottom gate top contact device. This variation is due to the difference in the contact resistance of both device structures.

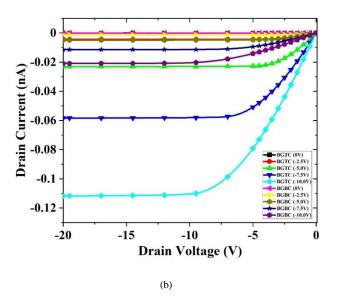

#### 3B. Top gate configuration

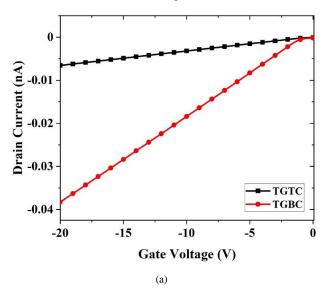

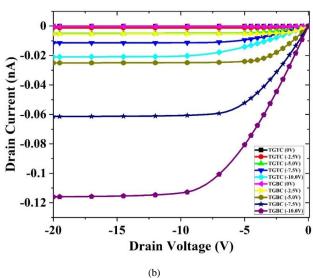

Gate voltage was varied from 0V to -20V to obtain the transfer curve of both the structures. The output curve was obtained by ranging drain voltage from 0V to -20V and gate voltage variation from 0V to -10V having a step size of -2.5V. These curves are shown in figure 3.

Volume VI Issue III

Figure 3. Electrical characteristics curves for top gate configuration where TGTC is top gate top contact and TGBC is top gate bottom contact, (a) Transfer curve, and (b) Output curve.

Figure 3 clearly shows that there are variations in transfer curves and output curves. At lower voltage ranges, results obtained in both the configurations are approximately but, variations were observed at higher applied voltages. This variation in results is due to the device geometry and placement of the electrodes with respect to OSC material, which in turn affects contact resistance, affecting the overall performance of the device at a higher voltage range.

Various electrical characteristics observed in all the four different device configurations were recorded and are stated in table 3.

| Device<br>Type                                | Thresh<br>old<br>Voltag<br>e (V) | I <sub>ON</sub>               | I <sub>OFF</sub>              | I <sub>ON</sub> /I <sub>OF</sub><br>F | Subt<br>hresh<br>old<br>swing<br>(V/de<br>cade) |

|-----------------------------------------------|----------------------------------|-------------------------------|-------------------------------|---------------------------------------|-------------------------------------------------|

| Bottom<br>gate top<br>contact<br>(BGTC)       | -0.525                           | -3.785<br>× 10 <sup>-11</sup> | -5.424<br>× 10 <sup>-15</sup> | 6.97 × 10 <sup>3</sup>                | 0.347                                           |

| Bottom<br>gate<br>bottom<br>contact<br>(BGBC) | -0.494                           | -4.009<br>× 10 <sup>-11</sup> | -1.757<br>× 10 <sup>-13</sup> | $2.28 \times 10^2$                    | 1.314                                           |

TABLE 3. ELECTRICAL CHARACTERISTICS OF VARIOUS DEVICE CONFIGURATIONS

| Top gate | -0.026 | -6.545              | -3.796              | 1.72 ×          | 0.874 |

|----------|--------|---------------------|---------------------|-----------------|-------|

| top      |        | × 10 <sup>-12</sup> | × 10 <sup>-14</sup> | 10 <sup>2</sup> |       |

| contact  |        |                     |                     |                 |       |

| (TGTC)   |        |                     |                     |                 |       |

|          |        |                     |                     |                 |       |

| Top gate | -0.423 | -3.826              | -1.758              | 2.17 ×          | 1.318 |

| bottom   |        | × 10 <sup>-11</sup> | × 10 <sup>-13</sup> | 10 <sup>2</sup> |       |

| contact  |        |                     |                     |                 |       |

| (TGBC)   |        |                     |                     |                 |       |

|          |        |                     |                     |                 |       |

#### Conclusion

After Modeling and simulation of various device structures were performed successfully, and it was observed that there was a slight variation in curves obtained in bottom-gate configurations at higher voltage range. However, in the case of top-gate configuration, there was slightly more variation at higher voltage range compared to that of lower voltage range. This variation was due to the different device geometry, as the device geometry/materials thickness plays a decisive role in the performance of electronic devices. Further, as per the requirement and application any suitable optimized geometry can be chosen and fabrication can be done.

#### Acknowledgements

Dr. M. K. Singh is thankful to the CRS project (ID: 1-5761775206) granted by NPIU/MHRD Govt. of India. Authors are grateful to all colleagues, faculty members & Head, Department of Electronics Engineering, HBTU Kanpur for giving time to time help and support. Mr. Abhishek Singh is especially thankful to MHRD Govt. of India/ HBTU Kanpur for providing financial assistance with GATE fellowship.

#### References

- T. Someya, Y. Kato, S. Iba, Y. Noguchi, T. Sekitani, H. Kawaguchi, and T. Sakurai, "Integration of organic FETs with organic photodiodes for a large area, flexible, and lightweight sheet image scanners." *IEEE transactions on electron devices*, 52(11), pp. 2502-2511, 2005.

- [2] E. Huitema, G. Gelinck, B. van der Putten, E. Cantatore, E. van Veenendaal, L. Schrijnemakers, B.H. Huisman, and D. de Leeuw, "Plastic transistors in active-matrix displays." *IEEE International Solid-State Circuits Conference, Digest of Technical Papers, ISSCC*, pp. 380-381, 2003.

- [3] B. Crone, A. Dodabalapur, Y.Y. Lin, R.W. Filas, Z. Bao, A. LaDuca, R. Sarpeshkar, H.E. Katz, and W. Li, "Large-scale complementary integrated circuits based on organic transistors." Nature, 403(6769), pp. 521-523, 2000.

- [4] C.D. Dimitrakopoulos, and P.R. Malenfant, "Organic thin-film transistors for large area electronics." Advanced materials, 14(2), pp. 99-117, 2002.

- [5] I. Nausieda, K. Ryu, I. Kymissis, A.I. Akinwande, V. Bulovic, and C.G. Sodini, "An organic active-matrix imager." *IEEE transactions* on electron devices, 55(2), pp. 527-532, 2008.

- [6] S. Shen, R. Tinivella, M. Pirola, G. Ghione and V. Camarchia, "SPICE Library for Low-Cost RFID Applications Based on

Pentacene Organic FET," 2010 6th International Conference on Wireless Communications Networking and Mobile Computing (WiCOM), Chengdu, pp. 1-4, 2010.

- [7] H. Klauk, "Organic thin-film transistors." Chemical Society Reviews, 39(7), pp. 2643-2666, 2010.

- [8] M. Weis, "Organic field-effect transistors." Encyclopedia of Physical Organic Chemistry, pp. 1- 39, 2016.

- [9] BK Kaushik, B. Kumar, Y.S. Negi and P. Mittal, "Prospects and limitations of organic thin film transistors (OTFTs)". In Advances in Computer Science, Engineering & Applications, Springer, Berlin, Heidelberg. pp. 125-139, 2012.

- [10] B. Hafsi, A. Boubaker, N. Ismaïl, A. Kalboussi, and K. Lmimouni. "TCAD Simulations of graphene field-effect transistors based on the quantum capacitance effect." *Journal of the Korean Physical Society*, 67(7), pp. 1201-1207, 2015.

- [11] N. Lu, L. Wang, L. Li, and M. Liu. "A review for compact model of graphene field-effect transistors." *Chinese Physics B*, 26(3), pp. 1-38, 2017.

- [12] P. Kumari, and A. D. D. Dwivedi. "Numerical Simulation and Characteriation of Pentacene based Organic Thin Film transistors with Top and Bottom Gate Configurations." Global Journal of Research In Engineering, pp. 6-12, 2019.

- [13] W. Wondmagegn, and R. Pieper. "Simulation of top-contact pentacene thin film transistor." Journal of computational electronics 8, pp. 19-24, 2009.

- [14] A.D.D. Dwivedi, S.K. Jain, R.D. Dwivedi, and S. Dadhich. "Numerical simulation and compact modeling of low voltage pentacene based OTFTs." *Journal of Science: Advanced Materials* and Devices, 4(4), pp. 561-567, 2019.

- [15] P. Kumari, and A.D.D. Dwivedi. "2D Numerical Simulation and Modeling of High-Performance Pentacene Organic Thin Film Transistor based on Poly (3-Dodecylthiophene-2, 5-Diyl) Dielectric Layer." International Journal on Future Revolution in Computer Science & Communication Engineering, 3, pp. 5-7, 2017.

- [16] P. Mittal, B. Kumar, Y.S. Negi, B.K. Kaushik, and R.K. Singh. "Channel length variation effect on performance parameters of organic field-effect transistors." *Microelectronics Journal*, 43(12), pp. 985-994, 2012.