# Optimization of the Al<sub>2</sub>O<sub>3</sub>/GaSb Interface and a High-Mobility GaSb pMOSFET

Aneesh Nainani, Toshifumi Irisawa, Ze Yuan, Brian R. Bennett, J. Brad Boos, *Member, IEEE*, Yoshio Nishi, *Fellow, IEEE*, and Krishna C. Saraswat, *Fellow, IEEE*

Abstract—While there have been many demonstrations on n-channel metal-oxide-semiconductor field-effect transistors (MOSFETs) in III-V semiconductors showing excellent electron mobility and high drive currents, hole mobility in III-V p-channel MOSFETs (pMOSFETs) has traditionally lagged in comparison to silicon. GaSb is an attractive candidate for high-performance III-V pMOSFETs due to its high bulk hole mobility. We fabricate and study GaSb pMOSFETs with an atomic layer deposition Al<sub>2</sub>O<sub>3</sub> gate dielectric and a self-aligned source/drain formed by ion implantation. The band offsets of Al<sub>2</sub>O<sub>3</sub> on GaSb were measured using synchrotron radiation photoemission spectroscopy. The use of a forming gas anneal to passivate the dangling bonds in the bulk of the dielectric was demonstrated. The density of interface states  $D_{it}$  was measured across the GaSb band gap using conductance measurements, and a midband-gap  $D_{it}$  of  $3 \times 10^{11}$ /cm<sup>2</sup>eV was achieved. This enabled pMOSFETs with a peak hole mobility value of 290 cm<sup>2</sup>/Vs.

Index Terms—Atomic layer deposition (ALD), gallium antimonide, hole mobility, III–V p-channel metal–oxide–semiconductor field-effect transistors (pMOSFETs).

### I. INTRODUCTION

aSb is an exciting III–V material, which may enable a high-performance/low-power complementary metal–oxide–semiconductor (CMOS) technology, which can outperform silicon. While there have been many demonstrations on n-channel metal–oxide–semiconductor field-effect transistors (nMOSFETs) in III–V showing excellent electron mobility and high drive currents, hole mobility in III–V p-channel MOSFETs (pMOSFETs) has traditionally lagged in comparison to silicon. GaSb is an attractive material for pMOSFET because of its high bulk mobility for holes (~850 cm²/Vs), which is among the

Manuscript received May 2, 2011; revised July 14, 2011; accepted July 14, 2011. Date of publication August 18, 2011; date of current version September 21, 2011. This work was supported in part by the Office of Naval Research and in part by Intel Corporation. The review of this paper was arranged by Editor A. Haque.

A. Nainani is with Applied Materials, Inc., Santa Clara, CA 95054-3299 USA, and also with the Center for Integrated Systems, Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: nainani@stanford.edu).

T. Irisawa is with the Collaborative Research Team Green Nanoelectronics Center, National Institute of Advanced Industrial Science and Technology, Tsukuba 305-8569, Japan.

Z. Yuan, Y. Nishi, and K. C. Saraswat are with the Center for Integrated Systems, Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA.

B. R. Bennett and J. B. Boos are with the Naval Research Laboratory, Washington, DC 20375 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2162732

highest of all III–V semiconductors and twice as high as silicon and GaAs. The electron mobility in GaSb is five times higher, as compared with that in silicon. Another metric, which should be considered while comparing different semiconductors for CMOS applications, is the ratio of their electron mobility to hole mobility, which is proportional to the ratios of channel widths for the nMOSFET and pMOSFET to drive the same level of current. This ratio is  $\sim\!8$  for GaSb, around 21 for GaAs, and greater than 50 for InAs and InSb. Thus, GaSb is more suited to enable a CMOS technology with traditional layout and circuit schemes.

GaSb also has other features that make it attractive for III-V CMOS. The charge neutrality level for GaSb is located at 0.1 eV from the valence band edge [1], thus the metal Fermilevel pins near the valence band for the metal/GaSb contact. This is favorable for obtaining contacts with low resistivity to p-type GaSb in the source/drain region of the pMOSFET. Contact resistivity values of less than  $1 \times 10^{-7} \Omega \text{cm}^2$  have been reported for p-type GaSb [2]. GaSb has a band gap of 0.72 eV, which is well matched to the loss minima for optical fiber communication and large enough to enable a high  $I_{\rm ON}/I_{\rm OFF}$ ratio, as compared to other III-V semiconductors [2]. Finally, GaSb has a melting point of 712 °C, as compared to 1238 °C for GaAs and 1414 °C for silicon. As for the thermal budget for processing scales with melting point, Sb-based materials are more suitable for low-temperature processing, which allows a simpler self-aligned process flow, and can be advantageously utilized when these materials are grown on top of another substrate, e.g., silicon, for heterogeneous integration.

The earliest attempt to fabricate MOSFETs on GaSb dates back to 1977 when Rockwell reported on a GaSb pMOSFET using pyrolytic silicon dioxide as the gate insulator [3]. The authors noted that the performance of the device was limited by the quality of the oxide, and the device showed a decrease in ON current and mobility with a decrease in measurement temperature indicating that the scattering mechanisms from the dielectric/interface were limiting the device performance. With the recent progress in the field of surface cleaning combined with atomic layer deposition (ALD), it has been possible to deposit high-quality dielectrics on III-V semiconductors. Many research groups have demonstrated nMOSFETs on an InGaAs/InP system using ALD dielectric and metal gate [4]-[6]. Only recently have people started investigating the passivation and interface properties of ALD oxide on GaSb [7], [8]. Ali et al. reported on the use of plasma-enhanced ALD to unpin the GaSb/dielectric interface [7]. Merckling et al.

| Report Documentation Page                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                           |                                                                                                                                           | Form Approved<br>OMB No. 0704-0188                                                                                |                                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Public reporting burden for the collection of information is estimated to maintaining the data needed, and completing and reviewing the collect including suggestions for reducing this burden, to Washington Headqu VA 22202-4302. Respondents should be aware that notwithstanding at does not display a currently valid OMB control number.                                                              | ion of information. Send comments a<br>arters Services, Directorate for Infor                                                                             | regarding this burden estimate of mation Operations and Reports                                                                           | or any other aspect of the 1215 Jefferson Davis                                                                   | is collection of information,<br>Highway, Suite 1204, Arlington                                                                   |  |

| 1. REPORT DATE JUL 2011                                                                                                                                                                                                                                                                                                                                                                                     | 2. REPORT TYPE                                                                                                                                            |                                                                                                                                           | 3. DATES COVE<br>00-00-2011                                                                                       | red<br>to 00-00-2011                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                           | 50 CONTRACT NUMBER                                                                                                |                                                                                                                                   |  |

| 4. TITLE AND SUBTITLE  Optimization of the Al2O3/GaSb Interface and a High-Mobility GaSb                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                           | 5a. CONTRACT NUMBER                                                                                               |                                                                                                                                   |  |

| pMOSFET                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                                                                                                                                           | 5b. GRANT NUMBER                                                                                                  |                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                           | 5c. PROGRAM ELEMENT NUMBER                                                                                        |                                                                                                                                   |  |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                           |                                                                                                                                           | 5d. PROJECT NUMBER                                                                                                |                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                           | 5e. TASK NUMBER                                                                                                   |                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                           | 5f. WORK UNIT NUMBER                                                                                              |                                                                                                                                   |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)  Naval Research Laboratory, Washington, DC, 20375                                                                                                                                                                                                                                                                                                        |                                                                                                                                                           |                                                                                                                                           | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                                                                       |                                                                                                                                   |  |

| 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES)                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                                                                                                                                           | 10. SPONSOR/MONITOR'S ACRONYM(S)                                                                                  |                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           |                                                                                                                                           | 11. SPONSOR/M<br>NUMBER(S)                                                                                        | ONITOR'S REPORT                                                                                                                   |  |

| 12. DISTRIBUTION/AVAILABILITY STATEMENT <b>Approved for public release; distributi</b>                                                                                                                                                                                                                                                                                                                      | ion unlimited                                                                                                                                             |                                                                                                                                           |                                                                                                                   |                                                                                                                                   |  |

| 13. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                           |                                                                                                                                           |                                                                                                                   |                                                                                                                                   |  |

| While there have been many demonstratransistors (MOSFETs) in III?V semic currents, hole mobility in III?V p-char to silicon. GaSb is an attractive candid hole mobility. We fabricate and study dielectric and a self-aligned source/drawere measured using synchrotron radit to passivate the dangling bonds in the states Dit was measured across the Gail Dit of 3 ?1011/cm2eV was achieved. The cm2/Vs. | onductors showing onel MOSFETs (pM ate for high-perform GaSb pMOSFETs win formed by ion impation photoemission bulk of the dielectric Sb band gap using c | excellent electron OSFETs) has tranance III?V pMC with an atomic lay uplantation. The kaspectroscopy. The was demonstrate onductance meas | mobility and ditionally lag OSFETs due to be deposition oand offsets to he use of a foed. The dens turements, and | d high drive gged in comparison to its high bulk n Al2O3 gate of Al2O3 on GaSb rming gas anneal ity of interface nd a midband-gap |  |

| 15. SUBJECT TERMS  Atomic layer deposition (ALD), galliumetal?oxide?semiconductor field-effect                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                         | • •                                                                                                                                       | channel                                                                                                           |                                                                                                                                   |  |

| 16. SECURITY CLASSIFICATION OF:                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           | 17. LIMITATION OF<br>ABSTRACT                                                                                                             | 18. NUMBER<br>OF PAGES                                                                                            | 19a. NAME OF<br>RESPONSIBLE PERSON                                                                                                |  |

c. THIS PAGE

unclassified

Same as

Report (SAR)

9

a. REPORT

unclassified

b. ABSTRACT

unclassified

explored the use of *in situ* deposition of  $Al_2O_3$  on GaSb grown on InP using molecular beam epitaxy and reported  $D_{it}$  values in the low  $10^{12}/\text{cm}^2\text{eV}$  range near the valence band [8]. While these are exciting results, the development of high-quality ALD dielectric on the GaSb surface still remains a nascent field, and MOSFETs on GaSb utilizing the ALD dielectric and their mobility have not been reported yet. In this paper, we explore the use of thermal ALD  $Al_2O_3$  to achieve quality MOSFETs with a GaSb channel.

Another challenge in achieving high-performance MOSFETs on GaSb is the development of source/drain technology with high density of activated carriers, low defects, and low contact resistance. Ion implantation in antimonides has traditionally been a challenge; the formation of hillocks and voids has been well known with high-dose of ion implantation in GaSb [9], [10]. In this paper, we attempt to overcome these challenges and demonstrate a pMOSFET in GaSb substrate using ALD  $\rm Al_2O_3$  as the dielectric and source/drain formed by ion implantation in a self-aligned process flow.

The rest of this paper is organized as follows: In Section II, we report on the development of an  $Al_2O_3$  gate dielectric on GaSb. Capacitance/conductance measurements and radiation from synchrotron are used to study the dielectric properties. The use of a forming gas anneal (FGA) to improve the dielectric properties is also discussed. Section III details the ion implantation process for forming source/drain and  $p^+/n$  diode characteristics for the pMOSFET. Section IV describes the fabrication flow and results obtained on the fabricated GaSb pMOSFET devices. Finally, we draw some conclusions in Section V.

# II. DIELECTRIC DEVELOPMENT

A high-quality dielectric on the GaSb surface is the key for achieving good MOSFET characteristics. Here, we report on the optimization of ALD Al<sub>2</sub>O<sub>3</sub> for the GaSb surface. We choose Al<sub>2</sub>O<sub>3</sub> as it has the advantages of a large band gap, high dielectric constant, high breakdown field ( $> 10^7$  V/cm), and thermal stability (amorphous for temperatures up to 1000  $^{\circ}$ C). The amorphous Al<sub>2</sub>O<sub>3</sub> film also acts as a better barrier for alkali ions, has fewer impurities, and has higher radiation resistance. Any high-k oxide for a III–V MOSFET must satisfy two basic criteria, i.e., 1) a clean and native-oxide-free interface with the semiconductor and 2) sufficient band offset of over 1 eV to act as a barrier for both electrons and holes [1]. The GaSb surface has been known to be highly reactive to atmospheric oxygen, and a thick native oxide quickly forms on the surface [11]. The removal of this oxide to produce a clean and thermally stable surface is essential in achieving good interface quality and low density of interface states  $D_{\mathrm{it}}$ . We use a chemical clean in 1:1 HCl for surface preparation before ALD. A HCl acid-based clean is effective to remove both the  $GaO_x$  and  $SbO_x$  on the GaSb surface. The comparison of various chemical cleans in producing a device-quality Sb surface was extensively studied using low-energy synchrotron radiation and photoluminescence measurements and has been reported elsewhere [12]. After the chemical clean, Al<sub>2</sub>O<sub>3</sub> was deposited at 300 °C by ALD using trimethyl aluminum (TMA) and water as the precursors with TMA being the starting pulse for the ALD. The root-mean-

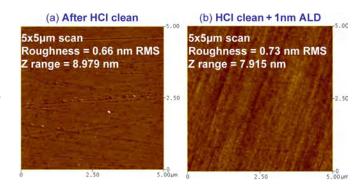

Fig. 1. AFM scan shows RMS roughness values of (a) 0.66 nm immediately after the chemical clean (b) and 0.73 nm after 10 cycles ( $\sim$ 1 nm) of Al $_2$ O $_3$  deposited by ALD.

square (RMS) roughness values of the surface just after HCl clean and after 10 cycles of ALD deposition were measured to be 0.66 and 0.73 nm, respectively, as shown in Fig. 1.

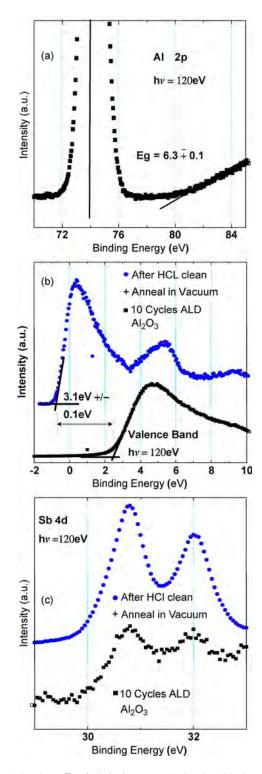

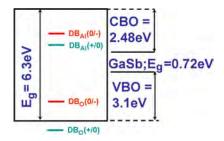

Synchrotron radiation photoemission spectroscopy (SRPES) was used to estimate the conduction band offset (CBO) and the valence band offset (VBO) for Al<sub>2</sub>O<sub>3</sub> on GaSb. The Al<sub>2</sub>O<sub>3</sub> band gap was measured to be 6.3 eV from the Al 2p loss spectrum [see Fig. 2(a)], which agrees well with values reported for ALD Al<sub>2</sub>O<sub>3</sub> deposited under similar conditions [13]. The VBO was measured by taking the difference between the valence band spectrum from the surface after the clean and after thin Al<sub>2</sub>O<sub>3</sub> deposition, as shown in Fig. 2(b) [14], using the Sb 4d peak from the GaSb substrate for alignment [see Fig. 2(c)]. The VBO was measured to be 3.1 eV by SRPES, which has a highenergy resolution near the valence band spectrum maximum. Using the known value of the GaSb band gap (0.72 eV) at room temperature, the CBO can be estimated by taking the difference of the Al<sub>2</sub>O<sub>3</sub> band gap with the VBO and the GaSb band gap, as shown in Fig. 3. The measured CBO/VBO of 2.48 eV/3.1 eV for Al<sub>2</sub>O<sub>3</sub> on GaSb are sufficient to minimize gate leakage by thermionic and tunneling processes, and the insulator is therefore well suited for a MOSFET design.

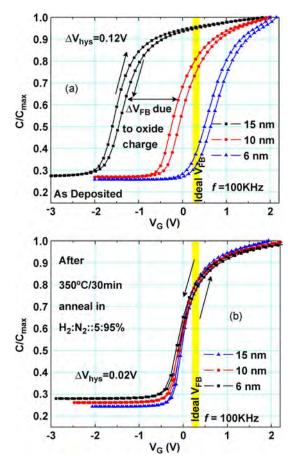

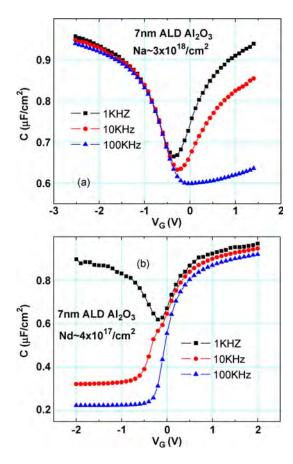

Al<sub>2</sub>O<sub>3</sub> films with thicknesses of 5–15 nm were deposited on GaSb using ALD. Film thickness was measured using ellipsometry, which was also verified with cross-sectional transmission electron microscopy. Capacitors were made on these films using platinum (Pt) electrode deposited in an e-beam evaporator through a shadow mask. Fig. 4(a) plots the capacitance-voltage (CV) characteristics at 100 kHz for capacitors on p-type GaSb for varying thicknesses of as-deposited Al<sub>2</sub>O<sub>3</sub>. The capacitance values are normalized with respect to the maximum capacitance in accumulation to compare the shift in flatband voltage  $V_{\rm FB}$ . We observe that in Fig. 4, the normalized capacitance curves are shifted parallel to each other for the as-deposited dielectric, indicating the presence of fixed charge in the bulk of the oxide and/or at the oxide/semiconductor interface. In addition, in comparison to the ideal  $V_{\rm FB}$  value calculated using the effective work function of Pt on  $Al_2O_3$  [15], the measured  $V_{\rm FB}$  is negatively shifted with respect to the ideal value for the thinner oxide thickness, whereas a positive  $V_{\rm FB}$  shift is observed for thicker dielectric thicknesses with respect to the ideal value.

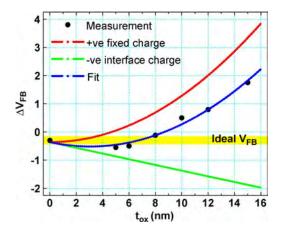

This issue is further examined in Fig. 5, where  $V_{\rm FB}$  is plotted as a function of oxide thickness for the as-deposited dielectric.

Fig. 2. (a) Band gap  $E_g$  of  ${\rm Al_2O_3}$  is measured using the Al 2p loss spectrum. (b) VBO is measured by taking the difference between the valence spectrum before and after depositing a thin layer of  ${\rm Al_2O_3}$ . (c) While using the Sb 4d peak from the substrate for alignment.

$V_{\rm FB}$  was extracted using the method of Hillard *et al.* [16]. The observed thickness dependence of  $V_{\rm FB}$  can be explained if we assume that there is negative fixed charge near the  ${\rm Al_2O_3}$  interface with GaSb and positive charge in the bulk of the oxide film. A negative linear shift in  $V_{\rm FB}$  as a function of dielectric thickness occurs due to negative charge at the semiconduc-

Fig. 3. Band offsets for  $Al_2O_3$  deposited by ALD on GaSb. The position of charge transition levels for dangling bonds in the oxide has been overlayed with the band diagram of the oxide.

Fig. 4. High-frequency CV characteristics on (a) as-deposited  ${\rm Al_2O_3}$  and (b) after FGA. The capacitance values are normalized to compare the  $V_{\rm FB}$  shift with varying dielectric thicknesses.

tor/oxide interface, as shown in Fig. 5, whereas a positive parabolic shift is expected when there is positive bulk charge present in the dielectric [17]. The functional dependence of the measured data can be fitted very well with the combination of negative linear and positive parabolic dependence (see Fig. 5), confirming the presence of positive bulk charge in the oxide and negative charge at the oxide/GaSb interface for the as-deposited Al<sub>2</sub>O<sub>3</sub>. A similar charge distribution has been also observed for Al<sub>2</sub>O<sub>3</sub> on InGaAs deposited under similar conditions by Shin *et al.* [18]. The authors attributed this charge distribution to the presence of an O-rich region near the interface and an Al-rich region away from the interface. It is known from first-principle calculations in amorphous Al<sub>2</sub>O<sub>3</sub> that the Al deficiency manifests itself in the form of oxygen dangling bonds,

Fig. 5. Measured  $V_{\rm FB}$  shift as a function of physical oxide thickness  $t_{\rm ox}$ . Experimental data can be fitted very well combining a linear shift with  $t_{\rm ox}$  due to negative interface charge and a parabolic shift with  $t_{\rm ox}$  due to positive bulk charge.

which have charge-transition levels at -0.83 and 0.61 eV above the valence band, as shown in Fig. 3, whereas the aluminum dangling bonds due to O deficiency are located at 5.12 and 5.35 eV above the valence band (see Fig. 3) [18]. Looking at the position of these dangling bonds in Fig. 3, we can predict that the O dangling bonds will be below the Fermi level and thus will be negatively charged, whereas the Al dangling bonds will be positively charged. This agrees well with the experimental result that the O-rich region near the interface has fixed negative charge, whereas the Al-rich region in the bulk has positive charge.

As the presence of fixed charge in the oxide or at the oxide/semiconductor is detrimental for MOSFET performance, the use of FGA was explored to reduce the fixed charge and improve the Al<sub>2</sub>O<sub>3</sub>/GaSb interface properties. Recently, the use of FGA has been shown to be very effective at improving the interface properties of the oxide/ $In_xGa_{1-x}As$  interface and passivating the bulk traps in Al<sub>2</sub>O<sub>3</sub> deposited by ALD under similar conditions [18], [19]. A theoretical analysis has predicted binding energy values of 1.3 eV for O-H and 1.4 eV for Al-H indicative of stable passivation. Hydrogen passivation can hence neutralize the effect of dangling bonds and improve the interface properties. Motivated by this, we tried an FGA anneal with forming gas  $(5/95\% : H_2/N_2)$  flowing at the rate of ~4 L/min at varying temperatures. A 30 min/350 °C anneal was found to be optimum to improve the dielectric properties. Fig. 4(b) plots the CV characteristics following the FGA anneal, where the normalized CVs for different dielectric thicknesses overlap each other, indicating the removal of fixed charge. The hysteresis reduces from ~120 mV for the as-deposited condition to  $\sim$ 20 mV after the FGA anneal, indicating passivation of bulk traps (see Fig. 4). A reduction in stretch-out indicating reduction of  $D_{it}$  was also observed. The temperatures above and below 350 °C were found to be less effective in improving the dielectric properties with FGA. A similar behavior with temperature has been observed with the effect of FGA on the dielectric/Ge interface [20] and has been attributed to insufficient diffusion of hydrogen radicals at low temperatures (< 350 °C) and deterioration of interface properties due to intermixing at the semiconductor/dielectric interface and desorption of hydrogen at higher temperatures (> 350  $^{\circ}$ C).

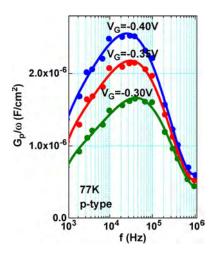

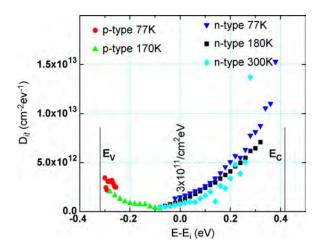

Fig. 6 plots the CV characteristics obtained after the FGA anneal on p- and n-type GaSb substrates for the frequency range of 1–100 kHz. An inversion response at room temperature was observed on both n- and p-type GaSb substrates. Frequency dispersion in accumulation, which is one indicator of  $D_{it}$ , was less than 1/2.1%/dec for the p- and n-type substrates. The  $D_{\rm it}$  distribution across the band gap was determined using the conductance method in the depletion region [21], [22] on n- and p-type substrates. The temperature was varied from 300 K-80 K, and measurements were made on both n- and p-type substrates to probe the  $D_{\rm it}$  distribution across the entire band gap. Fig. 7 shows a typical  $G_p/\omega$  versus frequency curve for the p-type substrate at 77 K. Fig. 8 plots the derived  $D_{\mathrm{it}}$ distribution. A midband-gap  $D_{\rm it}$  value of  $3 \times 10^{11}/{\rm cm}^2{\rm eV}$  was achieved. The  $D_{\rm it}$  distribution is asymmetric with low  $D_{\rm it}$ near the valence band edge and an order of magnitude higher  $D_{\rm it}$  toward the conduction band. The low  $D_{\rm it}$  values near the valence band is encouraging for obtaining a good pMOSFET, whereas the high  $D_{\mathrm{it}}$  values near the conduction band can be detrimental to the nMOSFET performance. It must be noted that the minimum of the  $D_{it}$  distribution occurs near the charge neutrality level of GaSb, which is located at  $\sim$ 0.1 eV from the valence band [1]. We also note that the  $D_{\rm it}$  distribution obtained is qualitatively similar to what is experimentally observed in germanium, which has a similar band gap as GaSb, and its charge neutrality center is located near the valence band as well [23].

# III. DIODE DEVELOPMENT FOR SOURCE/DRAIN

For the development of GaSb pMOSFET source/drain technology with a high density of activated carriers, low defects and low contact resistance are essential. Ion implantation in the antimonides has traditionally been a challenge, as the formation of hillocks and voids with a high dose of implantation in GaSb has been well known [9], [10]. In addition, it has been reported that this damage does not go away with furnace or rapid thermal anneal (RTA) even at high temperature. Furthermore, it has been noted that the threshold dose/energy of hillock formation decreases with increasing ion mass [9], [10]. Table I lists the dopant species for GaSb, i.e., Be, Si, and Zn act as acceptors in GaSb, and S, Se, and Te are the common donors. Thus, for the p<sup>+</sup>/n diode, the implantation dose at which hillock formation occurs is on the order of Zn < Si < Be. Similarly, for the  $n^+/p$ diode, it is on the order of S < Se < Te. The problem is worse for donors as the lightest atom for donors is S compared to Be for acceptors. It should be also noted that most of the previous work on implantation in GaSb was done without any dielectric layer on the top to absorb the energy of species being implanted.

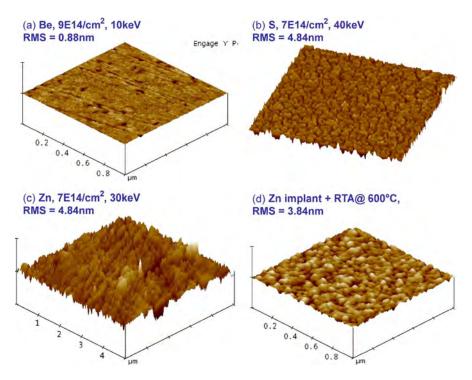

We experimented with ion implantation of several species in GaSb using thin ( $\sim$ 10 nm) Al<sub>2</sub>O<sub>3</sub> as the capping layer. The selection of implant energy and dose was guided by simulations performed with SRIM software [24] to produce a peak of the dopant species at the surface. Fig. 9(a)–(c) shows the atomic force microscopy (AFM) map of the surface after implantation

Fig. 6. Measured CV characteristics at room temperature over a frequency range of 1–100 kHz on (a) p-type GaSb with Na  $\sim 3\times 10^{18}/\text{cm}^2$  (b) n-type GaSb with Nd  $\sim 4\times 10^{17}/\text{cm}^2$ .

Fig. 7. Measured parallel  $G/\omega$  as a function of frequency for various gate voltages measured on a p-type GaSb capacitor at 77 K.

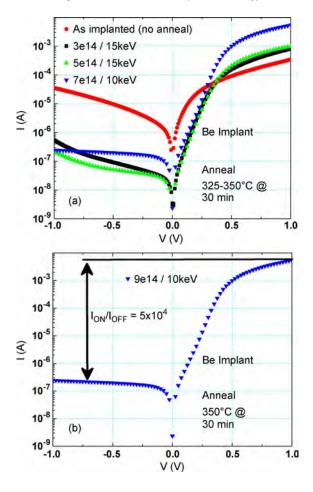

with Be, S, and Zn, respectively. A significant increase in surface roughness due to implant damage was observed for heavier species such as S and Zn. Furthermore, we observed that the surface still remains rough after RTA [see Fig. 9(d)]. The only good result was on Be, which has the lowest atomic mass and for which the surface roughness was less than 1 nm for an implant dose of  $9 \times 10^{14}/\text{cm}^2$ . Various implant and anneal conditions were attempted for Be to optimize the p<sup>+</sup>/n diode characteristics for the pMOSFET. The obtained diode IV

Fig. 8.  $D_{\rm it}$  distribution is calculated across the band gap using the conductance method.  $D_{\rm it}$  is scanned across the band gap utilizing both the p- and n-type substrates and varying the measurement temperature from 300 K to 77 K.

TABLE I DOPANT SPECIES IN GaSb

| Name | Nature   | Atomic Mass |

|------|----------|-------------|

| Be   | Acceptor | 9           |

| Si   | Acceptor | 28          |

| Zn   | Acceptor | 65.4        |

| S    | Donor    | 32          |

| Se   | Donor    | 78.9        |

| Те   | Donor    | 127.6       |

characteristics are plotted in Fig. 10(a). Good diode characteristics with  $I_{\rm ON}/I_{\rm OFF}$  of  $> 5 \times 10^4$  and an ideality factor of 1.4 could be obtained with annealing at 350 °C, as shown in Fig. 10(b).

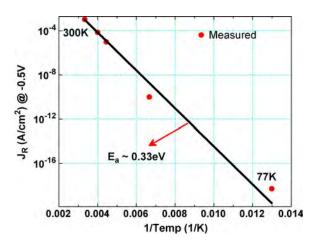

Fig. 11 plots the temperature dependence of the reverse leakage current for the p $^+/n$  diode. Reduction in reverse current was observed when the temperature was decreased from 300 K to 80 K. Activation energy  $E_a$  was calculated to be  $\sim\!0.33$  eV from the slope of the observed characteristics in Fig. 11. This value is close to half of the band gap of GaSb ( $E_g\sim0.72$  eV), suggesting that the intrinsic generation–recombination is dominant in the reverse leakage current [17], [25], [26].

## IV. TRANSISTOR FABRICATION AND CHARACTERISTICS

GaSb pMOSFETs were fabricated using a self-aligned gate-first process flow on an n-type GaSb substrate grown by the Czochralski process with Te as the n-type dopant. A carrier concentration of  $\sim\!3-4\times10^{17}/\text{cm}^3$ , which was the lowest available commercially, was chosen to reduce the effect of Coulomb scattering on transistor mobility. One hundred cycles ( $\sim\!10$  nm) of ALD  $Al_2O_3$  were deposited at 300 °C for use as the gate dielectric, followed by evaporation and patterning of the aluminum gate material. This was followed by ion implantation of beryllium. The source and drain contacts were formed by Ti/Ni

Fig. 9. AFM scan of the surface after: (a) Be implant with dose  $= 9 \times 10^{14}/\text{cm}^2$  and energy = 10 keV; (b) S implant with dose  $= 7 \times 10^{14}/\text{cm}^2$  and energy = 40 keV; (c) Zn implant with dose  $= 7 \times 10^{14}/\text{cm}^2$  and energy = 30 keV; and (d) RTA anneal of the Zn implanted sample at  $600 \,^{\circ}\text{C}$  for 5 min.

Fig. 10. (a) Various implant and anneal conditions were attempted to optimize the diode characteristics. (b) Diode with  $I_{\rm ON}/I_{\rm OFF}$  of  $5\times10^4$ , and ideality factor of 1.4 was achieved with annealing at 350  $^{\circ}{\rm C}$ .

Fig. 11. Reverse current  $J_R$  at applied voltage of  $-0.5~\rm V$  is measured as a function of temperature. The activation energy  $E_a$  of 0.33 eV is extracted from the slope.

deposition and liftoff. Fabrication of the transistors was completed with a 350 °C forming gas anneal, which also activates the source/drain implant. The temperature during the entire process never exceeds 400 °C. The low temperature required for source/drain activation allows for a self-aligned gate-first process flow without causing intermixing at the Al $_2$ O $_3$ /GaSb interface. The sheet resistance in the source/drain regions was measured to be 300  $\Omega/s$ quare using the transfer length method. Specific contact resistance of the Ti/Ni source/drain contact was measured to be  $\sim 2\times 10^{-5}~\Omega cm^2$ .

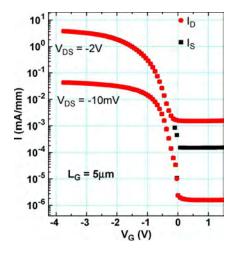

Fig. 12 plots the  $I_D$ – $V_G$  characteristics for the MOSFET device. The source current ON/OFF ratio is  $> 10^4$ , whereas the off current for the drain is limited by the reverse leakage through the large drain/body contact at large drain voltages (see

Fig. 12. Output characteristics of the GaSb pMOSFET.

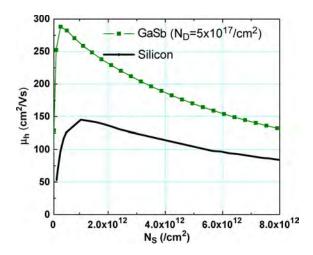

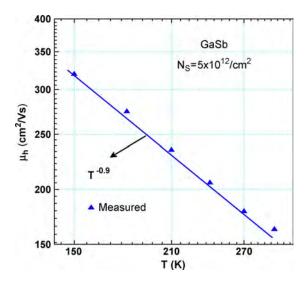

Fig. 12). The mobility for these transistors was extracted using the split CV analysis based on the  $I_D$ - $V_G$  characteristics of the transistors (gate length = 25  $\mu$ m) and the gate-to-channel capacitance  $C_{GC}$  measured at 100 kHz [17]. Note that no corrections for source/drain resistance or any other corrections were applied while extracting the mobility. Fig. 13 plots the extracted mobility as a function of sheet charge in the channel; a peak field-effect hole mobility of 290 cm<sup>2</sup>/Vs was obtained. Universal hole mobility in silicon is also plotted for comparison (see Fig. 13); the peak mobility in GaSb MOSFET is approximately twice higher in comparison to silicon, and the mobility gain over silicon is maintained even at high sheet charge. An increase in the ON current and correspondingly the mobility was observed when the temperature was decreased from 300 K to 80 K. The temperature dependence of mobility at a fixed sheet charge density of  $5 \times 10^{12}/\text{cm}^2$  is plotted in Fig. 14. The temperature dependence of  $T^{-0.85}$  is observed, which is closer to the  $T^{-1.0}$  dependence associated with mobility limited by interface roughness scattering. We did observe higher roughness in our devices, as compared to silicon/germanium from the AFM study in Fig. 1. The surface roughness on the GaSb surface clean was 0.66 nm, which is roughly twice higher in comparison to state-of-art silicon [27]. We believe that further optimization of the transistor output characteristics is possible with further improvement of the diode characteristics using a higher implant dose and an RTA.

### V. CONCLUSION

In conclusion, we have reported on the development of a high-quality ALD  $Al_2O_3$  gate dielectric on GaSb. The band offsets of  $Al_2O_3$  on GaSb were measured using SRPES and determined to be suitable for MOSFET development. FGA was effectively used to passivate the dangling bonds in the bulk of the dielectric and also to improve the interface properties [18]–[20]. Excellent CV characteristics were demonstrated on both p- and n-type substrates with frequency dispersion of less than 1/2.1%/dec. The  $D_{it}$  distribution was measured across the

Fig. 13. Hole mobility as a function of sheet charge. Silicon universal hole mobility data are plotted for comparison. Peak hole mobility of  $290~{\rm cm}^2/{\rm Vs}$  was obtained.

Fig. 14. Temperature dependence of hole mobility is plotted at fixed sheet charge of  $5\times 10^{12}/\text{cm}^2.$

GaSb band gap using conductance measurements; midband-gap  $D_{\rm it}$  of  $3\times 10^{11}/{\rm cm^2 eV}$  was achieved. A p<sup>+</sup>/n diode with an ON/OFF ratio of  $5\times 10^4$  and an ideality factor of 1.4 was demonstrated using ion implantation of Be.

A self-aligned process flow was used for fabricating pMOSFETs with the source/drain formed by ion implantation of Be. The maximum temperature during the process flow does not exceed 400 °C. Good transistor characteristics with  $I_{\rm ON}/I_{\rm OFF}>10^3$  and peak hole mobility of 290 cm²/Vs were obtained. Temperature-dependent measurements revealed a mobility value limited by interface scattering and a defect-free diode. This development paves the way for the demonstration of a complementary technology in III–V materials outperforming silicon.

### ACKNOWLEDGMENT

The authors would like to thank Dr. M. Ancona for technical discussions. Aneesh Nainani would like to thank Intel Corporation for a Ph.D. fellowship.

### REFERENCES

- J. Robertson and B. Falabretti, "Band offsets of high K gate oxides on III–V semiconductors," J. Appl. Phys., vol. 100, no. 1, pp. 014111-1– 014111-8, Jul. 2006.

- [2] P. S. Dutta, H. L. Bhat, and V. Kumar, "The physics and technology of gallium antimonide: An emerging optoelectronic material," *J. Appl. Phys.*, vol. 81, no. 9, pp. 5821–5870, May 1997.

- [3] E. E. Barrowcliff, L. O. Bubulac, D. T. Cheung, W. E. Tennant, and A. M. Andrews, "GaSb metal-insulator-semiconductor field-effecttransistors," in *IEDM Tech. Dig.*, 1977, pp. 559–562.

- [4] R. J. W. Hill, D. A. J. Moran, X. Li, H. Zhou, D. Macintyre, S. Thoms, A. Asenov, P. Zurcher, K. Rajagopalan, and J. Abrokwah, "Enhancementmode GaAs MOSFETS with an In<sub>0.3</sub>Ga<sub>0.7</sub>As channel, a mobility of over 5000 cm<sup>2</sup>/Vs, and transconductance of over 475 uS/um," *IEEE Electron Device Lett.*, vol. 28, no. 12, pp. 1080–1082, Dec. 2007.

- [5] J. Huang, N. Goel, H. Zhao, C. Y. Kang, K. S. Min, G. Bersuker, S. Oktyabrsky, C. K. Gaspe, M. B. Santos, P. Majhi, P. D. Kirsch, H. H. Tseng, J. C. Lee, and R. Jammy, "InGaAs MOSFET performance and reliability improvement by simultaneous reduction of oxide and interface charge in ALD (La)AlO<sub>x</sub>/ZrO<sub>2</sub> gate stack," in *IEDM Tech. Dig.*, 2009, pp. 355–358.

- [6] H. Zhao, Y. T. Chen, J. H. Yum, Y. Wang, F. Zhou, F. Xue, and J. C. Lee, "Effects of barrier layers on device performance of high mobility In<sub>0.7</sub>Ga<sub>0.3</sub>As metal–oxide–semiconductor field-effect-transistors," *Appl. Phys. Lett.*, vol. 96, no. 10, pp. 102101-1–102101-3, Mar. 2010.

- [7] A. Ali, H. S. Madan, A. P. Kirk, D. A. Zhao, D. A. Mourey, M. K. Hudait, R. M. Wallace, T. N. Jackson, B. R. Bennett, J. B. Boos, and S. Datta, "Fermi level unpinning of GaSb (100) using plasma enhanced atomic layer deposition of Al<sub>2</sub>O<sub>3</sub>," *Appl. Phys. Lett.*, vol. 97, no. 14, pp. 143502-1–143502-3, Oct. 2010.

- [8] C. Merckling, X. Sun, A. Alian, G. Brammertz, V. V. Afanasev, T. Y. Hoffmann, M. Heyns, M. Caymax, and J. Dekoster, "GaSb molecular beam epitaxial growth on p-InP(001) and passivation with in situ deposited Al<sub>2</sub>O<sub>3</sub> gate oxide," *J. Appl. Phys.*, vol. 109, no. 7, pp. 073719-1–073719-7, Apr. 2011.

- [9] R. Callec, P. Favennec, M. Salvi, H. LHaridon, and M. Gauneau, "Anomalous behavior of ion implanted GaSb," *Appl. Phys. Lett.*, vol. 59, no. 15, pp. 1872–1874, Oct. 1991.

- [10] R. Callec and A. Poudoulec, "Characteristics of implantation induced damage in GaSb," J. Appl. Phys., vol. 73, no. 10, pp. 4831–4835, May 1993.

- [11] Z. Y. Liu, B. Hawkins, and T. F. Kuech, "Chemical and structural characterization of GaSb(100) surfaces treated by HCl-based solutions and annealed in vacuum," *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct.*, vol. 21, no. 1, pp. 71–77, Jan. 2003.

- [12] A. Nainani, Y. Sun, T. Irisawa, Z. Yuan, M. Kobayashi, P. A. Pianetta, Y. Nishi, K. C. Saraswat, B. R. Bennett, and J. B. Boos, "Device quality Sb-based compound semiconductor surface: A comparative study of chemical cleaning," *J. Appl. Phys.*, vol. 109, no. 11, p. 114908, Jun. 2011. DOI: 10.1063/1.3590167.

- [13] N. V. Nguyen, M. Xu, O. A. Kirillov, P. D. Ye, C. Wang, K. Cheung, and J. S. Suehle, "Band offsets of  $Al_2O_3/In_xGa_{1-x}As$  (x=0.53 and 0.75) and the effects of postdeposition annealing," *Appl. Phys. Lett.*, vol. 96, no. 5, pp. 052107-1–052107-3, Feb. 2010.

- [14] R. Puthenkovilakam and J. P. Chang, "An accurate determination of barrier heights at the HfO<sub>2</sub>/Si interfaces," *J. Appl. Phys.*, vol. 96, no. 5, pp. 2701–2707, Sep. 2004.

- [15] Y.-C. Yeo, T.-J. King, and C. Hu, "Metal-dielectric band alignment and its implications for metal gate complementary metal—oxide—semiconductor technology," *J. Appl. Phys.*, vol. 92, no. 12, pp. 7266–7271, Dec. 2002.

- [16] R. Hillard, J. Heddleson, D. Zier, P. Rai-Choudhury, and D. Schroder, "Direct and rapid method for determining flatband voltage from non-equilibrium capacitance voltage data," in *Diagnostic Techniques for Semiconductor Materials and Devices*. Pennington, NJ: ECS, 1992, pp. 261–274.

- [17] D. K. Schroder, Semiconductor Material and Device Characterization. New York: Wiley-Interscience, 2006.

- [18] B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, "Origin and passivation of fixed charge in atomic layer deposited aluminum oxide gate insulators on chemically treated InGaAs substrates," *Appl. Phys. Lett.*, vol. 96, no. 15, pp. 152908-1–152908-3, Apr. 2010.

- [19] E. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley, "Temperature and frequency dependent electrical characterization of HfO<sub>2</sub>/In<sub>x</sub>Ga<sub>1-x</sub>As interfaces using

- capacitance-voltage and conductance methods," Appl. Phys. Lett., vol. 94, no. 10, pp. 102902-1-102902-3, Mar. 2009.

- [20] A. Pethe, "Germanium-based transistors for high-performance logic applications," Ph.D. dissertation, Stanford Univ., Palo Alto, CA, 2007.

- [21] E. Nicollian and A. Goetzberger, "The Si-SiO<sub>2</sub> interface-electrical properties as determined by the metal-insulator-silicon conductance technique," Bell Syst. Tech. J, vol. 46, no. 6, pp. 1055–1133, Jul./Aug. 1967.

- [22] K. Martens, C. Chi On, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, "On the correct extraction of interface trap density of MOS devices with high-mobility semiconductor substrates," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 547–556, Feb. 2008.

- [23] D. Kuzum, T. Krishnamohan, A. Nainani, S. Yun, P. A. Pianetta, H. S. P. Wong, and K. C. Saraswat, "High-mobility Ge N-MOSFETs and mobility degradation mechanisms," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 59–66, Jan. 2011.

- [24] J. F. Ziegler, "SRIM-2003," Nucl. Instrum. Methods Phys. Res. Section B, Beam Interact. Mater. Atoms, vol. 219/220, no. 1–4, pp. 1027–1036, Jun. 2004.

- [25] K. Morii, T. Iwasaki, R. Nakane, M. Takenaka, and S. Takagi, "High performance GeO<sub>2</sub>/Ge nMOSFETs with source/drain junctions formed by gas phase doping," in *IEDM Tech. Dig.*, 2009, pp. 681–684.

- [26] G. Thareja, J. Liang, S. Chopra, B. Adams, N. Patil, S. L. Cheng, A. Nainani, E. Tasyurek, Y. Kim, S. Moffatt, R. Brennan, J. McVittie, T. Kamins, K. Saraswat, and Y. Nishi, "High performance germanium n-MOSFET with antimony dopant activation beyond 1 × 10<sup>20</sup> cm<sup>-3</sup>," in *IEDM Tech. Dig.*, 2010, pp. 245–248.

- [27] C. H. Lee, T. Nishimura, T. Tabata, S. K. Wang, K. Nagashio, K. Kita, and A. Toriumi, "Ge MOSFETs performance: Impact of Ge interface passivation," in *IEDM Tech. Dig.*, 2010, pp. 18.1.1–18.1.4.

Aneesh Nainani . He received the B.S. and M.S. degrees in electrical engineering from the Indian Institute of Technology Bombay, Mumbai, India, both in 2007 and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 2011.

During his graduate studies, he was an intern at CEA-LETI, IBM Microelectronics, SEMATECH, and Applied Materials, Inc. He is currently with Applied Materials, Inc., Santa Clara, CA, and also with the Center for Integrated Systems, Stanford

University. He has published more than 30 papers on nanocrystal flash memory, III–V complementary metal–oxide–semiconductor, and thin-film solar cells. His research interests are in the physics and technology of semiconductors.

Dr. Nainani was a recipient of several awards, including the Intel PhD Fellowship, the School of Engineering Fellowship from Stanford University, and the National Talent Scholarship from the Government of India.

**Toshifumi Irisawa** received the B.S., M.S., and Ph.D. degrees from the University of Tokyo, Tokyo, Japan, in 1998, 2000, and 2003, respectively, all in applied physics. His Ph.D. thesis concerned the study on growth and transport properties of Si/Ge heterostructures.

In 2003, he joined Toshiba Research and Development Center, Kawasaki, Japan. From 2003 to 2008, he was a member of the MIRAI Project, Association of Super-Advanced Electronics Technology, Tokyo, where he was engaged in strained Si, SiGe (Ge)

device, and material technologies, including 3-D device structures. From 2008 to 2010, he was a Visiting Scholar at Stanford University, Stanford, CA, where he studied III–V metal–oxide–semiconductor technologies. After returning to Toshiba, he joined the Collaborative Research Team Green Nanoelectronics Center, National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, where he is currently working on low-power complementary metal–oxide–semiconductor device technologies.

Dr. Irisawa is a member of the Japan Society of Applied Physics.

**Ze Yuan** received the B.S. degree in microelectronic engineering in 2009 from Tsinghua University, Beijing, China, and the M.S. degree in electrical engineering in 2011 from Stanford University, Stanford, CA, where he is currently working toward the Ph.D. degree in electrical engineering.

His previous research interests include compact modeling of multigate devices and quantum transport simulation. He is currently working on the fabrication, characterization, and modeling of antimonidebased III–V metal–oxide–semiconductor field-effect

transistors.

Mr. Yuan was a recipient of the Stanford Graduate Fellowship.

**Brian R. Bennett** received the B.S. and M.S. degrees in geophysics and the Ph.D. degree in material science and engineering from the Massachusetts Institute of Technology in 1984, 1985, and 1992, respectively.

He served as a military officer in the Solid State Sciences Division, U.S. Air Force, from 1984 to 1988. Since 1992, he has been with the Naval Research Laboratory, Washington, DC, where he is currently serving as the Head of the Nanotechnology Section. His research focuses on the epitaxial growth

and applications of antimonide and arsenide semiconductor heterostructures, including n-channel InAs high-electron-mobility transistors and p-channel InGaSb field-effect transistors. His research also included electrooptic effects in Si and group III–V semiconductors and low-temperature deposition of silicon dioxide.

Dr. Bennett serves in the Electronic Materials Committee and is a member of the American Physical Society.

**J. Brad Boos** (M'85) received the B.S. degree in chemistry from the University of Maryland, College Park, in 1977 and the M.S. degree in electrical engineering from The George Washington University, Washington, DC, in 1987.

In 1980, he joined the Research Staff of the Electronics Science and Technology Division, Naval Research Laboratory, Washington, where he worked on III–V microwave and millimeter-wave device development. In 2002, he was appointed as the Head of the High-Speed Low-Power Devices Section. His

research efforts have included the design, fabrication, and characterization of InP-based HEMTs and photodetectors, and Sb-based HEMTs, p-channel heterojunction field-effect transistors, heterojunction bipolar transistors, and quantum devices.

Mr. Boos has served in the Technical Program and Steering Committees of the InP and Related Materials Conference and in the Technical Program Committee of the International Semiconductor Device Research Symposium. He also served as a Program Chair for the 2000 IPRM Conference.

Yoshio Nishi (SM'82–F'88) received the B.S. degree in materials science and engineering from Waseda University, Tokyo, Japan, and the Ph.D. degree (thesis doctor) in electronics engineering from the University of Tokyo, Tokyo.

He joined Toshiba Corporation, working in the area of semiconductor materials and processes during which he discovered the ESR PB Center at the Si–SiO2 interface, which is now accepted as the origin of the fast interface states. He is one of the pioneers in MNOS nonvolatile memory resulting in

256- and 1024-bit MNOS RAM devices productized in early 1970s. He led the group of silicon-on-sapphire (SOS)-based device research in the Research and Development (R&D) Center and developed technology for a 16-bit SOS microprocessor of medical computer for high-speed image data processing. Later, he managed the group of memory technology R&D in the Semiconductor Device Engineering Laboratory, which developed the world's first 1-Mb CMOS DRAM and 256-Kb SRAM and EPROM. In 1986, he joined Hewlett-Packard (HP) as the Director of the Silicon Process Laboratory, and then, he became the Director for the Integrated Circuit Business Division R&D Center running HP's high-performance CMOS technology R&D for PA RISC chips. He established the ULSI Research Laboratory as the advanced IC technology research for HP. In 1996, he joined Texas Instruments (TI), Dallas, as a Senior Vice President and the Director of R&D, in which he established a new R&D model and the Kilby Center for TI's IC technology R&D. In 2002, he joined Stanford University, Stanford, CA, as a Professor of electrical engineering. He served as the Director of Stanford Nanofabrication Facility, and he is currently the Research Director of the Center for Integrated Systems. His research interest at Stanford University includes resistive-change nonvolatile memory devices, new channel materials, including inorganic and organic semiconductors, metal-gate workfunction engineering, graphene band engineering, and group IV semiconductor light emissions. He has published more than 250 papers/conference talks, coauthored/edited 12 books, and held more than 50 patents in USA and Japan.

Dr. Nishi is the recipient of the IEEE Jack Morton Award (1995), the IEEE Robert Noyce Medal (2002), the PICMET Leadership in Technology Management Award (2007), and the SEMI Lifetime Achievement Award (2008).

Krishna C. Saraswat (M'70–S'71–SM'85–F'89) received the B.E. degree in electronics from Birla Institute of Technology and Science, Pilani, India, in 1968 and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1969 and 1974, respectively.

After finishing his Ph.D., he stayed at Stanford University as a Researcher and was appointed as a Professor of electrical engineering in 1983. He is currently a Rickey/Nielsen Professor, and by courtesy, a Professor of materials science and engineering with

the School of Engineering, Stanford University. During 1969-1970, he was with Texas Instruments, Dallas, where he worked on microwave transistors. He serves in the Leadership Council of the MARCO/DARPA-funded Focus Center for Materials, Structures, and Nano-Devices. He also has an honorary appointment of being an Adjunct Professor with Birla Institute of Technology and Science since January 2004 and a Visiting Professor during the summer of 2007 with the Indian Institute of Technology Bombay, Mumbai, India. During 2000-2007, he was an Associate Director of the NSF/SRC Center for Environmentally Benign Semiconductor Manufacturing. He has been a technical advisor, board member, and consultant to several industrial organizations in USA, Asia, and Europe. He has also advised several academic and government organizations worldwide. He was able to make more than 70 doctoral students graduate. He is the author or coauthor of more than 650 technical papers and the holder of 10 patents. His research interests are in new and innovative materials, structures, and process technology of silicon, germanium, and III-V devices and interconnects for VLSI and nanoelectronics. Special areas of his interest are new device structures to continuous-scaling metal-oxide-semiconductor transistors, DRAMs and Flash memory devices to nanometer regime, 3-D ICs with multiple layers of heterogeneous devices, and metal and optical interconnections.

Prof. Saraswat received the Best Paper Award for six of his technical papers. He was a recipient of the Thomas Callinan Award from The Electrochemical Society in 2000 for his contributions to dielectric science and technology, the 2004 IEEE Andrew Grove Award for seminal contributions to silicon process technology, the Inventor Recognition Award from MARCO/FCRP in 2007, and the Technovisionary Award from the India Semiconductor Association in 2007. He is listed by ISI as one of the 250 highly cited authors in his field.