# Optimized Active Disturbance Rejection Control for DC-DC Buck Converters With Uncertainties Using A Reduced-Order GPI Observer

Jun Yang, Member, IEEE, Hongyu Cui, Shihua Li, Senior Member, IEEE, and Argyrios Zolotas, Senior Member, IEEE

Abstract—The output voltage regulation problem of a PWMbased DC-DC buck converter under various sources of uncertainties and disturbances is investigated in this paper via an optimized active disturbance rejection control (ADRC) approach. Aiming to practical implementation, a new reduced-order generalized proportional integral (GPI) observer is first designed to estimate the lumped (possibly time-varying) disturbances within the DC-DC circuit. By integrating the disturbance estimation information raised by the reduced-order GPI observer (GPIO) into the output prediction, an optimized ADRC method is developed to achieve optimized tracking performance even in the presence of disturbances and uncertainties. It is shown that the proposed controller will guarantee the rigorous stability of closed-loop system, for any bounded uncertainties of the circuit, by appropriately choosing the observer gains and the bandwidth factor. Experimental results illustrate that the proposed control solution is characterised by improved robustness performance against various disturbances and uncertainties compared to traditional ADRC and integral MPC approaches.

*Index Terms*—DC-DC buck converter, active disturbance rejection control, optimized disturbance rejection, reduced-order GPIO, circuit uncertainties and disturbances.

# I. INTRODUCTION

Rapid developments in smart grid and renewable energy favoured extensive utilisation of DC-DC buck converters in various types of dc voltage regulation, e.g. in high voltage dc (HVDC) transmission, in adapters of electric devices, in dc motor drives, in the automotive industry etc. [11]–[13]. Being one of the most crucial components in power conversion, the precision of output voltage regulation in DC-DC buck converters is of particular importance to enable satisfactory performance of connected loads or devices [1]–[3]. However, accurate control of a DC-DC buck power converter is a rather challenging design exercise due to the following two major reasons: (i) it is intrinsically a hybrid system given the frequently switching mode of the circuit, (ii) the voltage regulation is subject to undesirable effects of the various disturbances and other system uncertainties, e.g. load resistance change,

J. Yang, H. Cui and S. Li are with School of Automation, Southeast University, Key Laboratory of Measurement and Control of CSE, Ministry of Education, Nanjing 210096, P.R. China (e-mails: j.yang84@seu.edu.cn, 220151401@seu.edu.cn and lsh@seu.edu.cn).

A. Zolotas is with School of Engineering, College of Science, University of Lincoln, Lincoln LN6 7TS, United Kingdom (e-mail: azolotas@lincoln.ac.uk).

input voltage variation, circuit parameter perturbation etc. [1], [14]. For example, the line voltage of HVDC transmission system is dependent of collected distributed generators and loads, which causes input voltage variation of grid connected DC-DC buck converters. Another example is the connected loads to adapters of electric devices that sometimes have different resistances [15], which is an important uncertainty factor for output voltage regulation. In addition, the magnetic characteristics of an inductor are usually nonlinear and uncertain especially under cases of large magnetic flux density in the ferromagnetic core of the converter circuit. The electro-magnetic interference produced by the switching actions of semiconductor such as switch transistors, diode, variable frequency transformer also causes external disturbances for the converter control. The various uncertainty factors inevitably degrade the quality and efficiency of power conversion, and consequently impose great challenges on higher-performance output voltage regulation of DC-DC buck converters.

Controlling such devices, Proportional-plus-Integral (PI) controllers have been traditionally utilized due to their simplicity in implementation but with limited control precision especially in the presence of large disturbances/uncertainties [15]. Advances in computational power availability of new generation of hardware devices enable practical implementation of modern advanced control approaches, i.e. sliding-mode control [5], [7], [9], [10], [14], geometric approach [8], robust control [4], [16], adaptive control [6], disturbance rejection control [15], [17], and receding optimization control [3], [18]-[20], to enhance the control performance of DC-DC buck converters. Among them, receding optimization control (ROC) has attracted considerable attention in the field of power converter control, attributed to the many advantages of its control algorithmic capacity guaranteeing optimized fast dynamic tracking responses to reference mutation, uncertain nonlinearities and undesirable disturbances [19]. Still within ROC, steady-state errors (SSE) raised by disturbances/uncertainties are addressed by employing integral action in the controller design [18]. Hence, SSE removal is realized at the price of sacrificing other control performance of the closed-loop system, due to the integral term interacting with other performance aspects such as transient behaviour, tracking, robust stability and performance [30], [31].

Therefore, it is of great importance to develop a controller that achieves optimized control performance of DC-DC power converters even in the presence of disturbances and uncertain-

The work was supported in part by National Natural Science Foundation of China under Grant 61203011, PhD Programs Foundation of Ministry of Education of China under Grant 20120092120031, and Natural Science Foundation of Jiangsu Province under Grant BK2012327.

ties. A promising way to address this is by introducing an observation of disturbance into the controller design [32]. Disturbance rejection control (DRC) offers a potentially advantageous technique to obtain outstanding disturbance rejection and robustness performances in DC-DC power converters. Active DRC (ADRC) is one of the most popular DRC approaches due to its intuitive concepts and simplicity for implementation, while requiring the least amount of plant information (i.e. only the system order should be known [21]–[23]). To date, ADRC has been extensively applied to practical systems such as AC servo motors [24], MEMS gyroscopes [25], fast tool servosystems [26], robotics [27], antenna systems [28] and gasoline engines [29].

In this paper, an optimized ADRC approach is proposed for the output voltage regulation of DC-DC buck converters without adopting integral control action. Rather than utilizing traditional GPIO [24], [33], a new reduced-order GPIO is firstly constructed to estimate the state and also the time varying uncertainties and disturbances simultaneously. Both the state and disturbance estimations are then introduced for output voltage prediction via Taylor series expansion. An optimized ADRC law is finally derived by solving a receding optimization problem. The utilization of a reduced-order GPIO in the optimized ADRC design provides a current sensorless mode to address the disturbance/uncertainty attenuation problem of the DC-DC buck converter, while exhibits the following noteworthy characteristics:

- In the best knowledge of the authors, this is the first time a rigorous stability analysis of the interconnected closedloop of the DC-DC buck converter is presented, which ensures asymptotic stability and robust performance even in the case of both system state-dependent and control input-dependent uncertainties.

- 2) A novel reduced-order GPIO that is one order lower than existing GPIOs is proposed. This admits the ability to higher-order disturbance estimation, while -similar to traditional ADRC - requires limited information of model and parameters (namely only the nominal values of input voltage, filter inductance and filter capacitor utilized).

- 3) An optimized ADRC approach is proposed by integrating the estimates by reduced-order GPIO into output voltage prediction. The optimized tracking performance and robustness against disturbance and uncertainties performed separately by assigning optimized feedback control parameters and observer gains, respectively, which addresses the coupling between system performance and controller parameters.

The newly proposed optimized ADRC is implemented on an NI LabVIEW-based real-time control test setup for validation purposes. The experimental results illustrate that the proposed control approach exhibits superior robustness performance against various disturbances and uncertainties compared to traditional ADRC and integral MPC approaches.

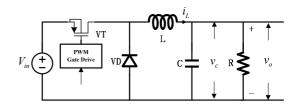

Fig. 1. The circuit diagram of a DC-DC buck converter.

# **II. PRELIMINARIES**

# A. Dynamic Models of DC-DC Converters

A generic PWM-based DC-DC buck converter comprising a dc input voltage source  $V_{in}$ , a PWM gate drive controlled switch VT, a diode VD, a filter inductor, a filter capacitor and a load resistor is shown in Fig. 1. The dynamic model is given as

$$\begin{cases} \frac{dv_{o}(t)}{dt} = \frac{1}{C}i_{L}(t) - \frac{1}{CR}v_{o}(t), \\ \frac{di_{L}(t)}{dt} = \frac{1}{L}\mu(t)V_{\text{in}} - \frac{1}{L}v_{o}(t), \end{cases}$$

(1)

where  $i_L$  is the average input current,  $v_o$  is the average output capacitor voltage, R is the load resistance of the circuit,  $V_{in}$  is an input voltage, L is a filter inductance, C is a filter capacitor, and the duty ratio  $\mu(t) \in [0, 1]$  represents the control signal. The model in (1) can be also re-arranged as follows

$$\frac{d^2 v_o(t)}{dt^2} = -\frac{1}{CR} \frac{dv_o(t)}{dt} - \frac{1}{CL} v_o(t) + \frac{V_{\rm in}}{CL} \mu(t).$$

(2)

Moreover, the reference output voltage is defined as  $v_r(t) = V_r$ , and the output voltage tracking error is defined as  $e(t) = v_o(t) - v_r(t)$ .

The objective of work presented in this paper is to design an optimized ADRC algorithm such that  $e(t) \rightarrow 0$  as  $t \rightarrow \infty$  in the presence of various uncertainties such as load resistance changes, input voltage variations, circuits parametric uncertainties and other external disturbances.

# B. Benchmark ADRCs

The nominal values of  $V_{in}$ , L and C are denoted as  $V_{in0}$ ,  $L_0$  and  $C_0$ , respectively. The DC-DC buck converter dynamics (2) are hence re-arranged as follows

$$\ddot{v}_o(t) = f(v_o(t), \dot{v}_o(t), \mu(t)) + b_0 \mu(t), \tag{3}$$

where  $f(v_o, \dot{v}_o, \mu) = a_1 v_o + a_2 \dot{v}_o + (b - b_0)\mu$  denotes the lumped uncertainties including variations of load resistance and input voltage, inductance and capacitance uncertainties, and other unmodeled disturbances such as EMI of the converter, with

$$b = \frac{V_{\text{in}}}{CL}, \ b_0 = \frac{V_{\text{in}0}}{C_0 L_0}, \ a_1 = -\frac{1}{CL}, \ a_2 = -\frac{1}{CR}$$

In the context of traditional ADRCs, an Extended State Observer (ESO) for the above converter system is designed as [21]

$$\begin{cases} \dot{\zeta}_1 = -\iota_1(\zeta_1 - v_o) + \zeta_2, \\ \dot{\zeta}_2 = -\iota_2(\zeta_1 - v_o) + \zeta_3 + b_0 \mu, \\ \dot{\zeta}_3 = -\iota_3(\zeta_1 - v_o), \\ \hat{v}_o = \zeta_1, \ \hat{v}_o = \zeta_2, \ \hat{f} = \zeta_3, \end{cases}$$

(4)

where  $\iota_i$  (i = 1, 2, 3) are observer gains,  $\hat{v}_o$ ,  $\hat{v}_o$  and  $\hat{f}$  are estimations of  $v_o$ ,  $\dot{v}_o$  and f, respectively. Similarly, a traditional full-order GPIO for the converter system is designed as [24]

$$\begin{cases} \zeta_{1} = -\iota_{1}(\zeta_{1} - v_{o}) + \zeta_{2}, \\ \dot{\zeta}_{2} = -\iota_{2}(\zeta_{1} - v_{o}) + \zeta_{3} + b_{0}\mu, \\ \dot{\zeta}_{3} = -\iota_{3}(\zeta_{1} - v_{o}) + \zeta_{4}, \\ \dot{\zeta}_{4} = -\iota_{4}(\zeta_{1} - v_{o}), \\ \dot{v}_{o} = \zeta_{1}, \ \dot{v}_{o} = \zeta_{2}, \ \hat{f} = \zeta_{3}, \ \dot{f} = \zeta_{4}, \end{cases}$$

$$(5)$$

where  $\iota_i$  (i = 1, 2, 3, 4) are observer gains,  $\hat{v}_o$ ,  $\hat{v}_o$ ,  $\hat{f}$  and  $\hat{f}$  are estimations of  $v_o$ ,  $\dot{v}_o$ , f and  $\dot{f}$ , respectively. The traditional ADRC laws based on the above two observers are generally designed as follows [21], [24]

$$\mu(t) = -\frac{1}{b_0} \left[ k_1 \left( v_o(t) - v_r(t) \right) + k_2 \hat{v}_o(t) + \hat{f}(t) \right], \quad (6)$$

where  $k_1$  and  $k_2$  are feedback control gains to be designed.

## III. OPTIMIZED ADRC

# A. Controller Design

1) Construction of the Reduced-Order GPIO: To enhance estimation precision and also enable easier practical implementation, a new reduced-order GPIO rather than ESO in traditional ADRC is constructed for the DC-DC buck converter as follows

$$\begin{cases} \dot{z}_2 = -\beta_1(z_2 + \beta_1 v_o) + z_3 + \beta_2 v_o + b_0 \mu, \\ \dot{z}_3 = -\beta_2(z_2 + \beta_1 v_o) + z_4 + \beta_3 v_o, \\ \dot{z}_4 = -\beta_3(z_2 + \beta_1 v_o), \\ \dot{v}_o = z_2 + \beta_1 v_o, \quad \hat{f} = z_3 + \beta_2 v_o, \quad \hat{f} = z_4 + \beta_3 v_o, \end{cases}$$

(7)

where  $\beta_i$  (i = 1, 2, 3) are observer gains,  $z_i$  (i = 2, 3, 4) are state variables of observer,  $\hat{v}_o$ ,  $\hat{f}$  and  $\hat{f}$  are estimations of  $\dot{v}_o$ , f and  $\dot{f}$ , respectively.

**Remark 1.** It can be seen from (5) and (7) that the signals  $\dot{v}_o$ , f and  $\dot{f}$  can be estimated by both traditional GPIO and the presented reduced-order GPIO. However, the signal  $\dot{f}$  can not be estimated by the ESO in (4). Clearly, GPIOs (5) and (7) do estimate the derivative of lumped disturbances, while the ESO (4) does not. On the other hand, the order of reduced-order GPIO (7) is three, which is one order lower than the traditional GPIO (5). Such a reduced-order feature shall facilitate the practical implementation to some extent.

**Remark 2.** It is noted that there are many other types of disturbance estimators [46], such as high-gain ESO [39], [40], sliding mode disturbance observer [41], [42], disturbance observer [38], unknown input observer [43], uncertainty and disturbance estimator [44], and equivalent input

disturbance-based estimator [45]. A major difference between GPIO and other types of disturbance estimators is that GPIO can estimate both the perturbations and the derivatives of the perturbations. The reason for utilizing GPIO here is that the estimate of the derivative of perturbations can be used to improve the prediction accuracy within the predictive control algorithm.

The observer estimation errors are defined as  $\varepsilon_2 = \hat{v}_o - \dot{v}_o$ ,  $\varepsilon_3 = \hat{f} - f$  and  $\varepsilon_4 = \hat{f} - \dot{f}$ . Combining the DC-DC converter dynamics (3) with the observer dynamics (7) we have

$$\begin{cases} \dot{\varepsilon}_2 = -\beta_1 \varepsilon_2 + \varepsilon_3, \\ \dot{\varepsilon}_3 = -\beta_2 \varepsilon_2 + \varepsilon_4, \\ \dot{\varepsilon}_4 = -\beta_3 \varepsilon_2 - \ddot{f}. \end{cases}$$

(8)

2) Design of Optimized ADRC: Since most optimal control approaches do not directly impose disturbance/uncertain information into the optimization problem, we utilize an output predictive approach for the development of the optimized ADRC approach. The design of the proposed approach is performed by the following three steps:

*Step 1–Define of Cost Function:* The cost function to be optimized for the DC-DC buck converter is defined as follows

$$J = \frac{1}{2} \int_{0}^{T_{P}} \left[ (\hat{v}_{o}(t+\tau) - \hat{v}_{r}(t+\tau))^{2} + \rho(\hat{\mu}(t+\tau) - \hat{\mu}_{r}(t+\tau))^{2} \right] d\tau,$$

(9)

where  $T_P$  is the predictive period,  $\hat{v}_o(t + \tau)$  is the predicted output voltage,  $\hat{v}_r(t + \tau)$  is the desired future reference output voltage,  $\hat{\mu}(t + \tau)$  is the future duty ratio to be determined,  $\hat{\mu}_r(t + \tau)$  is the corresponding future duty ratio to achieve desired  $\hat{v}_r(t + \tau)$ , and  $\rho$  is a positive real number weighting on the control input, respectively.

Step 2–Output Voltage Prediction: Noting that the input relative degree of the DC-DC buck converter is two, the future output voltage  $v_o(t+\tau)$  is predicted by Taylor series expansion

$$v_o(t+\tau) \approx v_o(t) + \tau \dot{v}_o(t) + \dots + \frac{\tau^{2+r}}{(2+r)!} v_o^{[2+r]}(t),$$

(10)

where r is the control order (see [34] for detailed definition). It should be noticed that the output prediction approach in (10) is different from many existing continuous prediction approaches such as [35]–[37] in the sense that the control order r is restricted to be one therein, while could be larger than 1 for the predictive approach in this paper. This additional design of freedom increases the accuracy of prediction and the stability for higher-order nonlinear systems [34]. Define the control sequence (also known as decision variables) by

$$\hat{\mu}(t) = \left[\hat{\mu}(t), \ \dot{\hat{\mu}}(t)\right]^{+}$$

To facilitate the implementation, we set r = 1 for the DC-DC buck converter here. Therefore, the estimations of higher-order derivatives of the output voltage under consideration of the disturbances are calculated by

$$\ddot{v}_o(t) = b_0 \hat{\mu}(t) + \hat{f}(t),$$

(11)

$$\hat{v}_o(t) = b_0 \dot{\hat{\mu}}(t) + \dot{f}(t).$$

(12)

Based on the estimations of  $\hat{v}_o$  in (7),  $\hat{v}_o$  in (11) and  $\hat{v}_o$  in (12), the output voltage prediction  $\hat{v}_o(t+\tau)$  under the control sequence  $\hat{\mu}(t)$  is approximated by

$$\hat{v}_{o}(t+\tau) = v_{o}(t) + \tau \hat{\bar{v}}_{o}(t) + \frac{\tau^{2}}{2!} \hat{\bar{v}}_{o}(t) + \frac{\tau^{3}}{3!} \hat{\bar{v}}_{o}(t)$$

$$= \mathcal{T}(\tau)(\hat{U}(t) + \hat{X}(t)),$$

(13)

-2

where

where

$$\mathcal{T}(\tau) = \begin{bmatrix} 1, \ \tau, \ \frac{\tau^2}{2!}, \ \frac{\tau^3}{3!} \end{bmatrix},$$

$$\hat{X}(t) = \begin{bmatrix} v_o(t), \hat{v}(t), \hat{f}(t), \hat{f}(t) \end{bmatrix}^{\top}, \ \hat{U}(t) = \begin{bmatrix} 0, 0, b_0 \hat{u}^{\top}(t) \end{bmatrix}^{\top}.$$

Step 3-Receding Optimization: The reference signal and the control input can be written as

$$\hat{v}_{\tau}(t+\tau) = \mathcal{T}(\tau)Y_{\tau}(t) \tag{14}$$

$$v_r(v + r) = r(r)r(v),$$

(11)

$$\hat{\mu}(t+\tau) = \mathcal{F}(\tau)\hat{\mu}(t), \qquad (15)$$

and

$$\hat{\mu}_r(t+\tau) = \mathcal{F}(\tau)\hat{\mu}_r(t), \qquad (16)$$

where  $Y_r(t) = [v_r(t), \dot{v}_r(t), \ddot{v}_r(t), \ddot{v}_r(t)]^\top$ ,  $\mathcal{F}(\tau) = [1, \tau]$  and  $\hat{\mu}_r(t) = \left[\hat{\mu}_r(t), \hat{\mu}_r(t)\right]^{\top}$ . According to (3), the variables  $\hat{\mu}_r(t)$  and  $\hat{\mu}_r(t)$  are defined as

$$\hat{\mu}_r(t) = \frac{\ddot{v}_r(t) - \hat{f}(t)}{b_0}, \\ \hat{\mu}_r(t) = \frac{\ddot{v}_r(t) - \hat{f}(t)}{b_0}.$$

(17)

By virtue of (13)-(16), the performance index (9) is expressed as follows

$$J = \frac{1}{2} \int_{0}^{T_{P}} \left[ (\mathcal{T}(\tau)(\hat{X} + \hat{U} - Y_{r}))^{2} + \rho \left( \hat{\mu}^{\top} - \hat{\mu}_{r}^{\top} \right) \mathcal{F}^{\top}(\tau) \mathcal{F}(\tau) \left( \hat{\mu} - \hat{\mu}_{r} \right) \right] d\tau$$

$$= \frac{1}{2} (\hat{X}^{\top} + \hat{U}^{\top} - Y_{r}^{\top}) \bar{\mathcal{T}} (\hat{X} + \hat{U} - Y_{r})$$

$$+ \frac{1}{2} \rho \left( \hat{\mu}^{\top} - \hat{\mu}_{r}^{\top} \right) \bar{\mathcal{F}} \left( \hat{\mu} - \hat{\mu}_{r} \right),$$

(18)

where

$$\bar{\mathcal{T}} = \int_0^{T_P} \mathcal{T}^\top(\tau) \mathcal{T}(\tau) d\tau, \ \bar{\mathcal{F}} = \int_0^{T_P} \mathcal{F}^\top(\tau) \mathcal{F}(\tau) d\tau.$$

Matrix  $\overline{\mathcal{T}}$  is partitioned in the following sub-matrices

$$\bar{\mathcal{T}} = \begin{bmatrix} \bar{\mathcal{T}}_{22} & \bar{\mathcal{T}}_{21} \\ \bar{\mathcal{T}}_{21}^\top & \bar{\mathcal{T}}_{11} \end{bmatrix}$$

(19)

where the sub-matrices are all with dimension of  $2 \times 2$ . Taking partial derivative of J with respect to  $\hat{\mu}$  gives

$$\frac{\partial J}{\partial \hat{\mu}} = b_0 \left[ \bar{\mathcal{T}}_{21}^{\top}, \ \bar{\mathcal{T}}_{11} \right] (\hat{X} - Y_r) + (b_0^2 \bar{\mathcal{T}}_{11} + \rho \bar{\mathcal{F}}) \hat{\mu} - \rho \bar{\mathcal{F}} \hat{\mu}_r = b_0 \left[ \bar{\mathcal{T}}_{21}^{\top}, \ \bar{\mathcal{T}}_{11} + \rho \bar{\mathcal{F}} / b_0^2 \right] (\hat{X} - Y_r) + (b_0^2 \bar{\mathcal{T}}_{11} + \rho \bar{\mathcal{F}}) \hat{\mu}$$

(20)

Letting  $\partial J/\partial \hat{\mu} = 0$ , the optimized control law  $\hat{\mu}^*$  is obtained from (20) given below

$$\hat{\mu}^* = -\frac{1}{b_0} \left[ \left( \bar{\mathcal{T}}_{11} + \frac{\rho}{b_0^2} \bar{\mathcal{F}} \right)^{-1} \bar{\mathcal{T}}_{21}^\top, I_{2\times 2} \right] (\hat{X} - Y_r). \quad (21)$$

Taking the first row of the optimized control law (21), the control law to be applied to the plant is given by

$$\hat{\mu}^*(t) = C_{\mu} \hat{\mu}^*,$$

(22)

where  $C_{\mu} = [1, 0]$ .

Since the reference voltage  $V_r$  is a constant, the resultant optimized ADRC law is given by

$$\mu^*(t) = -\frac{1}{b_0} \left[ k_1 \left( v_o(t) - v_r(t) \right) + k_2 \hat{v}_o(t) + \hat{f}(t) \right], \quad (23)$$

where  $\hat{v}_o$  and  $\hat{f}$  are generated by the reduced-order G-PIO (7), and  $K = [k_1, k_2]$  is the first row of matrix  $\left(\bar{\mathcal{T}}_{11} + \frac{\rho}{b_0}\bar{\mathcal{F}}\right)^{-1}\bar{\mathcal{T}}_{21}^{\top}$ . The following lemma plays a key role in stability analysis of the presented control approach.

Lemma 1. The presented control law (23) with assigned control order r = 1 ensures that the characteristic function  $P(s) = s^2 + k_2 s + k_1$  is Hurwitz stable.

Proof: With the definition given in (23), the control gains  $k_1$  and  $k_2$  are calculated as

$$k_{1} = \frac{15T_{p}^{2}b_{0}^{2}(T_{p}^{4}b_{0}^{2} + 420\rho)}{T_{p}^{8}b_{0}^{4} + 1224\rho T_{p}^{4}b_{0}^{2} + 15120\rho^{2}},$$

$$k_{2} = \frac{6T_{p}^{3}b_{0}^{2}(T_{p}^{4}b_{0}^{2} + 7560\rho)}{T_{p}^{8}b_{0}^{4} + 1224\rho T_{p}^{4}b_{0}^{2} + 15120\rho^{2}}.$$

(24)

Since both the weighting factor  $\rho$  and the prediction period  $T_p$  are positive constants, the characteristic function P(s) = $s^{2} + k_{2}s + k_{1}$  is always Hurwitz stable. This completes the proof.

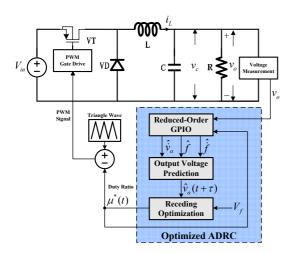

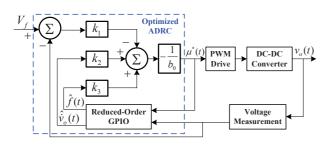

Note that the proposed control approach needs few numerous computations for practical implementation. Indeed, the presented controller consisting of (23) and (7) is rather concise and straightforward for implementation in the sense that the control law (23) acting as a common linear feedback control law, while (7) serving as a third order linear observer. The control structure and the implementation block diagram of the proposed optimized ADRC method for DC-DC buck converter are shown in Figs. 2 and 3, respectively.

#### B. Stability Analysis

Combining the DC-DC buck converter dynamics (3), the observer dynamics (7), and the control law (23), the closed-loop system dynamics are governed by the following expression

$$\ddot{e} + k_2 \dot{e} + k_1 e = -\varepsilon_3 - k_2 \varepsilon_2, \tag{25}$$

where  $\varepsilon_2$  and  $\varepsilon_3$  given by (8) are state and disturbance estimation errors of the reduced-order GPIO (7), respectively.

Remark 3. Similar to most of the existing disturbance estimator-based control approaches, see [23], [30], stability of the closed-loop system (8) and (25) could be easily established if the lumped disturbances f satisfy the condition of f = 0. However, the lumped disturbance is an uncertain function in terms of the states of the system, and rigorous stability of the closed-loop system is a rather complicated task.

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I-REGULAR PAPERS

Fig. 2. The control structure of the DC-DC buck converter under the proposed optimized ADRC control approach.

Fig. 3. The implementation block diagram of the DC-DC buck converter under the proposed optimized ADRC control approach.

In this section, we attempt to establish rigorous stability of the closed-loop system with general lumped disturbance f. The result is summarized in the following theorem.

**Theorem 1.** Consider the closed-loop system consisting of the DC-DC buck converter system (1), and the proposed optimized ADRC law (23) with the reduced-order GPIO (7). The observer gains are designed as  $\beta_i = \omega^i \overline{\beta}_i$  for i = 1, 2, 3where  $\omega > 0$  is an observer bandwidth factor to be assigned, and  $\overline{\beta}_i$  is selected such that the following inequalities hold for any  $\gamma_b = b/b_0 > 0$ , i.e.

$$\beta_1 > 0, \ \beta_2 > 0, (2 - 2\gamma_b)\bar{\beta}_1\bar{\beta}_2/\gamma_b < \bar{\beta}_3 < (2 - \gamma_b)\bar{\beta}_1\bar{\beta}_2/\gamma_b,$$

(26)

The rigorous stability of the closed-loop system can be guaranteed by choosing sufficiently large observer bandwidth factor  $\omega$ .

*Proof:* First, combining the plant dynamics (3), the observer estimation error (8) and the control law (23) with f, the dynamics of  $\ddot{f}$  is governed by

$$\ddot{f} = \delta_{e_1} e + \delta_{e_2} \dot{e} + \delta_{\varepsilon_2} (\beta_1, \beta_2) \varepsilon_2 + \delta_{\varepsilon_3} (\beta_1, \beta_2) \varepsilon_3 + \delta_{\varepsilon_4} \varepsilon_4 + \mu_b \beta_3 \varepsilon_2,$$

(27)

where

$$\begin{split} \mu_b &= (b-b_0)/b_0, \\ \delta_{e_1} &= -k_1 \varpi_1 + k_1 k_2 \varpi_2, \\ \delta_{e_2} &= -k_2 \varpi_1 + (k_2^2 - k_1) \varpi_2, \\ \delta_{\varepsilon_2} &= -k_2 \varpi_1 + (k_2^2 + k_2 \beta_1 + \beta_2) \varpi_2 \\ &- \mu_b \left( k_2 (\beta_1^2 - \beta_2) - \beta_1 \beta_2 \right), \\ \delta_{\varepsilon_3} &= - \varpi_1 + \mu_b \left( k_2 \beta_1 + \beta_2 \right), \\ \delta_{\varepsilon_4} &= - \varpi_2 - \mu_b k_2, \end{split}$$

with  $\varpi_1 = a_1 - \mu_b k_1$ ,  $\varpi_2 = a_2 - \mu_b k_2$ . Define  $\eta_2 = \omega^2 \varepsilon_2$ ,  $\eta_3 = \omega \varepsilon_3$  and  $\eta_4 = \varepsilon_4$ . Collecting the tracking error dynamics (25) and the observer error dynamics (8), the closed-loop system is given below

$$\begin{split} \dot{\xi} &= \underbrace{\begin{bmatrix} 0 & 1 \\ -k_1 & -k_2 \end{bmatrix}}_{A_{\xi}} \xi + \underbrace{\begin{bmatrix} 0 & 0 & 0 \\ -k_2 \omega^2 & -1/\omega & 0 \end{bmatrix}}_{B_{\xi}} \eta, \\ \dot{\eta} &= \omega \underbrace{\begin{bmatrix} -\bar{\beta}_1 & 1 & 0 \\ -\bar{\beta}_2 & 0 & 1 \\ -\gamma_b \bar{\beta}_3 - \mu_b \bar{\beta}_1 \bar{\beta}_2 & -\mu_b \bar{\beta}_2 & 0 \end{bmatrix}}_{A_{\eta}} \eta \\ &+ \underbrace{\begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ \tau_2(\omega) & \tau_3(\omega) & -\delta_{\epsilon_4} \end{bmatrix}}_{E_{\eta}} \eta \\ &+ \underbrace{\begin{bmatrix} 0 & 0 \\ 0 & 0 \\ -\delta_{e_1} & -\delta_{e_2} \end{bmatrix}}_{B_{\eta}} \xi, \end{split}$$

(28)

where  $\xi = [e_1, e_2]^{\top} = [e, \dot{e}]^{\top}, \ \eta = [\eta_2, \eta_3, \eta_4]^{\top}$ , and

$$\tau_2(\omega) = (k_2 \varpi_1 - k_2^2 \varpi_2 - k_2 \varpi_2 \omega)/\omega^2 + (\mu_b k_2 \bar{\beta}_1^2 - \mu_b k_2 \bar{\beta}_2 - \varpi_2 \bar{\beta}_2), \tau_3(\omega) = (\varpi_1 - \mu_b k_2 \bar{\beta}_1 \omega)/\omega.$$

With a choice of observer parameters  $\bar{\beta}_i$  satisfying the inequalities (26), it can be shown that matrix  $A_{\eta}$  is Hurwitz stable, indicating that there exists a symmetric positive definite matrix  $P_{\eta}$  such that

$$A_{\eta}^{\top} P_{\eta} + P_{\eta} A = -2I_{3\times3}.$$

(29)

It follows from Lemma 1 that the predictive control law (23) ensures that  $A_{\xi}$  is Hurwitz stable. Consequently, we also have that

$$A_{\xi}^{\top} P_{\xi} + P_{\xi} A_{\xi} = -2I_{2 \times 2}, \tag{30}$$

where  $P_{\xi}$  is also a symmetric positive definite matrix.

Define a composite candidate Lyapunov function as follows

$$V(\xi,\eta) = \frac{1}{2}\xi^{\top} P_{\xi}\xi + \frac{1}{2}\eta^{\top} P_{\eta}\eta.$$

(31)

Taking derivative of  $V(\xi, \eta)$  in (31) along the closed-loop

system dynamics (28) gives

$$\dot{V}(\xi,\eta) = - \|\xi\|^{2} - \omega \|\eta\|^{2} + \xi^{\top} P_{\xi} B_{\xi} \eta

+ \xi^{\top} B_{\eta}^{\top} P_{\eta} \eta + \frac{1}{2} \eta^{\top} (E_{\eta}^{\top} P_{\eta} + P_{\eta} E_{\eta}) \eta

\leq - \|\xi\|^{2} - \omega \|\eta\|^{2} + \|\xi\|^{2} / 4 + \|P_{\xi} B_{\xi}\|^{2} \|\eta\|^{2}

+ \|\xi\|^{2} / 4 + \|B_{\eta}^{\top} P_{\eta}\|^{2} \|\eta\|^{2}

+ \frac{1}{2} \|E_{\eta}^{\top} P_{\eta} + P_{\eta} E_{\eta}\| \cdot \|\eta\|^{2}

\leq - \|\xi\|^{2} / 2 - (\omega - \omega^{*}) \|\eta\|^{2},$$

(32)

where  $\omega^*$  is a sufficiently large positive constant regardless of  $\omega$ , determined by

$$\omega^* > \|P_{\xi}B_{\xi}\|^2 + \|B_{\eta}^{\top}P_{\eta}\|^2 + \frac{1}{2}\|E_{\eta}^{\top}P_{\eta} + P_{\eta}E_{\eta}\|.$$

Hence, for any  $\omega > \omega^*$ , the following holds

$$\dot{V}(\xi,\eta) \leq -\min\left\{\frac{1}{2},\omega-\omega^*\right\} \left(\|\xi\|^2+\|\eta\|^2\right), \qquad (33)$$

$$\leq -\gamma_v V(\xi,\eta),$$

where  $\gamma_v > 0$  is determined by

$$\gamma_v = \frac{\min\left\{1, 2(\omega - \omega^*)\right\}}{\max\left\{\lambda_{\max}(P_{\xi}), \lambda_{\max}(P_{\eta})\right\}},$$

with  $\lambda_{\min}(\bullet)$  and  $\lambda_{\max}(\bullet)$  representing the minimum and maximum eigenvalues of matrix  $\bullet$ . This completes the proof.

**Remark 4.** In most of existing ADRCs, the extended state observer is used to estimate the lumped disturbances including uncertainties. However, it is not clear how large amount of uncertainties can be handled by a designed ADRC law. In this paper, we propose a new approach ensuring qualitative robustness performance of the presented reduced-order GPIO-based control approach. As indicated in Theorem 1 in the paper, the qualitative relationship between controller parameters and circuit parameters ensuring stability is established.

**Remark 5.** The structure of the optimized ADRC law (23) is quite similar with the traditional ADRC law (6) with the gains  $k_1$  and  $k_2$  determined by the optimized design, which also indicates that the presented control law has a similar efficiency on controller operation in comparison with the traditional ADRC method. As clearly shown by (24) the optimized control gains  $k_1$  and  $k_2$  are functions of the predictive period  $T_P$  and control input weighting factor  $\rho$ . The purpose of the optimized design is that the parameters  $T_P$  and  $\rho$  in the performance index (9) is directly related to the tracking performance of closed-loop system. For example, the parameter  $T_P$  determines the transient performance (fast or slow), and the parameter  $\rho$ can be tuned to penalize the excessive control energy.

**Remark 6.** Theorem 1 reveals that it is necessary to assign a larger bandwidth factor  $\omega$  to gain more emphasized robustness/disturbance rejection performances. However, the measurement noises will be amplified by the observer if  $\omega$  is too large. Consequently, from a practical application perspective, the bandwidth factor  $\omega$  of the observer should be appropriately selected to trade off between robustness/disturbance

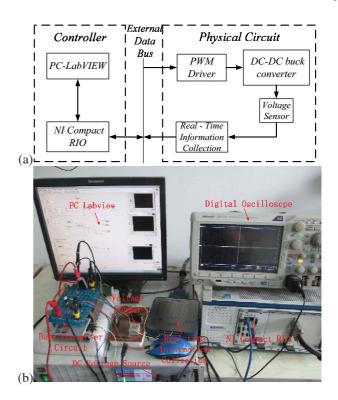

Fig. 4. (a) Configuration of experimental setup, (b) Photograph of the experimental prototype.

rejection performance and measurement noise attenuation. In addition, the existing noise attenuation approaches such as Kalman Filter could be combined with the presented approach to simultaneously enhance disturbance rejection and noise attenuation performances.

# IV. EXPERIMENTAL IMPLEMENTATION AND PERFORMANCE VALIDATION

The experimental test setup configuration and prototype are depicted in Fig. 4, comprising a DC-DC buck converter, a NI Compact RIO (embedded monitoring and control platform: NI PXIe-1078, NI R Series Multifunction RIO: NI PXI-7853R, NI LabVIEW Real-Time Module 12.0), a PC-LabVIEW2012, a programmable desktop laboratory DC power supplies (EA-PSI 9500-20 2U), a voltage sensor (VSM025A), etc. The nominal values of the parameters of the DC-DC buck converter are listed in Table I. The wordlength of the voltage AD converter is 16 Bits in the experimental test setup. The control algorithm is discretized using the basic forward difference approach. The controller updating period is 0.1 ms, and the sampling frequency for the experiment is  $f_s = 10$  kHz. The converter is controlled by a basic PWM gate drive; that is, the PWM driven signal is generated by comparing the duty ratio signal with a triangle wave signal. The fixed PWM switching frequency is  $f_{pwm} = 10$  kHz.

To evaluate the performance improvement of the proposed optimized ADRC method and enable fair comparison with conventional approaches, instead of assessing the power circuit specifications that extensively used for circuit topology and parameters design and analysis, two benchmark control

TABLE I

PARAMETERS OF THE DC-DC BUCK CONVERTER

| Parameter                | Symbol           | Value          |

|--------------------------|------------------|----------------|

| Input Voltage            | V <sub>in0</sub> | 100 V          |

| Reference Output Voltage | $V_f$            | 50 V           |

| Inductance               | Ľ                | 10 mH          |

| Capacitance              | C                | $1000 \ \mu F$ |

| Nominal Resistance       | $R_0$            | 50 Ω           |

approaches including traditional ADRC [21] and integral MPC [47] approaches are implemented accordingly. A tradeoff among various performances including satisfactory tracking (offset free, small overshoot, fast transient behaviour, etc.), disturbance rejection and robustness against parametric uncertainties must be taken into account when tuning the controller parameters in the paper. Consequently, fast transient performance is one of the most important control specifications but not the unique one for controller design and tuning. The fast transient behaviour can be easily achieved by assigning larger control gains for all the three controllers, however, this will inevitably degrade other control specifications such as larger overshoot, undesirable disturbance rejection and robustness performances. Since this paper is mainly concerned with disturbance rejection and robustness performance against uncertainties, our parameter tuning criterion is to assign adequate controller parameters ensuring similar satisfactory tracking performance for all the three control approaches. We then discuss and compare the disturbance rejection and robustness performance of the three control approaches. It is shown in later Figs. 5 and 6 that all the three controllers have quite similar tracking control performance. The control inputs (duty ratios) during the tracking task are quite similar as well. To this end, the controller parameters of the optimized ADRC law (23) are

$$k_1 = 4.15 \times 10^3, \ k_2 = 570,$$

$\beta_1 = 1.2 \times 10^4, \ \beta_2 = 4.8 \times 10^7, \ \beta_3 = 6.4 \times 10^{10}.$

The control parameters of the traditional ADRC law (with a reduced-order ESO) are

$$k_1 = 7000, \ k_2 = 300, \ \iota_1 = 8,000, \ \iota_2 = 1.6 \times 10^7.$$

The integral MPC controller parameters are

$$N_p = 75, \ N_c = 2, \ T_s = 3.53 \times 10^{-5}.$$

Then, the robustness performance of the proposed optimized ADRC method is tested for the DC-DC buck converters in the cases of various sources of disturbances and uncertainties.

#### A. Robustness Performance Test

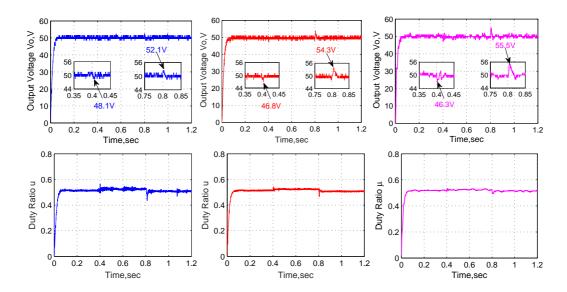

1) Case I-Robustness Against Sudden Load Resistance Changes: Here the load resistance is assumed to have sudden decrease and increase during the operating process. The load resistance settings are the following

$$R = \begin{cases} 50 \ \Omega \ (=R_0), & \text{for } t \in [0, \ 0.4) \text{ sec}, \\ 25 \ \Omega \ (=0.5R_0), & \text{for } t \in [0.4 \ 0.8) \text{ sec}, \\ 100 \ \Omega \ (=2R_0), & \text{for } t \in [0.8, \ 1.2] \text{ sec} \end{cases}$$

The experimental response curves of the output voltage and the duty ratio under the proposed optimized ADRC, traditional ADRC and integral MPC approaches are shown in Fig. 5.

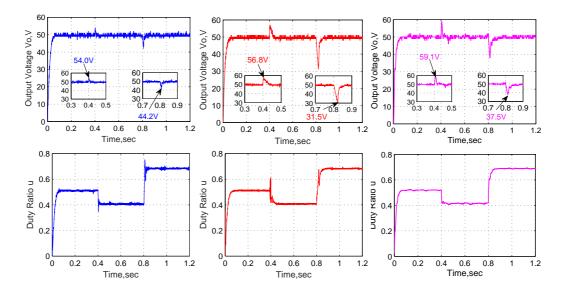

2) Case II-Robustness Against Input Voltage Variations: Here the robustness against input voltage variations of the proposed method is tested. The input voltage is take to vary as follows

$$V_{\rm in} = \begin{cases} 100 \ V \ (=V_{\rm in0}), & \text{for } t \in [0, \ 0.4) \ \text{sec}, \\ 125 \ V \ (=1.25V_{\rm in0}), & \text{for } t \in [0.4 \ 0.8) \ \text{sec}, \\ 75 \ V \ (=0.75V_{\rm in0}), & \text{for } t \in [0.8, \ 1.2] \ \text{sec} \end{cases}$$

The experimental response curves of the output voltage and the duty ratio under the proposed controller, traditional ADRC and integral MPC control approaches are hence shown in Fig. 6.

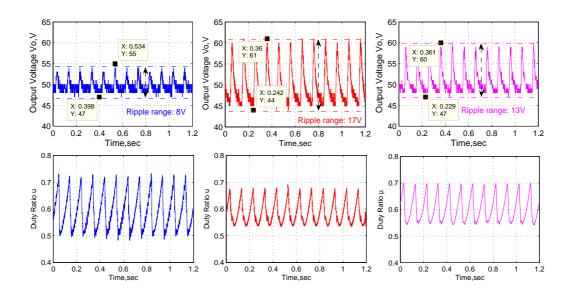

*3) Case III-Robustness Against Time-Varying Disturbances:* Here we further investigate robustness against time-varying disturbances of the proposed optimized ADRC approach. A generic sawtooth waveform of time-varying disturbance is taken to acting on the input voltage of the converter system. The frequency and amplitude of the disturbances are 10 Hz and 10V, respectively. Response curves of the output voltage and duty ratio in the presence of such a time-varying disturbance via the three control approaches are shown in Fig. 7.

It can be observed from the above three cases of experimental validation that although both the traditional ADRC and integral MPC approaches could remove the offset caused by load resistance change and input voltage variations, fail to remove the offset caused by time-varying disturbances (it should be noted that integral MPC is superior than TADRC). As shown by Figs. 5-7, the proposed optimized ADRC (based on the usefulness of the ADRC method) further improves transient and static performance in the presence of various disturbances and uncertainties including load resistance changes, output voltage variations and time-varying disturbances compared to the other approaches. It is also observed from Figs. 5 and 6 that the maximum output voltage drop/raise (MOVD/MOVR) of the proposed optimized ADRC approach is lesser than those provided by the traditional ADRC and integral MPC methods. Similarly, the recovery time after sudden load changes and input voltage variations of the optimized ADRC method is much shorter than those of the other two approaches. For completeness the performance indices (MOVD, MOVR, maximum recovery time (MRT) and integral of absolute error (IAE)), comparison among the three control approaches is shown in Table II.

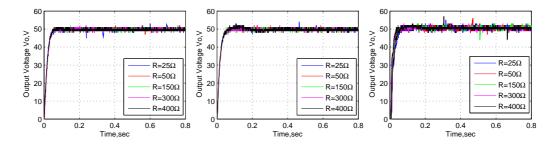

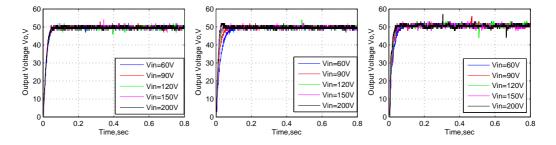

#### B. Adaptive Capacity Verification

Here the adaptive capacity of the proposed optimized ADRC with respect to various load resistance change and input voltage variations is investigated. The response curves of the output voltage under the three controllers in the presence of different load resistance changes and input voltage variations are shown by Fig. 8 and Fig. 9, respectively.

The results shown in the aforementioned figures illustrate that the output voltage responses of the proposed optimized ADRC approach (which inherits good properties of traditional

Fig. 5. Variable response curves of DC-DC buck converter via optimized ADRC (left), traditional ADRC (middle) and integral MPC (right) control, in the presence of sudden load resistance changes (top: o/p voltage; bottom: duty ratio).

Fig. 6. Variable response curves of DC-DC buck converter under the optimized ADRC (left), traditional ADRC (middle) and integral MPC (right) control, in the presence of sudden input voltage variations (top: o/p voltage; bottom: duty ratio).

TABLE II EXPERIMENTAL PERFORMANCE INDICES OF OPTIMIZED ADRC (OADRC), TRADITIONAL ADRC (TADRC) AND INTEGRAL MPC CONTROLLER

| Test Type | Performance | Controllers |        |              |

|-----------|-------------|-------------|--------|--------------|

|           |             | OADRC       | TADRC  | Integral MPC |

| Case I    | MOVR (V)    | 2.1         | 4.3    | 5.5          |

|           | MOVD (V)    | 1.9         | 3.2    | 3.7          |

|           | MRT (sec)   | 0.0064      | 0.0188 | 0.0350       |

|           | IAE (V)     | 0.5988      | 0.6564 | 0.6030       |

| Case II   | MOVR (V)    | 4.0         | 6.8    | 9.1          |

|           | MOVD (V)    | 5.8         | 18.5   | 12.5         |

|           | MRT (sec)   | 0.0292      | 0.0716 | 0.0862       |

|           | IAE (V)     | 0.234       | 0.4412 | 0.6200       |

| Case III  | IAE (V)     | 1.3844      | 4.396  | 2.8850       |

ADRC) under the given variations offers an almost flat response in all cases. This illustrates the efficacy of the adaptive capacity of the proposed control solution.

## V. CONCLUSION

The work in this paper has addressed the current sensorless optimized ADRC design problem for a generic DC-DC buck converter subject to multiple sources of disturbances including load resistance mutation, input voltage variation, etc. To facilitate practical implementation, a novel reduced-order GPIO has been proposed for the involved lumped time-varying disturbance estimation. Moreover, disturbance estimations have been incorporated into the output voltage prediction process largely improving the output prediction accuracy. Different from most of existing disturbance estimator-based control approaches,

Fig. 7. Variable response curves of DC-DC buck converter under the optimized ADRC (left), traditional ADRC (middle) and integral MPC (right) control, in the presence of time-varying disturbances (top: o/p voltage; bottom: duty ratio).

Fig. 8. Output voltage response curves of DC-DC buck converter in the presence of various load resistance changes under the optimized ADRC (left), traditional ADRC (middle) and integral MPC control (right) approaches.

Fig. 9. Output voltage response curves of DC-DC buck converter in the presence of various input voltage variations under the optimized ADRC (left), traditional ADRC (middle) and integral MPC (right) control approaches.

including traditional ADRC, a rigorous analysis on robustness stability has been provided for the proposed optimized ADRC method. The experimental results on the power converter have shown that overall the proposed optimized method outperforms both traditional ADRC and integral MPC approaches in the presence of various disturbances and uncertainties.

# REFERENCES

- M. Kumar, and R. Gupta, "Stability and sensitivity analysis of uniformly sampled DC-DC converter with circuit parasitics," *IEEE Trans. Circuits Syst. I-Regul. Pap.*, vol. 63, no. 11, pp. 2086-2097, 2016.

- [2] S. Lee, S. Jung, C. Park, C.-T. Rim, and G.-H. Cho, "Accurate dead-time control for synchronous buck converter with fast error sensing circuits," *IEEE Trans. Circuits Syst. I-Regul. Pap.*, vol. 60, no. 11, pp. 3080-3089, 2013.

- [3] H.C. Foong, Y. Zheng, Y.K. Tan, and M.T. Tan, "Fast-transient integrated digital DC-DC converter with predictive and feedforward control," *IEEE Trans. Circuits Syst. I-Regul. Pap.*, vol. 59, no. 7, pp. 1567-1576, 2012.

- [4] G. Garcerá, E. Figueres, and A. Mocholí, "Novel three-controller average current mode control of DC-DC PWM converters with improved robustness and dynamic response," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 516-528, 2000.

- [5] S.K. Mazumder, H.N. Ali, and D. Borojević, "Robust control of parallel DC-DC buck converters by combining integral-variable-structure and multiple-sliding-surface control schemes," *IEEE Trans. Power Electron.*,

vol. 17, no.3, pp. 428-437, 2002.

- [6] E. Figueres, G. Garcerá, J.M. Benavent, M. Pascual, and J.A. Martínez, "Adaptive two-loop voltage-mode control of DC-DC switching converters," *IEEE Trans. Ind. Electron.*, vol. 53, no. 1, pp. 239-253, 2006.

- [7] C.H. Rivetta, A. Emadi, G.A. Williamson, R. Jayabalan, and B. Fahimi, "Analysis and control of a buck DC-DC converter operating with constant power load in sea and undersea vehicles," *IEEE Trans. Ind. Appl.*, vol. 42, no. 2, pp. 559-572, 2006.

- [8] S. Kapat, P.S. Shenoy, and P.T. Krein, "Near-null response to large-signal transients in an augmented buck converter: A geometric approach," *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3319-3329, 2012.

- [9] M. Somnath, "Dynamics and stability issues of a discretized slidingmode controlled DC-DC buck converter governed by fixed-event-time switching," *IEEE Trans. Circuits Syst. I-Regul. Pap.*, vol. 60, no. 6, pp. 1657-1669, 2013.

- [10] R. Ling, D. Maksimovic, and R. Leyva, "Second-order sliding-mode controlled synchronous buck DCCDC converter," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 2539-2549, 2016.

- [11] J.-Y. Lee and H.-J. Chae, "6.6-kW onboard charger design using DCM PFC converter with harmonic modulation technique and two-stage DC/DC converter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 3, pp. 1243– 1252, 2014.

- [12] J. Sha, J. Xu, S. Zhong, S. Liu, and L. Xu, "Control pulse combinationbased analysis of pulse train controlled DCM switching DC-DC converters," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 246–255, 2015.

- [13] D. Flores Cortez, G. Waltrich, J. Fraigneaud, H. Miranda, and I. Barbi, "DC-DC converter for dual voltage automotive systems based on bidirectional hybrid switched-capacitor architectures," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 3296–3304, 2015.

- [14] S.-C. Tan, Y.-M. Lai, and C. K. Tse, "General design issues of slidingmode controllers in DC–DC converters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1160–1174, 2008.

- [15] B. Sun and Z. Gao, "A DSP-based active disturbance rejection control design for a 1-kW H-bridge DC-DC power converter," *IEEE Trans. Ind. Electron.*, vol. 52, no. 5, pp. 1271–1277, 2005.

- [16] C. Zhang, J. Wang, S. Li, B. Wu, and C. Qian, "Robust control of PWMbased DC-DC buck converters with uncertainty via sampled-data output feedback," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 504–515, 2015.

- [17] J.X. Wang, S.H. Li, J. Yang, B. Wu, and Q. Li, "Extended state observer-based sliding mode control for PWM-based DC-DC buck power converter systems with mismatched disturbances," *IET Control Theory and Applications*, vol. 9, no. 4, pp. 579–586, 2015.

- [18] O. König, G. Gregorčič, and S. Jakubek, "Model predictive control of a DC–DC converter for battery emulation," *Control Eng. Practice*, vol. 21, no. 4, pp. 428–440, 2013.

- [19] J. Rodriguez, M. P. Kazmierkowski, J. R. Espinoza, P. Zanchetta, H. Abu-Rub, H. A. Young, and C. A. Rojas, "State of the art of finite control set model predictive control in power electronics," *IEEE Trans. Ind. Inform.*, vol. 9, no. 2, pp. 1003–1016, 2013.

- [20] A. Beccuti, M. Kvasnica, G. Papafotiou, and M. Morari, "A decentralized explicit predictive control paradigm for parallelized DC-DC circuits," *IEEE Trans. Control Syst. Technol.*, vol. 21, no. 1, pp. 136–148, 2013.

- [21] J. Han, "From PID to active disturbance rejection control," *IEEE Trans. Ind. Electron.*, vol. 56, no. 3, pp. 900-906, 2009.

- [22] Y. Huang and X. Xue, "Active disturbance rejection control: methodology and theoretical analysis," *ISA Trans.*, vol. 53, no. 4, pp. 963-976, 2014.

- [23] S. Li, J. Yang, W.-H. Chen, and X. Chen, "Generalized extended state observer based control for systems with mismatched uncertainties," *IEEE Trans. Ind. Electron.*, vol. 59, no. 12, pp. 4792–4802, 2012.

- [24] H. Sira-Ramírez, J. Linares-Flores, C. García-Rodríguez, and M. A. Contreras-Ordaz, "On the control of the permanent magnet synchronous motor: An active disturbance rejection control approach," *IEEE Trans. Control Syst. Technol.*, vol. 22, no. 5, pp. 2056-2063, 2014.

- [25] Q. Zheng, L. Dong, D. H. Lee, and Z. Gao, "Active disturbance rejection control for MEMS gyroscopes," *IEEE Trans. Control Syst. Technol.*, vol. 17, no. 6, pp. 1432-1438, 2009.

- [26] D. Wu and K. Chen, "Design and analysis of precision active disturbance rejection control for noncircular turning process," *IEEE Trans. Ind. Electron.*, vol. 56, on. 7, pp. 2746-2753, 2009.

- [27] J. Su, W. Qiu, H. Ma and P.Y. Woo, "Calibration-free robotic eye-hand coordination based on an auto disturbance-rejection controller," *IEEE Trans. Robot.*, vol. 20, no. 5, pp. 899-907, 2004.

- [28] D. Qiu, M. Sun, Z. Wang, Y. Wang and Z. Chen, "Practical winddisturbance rejection for large deep space observatory antenna," *IEEE Trans. Control Syst. Technol.*, vol. 22, no. 5, pp. 1983-1990, 2014.

- [29] W. Xue, W. Bai, S. Yang, K. Song, Y. Huang and H. Xie, "ADRC with adaptive extended state observer and its application to air-fuel ratio control in gasoline engines," *IEEE Trans. Ind. Electron.*, vol. 62, on. 9, pp. 5847-5857, 2015.

- [30] S. Li, J. Yang, W.-H. Chen, and X. Chen, Disturbance Observer Based Control: Methods and Applications. CRC Press, Florida, USA, 2014.

- [31] J. Yang, S. Li, and X. Yu, "Sliding-mode control for systems with mismatched uncertainties via a disturbance observer," *IEEE Trans. Ind. Electron.*, vol. 60, no. 1, pp. 160–169, 2013.

- [32] M. Morari and U. Maeder, "Nonlinear offset-free model predictive control," *Automatica*, vol. 48, no. 9, pp. 2059-2067, 2012.

- [33] M. Fliess, R. Marquez, E. Delaleau, and H. Sira-Ramirez, "Generalized proportional-integral controllers," *ESAIM: Control, Optimization and Calculus of Variations*, vol. 7, pp. 23–41, 2002.

- [34] W.-H. Chen, D. Ballance, and P. Gawthrop, "Optimal control of nonlinear systems: a predictive control approach," *Automatica*, vol. 39, no. 4, pp. 633–641, 2003.

- [35] C.K. Ahn, P. Shi, and M.V. Basin. "Deadbeat dissipative FIR filtering," *IEEE Trans. Circuits Syst. I-Regul. Pap.*, vol. 63, no. 8, pp. 1210-1221, 2016.

- [36] C.K. Ahn, Y.S. Shmaliy, P. Shi, and Y. Zhao. "Receding-horizon  $l_2 l_{\infty}$ FIR filter with embedded deadbeat property," *IEEE Trans. Circuits Syst. II-Express Briefs*, vol. 64, no. 2, pp. 211-215, 2017.

- [37] C.K. Ahn, P. Shi, and L. Wu. "Receding horizon stabilization and disturbance attenuation for neural networks with time-varying delay," *IEEE T. Cybern.*, vol. 45, no. 12, pp. 2680-2692, 2015.

- [38] K. Ohishi, M. Nakao, K. Ohnishi, and K. Miyachi, "Microprocessor controlled dc motor for load-insensitive position servo system," *IEEE Trans. Ind. Electron.*, vol. 34, no. 1, pp. 44–49, 1987.

- [39] L. Jiang, Q. H. Wu, J. Y. Wen. "Decentralized nonlinear adaptive control for multi-machine power systems via high-gain perturbation observer," *IEEE Trans. Circuits Syst. I-Regul. Pap.*, vol. 51, no. 10, pp. 2052–2059, 2004.

- [40] Q. H. Wu, L. Jiang, J. Y. Wen. "Decentralised adaptive control of nonlinear systems using high gain observer," *Int. J. Control*, vol. 77, no. 8, pp. 703–712, 2004.

- [41] H. Elmali and N. Olgac, "Sliding mode control with perturbation estimation (SMCPE): a new approach," *Int. J. Control*, vol. 56, pp. 923– 941, 1993.

- [42] J. T. Moura, H. Elmali, and N. Olgac, "Sliding mode control with sliding perturbation observer," J. Dyn. Syst. Meas. Control-Trans. ASME, vol. 119, pp. 657–665, 1997.

- [43] C. D. Johnson, "Optimal control of the linear regulator with constant disturbances," *IEEE Trans. Autom. Control*, vol. 13, no. 4, pp. 416–421, 1968.

- [44] Q.-C. Zhong, A. Kuperman, and R.-K. Stobart, "Design of UDE-based controllers from their two-degree-of-freedom nature," *Int. J. Robust Nonlinear Control*, vol. 17, no. 21, pp. 1994–2008, 2011.

- [45] J. H. She, M. X. Fang, Y. Ohyama, H. Hashimoto, and M. Wu, "Improving disturbance-rejection performance based on an equivalent input disturbance approach," *IEEE Trans. Ind. Electron.*, vol. 55, no. 1, pp. 380–389, 2008.

- [46] W.-H. Chen, J. Yang, L. Guo, and S. Li, "Disturbance-observer-based control and related methods–An overview," *IEEE Trans. Ind. Electron.*, vol. 63, no. 2, pp. 1083–1095, 2016.

- [47] L. Wang, Model Predictive Control System Design and Implementation Using MATLAB, London: Springer, 2009.

Jun Yang (M'11) received his B.Sc. degree in the Department of Automatic Control from Northeastern University, Shenyang, China in 2006. In 2011, he received his Ph.D. degree in control theory and control engineering from School of Automation, Southeast University, Nanjing, China, where he is currently an Associate Professor. His research interests include disturbance estimation and compensation, advanced control theory and its application to flight control systems and motion control systems. He is an Associate Editor of the TRANSACTIONS OF THE

INSTITUTE OF MEASUREMENT AND CONTROL.

#### IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I-REGULAR PAPERS

**Hongyu Cui** (SM'06) was born in Dongtai, Jiangsu Province, China in 1991. He received the B.Sc degree from School of Automation in Southeast University, Nanjing, China in 2014. He received the Master degree in control engineering from School of Automation in Southeast University in 2017. His research interests focus on the applications of advanced control strategies in power electronic system and servo system.

Shihua Li (SM'10) received his bachelor, master, Ph.D. degrees all in Automatic Control from Southeast university, Nanjing, China in 1995, 1998 and 2001, respectively. Since 2001, he has been with School of Automation, Southeast University, where he is currently a professor and the director of Mechatronic Systems Control Laboratory. His main research interests lie in modeling, analysis and nonlinear control theory with applications to mechatronic systems, including manipulator, robot, AC motor, power electronic systems and others.

Argyrios Zolotas is a Reader in College of Science and Deputy Director of Research in the School of Engineering. He joined Lincoln in 2014, while previously held academic positions at University of Sussex and Loughborough University, and a Post-Doctoral Research Fellowship at Imperial College London. Argyrios leads research in the area of integrated systems and control design. He is an expert on feedback control systems analysis and design (robust control and fault tolerant control), sensor configuration for control and fault tolerance, control

applications in railway engineering, system complexity and robustness.