# Optimized low voltage low power dynamic comparator robust to process, voltage and temperature variation

Julie Roslita Rusli<sup>1</sup>, Suhaidi Shafie<sup>2</sup>, Roslina Mohd Sidek<sup>3</sup>, Hasmayadi Abdul Majid<sup>4</sup>, W. Z. Wan Hassan<sup>5</sup>, M.A. Mustafa<sup>6</sup>

<sup>1</sup>British Malaysia Institute, Universiti Kuala Lumpur (UNIKL BMI), Malaysia <sup>1,2,3,5,6</sup>Department of Electrical and Electronic Eng., Universiti Putra Malaysia (UPM), Malaysia <sup>2,3</sup>System-on-Chip Research Centre, Universiti Putra Malaysia (UPM), Malaysia <sup>2</sup>Institute of Advanced Technology (UPM), Malaysia <sup>4</sup>Nano Semiconductor Tech. Department., MIMOS BERHAD TEC., Malaysia

#### **Article Info**

## Article history:

Received May 27, 2019 Revised Jul 2, 2019 Accepted Jul 16, 2019

## Keywords:

Dynamic comparator Double-tail dynamic comparator Low power comparator ADC SAR ADC

## Corresponding Author:

Julie Roslita Rusli, Electronics Department, UNIKL BMI, Selangor, Malaysia, Email: julie@unikl.edu.my

## **ABSTRACT**

Power consumption and speed are the main criteria in designing comparator for analog-to-digital converter (ADC). This paper presents an optimized low voltage low power dynamic comparator which is robust to process, voltage and temperature (PVT) variations with adequate speed. The comparator circuit was designed using  $0.18\mu m$  CMOS technology with low voltage supply of 0.8V. The method used to verify the robustness of the comparator circuit across 45 PVT is presented. The circuit is simulated with 10% voltage supply variation, five process corners and temperature variation from  $0^{\circ}C$  to  $100^{\circ}C$ . The simulation result show that the proposed comparator circuit achieved significant reduction of power consumption and delay during worst case condition compared to dynamic comparator proposed from previous researchers.

Copyright © 2020 Institute of Advanced Engineering and Science.

All rights reserved.

783

#### 1. INTRODUCTION

Energy efficiency is the main key parameter in many emerging system-on-chip (SoC) applications such as wireless sensor networks and portable electronics devices [1, 2]. Due to the high demand of such ultralow power applications, the needs for energy efficient analog-to-digital converter (ADC) are really essential. Among ADC architectures, successive approximation register ADC (SAR ADC) consumes relatively low power with acceptable speed and resolution [3, 4]. In SAR ADC, comparator is the main block to convert analog signal into digital code [5]. As a critical block, comparator needs to be robust enough to operate with low supply voltage in order to achieve low power consumption [5]. To ensure the robustness of a design, process corner simulation is required at the design stage. Process corner represents the extremes parameter variation of integrated circuit design which is fabricated on semiconductor wafer [6-15]. Parameter variations include range of process transistor properties, supply voltages and die temperatures [8, 9]. In nanoscale technology, scaling down of voltage supply near to threshold voltage can provide excessive savings in dynamic energy. However it will reduce the voltage headroom for cascode structure to operate correctly [7-17]. Therefore, to design low voltage and low power dynamic comparator with low supply voltage is a big challenge when the number of transistor stacking is high [16-23].

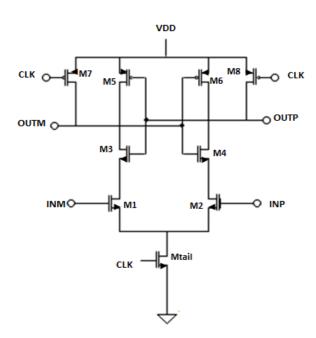

The most popular energy efficient comparator is dynamic comparator Figure 1 which only operates during regeneration time [2-18]. The additional features are high input impedance, rail to rail output swing, zero static power, low offset voltage and fast decision making that comes from strong positive feedback and

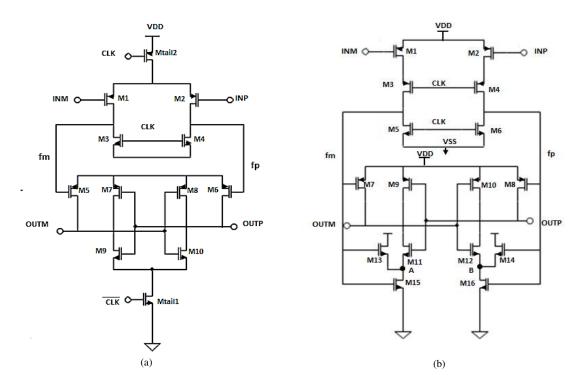

differential input architecture [1-22]. However, this topology requires high supply voltage to operate the circuit because numbers of transistors stacking are high. For this reason, this topology is perceived to be unsuitable for ultra-dep sub-micrometer CMOS technology with limited supply voltage and small voltage headroom. To overcome these issues, in [10], had proposed double-tail dynamic comparator with double-tail topology by splitting the pre-amplifier and latching stage Figure 2(a). The objective is to reduce the number of stacking transistor and at the same time improve the current flow in the small voltage headroom [1, 10, 24]. However, this topology consumes high power consumption because of pre-amp and latching stage operates at the same duration [1]. Further, the two phase latching clock method also contributes to high energy consumption, large die area and increase delay at regeneration time [12]. In [12], proposed modification of double-tail dynamic comparator which is known as pseudo differential dynamic comparator Figure 2(b). The tail transistor in latching stage was removed and only one clock phase is required to trigger the circuit. In this topology, the skew between two phases of latching clock has been eliminated and at the same time, the offset voltage can be reduced [10]. However this topology consumes high power consumption due to additional reset transistors in the circuit.

In [10] and [12], have proposed dynamic comparators with optimization on power consumption and speed. However, there are no details verification result over 45 process corners variation that have been recorded. This paper presents a new low power low voltage dynamic comparator which is robust to 45 process corners variation as shown in Section 2. A verification method used to verify the robustness of proposed comparator over 45 process corner variation is explained in Section 3. The process corner simulation result and performance comparison over PVT variation of proposed comparator. In [10] and [12], comparator is presented in Section 4. For simulation, 0.18µm CMOS technology at 0.8 supply voltage (VDD) and 0.4 voltage common mode (VCM) is set and PMOS is used as differential input transistor.

Figure 1. Schematic diagram of the conventional dynamic comparator

## 2. DESIGN METHODOLOGY

## 2.1. Conventional Double-Tail Dynamic Comparator

The first double-tail dynamic comparator was proposed by *Schinkel in 2007* Figure 2(a). In this topology, the number of stacking transistor was reduced by splitting pre-amplifier and latching stage. By introducing two stages dynamic comparator or double-tail dynamic comparator, individual tail transistors *Mtail1* and *Mtail2* are used in pre-amp and latching stages. The *Mtail1* at latching stage enables the large current to enhance latching speed while *Mtail2* allows small current flow at pre-amp stage to achieve low offset voltage at input comparator [10]. This comparator circuit operates in two conditions; reset phase and regeneration phase. During reset phase, CLK = VDD both *Mtail* are in OFF condition, transistors *M5/M6* reset node *fm / fp* to GND and pull OUTP /OUTM to VDD. In regeneration phase, CLK = GND both *Mtail* are turned ON, transistors *M5/M6* are turned OFF and voltage at node *fm / fp* start to drop with the rate of

*IMtail1/Cfm(fp)*. During this time, a voltage different at node *fm* and *fp* is developed and it becomes a gain to the latch state. This topology has less kickback noise due to the isolation between input and output node [1-10]. However, this topology consumes high power because of pre-amp and latching stage start to operate at the same duration [1-25]. Further, the two phase latching clock method also contributes to high energy consumption, large die area and increase delay at regeneration time [10].

Figure 2. Schematic of (a) Schinkel's comparator (b) Paik's comparator

## 2.2. Pseudo Differential Dynamic Comparator

In [12], proposed pseudo differential dynamic comparator Figure 2(b). The design is based on Schinkel's 2007 comparator with modification on the tail transistor in latching stage. In this design, only one clock phase is required to trigger the circuit. The latching stage is triggered by signal from output of a preamplifier [12]. The operations of this comparator are similar to conventional double-tail dynamic comparator which begins by resetting phase in pre-amplifier and followed by regeneration phase. During reset phase, CLK = VDD, *M3/M4* are OFF while *M5/6* are ON. Then, the output pre-amplifier node *fm/fp* will be reset to ground. Thus, *M7/M8* at latching stage turns ON and pulls node *OUTM/OUTP* to VDD while *M13/M14* and *M15/M16* are turned off causing latching phase not to be activated. When CLK=GND, regeneration phase, *M3/M4* are ON while *M5/6* are OFF. The drain current *M3/M4* is determined by input voltage at INP and INM. The different rate of current flow per time at node *A/B* develops high voltage different as time passes by. It becomes an input gain to the latching stage. In this topology, the skew between two phases of latching clock has been eliminated and at the same time, the offset voltage can be reduced [10].

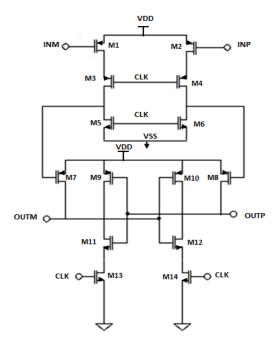

## 2.3. Low Voltage Low Power Comparator Design

From the performance of process corner simulation result in Paik and Schinkel comparator, we proposed new low voltage low power comparator as given in Figure 3. The improvement focuses on power consumption and delay during PVT variation as shown in Table 3. Due to good performance of Paik's comparator, some modifications have been done in order to improve the power consumption and delay of the circuit when it operates with 0.8V voltage supply and 0.8mV input voltage different ( $\Delta$ Vin). The same topology in Paik's comparator was used in this comparator but transistor M13/M14 was removed. In Paik's comparator, this transistor is used to reset the node A and B to reduce mismatch between M15/M16. However, this feature is not necessary in medium speed because it induced additional power consumption and delay.

786 🗖 ISSN: 2502-4752

Figure 3. Schematic of proposed comparator'

## 2.4. PVT Verification Method

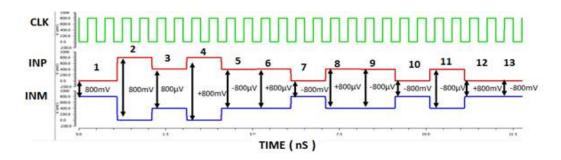

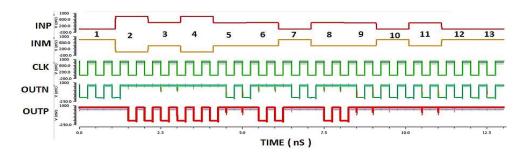

To verify the performance of each comparator, test setup as in Table 1 was used during 45 corner simulation. The clock frequency was set to 2 MHz and the period of each test sequence is set to 1 $\mu$ S. Both differential input positive (INP) and input negative (INM) are set in two worst condition of  $\Delta$ Vin, small  $\Delta$ Vin = 800 $\mu$ V and big  $\Delta$ Vin = 800mV. This worst condition of  $\Delta$ Vin selected based on the maximum and minimum different of input voltage for the proposed comparator which are 800mV and 800 $\mu$ V. The minimum input different 800 $\mu$ V is the 1/2 LSB for 10 bits digital output. The four values of input voltage are used to create input test pattern (small  $\Delta$ Vin = 800 $\mu$ V and big  $\Delta$ Vin = 800mV) as shown in Figure 4. For test pattern (big  $\Delta$ Vin), as shown in Figure 4, the test sequence 2, the INP is set at voltage 800mV and INM is set at voltage 0V. For test pattern (small  $\Delta$ Vin), as shown in Figure 4, the test sequence 3, the INP is set at voltage 400.4mV and INM is set at voltage 399.6mV. The order of test sequence in Table 1 is set based on the transition of input level in worst case condition. From the sequence we can observe the performance of the comparator in the worst case condition of input different and variation of process, voltage and temperature.

To verify the robustness of the circuit through fabrication process, voltage and temperature (PVT) variation, 45 process corner simulations is required. In corner simulation setup, PVT parameter was set to fabrication process corner (FS; SS; SF; TT; FF), voltage supply (VDD) (720mV; 800mV; 880mV) and temperature (0°C; 27°C; 100°C). The parameter of VDD is based on 10% voltage variation and temperature is based on low temp 0°C room temp 27°C and high temp 100°C. The detail of transistor condition over process corner variation is stated in Table 2. For process F, transistor is operating at high speed and at the same time consumes high power while for S process; transistor is in worst speed and low power condition.

Figure 4. Waveform of input test pattern

| Table 1. Details of Input Test Setup | Table | 1. | Detail | s of | Input | Test | Setup |

|--------------------------------------|-------|----|--------|------|-------|------|-------|

|--------------------------------------|-------|----|--------|------|-------|------|-------|

| Test     | Time        | Input   |          | Voltage Input                  |

|----------|-------------|---------|----------|--------------------------------|

| Sequence | Period (µS) | INP(mV) | INM (mV) | Different                      |

| 1        | 0-1         | 0       | 800      | $-\Delta Vin = -800mV$         |

| 2        | 1-2         | 800     | 0        | $+\Delta Vin = +800mV$         |

| 3        | 2-3         | 400.4   | 399.6    | $+\Delta Vin = +800uV$         |

| 4        | 3-4         | 800     | 0        | $+\Delta Vin = +800mV$         |

| 5        | 4-5         | 399.6   | 400.4    | $-\Delta Vin = -800\mu V$      |

| 6        | 5-6         | 400.4   | 399.6    | $+\Delta Vin = +800\mu V$      |

| 7        | 6-7         | 0       | 800      | $-\Delta Vin = -800 mV$        |

| 8        | 7-8         | 400.4   | 399.6    | $+\Delta Vin = +800 \mu V$     |

| 9        | 8-9         | 399.6   | 400.4    | $-\Delta Vin = -800\mu V$      |

| 10       | 9-10        | 0       | 800      | $-\Delta Vin = -800 \text{mV}$ |

| 11       | 10-11       | 399.6   | 400.4    | $-\Delta Vin = -800 \mu V$     |

| 12       | 11-12       | 800     | 0        | $+\Delta Vin = +800mV$         |

| 13       | 12-13       | 0       | 800      | $-\Delta Vin = -800mV$         |

Table 2. Standard Fabrication Process Corner Parameter

| Corner Parameter | Condition            |                      |  |  |

|------------------|----------------------|----------------------|--|--|

| Corner Farameter | NMOS                 | PMOS                 |  |  |

| FF               | FAST – high mobility | FAST – high mobility |  |  |

| SS               | SLOW - low mobility  | SLOW - low mobility  |  |  |

| TT               | TYPICAL - nominal    | TYPICAL - nominal    |  |  |

| FS               | FAST – high mobility | SLOW - low mobility  |  |  |

| SF               | SLOW - low mobility  | FAST – high mobility |  |  |

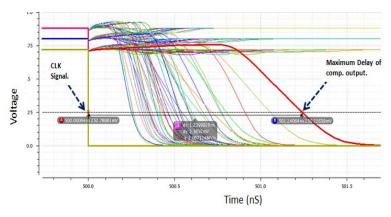

## 2.5. Power Consumption and Delay Measurement Method

To measure average power consumption from the comparator circuits, the expression (1) was set in Calculator tools in Virtuoso Visualization Analysis XL and Analog Design Environment (ADE). In calculator windows, select option *average* from Function Panel for measuring average power consumption, and then choose *IT* from Schematic Selection Toolbar for *transient current*. The *V20/PLUS* in (1) represents voltage supply for comparator circuit. To measure the maximum and minimum power consumption, the expression (1) needs to be set in process corner simulation setup. Worst case delay measured at voltage VDD/2 is shown in Figure 5.

$$(average (IT("/V20/PLUS")) * 0.8)$$

(1)

Figure 5. Maximum delay process corner simulation result of proposed comparator

## 3. SIMULATION RESULT AND DISCUSSION

The simulation result and comparison of the proposed design with *Paik's* and *Schinkel's* comparator is presented in this section.

## 3.1. Functional Simulation

Figure 6 shows 45 process corner simulation of proposed comparator design. The comparator passes all 45 process corner in clock frequency 2MHz. As shown in Figure 6, the proposed design able to operate in

788 🗖 ISSN: 2502-4752

critical input sequence set in INP /INM signal. The output positive OUTP and output negative OUTN will reset high to VDD and toggle to 0V referring to INP /INM signal and every negative edge of clock CLK signal.

Figure 6. 45 Process corner simulation result of proposed comparator

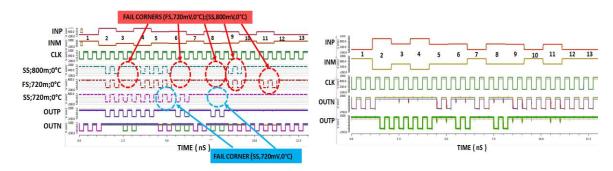

Figure 7 shows details of 45 process corners simulation result from *Schinkel's* comparator circuit. The details of failure capture in output positive (OUTP) signal. From the simulation result, it failed at 3 process corners which are at  $(SS;800mV;0^{\circ}C)$ ,  $(FS;720mV;0^{\circ}C)$ , and  $(SF;720mV;0^{\circ}C)$ .

For process corner (FS;720mV;0°C), failure occurred in test sequence number (3, 6, 8, 9,11). The failure occurred in minimum positive input INP is 400.4mV. At this process corner variation, transistor NMOS is set in high mobility, transistor PMOS is in low mobility, VDD supplies is set to 10% lower than nominal VDD 720mV and low temperature 0°C. The transistor PMOS take longer time to operate in weak condition and results in low gain at input latch.

For (SS;800mV;0°C) process corner, the failure occurred at test sequence number (3, 6, 8, 9). The failure occurred in minimum positive input INP is 400.4mV. At this process corner variation, transistor NMOS and PMOS both set in low mobility, VDD supplies is set to nominal VDD 800mV and low temperature 0°C. The weak condition of both transistor cause longer time required to operate.

For (SS;720mV;0°C) process corner, the failure occurred at test sequence number (5, 8). The failure occurred in minimum positive input INP is 400.4mV and minimum negative input INP is 399.6mV. At this process corner variation, transistor NMOS and PMOS both set in low mobility, VDD supplies is set to 10% lower than nominal VDD 720mV and low temperature 0°C. Transistors take longer time to operate in weak condition and results in low gain at input latch. From the test sequence 3, 5, 6, 8, 9, 11 we can detect the existence of offset voltage in *Schinkel's* comparator which affects the performance while operating in FS and SS process corner, VDD 800mV and 720mV, temperature 0°C condition.

Figure 8 shows the corner simulation result from Paik's comparator circuit in [4]. From the corner simulation result, Paik's comparator able to compare the sequence of input different set according to test setup in Table 1. However, at test sequence 5, 9, 11 which at input different  $800\mu V$ , we can see the delay occurred in OUTN. The delay will increase the power consumption of the comparator circuit. The details of power consumption during worst case condition are presented in Table 3.

Figure 7. 45 process corners simulation result of *Schinkel's* comparator circuit with failing at 3 process corners which are at (FS;720mV; 0°C), (SS;720mV; 0°C) and (SF;880mV;100°C).

Figure 8. 45 corners simulation result of *Paik's* comparator circuit

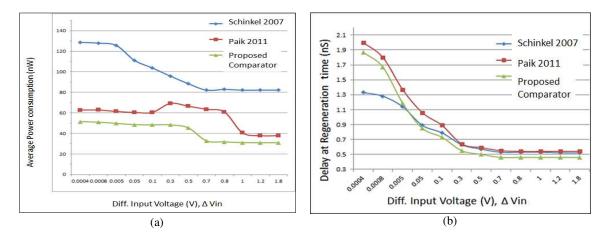

The comparison of average power consumption versus different input voltage ( $\Delta Vin$ ) at typical corner simulation of proposed comparator with Paik's and Schinkel's comparator is tabulated in Figure 9 (a). During typical corner simulation, proposed comparator is able to reduce the average power consumption from Schinkel's comparator up to 60% and 18% from Paik's comparator while operating in small  $\Delta Vin=800\mu V$ . At  $\Delta Vin=800mV$ , average power consumption of proposed comparator is reduced to 48% from Paik's comparator and 62% from Schinkel's comparator. Figure 9(b) depicts the simulated regeneration delay versus differential input voltage ( $\Delta Vin$ ). At  $\Delta Vin=800\mu V$ , delay for proposed comparator is 60% faster than Schinkel's comparator and 18% faster than Paik's comparator. The delay of all comparators in Figure 9(b) decreases when  $\Delta Vin$  is greater than 0.7V.

Figure 9. (a) Average power consumption (nW) versus different input voltage ( $\Delta$ Vin) at typical corner simulation, (b) Delay regeneration time (nS) versus different input voltage ( $\Delta$ Vin) at typical corner simulation

#### 3.2. Performance Comparison

Table 3 shows comparison of proposed comparator with *Paik's* and *Schinkel's* comparator. From the 45 process corner simulation, the maximum average power consumption of proposed comparator at (VDD=880mV; Temp.=100°C; Process Corner = FF) is 77nW, which is 87% lower than *Paik's* comparator and 73% lower than *Schinkel's* comparator. Besides the minimum average power consumption at VDD = 720V, temp.= 0°C and SS process corner is 33nW, 26% lower than *Paik's* comparator and 57% lower than *Schinkel's* comparator. The maximum delay of comparator at corner parameter VDD = 880mV, temp. = 100°C, FF process corner is 1.2nS when the input different is 800mV. It reduces to 250pS at VDD=720mV, temp. =0°C, SS process corner [14-26].

| Table 3. Performance Co | omparison over l | Pγ | ΤV | /ariation |

|-------------------------|------------------|----|----|-----------|

|-------------------------|------------------|----|----|-----------|

| Comparator Configuration                                                            | Schinkel's | Paik's     | Proposed   |

|-------------------------------------------------------------------------------------|------------|------------|------------|

|                                                                                     | Comparator | Comparator | Comparator |

| CMOS Technology                                                                     | 0.18 µm    | 0.18 µm    | 0.18 µm    |

| Supply Voltage                                                                      | 0.8 V      | 0.8 V      | 0.8 V      |

| Clock Frequency                                                                     | 2 MHz      | 2 MHz      | 2 MHz      |

| Max. Average Power consumption (VDD=0.88V; Temp. =100°C; Process FF)                | 288 nW     | 600 nW     | 77 nW      |

| Min. Average Power consumption (VDD=0.72V; Temp.= 0°C; Process SS)                  | 87 nW      | 50 nW      | 36 nW      |

| Max Regeneration Delay; $\Delta Vin=800mV$<br>(VDD = 0.72V; Temp.= 0°C; Process SS) | 1.3 nS     | 1.5 nS     | 1.2 nS     |

| Min Regeneration Delay ; ΔVin=800mV, (VDD=0.88V; Temp. =100°C; Process FF)          | 298 pS     | 293 pS     | 250 pS     |

## 4. CONCLUSION

In this paper, we have presented a verified new dynamic comparator with low voltage and low power performance. Proposed comparator passed all 45 process corner simulations with significant improvement of power consumption during worst case condition compared to *Paik's* and *Schinkel's* comparators. From the

simulation of maximum worst case condition, the average power consumption of proposed comparator is 77nW which is 87% lower than Paik's comparator and 73% lower than Schinkel's comparator. The regeneration delay is improved 7% compared to Schinkel's and 20% than Paik's comparator. At the minimum worst case condition during  $\Delta V$ in 800 $\mu V$ , average power consumption is 36nW and regeneration delay is 250 pS. In typical condition simulation, the average power consumption of proposed comparator is 69% lower from *Schinkel's* comparator and 18% from *Paik's* comparator. It can be concluded that the performance of proposed comparator improved in term of power consumption during the typical and worst case condition compared to Paik's and Schinkel's comparators. At the same time, the appropriate PVT verification method during the design stage is required in order to verify the robustness of low power low voltage dynamic comparator.

## **ACKNOWLEDGEMENTS**

The authors acknowledge University Putra Malaysia (UPM) for supporting this research work under supervision, fund by FRGS Grant (5540076) Kementerian Pelajaran Malaysia, Institute of Advanced Technology Malaysia (ITMA), Universiti Kuala Lumpur British Malaysia Institute and MIMOS in which this work was possible.

#### REFERENCES

- [1] H. S. Bindra, C. E. Lokin, D. Schinkel, A. Annema and B. Nauta, "A 1.2V Dynamic Bias Latch-Type Comparator in 65-nm CMOS With 0.4mV Input Noise." *IEEE Journal of Solid State Circuits*, 2018.

- [2] S. Babayan and R.Lotfi, "Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator". *IEEE Trans. On VLSI System*, Vol. 22, No. 2,pp.343-352, 2014.

- [3] M.Elzakker, E.Tuijil, P.Geraedts, D, Schinkel, E.A.M.Klumperink and B.Nauta, "A 10-bit Charge-Redistribution ADC Consuming 1.9uW at 1 MS/s," *IEEE Journal of Solid-State Circuits*, Vol. 45,pp. 1007-1015, 2010.

- [4] S. Brenna and A. Bonfanti, "A 6-fJ/conversion-step 200-kSps asynchronous SAR ADC with attenuation capacitor in 130nm CMOS," *Analog Integr. Circ. Sig. Process*, vol. 81.pp.181-194, 2014.

- [5] Gisela de La F.C, Guillermo E. F.V, Victor R. G. and A. Diaz-Mendez 1 "A new CMOS comparator robust to process and temperature variations for SAR ADC converters," *Analog Integr Circ Sig Process*, vol. 90, pp 301–308, 2017

- [6] V. Stopjakova, M. Rakus, M. Kovac, D. Arbet, L. Nagy, M. Sovcik and M. Potocny, "Ultra-low voltage analog IC design: challenges, methods and examples," *Rasioengineering*, VOL.27, NO.1, 2018.

- [7] R. Benschwartz, P. Sakthivel, "A Process Variation Tolerant OTA Design for Low Power ASIC Design," Circuits and Systems, vol. 7, pp 956-970, 2016.

- [8] M. Shoniker, O. Oleynikov, B. F. Cockburn, J. Han, M. Rana and W. Pedrycz, "Automatic Selection of Process Corner Simulations for Faster Design Verification," *IEEE Trans. On Computer-Aided Design of Integrated Circuits and Systems*, 2018.

- [9] M. Shoniker, B. F. Cockburn, J. Han and W. Pedrycz, "Minimizing the Number of Process Corner Simulations during Design Verification," *Design Automation & Test in Europe Con. & Exhibit*, 2015.

- [10] D. Schinkel, E. Kensink, E.Klumperink, E. Van Tuijl and B. Nauta, "A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time," in Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, Feb. 2007, pp. 314-415, 2007.

- [11] Julie R. Rusli, Noor Shelida Salleh, Masnita M. Isa, KY Tan and Suhaidi Shafie, "Analysis of Power Consumption SAR-ADC Dynamic Comparator," *Journal Technology UTM*, eISSN 2180-3722, 2016.

- [12] D. Paik, M. Miyahara and A.Matsuzawa,"An Analysis on a Pseudo-Differential Dynamic Comparator with Load Capacitance Calibration," in ASIC (ASICON), IEEE 9th International Conference, pp. 461 464, 2011.

- [13] L.F. Rahman, M. I. Reaz, C. C. Yin, M. Marufuzzaman and M. A. Rahman, "A High-Speed and Low-Offset Dynamic Latch Comparator," *Hindawi Publishing Corporation, The Scientific World Journal*, Volume 2014, 2014.

- [14] Julie Roslita Rusli, R. M. Sidek, Hasmayadi Abdul Majid, Wan Zuha Wan Hassan, Mohd Amrallah Mustafa, Suhaidi Shafie, "Design and Verification of Low Voltage Low Power Dynamic Comparator over PVT Variation," Proc. Of the 2018 IEEE 5<sup>th</sup> International Conference on Smart Instrumentation, (ICSIMA2018), 2018.

- [15] Hai Huang, Hongda Xu, Brian Elies and Yun Chiu, "A Non-Interleaved 12-b 330-MS/s Pipelined-SAR ADC With PVT-Stabilized Dynamic Amplifier Achieving Sub-1-dB SNDR Variation," *IEEE Journal of Solid-State Circuits*, Vol. 52, No.12, 2017.

- [16] Abdullah El-Bayoumi, Hassan Mostafa and Ahmed M.Soliman, "A new 16-bit low-power PVT-calibrated time-based differential Analog-to-Digital Converter (ADC) circuit in CMOS 65nm technology," 2015 IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2015.

- [17] B. Vidya, G.Gowrilakshmi, P. Sasikumar, "Design and Implementation of 8-Bit SAR ADC with Built-in-Self-Calibration and Digital-Trim Technique," *International Journal of Advanced Research in Electrical Electronics and Instrumentation Engineering*, Vol. 4, Issue 11, 2015.

- [18] Hao Xu, Asad A.Abidi, "Analysis and Design of Regenerative Comparators for Low Offset and Noise," *IEEE Transactions on Circuy 44its and System-I: Regular Papers*, Vol.66, No 8, 2019.

- [19] Fernando Paixao Cortes, Eric Fabris, Sergio Bampi, "Analysis and design of amplifiers and comparators in CMOS 0.35um technology," *Microelectronics Realiblity* (2004)657-664, 2004.

- [20] Saurav Chakraborty, Abhijit Mallik, Chandan Kumar Sarkar, "Subtreshold Performance of Dual-Material Gate CMOS Devices and Circuits for Ultralow Power Analog/Mixed-Signal Applications," *IEEE Transactions on Electron Devices*, Vol.55, No.3, 2008.

- [21] Yao Wang, Haibo Wang, Guangjun Wen, "Design Techniques for Ultra Low Voltage Comparator Circuits," *Journal of Circuits, Systems and Computers*, Vol.24, No.1, 2015.

- [22] Vijay Savani, N.M. Devashrayee, "Analysis and design of low-voltage low-power high-speed double tail current dynamic latch comparator," *Analog Integr. Circ. Signal Processing*, vol. 93, pp. 287-298, 2017.

- [23] A. Rabiei, A. Najafizadeh, A. Khalafi, S.M. Ahmad, "A new ultra low power high speed dynamic comparator," 2015 23<sup>rd</sup> Iranian Conference on Electrical Engineering, 2015.

- [24] A.Rezapour, H. Shamsi, H. Abbasizadeh, K.Y. Lee, "Low Power High Speed Dynamic Comparator," 2018 IEEE International Symposium on Circuits and Systems, 2018.

- [25] Aakash. S, Anisha. A, Jaswanth Das G., Abhiram T, Anita J.P., "Design of a low power, high speed double tail comparator," 2017 International Conference on circuits Power and Computing Technologies, 2017.

- [26] Rahman, L. F., Reaz, M. M. I., Restu, W. I. I., Marufuzzaman, M., & Sidek, L. M., "Design and analysis of high gain low power CMOS comparator," *Indonesian Journal of Electrical Engineering and Informatics*, 6(4), 471-476, 2018.

#### **BIOGRAPHIES OF AUTHORS**

Julie Roslita Rusli received the Bachelor of Engineering (Electrical and Electronics) from University of Lincoln in 2001. From 2002 to 2004, she was with Intel Malaysia (M) Sdn. Bhd as a Validation Engineer in Board Design Center Malaysia. He received the Master of Science (Electronics Engineering) from Universiti Putra Malaysia in 2011. She is a Lecturer in Universiti Kuala Lumpur British Malaysia Institute since 2004 until present. Currently her pursuing PhD in area Mix Signal IC Design. His current research is on Ultra Low Power SAR ADC.

Suhaidi Shafie received the Bachelor of Engineering (Electrical and Electronics) from University of the Ryukyus, Japan in 2000. From 2000 to 2002, he was with ALPS Electric (M) Sdn. Bhd. He received the Master of Engineering (Electrical and Electronics) from Tokyo University of Agriculture and Technology, and the Doctor of Engineering (Nanovision) from Shizuoka University in 2005 and 2008, respectively. He is an Associate Professor in Universiti Putra Malaysia and the Head of Functional Devices Laboratory. Dr. Suhaidi is working in Mix Signal IC Design and Solar Energy research. His current projects include Ultra Low Power SAR ADC and High Efficiency Dye Sensitized Solar Cell. He is was the chapter chair of IEEE Circuits and Systems Malaysia Chapter and actively involves in IEEE CAS and Malaysia Chapters activities.

Roslina Mohd Sidek received the B.Sc. degree in Electrical Engineering from The George Washington University, Washington D.C in 1990, the M.Sc. degree in Microelectronics Systems Design in 1993 and Ph.D. degree in Microelectronics in 1999, both from University of Southampton, U.K. She joined Universiti Putra Malaysia, Malaysia as a lecturer in 1999. Her research interests include Semiconductor Devices and Modelling, Integrated Circuit (IC) Design, Fabrication and Testing as well as Nanoelectronics.

Hasmayadi Abdul Majid received the Bachelor of Engineering (Computer and Information System) from International Islamic University Malaysia in 2001. He received the Master of Electrical Engineering from Universiti Teknologi Malaysia in 2011. He is employed by MIMOS Berhad, a National Strategic Agency for Electronic and ICT since 2001. He is a Staff Engineer in Analog and Mixed Signal Group. Mr. Hasmayadi is working on SAR ADC specializing on Comparator and ADC reference generator. His current projects include 11-bit Single-input SAR ADC and 12-bit Differential-input SAR ADC.

Wan Zuha Wan Hasan received the degree in Electrical and Electronic Engineering from Universiti Putra Malaysia in 1997. He received the Ph.D. degree in Microelectronic Engineering from the Universiti Kebangsaan Malaysia in 2010. Currently, he is a senior lecturer at Department of Electrical and Electronic Engineering, Universiti Putra Malaysia. His research interests include Memory Testing, MEMS Sensor and Robotic and Automation.

Mohd Amrallah Mustafa received the Bachelor of Engineering (Electrical and Electronics) from Universiti Putra Malaysia, Malaysia in 2000. He received the Master of Engineering (Control and Automation) also from Universiti Putra Malaysia, Malaysia and PhD (Eng.) in Nano vision from Shizuoka University, Japan in 2007 and 2013, respectively. He is a Senior Lecturer in Universiti Putra Malaysia. Dr. Mohd Amrallah is working in Solar Cell, CMOS Image Sensors, Analog IC design and robotics. His current projects include Charging Pad for Unmanned Aerial Vehicle and High Efficiency Dye Sensitized Solar Cell. He was the Excomm of IEEE Circuits and Systems Malaysia Chapter and vice secretary of IEEE EDS Malaysia Chapter. He actively involves in IEEE CAS and EDS Malaysia Chapters activities.