### **UC Irvine**

### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Optimizing Many-Threads-to-Many-Cores Mapping in Parallel Electronic System Level Simulation

#### **Permalink**

https://escholarship.org/uc/item/8sf0g2dh

#### **Author**

Liu, Guantao

#### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} \text{UNIVERSITY OF CALIFORNIA,} \\ \text{IRVINE} \end{array}$

Optimizing Many-Threads-to-Many-Cores Mapping in Parallel Electronic System Level Simulation

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Engineering

by

Guantao Liu

Dissertation Committee: Professor Rainer Dömer, Chair Professor Kwei-Jay Lin Professor Mohammad A. Al Faruque

## **DEDICATION**

To my dearest parents for their unconditional love and support

## TABLE OF CONTENTS

|                           |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                  |

|---------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| LI                        | ST (                            | OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                       | vi                                                    |

| LI                        | ST (                            | OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                        | viii                                                  |

| LI                        | ST (                            | OF ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                    | ix                                                    |

| $\mathbf{A}^{\mathbf{c}}$ | CKN                             | IOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                     | x                                                     |

| $\mathbf{C}^{\gamma}$     | URR                             | ICULUM VITAE                                                                                                                                                                                                                                                                                                                                                                                                     | xi                                                    |

| $\mathbf{A}$              | BST                             | RACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                                                                                         | xiv                                                   |

| 1                         | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | System Level Design and Simulation  1.1.1 Discrete Event Simulation  1.1.2 Synchronous Parallel Discrete Event Simulation  1.1.3 Out-of-Order Parallel Discrete Event Simulation  Recoding Infrastructure for SystemC (RISC)  1.2.1 Segment Graph  1.2.2 Conflict Analysis  1.2.3 Source Code Instrumentation  1.2.4 Compiler Backend  1.2.5 Simulator  Thread-to-Core Mapping  Related Work  Goals and Overview | 3<br>5<br>7<br>10<br>12<br>13<br>15<br>16<br>16<br>17 |

| 2                         | 2.1<br>2.2<br>2.3<br>2.4        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                     | . 29<br>. 30<br>. 31<br>. 33                          |

|   |                                                        | 2.4.4 Segment-Aware Dispatch Algorithm                              | 35  |  |  |  |

|---|--------------------------------------------------------|---------------------------------------------------------------------|-----|--|--|--|

|   | 2.5                                                    | Experimental Evaluation                                             | 41  |  |  |  |

|   |                                                        | 2.5.1 Task Graph Benchmarks                                         | 42  |  |  |  |

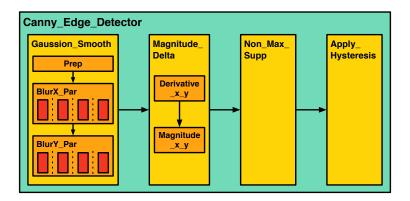

|   |                                                        | 2.5.2 Canny Edge Detector Example                                   | 48  |  |  |  |

|   |                                                        | 2.5.3 JPEG Encoder Example                                          | 49  |  |  |  |

|   | 2.6                                                    | Conclusion                                                          | 51  |  |  |  |

| 3 | Cor                                                    | re Distance                                                         | 52  |  |  |  |

|   | 3.1                                                    | Introduction                                                        | 52  |  |  |  |

|   |                                                        | 3.1.1 Motivation                                                    | 54  |  |  |  |

|   | 3.2                                                    | Core Distance                                                       | 54  |  |  |  |

|   |                                                        | 3.2.1 Definition of Core Distance                                   | 55  |  |  |  |

|   |                                                        | 3.2.2 Core Distances on Hierarchical Multi-Core Platforms           | 56  |  |  |  |

|   |                                                        | 3.2.3 Core Distances on Many-Core Platforms                         | 57  |  |  |  |

|   |                                                        | 3.2.4 Core Distances on Busy Many-Core Platforms                    | 59  |  |  |  |

|   | 3.3                                                    | Minimizing Inter-Core Communication                                 | 60  |  |  |  |

|   |                                                        | 3.3.1 Mapping Communicating Threads Close to the TD                 | 61  |  |  |  |

|   |                                                        | 3.3.2 Pizza Slice Algorithm                                         | 63  |  |  |  |

|   | 3.4                                                    | Experimental Results                                                | 65  |  |  |  |

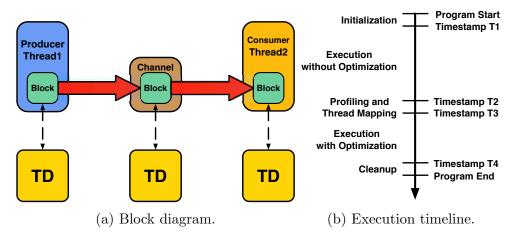

|   |                                                        | 3.4.1 Producer-Consumer Model                                       | 65  |  |  |  |

|   |                                                        | 3.4.2 Mandelbrot Set Renderer Example                               | 68  |  |  |  |

|   | 3.5                                                    | Related Work                                                        | 71  |  |  |  |

|   | 3.6                                                    | Conclusion                                                          | 72  |  |  |  |

| 4 | Communication-Aware Thread Mapping 73                  |                                                                     |     |  |  |  |

|   | 4.1                                                    | Introduction                                                        | 73  |  |  |  |

|   | 4.2                                                    | Related Work                                                        | 75  |  |  |  |

|   | 4.3                                                    | Communication Latency on Hierarchical Multiprocessor Platforms      | 76  |  |  |  |

|   | 4.4                                                    | Communication Patterns of System Level Designs                      | 79  |  |  |  |

|   | 4.5                                                    | Communication-Aware Thread Mapping Framework                        | 81  |  |  |  |

|   | 4.6                                                    | Experimental Evaluation                                             | 85  |  |  |  |

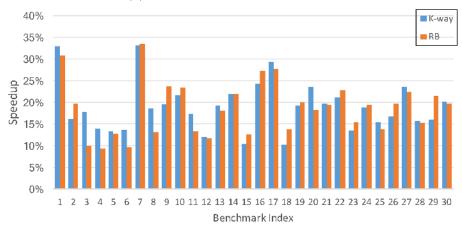

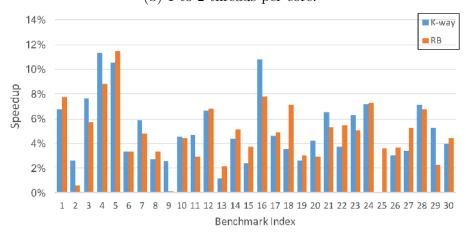

|   |                                                        | 4.6.1 Task Graph Benchmarks                                         | 86  |  |  |  |

|   | 4.7                                                    | Conclusion                                                          | 94  |  |  |  |

| 5 | Computation- and Communication-Aware Thread Mapping 97 |                                                                     |     |  |  |  |

|   | 5.1                                                    | Integration of Our Methods                                          | 98  |  |  |  |

|   |                                                        | 5.1.1 Computation Weight in Real-World Examples                     | 98  |  |  |  |

|   |                                                        | 5.1.2 Computation- and Communication-Aware Scheduling Algorithm     | 100 |  |  |  |

|   | 5.2                                                    | Experimental Evaluation                                             | 103 |  |  |  |

| 6 | Con                                                    | nclusion                                                            | 106 |  |  |  |

|   | 6.1                                                    | Contributions                                                       | 106 |  |  |  |

|   |                                                        |                                                                     | 107 |  |  |  |

|   |                                                        | 6.1.2 A Segment-Aware Multi-Core Scheduler for SystemC PDES         | 107 |  |  |  |

|   |                                                        | 6.1.3 Core Distance Profiling on Multi-Core and Many-Core Platforms | 108 |  |  |  |

|                  | 6.1.4        | A Communication-Aware Thread Mapping Framework            | 108 |  |

|------------------|--------------|-----------------------------------------------------------|-----|--|

| 6.2              | Future       | e Work                                                    | 109 |  |

|                  | 6.2.1        | Thread Mapping for Sporadic Models                        | 109 |  |

|                  | 6.2.2        | Extending the Thread Mapping Framework for More Platforms | 109 |  |

|                  | 6.2.3        | Resource Contention Analysis on More Factors              | 110 |  |

|                  |              |                                                           |     |  |

| ${f Bibliogram}$ | Bibliography |                                                           |     |  |

## LIST OF FIGURES

|      |                                                                              | Page |

|------|------------------------------------------------------------------------------|------|

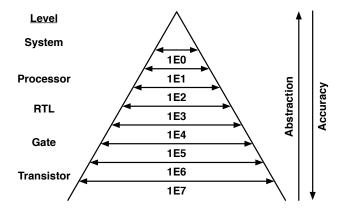

| 1.1  | Level of abstraction in system design [31]                                   | . 2  |

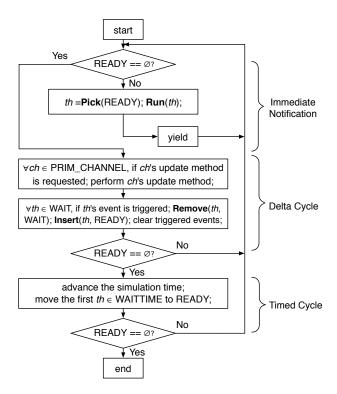

| 1.2  | DES scheduler for SystemC                                                    | . 3  |

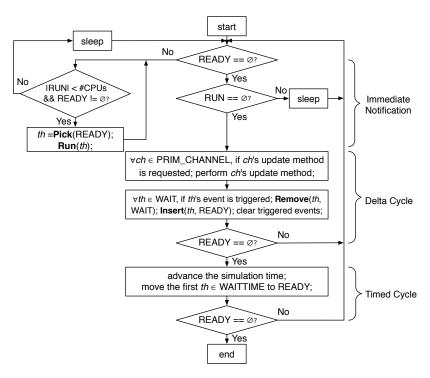

| 1.3  | PDES scheduler for SystemC                                                   |      |

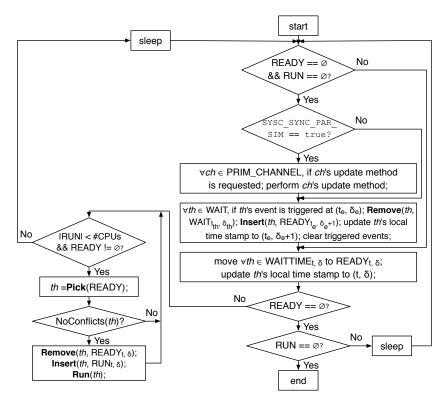

| 1.4  | OoO PDES scheduler for SystemC                                               |      |

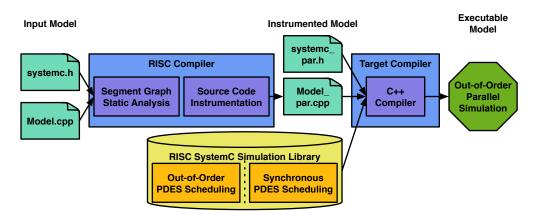

| 1.5  | RISC Compiler and Simulator for OoO PDES of SystemC                          | . 11 |

| 1.6  | SystemC thread and Segment Graph (SG) [57]                                   | . 13 |

| 1.7  | Problem decription of thread-to-core mapping in SystemC PDES                 |      |

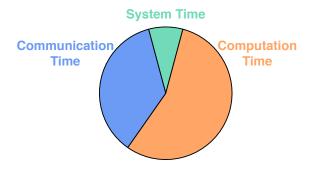

| 1.8  | Decomposition of execution time of ESL simulation                            | . 23 |

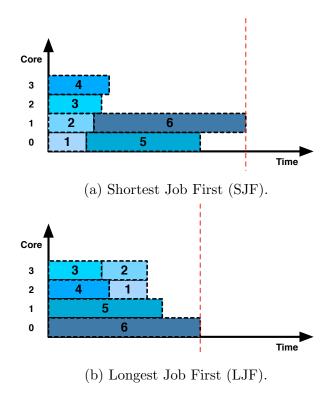

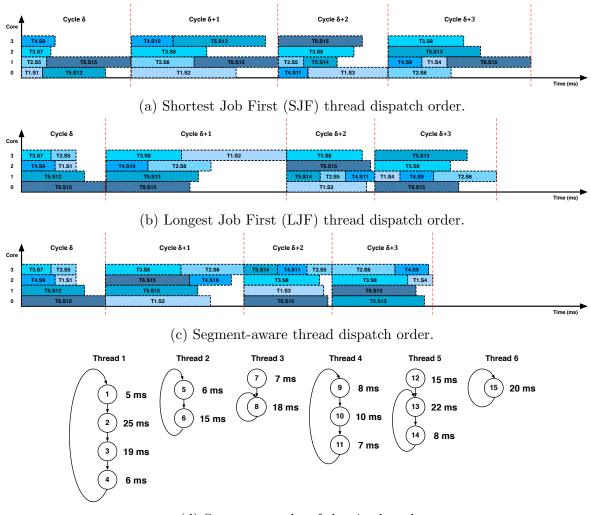

| 2.1  | Two multi-core thread dispatch policies                                      | . 32 |

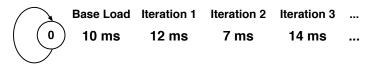

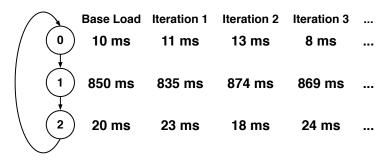

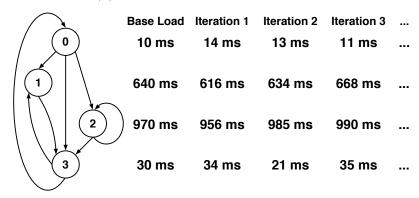

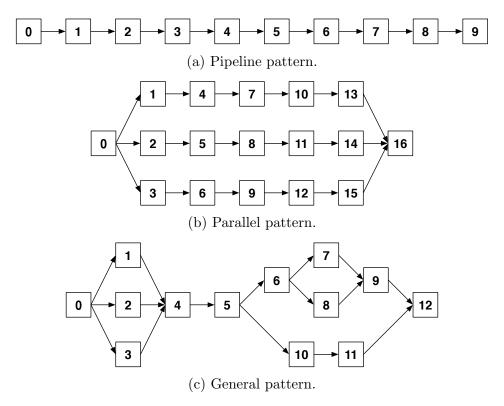

| 2.2  | Different segment structures in a thread                                     | . 36 |

| 2.3  | Thread execution timelines determined by different thread dispatch policies. | 37   |

| 2.4  | SystemC source-code instrumentation                                          | . 38 |

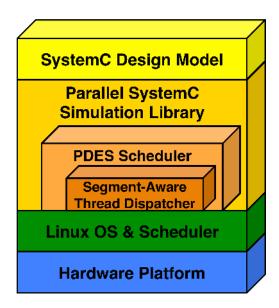

| 2.5  | Software hierarchy of our parallel SystemC simulator implementation          | . 41 |

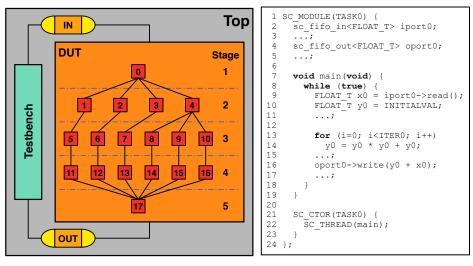

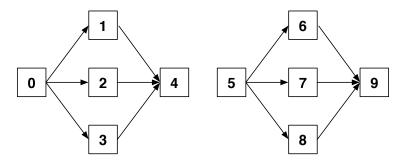

| 2.6  | Synthetic SystemC benchmark models                                           | . 42 |

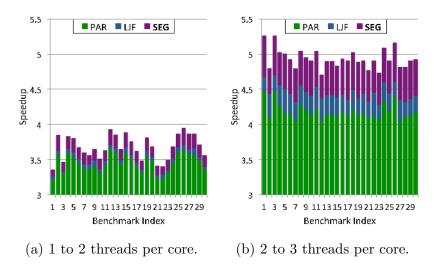

| 2.7  | Performance comparison for general threads (Figure 2.2c) on a 8-core host.   | . 47 |

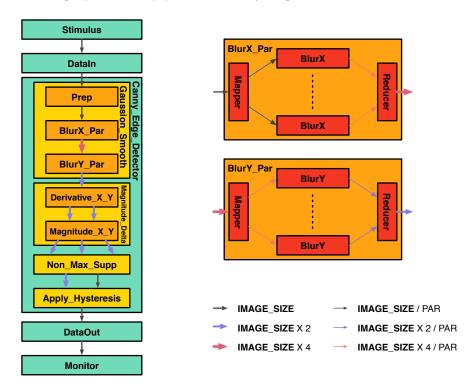

| 2.8  | Pipelined Canny edge detector example                                        | 49   |

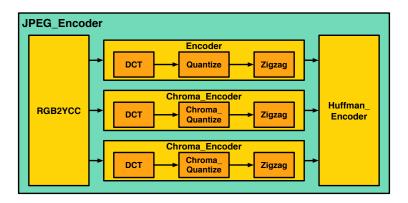

| 2.9  | Pipelined JPEG encoder example                                               | . 50 |

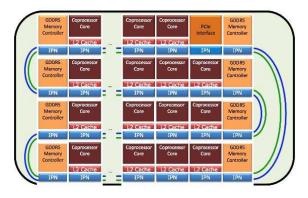

| 3.1  | Intel Xeon Phi coprocessor architecture [39]                                 |      |

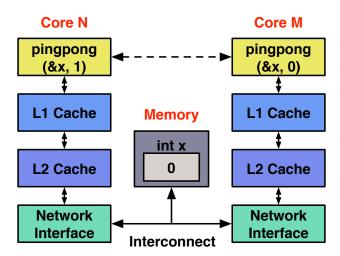

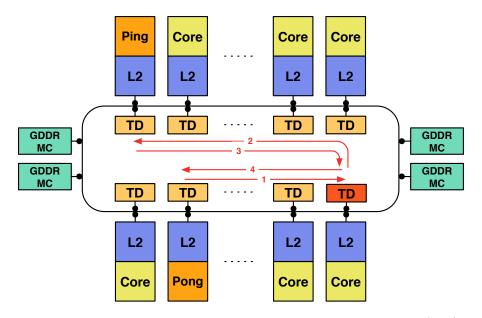

| 3.2  | Ping-pong communication for measuring core distance                          |      |

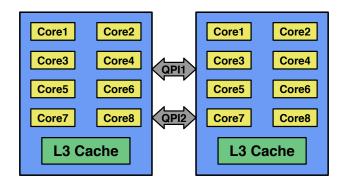

| 3.3  | Intel Xeon E5-2680 dual-CPU architecture                                     | . 57 |

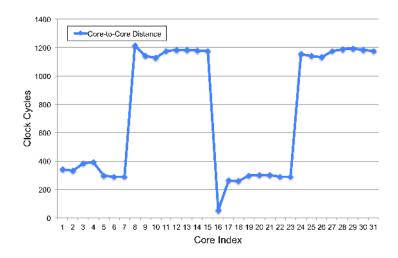

| 3.4  | Core Distances from Core 0 to other cores on Intel Xeon E5-2680              | . 57 |

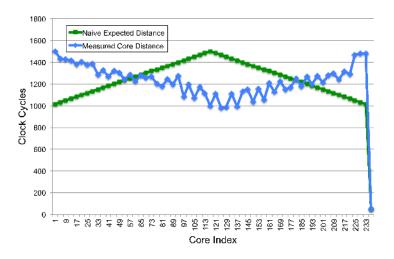

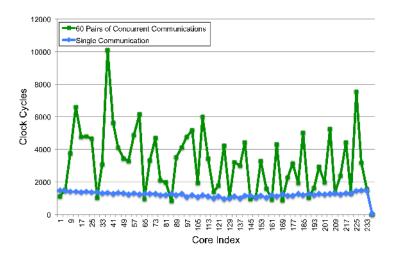

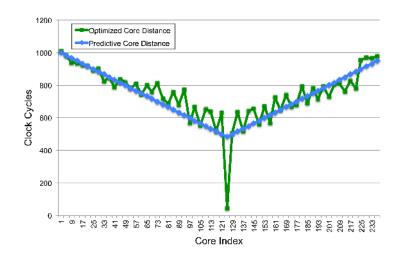

| 3.5  | Core distances from Core 0 to other cores on Xeon Phi 5110P                  |      |

| 3.6  | Cache coherence via distributed tag directories (TD)                         |      |

| 3.7  | Core distances from Core 0 to other cores at $50\%$ core utilization         |      |

| 3.8  | Optimized inter-core communication latency                                   |      |

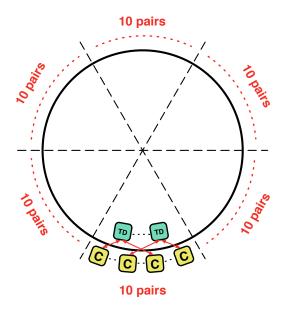

| 3.9  | "Pizza Slice Algorithm" for cores and TDs on a ring network                  |      |

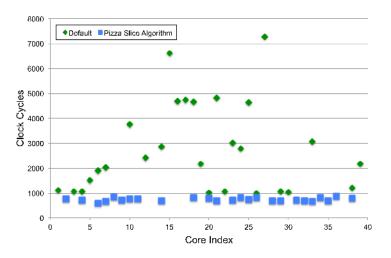

|      | Communication latency comparison as for the Pizza Slice Algorithm            |      |

|      | Producer-consumer example                                                    |      |

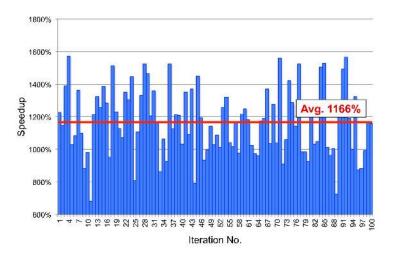

|      | Speedup of mapping producer-consumer threads to the same core                |      |

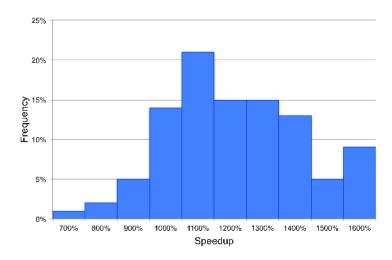

|      | Speedup histogram of mapping producer-consumer threads to the same core.     |      |

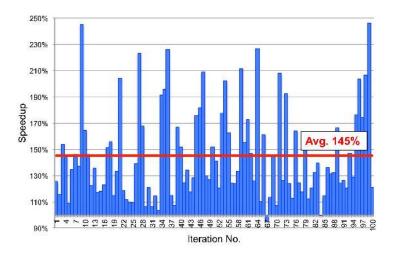

|      | Speedup of mapping producer-consumer threads close to TD                     |      |

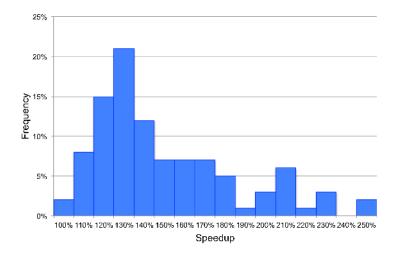

|      | Speedup histogram of mapping producer-consumer threads close to TD           |      |

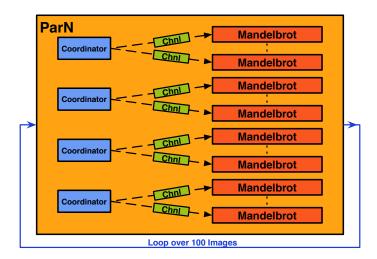

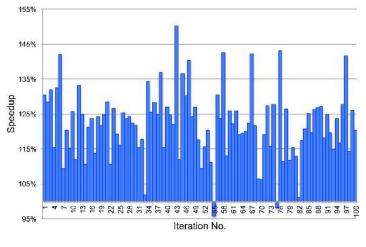

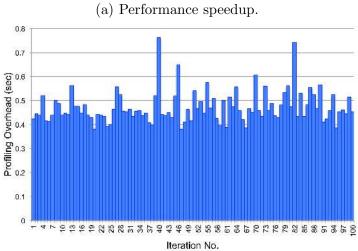

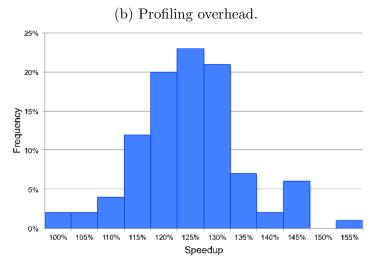

| 3.16 | Block diagram of the Mandelbrot renderer example                             | . 69 |

| 3.17 | Apply Pizza Slice Algorithm to the Mandelbrot renderer             | 70  |

|------|--------------------------------------------------------------------|-----|

| 4.1  | Benchmark for communication latency exploration                    | 76  |

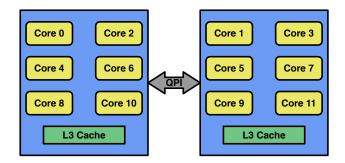

| 4.2  | A 12-core workstation architecture                                 | 76  |

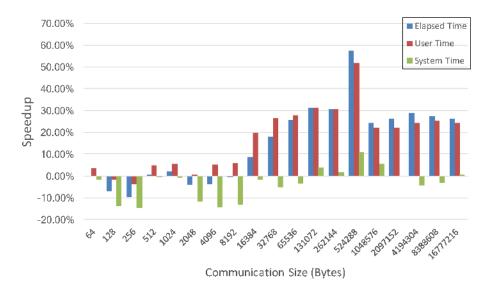

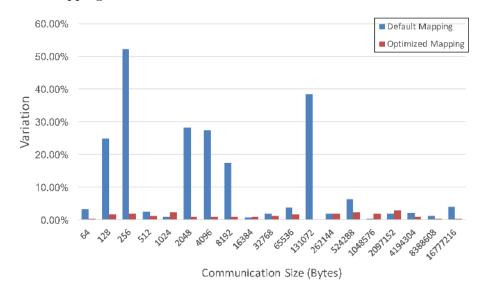

| 4.3  | Performance of the Linux default mapping and the optimized mapping | 77  |

| 4.4  | Different communication patterns in ESL design models              | 79  |

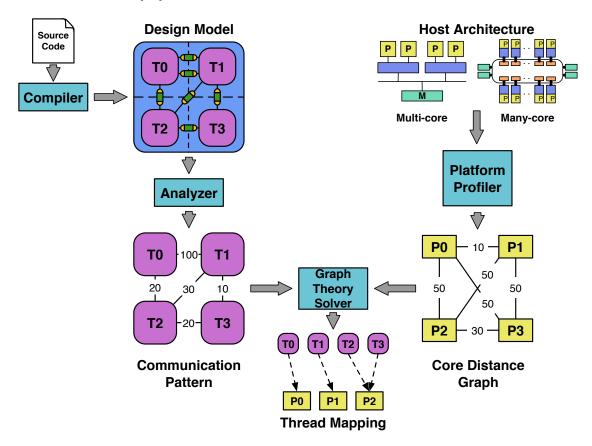

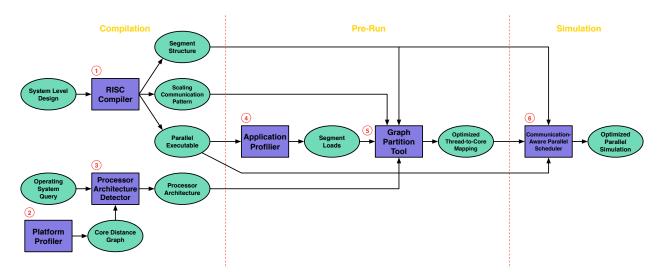

| 4.5  | Communication-aware thread mapping framework                       | 82  |

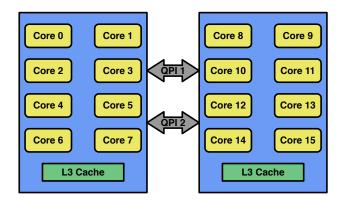

| 4.6  | A 16-core workstation architecture                                 | 86  |

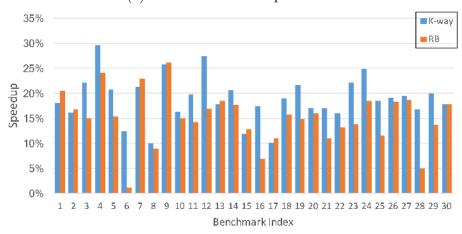

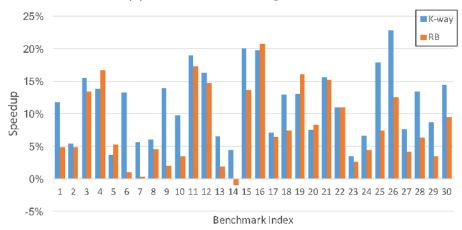

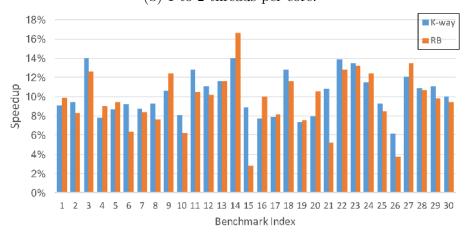

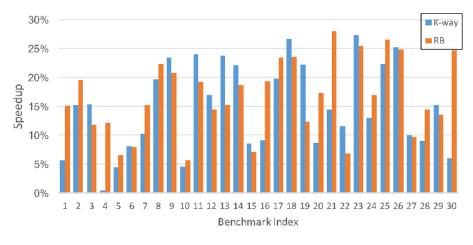

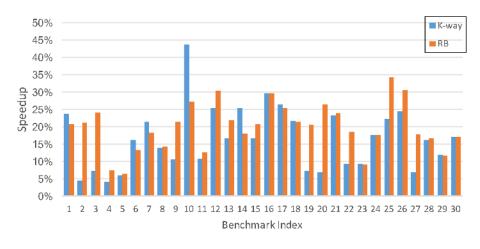

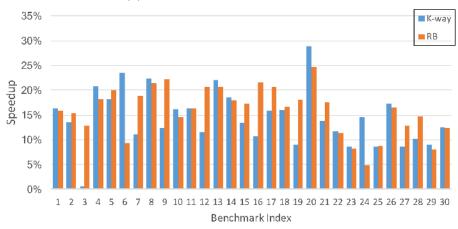

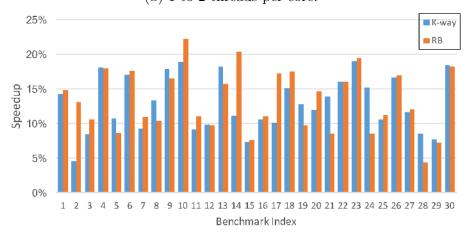

| 4.7  | Performance comparison for pipeline patterns on a 12-core host     | 89  |

| 4.8  | Performance comparison for pipeline patterns on a 16-core host     | 90  |

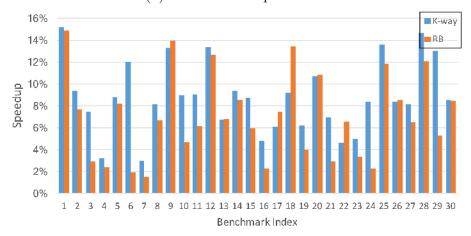

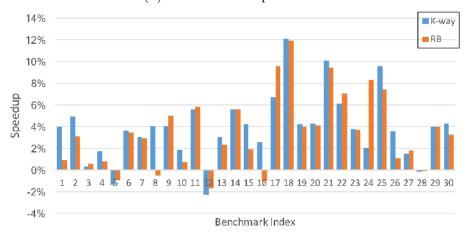

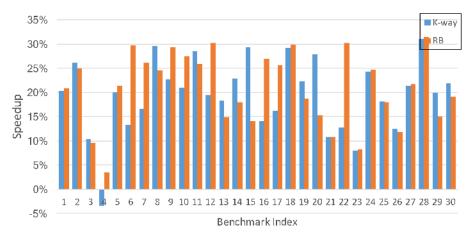

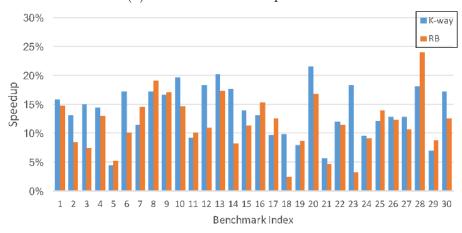

| 4.9  | Performance comparison for parallel patterns on a 12-core host     | 92  |

| 4.10 | Performance comparison for parallel patterns on a 16-core host     | 93  |

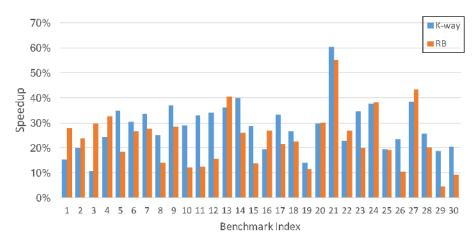

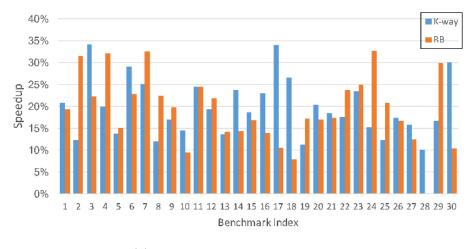

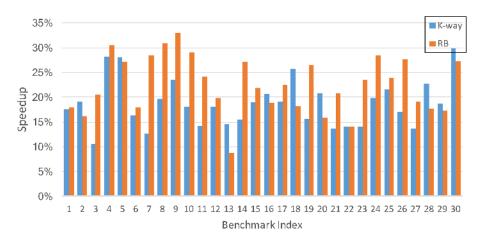

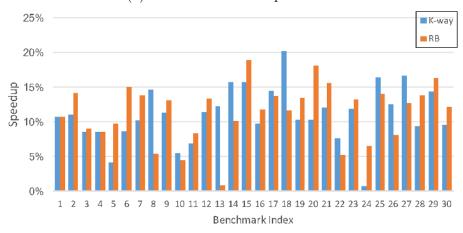

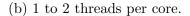

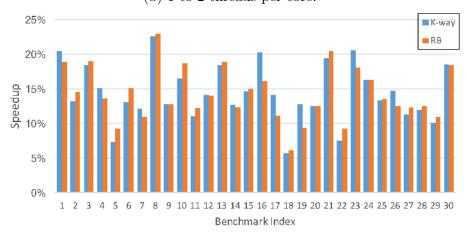

| 4.11 | Performance comparison for general patterns on a 12-core host      | 95  |

| 4.12 | Performance comparison for general patterns on a 16-core host      | 96  |

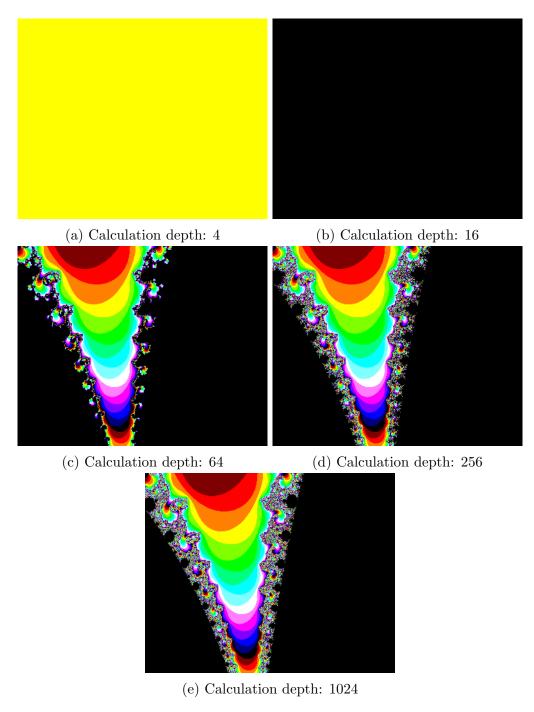

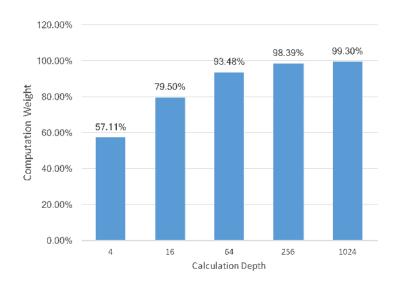

| 5.1  | Mandelbrot set images with different calculation depths            | 99  |

| 5.2  | Computation weight of a Mandelbrot set renderer example            | .00 |

| 5.3  | Communication graph of the pipelined Canny edge detector           | 04  |

## LIST OF TABLES

|     |                                                                         | Page  |

|-----|-------------------------------------------------------------------------|-------|

| 2.1 | Workstations used for experiments                                       | 41    |

| 2.2 | Performance comparison for single-segment threads                       | 43    |

| 2.3 | Performance comparison for multi-segment threads                        | 45    |

| 2.4 | Performance comparison for general threads                              | . 47  |

| 2.5 | Performance comparison for Canny edge detector on a 8-core host         | 49    |

| 2.6 | Performance comparison for JPEG encoder on a 8-core host                | 49    |

| 4.1 | Numbers of different communication patterns in our ESL design models    | . 80  |

| 4.2 | Comparison of the Linux scheduling and our thread mapping framework     | . 84  |

| 4.3 | Workstations used for evaluation                                        | . 85  |

| 4.4 | Performance comparison for pipeline communication patterns              | . 87  |

| 4.5 | Performance comparison for parallel communication patterns              | . 91  |

| 4.6 | Performance comparison for general communication patterns               | . 94  |

| 5.1 | Performance comparison of our proposed methods for Canny edge detector. | . 104 |

## LIST OF ALGORITHMS

|   |                                                           | Page |

|---|-----------------------------------------------------------|------|

| 1 | Conflict Detection in OoO PDES Scheduler                  | 10   |

| 2 | Segment-Aware Scheduling Algorithm                        | 40   |

| 3 | Ping-Pong Communication Function                          | 56   |

| 4 | Find the Responsible Tag Directory                        | 61   |

| 5 | Thread Initialization without Optimization                | 62   |

| 6 | Thread Initialization with Optimization                   | 62   |

| 7 | Processor Architecture Detection Algorithm                | 81   |

| 8 | Computation- and Communication-Aware Scheduling Algorithm | 101  |

#### ACKNOWLEDGMENTS

It has been a long and wonderful journey to pursue the doctorate degree during the past five years, and life would have been much more difficult without the support from my professors, family, colleagues and friends. Thus, I would like to take this opportunity to thank these great people for encouraging and inspiring me in this journey.

First and foremost, I would like to gratefully and sincerely thank my advisor, Professor Rainer Dömer, for his guidance, motivation, understanding and patience during my graduate study at UC Irvine. It has been a great learning experience to be a member of his research group and a teaching assistant of his class. His considerable insights, kind personality and sense of humor created an enjoyable and pleasant working environment in our group. Thanks to this, I have learned much more from our meetings and conversations in the past few years, not only on researching and teaching, but also on life and philosophy. This is a treasure that will benefit me for a whole lifetime.

Next, I would like to thank Professor Kwei-Jay Lin and Professor Mohammad A. Al Faruque, for taking time out of their busy schedules to serve as my committee members and provide me constructive suggestions and feedback on my dissertation.

Many thanks to my colleagues in the LECS group, including Weiwei Chen, Xu Han, Yasaman Samei, Che-Wei Chang and especially Tim Schmidt, for the fruitful talks, discussions and teamwork. I appreciate all their help during my graduate program.

Also, I am thankful to all my friends and colleagues in the Chinese Students and Scholars Association at UC Irvine. Those wonderful events and activities we attended and hosted together have greatly enriched my nerdy social life, and they always gave me joy and happiness to continue my research in the United States.

This work has been supported in part by funding from Intel Corporation. I thank Intel for the valuable support.

Last but not least, I would like to express my deepest gratitude to my parents, Xinyong Liu and Biyuan She, for their unconditional love and endless faith in me. Their support is the very source of power and morale for me to pursue my dream.

### CURRICULUM VITAE

#### Guantao Liu

#### **EDUCATION**

Doctor of Philosophy in Computer Engineering

University of California, Irvine

Master of Science in Electrical and Computer Engineering

University of California, Irvine

Bachelor of Engineering in Information Engineering

Southeast University

2013

Irvine, California

Ranjing, China

#### RESEARCH EXPERIENCE

Graduate Student Researcher

University of California, Irvine

2011–2017

Irvine, California

#### TEACHING EXPERIENCE

Teaching Assistant

University of California, Irvine

2015–2016

Irvine, California

#### INDUSTRIAL EXPERIENCE

Software Engineer Intern

Arista Networks

Systems Software Intern

Samsung Research America - Sillicon Valley

San Jose, California

IC Design Verification Intern

Broadcom

Irvine, California

#### REFEREED JOURNAL PUBLICATIONS

- G. Liu, T. Schmidt, and R. Dömer. A Communication-Aware Thread Mapping Framework for SystemC PDES. In preparation, February 2017.

- W. Chen, X. Han, C. Chang, G. Liu, and R. Dömer. **Out-of-Order Parallel Discrete Event Simulation for Transaction Level Models**. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 33, no. 12, pp. 1859-1872, December 2014.

#### REFEREED BOOK CHAPTERS

R. Dömer, G. Liu, and T. Schmidt. **Parallel Simulation**. Chapter 18 in *Handbook of Hardware/Software Codesign* by S. Ha and J. Teich, Springer, accepted for publication, August 2016.

#### REFEREED CONFERENCE PUBLICATIONS

- T. Schmidt, G. Liu, and R. Dömer. **Exploiting Thread and Data Level Parallelism** for Ultimate Parallel SystemC Simulation. In *Proceedings of Design Automation Conference 2017*, accepted for publication, February 2017.

- T. Schmidt, G. Liu, and R. Dömer. **Hybrid Analysis of SystemC Models for Fast and Accurate Parallel Simulation**. In *Proceedings of the Asia and South Pacific Design Automation Conference 2017*, Tokyo, Japan, January 2017.

- G. Liu, T. Schmidt, and R. Dömer. A Segment-Aware Multi-Core Scheduler for SystemC PDES. In *Proceedings of the International High Level Design Validation and Test Workshop 2016*, Santa Cruz, California, October 2016.

- T. Schmidt, G. Liu, and R. Dömer. **Automatic Generation of Thread Communication Graphs from SystemC Source Code**. In *Proceedings of the 19th International Workshop on Software and Compilers for Embedded Systems*, St. Goar, Germany, May 2016.

- G. Liu, T. Schmidt, and R. Dömer. Optimizing Thread-to-Core Mapping on Manycore Platforms with Distributed Tag Directories. In *Proceedings of the Asia and South Pacific Design Automation Conference 2015*, Tokyo, Japan, January 2015.

#### MASTER THESIS

G. Liu. A Hybrid Thread Library for Efficient Electronic System Level Simulation. Master's thesis, University of California, Irvine, Irvine, California, June 2013.

#### TECHNICAL REPORTS

- G. Liu, T. Schmidt, and R. Dömer. **RISC Compiler and Simulator, Beta Release Vo.3.0: Out-of-Order Parallel Simulatable SystemC Subset**. Center for Embedded and Cyber-Physical Systems, Technical Report 16-06, September 2016.

- G. Liu, T. Schmidt, and R. Dömer. **RISC Compiler and Simulator, Alpha Release V0.2.1: Out-of-Order Parallel Simulatable SystemC Subset**. Center for Embedded and Cyber-Physical Systems, Technical Report 15-02, October 2015.

- G. Liu, and R. Dömer. A Hybrid Thread Library for Efficient Electronic System Level Simulation. Center for Embedded Computer Systems, Technical Report 13-11, October 2013.

- G. Liu, and R. Dömer. A User-Level Thread Library Built on Linux Context Functions for Efficient ESL Simulation. Center for Embedded Computer Systems, Technical Report 13-07, June 2013.

- G. Liu, and R. Dömer. **Performance Evaluation and Optimization of A Custom Native Linux Threads Library**. Center for Embedded Computer Systems, Technical Report 12-11, October 2012.

#### OPEN SOURCE SOFTWARE RELEASES

- R. Dömer, G. Liu, and T. Schmidt. RISC Compiler and Simulator, Beta Release V0.3.0. http://cecs.uci.edu/~doemer/risc.html#RISC030, September 2016.

- R. Dömer, G. Liu, and T. Schmidt. **RISC Compiler and Simulator, Alpha Release V0.2.1**. http://cecs.uci.edu/~doemer/risc.html#RISC021, October 2015.

- R. Dömer, G. Liu, and T. Schmidt. RISC Compiler and Simulator, Alpha Release V0.2.0. http://cecs.uci.edu/~doemer/risc.html#RISC020, September 2015.

- R. Dömer, G. Liu, and T. Schmidt. RISC API, Alpha Release V0.1.0. http://cecs.uci.edu/~doemer/risc.html#RISC010, June 2014.

### ABSTRACT OF THE DISSERTATION

Optimizing Many-Threads-to-Many-Cores Mapping in Parallel Electronic System Level Simulation

By

#### Guantao Liu

Doctor of Philosophy in Computer Engineering

University of California, Irvine, 2017

Professor Rainer Dömer, Chair

In hardware/software codesign, Discrete Event Simulation (DES) has been in use for decades to verify and validate the functionality of Electronic System Level (ESL) models. Since the parallel computing platforms are readily available today, many Parallel Discrete Event Simulation (PDES) approaches are proposed to improve the simulation performance. However, as the thread parallelism increases in ESL designs and core count multiplies on multi-core and many-core platforms, thread-to-core mapping becomes critical in PDES.

In this dissertation, we propose a computation- and communication-aware approach to optimize thread mapping for parallel ESL simulation, with the aims of load balancing and communication minimization. As we identify that the order of dispatching parallel threads has a significant influence on the total simulation time, and Longest Job First (LJF) shows better performance than the Linux default thread dispatch policy, we first propose a segment-aware LJF scheduler for PDES. Our segment-aware scheduler can accurately predict the run time of the thread segments ahead, and thus make better dispatching decisions. Next, we define the concept of core distance for multi-core and many-core architectures, which quantifies core-to-core communication latency and characterizes processor hierarchies. For many-core architectures using directory-based cache coherence protocols, we observe that

core-to-core transfers are not always significantly faster than main memory accesses, and the core-to-core communication latency depends not only on the physical placement on the chip, but also on the location of the distributed cache tag directory. Thus, using a ping-pong memory benchmark, we quantify the core distance on a ring-network many-core platform and propose an algorithm to optimize thread-to-core mapping in order to minimize on-chip communication overhead. Altogether, based on a static analysis of communication patterns and core distance and a dynamic profiling of computation load, our proposed framework utilizes a heuristic graph partitioning algorithm and automatically generates an optimized thread mapping, which minimizes inter-chip communication overhead. In our systematic evaluation, our approach consistently shows a significant performance gain on top of the order-of-magnitude speedup of PDES.

The contributions of this dissertation include a segment-aware multi-core scheduler, core distance profiling, a communication-aware thread mapping framework, together with an open-source software package for Out-of-Order PDES.

## Chapter 1

## Introduction

Embedded and cyber-physical systems are pervasive and ubiquitous nowadays, covering automotive and avionic systems, medical devices, smart home appliances, mobile and consumer electronics, and others. However, due to the increasing size, complexity and heterogeneity of the embedded and cyber-physical systems, it is extremely difficult for system designers to consider all the implementation details at the early stages of the design [72, 62]. Therefore, Electronic System Level (ESL) [62] design methodology is proposed to cope with such design challenges. With this approach, designers can elevate the abstraction level of the design and hide low-level implementation details, and thus focus on the functional specification and algorithms in the design. Before the system level design is refined to a lower abstraction level, it must be verified to assure the correctness [28]. The most common approach to verify the system level design is Simulation-based Validation, which is relatively fast yet accurate [25]. As the parallel processing capabilities are readily available in today's multicore and many-core hosts, parallel ESL simulation has recently attracted a lot of attention. In this dissertation, we aim at optimizing the thread-to-core mapping in parallel Electronic System Level simulation.

### 1.1 System Level Design and Simulation

The 2004 edition of the International Technology Roadmap for Semiconductors defines system level as "a level above RTL including both hardware and software design" [41]. In order to address the design challenges of radically increasing size and complexity of both embedded hardware and software, system level design is proposed as a holistic approach to cover the complete picture of the entire system. Figure 1.1 illustrates the complexities of different levels of abstraction in system design. Clearly, while there are tens of millions of transistors in a system, the number of components in the system level is reduced to less than ten, which mainly consist of hardware platforms and software implementations. The trade-off here is that the higher the abstraction level is, the less complexity and accuracy the model has. Due to the design challenges of embedded systems nowadays, "a well-known solution for dealing with complexity is to exploit hierarchy and to move to higher levels of abstraction" [24]. Thus, system level modeling is a promising approach at the early stages of the design.

Figure 1.1: Level of abstraction in system design [31].

In order to shorten the time-to-market design period, fast and accurate ESL simulation is critical in system design and validation. Basically, there are three types of computer-based simulation: discrete event, continuous and Monte Carlo [65]. As digital systems are naturally discrete, most of the ESL simulation approaches use discrete event semantics. Next, we discuss different Discrete Event Simulation (DES) scheduling algorithms.

#### 1.1.1 Discrete Event Simulation

In order to describe hardware and software components in system level designs, System-Level Description Languages (SLDLs) are proposed to add supports of system level modeling, such as behavioral and structural hierarchy, concurrency, communication, synchronization, and timing constraints [25]. Two predominant examples of SLDLs are SystemC [33] and SpecC [29]. While SpecC is a superset of ANSI-C and widely used in academia, SystemC is a C++ library and the de-facto language for system level design in industry. Also, SystemC is published as an IEEE standard for system design [37]. Thus, we use SystemC as the example of SLDL in this dissertation.

Figure 1.2: Traditional Discrete Event Simulation (DES) scheduler for SystemC [56].

Figure 1.2 depicts a traditional Discrete Event Simulation (DES) scheduling algorithm for SystemC. In DES, we have the following definitions of data structures and operations [26]:

#### 1. Definition of thread queues in DES:

- QUEUES = {READY, RUN, WAIT, WAITTIME, COMPLETE}.

- READY =  $\{th \mid th \text{ is ready to run}\}.$

- $RUN = \{th \mid th \text{ is currently running}\}.$

- WAIT =  $\{th \mid th \text{ is waiting for an event}\}.$

- WAITTIME =  $\{th \mid th \text{ is waiting for time advance}\}.$

- COMPLETE =  $\{th \mid th \text{ has completed its execution}\}.$

#### 2. Simulation invariants in DES:

Let THREADS be the set of all threads created in DES. Then, at all times, the following conditions hold:

- THREADS = READY  $\cup$  RUN  $\cup$  WAIT  $\cup$  WAITTIME  $\cup$  COMPLETE.

- $\bullet \ \, \forall A,B \in \mathsf{QUEUES}, A \neq B: A \cap B = \varnothing.$

#### 3. Operations on threads and queues:

- $\mathbf{Run}(th)$ : Dispatch thread th and th starts execution.

- $th = \mathbf{Pick}(\mathsf{READY})$ : Pick a thread th from the READY queue.

- Remove(th, WAIT): Remove the thread th from the WAIT queue.

- Insert(th, READY): Add the thread th to the READY queue.

#### 4. Initial state at the beginning of DES:

- THREADS =  $\{th_{root}\}$ .

- $RUN = \{th_{root}\}.$

- READY = WAIT = WAITTIME = COMPLETE =  $\varnothing$ .

- $(t, \delta) = (0, 0)$  where t represents the timed cycle, and  $\delta$  represents the delta cycle.

In DES, the timed cycle represents the acutal time advance, and the delta cycle interprets the zero-delay semantics in digital systems. Specifically, the delta cycle lasts for an infinitesimal amount of time and imposes a partial order of simulation actions [33]. Also, SystemC standard allows to notify an event immediately within the same delta cycle [37]. Thus, the scheduling algorithm in Figure 1.2 implies three causal loops resulting from immediate notification, delta cycle and timed cycle.

In Figure 1.2, it is clear that there is a single thread running at all times. When one thread finishes its current evaluation phase, it yields to another thread in the READY queue. When all threads in the READY queue complete their current delta cycle, the root thread resumes and performs the channel update and event notification. Then, a new delta cycle begins. If no more threads are runnable after the update and notification, the scheduler advances the simulation time and starts a new timed cycle. The earliest timed event is processed and the associate thread is moved from the WAITTIME queue to the READY queue. The traditional DES terminates when both the WAITTIME and READY queues are empty.

### 1.1.2 Synchronous Parallel Discrete Event Simulation

In comparison to DES, a Parallel Discrete Event Simulation (PDES) [27] scheduler dispatches multiple threads from the READY queue concurrently. Figure 1.3 shows a synchronous PDES scheduler for SystemC.

In the synchronous PDES scheduling algorithm, as long as the READY queue is not empty and an idle core is available, one more thread is dispatched from the READY queue. When a thread finishes earlier than other threads in the same delta cycle, a new ready thread is assigned to the idle core, unless no more thread is available in the READY queue. In this case, the processing core keeps idle until the next delta cycle or any event is immediately notified. Then, after all threads finish their current delta cycle, the last running thread performs the

Figure 1.3: Synchronous Parallel Discrete Event Simulation (PDES) scheduler for SystemC [56].

update and notification phases, and advances the timed cycle if the READY queue is still empty. Note that the synchronous PDES implies an absolute barrier at the end of delta and timed cycle. All threads are blocked at the barrier until any other threads finish their current evaluation phase.

In order to avoid race conditions among accesses to internal scheduling resources, synchronous PDES introduces a mutex lock to protect the SystemC kernel. Any thread needs to acquire the mutex before modifying the state of the kernel. For safe communication, the channel between modules is explicitly protected with a local lock. Also, note that while any threading model (user-level or kernel-level threads) is acceptable for the traditional DES, the underlying operating system needs to be aware of the parallel threads in PDES [25]. Thus, only kernel-level threads (e.g., POSIX threads) are applicable in the synchronous PDES.

In the SystemC Language Reference Manual (LRM) [37], it clearly states that "process instances execute without interruption". This requirement is also known as cooperative (or co-

routine) multitasking in the SystemC execution semantics. As detailed in [26], this particular problem of parallel simulation is specifically addressed in the SystemC LRM:

"An implementation running on a machine that provides hardware support for concurrent processes may permit two or more processes to run concurrently, provided that the behavior appears identical to the co-routine semantics defined [...]. In other words, the implementation would be obliged to analyze any dependencies between processes and constrain their execution to match the co-routine semantics."

We will describe the required dependency analysis for parallel SystemC simulation in Section 1.2, which is also needed for the Out-of-Order PDES.

#### 1.1.3 Out-of-Order Parallel Discrete Event Simulation

In order to break the implicit barriers at the delta and timed cycle boundaries in the synchronous PDES, [12, 11] propose an Out-of-Order Parallel Discrete Event Simulation (OoO PDES) scheduling algorithm. Figure 1.4 depicts the OoO PDES scheduler for SystemC.

In OoO PDES, data structures and operations are refined as follows:

- 1. Each thread th is assigned a localized time stamp  $(t_{th}, \delta_{th})$ .

- 2. Each event is assigned a notification time stamp  $(t_e, \delta_e)$ .

- 3. Time stamps are ordered in the following way:

- $(t_1, \delta_1) = (t_2, \delta_2)$  iff  $t_1 = t_2, \delta_1 = \delta_2$ .

- $(t_1, \delta_1) < (t_2, \delta_2)$  iff  $t_1 < t_2$ , or  $t_1 = t_2, \delta_1 < \delta_2$ .

Figure 1.4: Out-of-Order Parallel Discrete Event Simulation (OoO PDES) scheduler for SystemC.

- $(t_1, \delta_1) > (t_2, \delta_2)$  iff  $t_1 > t_2$ , or  $t_1 = t_2, \delta_1 > \delta_2$ .

- 4. Thread queues are separated to multiple sets with different time stamps:

- QUEUES = {READY, RUN, WAIT, WAITTIME, COMPLETE}.

- READY =  $\cup$ READY<sub>t, $\delta$ </sub>, READY<sub>t, $\delta$ </sub> = {th | th is ready to run at  $(t, \delta)$ }.

- $RUN = \bigcup RUN_{t,\delta}$ ,  $RUN_{t,\delta} = \{th \mid th \text{ is running at } (t, \delta)\}$ .

- WAIT =  $\bigcup$ WAIT<sub> $t,\delta$ </sub>, WAIT<sub> $t,\delta$ </sub> = { $th \mid th$  is waiting for an event ( $id_e, t_e, \delta_e$ ) since ( $t, \delta$ ), where ( $t_e, \delta_e$ )  $\geq$  ( $t, \delta$ )}.

- WAITTIME =  $\cup$ WAITTIME<sub>t, $\delta$ </sub>, WAITIME<sub>t, $\delta$ </sub> = {th | th is waiting for time advance to  $(t, \delta)$ }.

- COMPLETE =  $\cup$ COMPELETE<sub>t, $\delta$ </sub>, COMPLETE<sub>t, $\delta$ </sub> = {th | th completed its execution at  $(t, \delta)$ }.

#### 5. Initial state at the beginning of OoO PDES:

- THREADS =  $\{th_{root}\}$ , where  $(t_{root}, \delta_{root}) = (0, 0)$ .

- $RUN = RUN_{0.0} = \{th_{root}\}.$

- READY = READY $_{0,0}$  = WAIT = WAIT $_{0,0}$  = WAITTIME = WAITTIME $_{0,0}$  = COMPLETE = COMPLETE $_{0,0}$  =  $\varnothing$ .

In OoO PDES, every thread th has its own localized time stamp  $(t_{th}, \delta_{th})$ , so that the global in-order event and simulation time updates are relaxed, allowing more threads (at different simulation cycles) to run in parallel and ahead of time [11, 56]. This results in a higher degree of parallelism and thus higher simulation speed.

Compared to the synchronous PDES in Figure 1.3, there is no more classic delta and timed cycles in Figure 1.4. Each thread performs the delta and timed cycles locally. Thus, due to the out-of-order scheduling and the eliminated central scheduling point for delta cycles, it is rather difficult to determine a safe point in OoO PDES scheduling when primitive channel update requests can be served. However, it is always possible to safely fall back to synchronous PDES (SYSC\_SYNC\_PAR\_SIM equals true in Figure 1.4) when primitive channel updates are requested.

In Figure 1.4, the Out-of-Order PDES scheduling is aggressive. The scheduler moves threads from the WAIT queue to the READY queue whenever the READY and RUN queues become empty, and any threads in WAITTIME are moved to READY as soon as possible. Also, the scheduler dispatches one more thread for execution as long as an idle core and a ready thread without conflicts (NoConflicts(th) is true) are available.

Algorithm 1 lists the pseudocode of conflict detection in the OoO PDES scheduler. Here, NoConflicts(th) checks for any potential conflicts between Thread th and any other concurrent threads in RUN, READY and WAIT with an earlier or equal time. For each pair of

#### Algorithm 1 Conflict Detection in OoO PDES Scheduler

```

1: bool NoConflicts(Thread th) {

2: for all th_2 \in \mathsf{RUN} \cup \mathsf{READY} \cup \mathsf{WAIT} where (th_2.t, th_2.\delta) \leq (th.t, th.\delta) do

if Conflict(th, th_2) then

4:

return false

5:

end if

6: end for

7: return true

8: }

9:

10: bool Conflict(Thread th, Thread th_2) {

11: if th has data conflict with th_2 then

return true /* check data hazards */

12:

13: end if

14: if th_2 may enter another segment before th then

return true /* check time hazards */

15:

16: end if

17: if th_2 may wake up another thread to run before th then

return true /* check event hazards */

19: end if

20: return false

21: }

```

concurrent threads,  $Conflict(th, th_2)$  checks for any data, timing and event hazards between Threads th and  $th_2^{-1}$ . As we are using advanced static compile-time analysis and optionally dynamic run-time analysis (Section 1.2) to identify all the potential conflicts, these checks can be performed in constant time as simple table lookups.

## 1.2 Recoding Infrastructure for SystemC (RISC)

To realize the OoO PDES approach for the SystemC language, we propose the Recoding Infrastructure for SystemC (RISC) and describe the overall RISC Compiler and Simulator proof-of-concept prototype (Beta Release V0.3.0 as of 2016-09-30) in [56]. Currently, the

<sup>&</sup>lt;sup>1</sup>Note that Algorithm 1 here is revised from Algorithm 2 in [11], in order to match the SystemC semantics.

RISC software is available as an open source package and can be downloaded freely from the following website [55]: http://www.cecs.uci.edu/~doemer/risc.html.

Figure 1.5: RISC Compiler and Simulator for OoO PDES of SystemC.

In contrast to the traditional SystemC simulation where a regular SystemC-agnostic C++ compiler includes the SystemC headers and links the input model directly against the SystemC library, we introduce a *dedicated SystemC compiler* to perform semantics-compliant SystemC simulation with maximum parallelism. As shown in Figure 1.5, our RISC compiler acts as a frontend that processes the input SystemC model and generates an intermediate model with special instrumentation for OoO PDES. The instrumented parallel model is then linked against our extended RISC SystemC library by the target compiler (a regular SystemC-agnostic C++ compiler) to produce the final executable model. OoO PDES is then performed simply by running the generated executable model.

From the user perspective, we essentially replace the regular SystemC-agnostic C++ compiler with the SystemC-aware RISC compiler (which in turn calls the underlying C++ compiler). Otherwise, the overall SystemC validation flow remains the same as before. It is just faster due to the parallel simulation.

Internally, the RISC compiler performs three major tasks, namely Segment Graph construction, conflict analysis, and source code instrumentation. The simulator implements the semantics-compliant Out-of-Order PDES of SystemC, and falls back to synchronous PDES when the update methods in primitive channels are requested.

#### 1.2.1 Segment Graph

The first task of the RISC compiler is to parse the SystemC input model into an Abstract Syntax Tree (AST) and then create a SystemC structural representation from the AST which reflects the SystemC module and channel hierarchy, connectivity, and other SystemC-specific relations, similar to the SystemC-clang representation [48, 69]. On top of this, the RISC compiler then builds a Segment Graph (SG) [12] data structure for the model.

In DES and PDES, threads switch back and forth between the states of running (threads in the READY and RUN queues) and waiting (threads in the WAIT and WAITTIME queues). A series of source code statements executed by a thread between two scheduling points can be defined as a thread segment [11]. Then, for a SystemC model, it can be converted to a corresponding Segment Graph (SG). The SG is a directed graph that represents the code segments executed during the simulation. The nodes in the SG are code segments and the edges indicate the transitions from one segment to another. The code segments always start from a SystemC scheduling primitive, e.g., wait, SC\_METHOD, SC\_THREAD, and SC\_CTHREAD.

Figure 1.6 shows a SystemC thread with its segments and the corresponding SG. As shown, every segment starts with a scheduling primitive (including thread creation and context switches, e.g., the SC\_THREAD in line 23 or the wait statement in line 12) and ends before another. The read and write functions in this example invoke a wait statement inside the function calls, so they are all blocking and start new segments (segment 1 and 3 in the read function and segment 4 in the write function). Also, as indicated in Figure 1.6a and 1.6b, one source code statement (e.g., the while statement in line 8) may belong to several

```

SC MODULE (M)

sc_port<i blocking_receiver> InPort1;

sc_port<i_blocking_receiver> InPort2;

sc_port<i_blocking_sender> OutPort;

void main (void)

int i, x, y;

while (true) {

InPort1->read(x);

for (i=0; i<LOOP1; i++)</pre>

x += 1;

wait(1, SC_MS);

if (x%2 != 0) {

InPort2->read(y);

for (i=0; i<LOOP2; i++)

x *= y;</pre>

15

OutPort->write(x);

18

19

20

21

SC_CTOR(M) {

23

SC_THREAD(main);

24

```

```

26 class c_blocking_channel: public sc_channel, 27 public i_blocking_receiver,

public i_blocking_sender {

private:

29

30

sc_event Req;

sc_event Ack;

32

33

read(y) 35

public:

read(x)

void read(int &d) {

s0s2<mark>s4</mark>

s2 36 s2 37

d = Data;

s0s2<mark>s4</mark>

Ack.notify(SC_ZERO_TIME);

38

wait (Req);

39

write(x) 40 41

void write(int d) {

wait(Ack);

43

Data = d;

Req.notify(SC_ZERO_TIME);

44

45

46

c_blocking_channel(sc_module_name name):

47

48

sc_channel(name) { Data = INITIAL_VALUE; }

```

(a) Source code of an SC\_THREAD.

(b) Source code of read and write.

(c) Segment graph.

Figure 1.6: SystemC thread and Segment Graph (SG) [57].

segments, depending on the execution paths. Here, the implementation of  $c\_blocking\_channel$  is simplified for demonstration purpose.

- [11] presents a formal description of the Segment Graph and its construction algorithm, and

- [75] lists the detailed RISC Application Programming Interface (API).

## 1.2.2 Conflict Analysis

The segment graph data structure serves as the foundation for segment *conflict analysis*. As outlined in Algorithm 1, the OoO PDES scheduler must ensure that every ready thread to be dispatched has no conflicts (e.g., data hazards, timing hazards and event hazards) with any other threads currently in the READY, RUN and WAIT queues. Here, we utilize the RISC compiler to detect any potential conflicts between these threads with *static* analysis at compile time or *dynamic* analysis at run time.

- Static Analysis: Static analysis relies purely on the available information in the SystemC source code of the design model at hand. In this case, the RISC compiler performs very conservative identification of the potential hazards in the model, as outlined in [11]. Identifying all possible hazards is a complex analysis task that requires the full "understanding" of the module hierarchy. Here we statically extract the module hierarchy and analyze the individual threads.

- Dynamic Analysis: However, in most cases not all of the needed information can be gathered statically. For instance, design parameters may be passed via the command line to define the number of modules, certain channel characteristics, or other configuration information. In such SystemC models, the instantiated modules, channels, and ports are typically created through loops in a dynamic fashion. Thus, these exact parameters are only available at run time, so they cannot be statically analyzed. In these cases, dynamic analysis is needed.

In dynamic analysis, the compilation flow is extended by a preprocessing step. The input SystemC model is fed into the RISC elaborator which produces an executable model that only performs the SystemC elaboration phase. At the end of the elaboration phase, the executable model automatically traverses the created module hierarchy via the SystemC introspection API and dumps this detailed structural design information into an instance connectivity file. This file is in turn provided as an input to the RISC compiler, so that the dynamically created design hierarchy and specific instance connectivity can be used for precise conflict analysis. The instance connectivity data

file includes the actual module hierarchy, the specific port mapping, and the actual target variable mapping of references.

The dynamic analysis takes run-time information into account and augments the classic static analysis. The combination of static and dynamic analysis in the RISC compiler is called *hybrid* analysis [77].

#### 1.2.3 Source Code Instrumentation

As a result of the conflict analysis (static, dynamic, or hybrid [77]), the RISC compiler generates several conflict tables that describe all possible conflicts between threads in any two segments. Using this conservative information, the simulator can then at run-time quickly determine by a simple table lookup whether or not it is safe to dispatch any given thread in parallel or ahead of time.

To pass information from the compiler to the simulator, we use automatic model instrumentation. That is, the intermediate model generated by the compiler contains instrumented (automatically generated) source code which the simulator can then rely on. At the same time, the RISC compiler also instruments user-defined SystemC channels with automatic protection against race conditions among communicating threads, as discussed in Section 1.1.2. Note that the source code instrumentation is performed automatically by the RISC compiler and no user-interaction is necessary.

In total, the RISC source code instrumentation includes four major components:

Segment and instance IDs: Individual threads are uniquely identified by a creator instance ID and their current code location (segment ID). Both IDs are passed into the simulator kernel as additional arguments to scheduling primitives, including wait and thread creation.

- 2. **Data and event conflict tables**: Segment concurrency hazards due to potential data conflicts and event conflicts are provided to the simulator as two-dimensional tables indexed by a pair of segment ID and instance ID.

- 3. Current and next time advance tables: Timing hazards between concurrent threads are passed to the RISC simulator as one-dimensional tables indexed by segment ID.

- 4. User-defined channel protection: SystemC allows users to define new channels for customized inter-thread communication. To ensure such communication is also safe in OoO PDES, the RISC compiler automatically protects user-defined channels (e.g., those derived from sc\_channel and sc\_prim\_channel) by acquiring a channel lock (mutex) at the entry of the channel methods and releasing the lock at the exit. Thus, it is guaranteed that the execution of channel methods is mutually execlusive, and avoids the potential race conditions when communicating threads exchange data.

### 1.2.4 Compiler Backend

After the automatic source code instrumentation, the RISC compiler passes the generated intermediate model to the underlying regular C++ compiler. That target compiler then generates the final simulation executable by linking the instrumented code against the RISC extended SystemC library.

#### 1.2.5 Simulator

Same as the Accellera proof-of-concept implementation of System DES [86], the RISC simulator is not an explicit tool, but a run-time library [52] that the generated executable model

is linked against. Thus, the Out-of-Order PDES is performed by executing the generated model from the target compiler.

By default, the RISC simulator follows the Out-of-Order PDES scheduling algorithm as outlined in Section 1.1.3. However, as soon as SystemC primitive channels are used with requests to the update methods, the simulator falls back to the synchronous PDES execution. Thus, as discussed in Section 1.1.3, such models will execute in safe synchronous mode.

As OoO PDES allows a higher number of threads running in parallel or even ahead of time, run-time scheduling optimization becomes critical for maximizing the simulation performance. Thus, we focus on the thread-to-core mapping and scheduling in this dissertation, and present details of various optimization algorithms in the following chapters.

## 1.3 Thread-to-Core Mapping

As discussed in Section 1.1.2 and 1.1.3, there are multiple threads running concurrently in the synchronous PDES and Out-of-Order PDES. A key challenge here is to determine the thread-to-core mapping for extracting maximum simulation performance [46, 17, 92]. Due to the shared resource contention on processing units and memory hierarchy, the simulation speed can be slowed down by more than 50% [92], and the scalable performance is not always readily available on multi-core and many-core hosts [18]. Also, the heterogeneity of the memory hierarchy may lead to varying communication latency, depending on whether the communication happens through local or remote caches, or even main memory [21]. Due to the complexity of the applications' behavior, the underlying resource topologies and the cache coherency protocols, determining the thread-to-core mapping that ensures the lowest contention and performance degradation [87, 81] has exponential complexity [19] and the problem of optimal thread-to-core mapping is NP-complete [44]. As an inefficient

thread-to-core mapping also results in inefficent resource usage on multi-core and many-core hosts [45, 49], it is critical to efficiently optimize thread mapping in synchronous and Out-of-Order PDES.

In general, there are two categories of thread mapping methods, i.e., static and dynamic. The static methods usually leverage memory traces from binary instrumentation tools [71, 3, 23], which characterize the communication and computation loads for an application through profiling. Then, a static thread mapping is produced for the application to improve its run-time performance. Static mapping methods [9, 71, 3, 23] are simple to apply, and do not require to modify the source code of applications or support libraries. However, static thread mappings are not responsive to the run-time behavior of mapped workloads [54]. In comparison, dynamic thread mapping detects communication and tracks correlation between threads at run time, and performs online thread migration to cope with workload phase changes [21, 54]. It usually monitors page table accesses or page faults [22, 21, 88] to characterize the communication patterns, and then formulates the mapping problem as graph matching [22, 21] or 0-1 Integer Linear Programming (ILP) [46, 54]. In most cases, dynamic mapping performs better than static mapping at run time, but needs to be implemented at the OS kernel level [21, 22, 88].

In comparison to the general applications where any number of concurrent threads may arrive, execute and terminate in an unpredictable way [19], all the ready-to-run threads in SystemC PDES are available at the beginning of the delta cycle. Also, the behavioral and structural hierarchy of the ESL design model is clearly specified in SLDL (e.g., SystemC or SpecC) source code. Thus, the execution flow of PDES can be analyzed statically from the source code, and the same execution pattern repeats periodically<sup>2</sup>. In addition, both SLDL (SystemC and SpecC) implement their simulation libraries in the user level [86, 7] for

<sup>&</sup>lt;sup>2</sup>In SystemC it is a common coding idiom to include an infinite loop within a SC\_THREAD or a SC\_CTHREAD, and a SC\_METHOD executes its associate function from beginning to end whenever it is triggered [37]. SpecC has similar characteristics [29].

flexibility and portability, so dynamic mapping methods at the kernel level are not a good fit here. On the other hand, static methods using memory traces or binary analysis usually incur a high overhead [21]. Therefore, we propose a hybrid approach in this dissertation.

Figure 1.7: Problem decription of thread-to-core mapping in SystemC PDES.

Figure 1.7 depicts the problem of thread-to-core mapping in the context of SystemC PDES, together with our proposed approach. Here, we define our problem as follows:

With full source code of an ESL design model and no a priori knowledge of the underlying host architecture, optimize the thread-to-core mapping in SystemC Parallel Discrete Event Simulation. The goal here is to mitigate resource contention and communication latency and thus improve simulation performance.

In order to solve this problem, we propose to utilize our RISC compiler outlined in Section 1.2, and generate a communication pattern (presented in Section 4.4) to characterize the workload

and communication in a design model. Then, as for the host architecture, we identify it with a concept of *core distance* (defined in Section 3.2) through profiling. Next, with two graphs (i.e., *Communication Pattern* and *Core Distance Graph* in Figure 1.7) available, a graph theory solver is used to generate an optimized thread mapping at run time. Compared to the previous thread mapping methods, our proposal is entirely implemented at the user level, and specifically designed for SystemC PDES. It guarantees sufficient accuracy and manageable overhead.

### 1.4 Related Work

Due to the inexpensive availability of parallel computing capabilities on multi-core and many-core hosts, Parallel Discrete Event Simulation (PDES) has become increasingly popular [27, 8, 67] during the past few decades. Despite all the PDES approaches follow the Discrete Event Simulation (DES) semantics and dispatch multiple threads concurrently, they differ in three major aspects: synchronization paradigms, abstraction levels, and host architectures.

Currently, there exist two major synchronization paradigms in PDES approaches, namely conservative and optimistic. Conservative PDES typically requires dependency analysis, and only dispatches threads that are safe to run concurrently. Either the conservative synchronous PDES scheduler [78] ensures in-order execution where the temporal barriers prevents effective parallelism, or the asynchronous approach [11] requires advanced compile-time conflict analysis (Section 1.2.2) to break the implicit barriers at the boundaries of delta and timed cycles. In contrast, optimistic PDES [43] assumes that threads are always safe to run and performs rollbacks if errors are detected.

Recalling Figure 1.1 which depicts the abstraction levels in system design, various PDES approaches also target different levels of abstraction. [34] compares different PDES approaches,

including synchronous, asynchronous and cycle based simulation, at the Register Transfer Level (RTL). In order to speed up simulation, Transaction Level Modeling (TLM) [6] elevates the abstraction of communication and trade-offs timing accuracy against simulation speed. Also, source-level [84] and host-compiled [30] simulation abstract computation on the target platform to boost simulation speed. In addition, some approaches target mixed-abstraction levels (e.g., RTL and TLM in [79]).

Other PDES approaches are customized for specific host architectures. While most PDES approaches [78, 11, 63] target the common Symmetric Multiprocessing (SMP) machines, [80] emulates SystemC descriptions on FPGA and [66] partitions computation model in SystemC into concurrent threads on GPGPU. In [79], authors parallelize SystemC simulation across CPUs and GPUs.

As various PDES approaches allow multiple threads running concurrently on parallel processing units, it is critical to schedule these threads efficiently. In general, thread-to-core mapping is optimized for mitigating resource contention and communication latency in parallel execution. Two distinguished categories of mapping methods exist, namely static and dynamic. The static mapping methods [71, 3, 23] usualy use memory traces or binary analysis to characterize the computation and communication behaviors of an application, and generate a static thread mapping at compile time. In contrast, dynamic methods [54, 22, 21, 88, 46] profile applications at run time, and perform thread migration in response to the dynamic workload variation. [21] monitors accesses to page table and detects shared pages between threads, using this information as the communication pattern to dynamically migrate threads. In [19], authors propose an approach to first characterize applications offline, and then dynamically adjust the thread mapping at run time, based on the static application characteristics. [13] presents a run-time strategy that incorporates the user behavior information. In addition, thread mapping and data mapping are closely related. [22, 9, 46, 36] exploits thread mapping and data mapping simultaneously.

Different mapping methods are also customized for different host architectures. In [54] and [5], authors propose dynamic thread mapping strategies for heterogeneous multiprocessor systems. [51, 50] target General-Purpose Graphics Processing Units (GPGPU), and [88, 82] study Distributed Shared Memory (DSM) systems. Also, thread mapping for Networks-on-Chip (NoC) is a hot research topic [46, 13, 64, 9] in recent years. In [60, 15], authors take the characteristics of Non-Uniform Memory Access (NUMA) systems into consideration, and reduce the costly remote memory accesses via thread mapping. [35, 36] address the problem of thread mapping on Chip Multiprocessors (CMP).

In comparison to the previous mapping methods for general applications, we propose a PDES-specific approach in this dissertation. As outlined in Section 1.1, a number of threads are ready to run at the beginning of the delta cycle, and the behavioral and hierarchical structure of the design model is well presented in SLDL. Thus, we propose to first use our RISC compiler (Section 1.2) to analyze the communication pattern of the design model, and then optimize thread mapping at run time. Also, our approach requires no a priori knowledge of the underlying platform. It automatically profiles the host architecture and incorporates this information to the thread mapping optimization.

# 1.5 Goals and Overview

As outlined in Section 1.3, a good thread mapping for multiprocessor architectures (e.g., DSM, NUMA, and NoC) usually has the following requirements [88]:

- 1. Load Balancing: Load is uniformly distributed across different nodes (e.g., processors), and nodes' computational capacities match threads' computational needs.

- 2. Communication Minimization: The communication cost between threads located on distinct nodes are minimized.

Here, Load Balancing aims at mitigating the contention on shared resources, specifically the processing elements, on the host platform. In order to efficiently utilize the available computing units, none of them should be overloaded or underloaded. On the other hand, Communication Minimization targets the costly communication latency between separate nodes. To take advantage of the faster on-chip communication, it is necessary to map threads that share a high communication volume to processing cores on the same node. Both Load Balancing and Communication Minimization need to be taken into consideration in thread-to-core mapping.

Figure 1.8: Decomposition of execution time of ESL simulation.

When running an ESL simulation on Linux, its execution time consists of two parts, namely system time and user time, when the simulation runs in kernel mode and user mode, respectively. In particular, user time can be further decomposed into computation time and communication time, according to the purpose of the execution. Figure 1.8 illustrates the typical decomposition of the execution time. Here, in order to optimize thread-to-core mapping for parallel ESL simulation, we would like to target different parts of the complete execution time.

First, the system time refers to the amount of time when the application executes in the kernel mode. It is mainly contributed by thread context switching and system I/O, and usually much shorter than user time. Note that it is difficult to accelerate the system time purely by user-level thread mapping. The most effective approach is to optimize the

underlying thread library. Our previous work [53] proposes a hybrid thread library to reduce the overhead of thread creation/deletion and context switching.

Next, the computation time covers the amount of time on data crunching, mainly in the Arithmetic-Logic Unit (ALU) and Floating-Point Unit (FPU). When the total workload is determined by the specification and compiler, the total computation time varies significantly, depending on the dispatch order and thread-to-processor partitioning. **Load Balancing** improves computation time effectively.

Last, the communication time is composed of the communication latency between threads and the memory access. Notably, the memory hierarchy presents different access speeds on different levels, and the on-chip communication is always faster than the inter-chip one. Thus, **Communication Minimization** is a promising approach to shorten communication time.

Section 1.3 defines our problem of thread mapping. More specifically, our goals include:

- 1. Reducing the Computation Time in SystemC PDES: For those computation-intensive applications and examples, we would like to optimize load balancing in PDES through thread mapping, so as to reduce the computation time effectively.

- 2. Mitigating the Communication Time in SystemC PDES: For those communication-intensive examples, it is critical to mitigate the costly on-chip and inter-chip communication, and map threads that share a high amount of communication to cores on the same chip.

- 3. Decreasing the Total User Time in SystemC PDES: Finally, we target the general-purpose application, in which both computation and communication are significant. Here, we try to minimize the complete user time in SystemC PDES, by taking both Load Balancing and Communication Minimization into consideration.

In the following chapters, we present our approach to realize these goals. Specifically, Goal 1 is addressed in Chapter 2, and Goal 2 is achieved in Chapter 3 and 4. In Chapter 5, we propose an integrated algorithm to meet Goal 3.

The rest of the dissertation is organized as follows:

In Chapter 2, we propose a dynamic load-profiling and segment-aware scheduling algorithm with optimized thread dispatching to balance workloads on parallel processing units. Based on a compile-time generated Segment Graph (SG), our scheduler [57] can accurately predict the run time of the thread segments ahread and thus make better dispatching decisions. In the evaluation, our segment-aware scheduler consistently shows a significant performance gain compared to the previous scheduling policies.

In Chapter 3, we first define the concept of *core distance* for multi-core and many-core architectures, and observe that for many-core architectures using directory-based cache coherence protocols, the core-to-core communication latency depends not only on the physical placement on the chip, but also on the location of the distributed cache tag directory. Using a ping-pong memory benchmark, we quantify the core distance of a ring-network platform, and propose an algorithm [58] to optimize the thread-to-core mapping in order to minimize on-chip communication overhead. In our experiments, our algorithm speeds up communication-intensive benchmarks by more than 25% on average over the Linux default mapping strategy.

Based on the core distance concept from Chapter 3, we explore thread mapping for the general multiprocessor architectures in Chapter 4. By analyzing the communication pattern and profiling the processor architecture, our proposed framework formulates the problem of thread mapping as graph partitioning and automatically generates an optimized thread-to-core mapping for the target architecture. Our framework is *not* customized for a specific

architecture, and reduces the costly inter-chip communication. In the comprehensive evaluation, our approach shows a performance gain of up to 28% with negligible overhead.

In Chapter 5, we integrate our thread mapping techniques in Chapter 2 and 4 to reduce the total user time for general design models, in which both computation and communication are intensive. The experimental results show that our integration performs better than both techniques from Chapter 2 and 4 for a real-world application, and achieves an additional speedup of 10% compared to the previous two methods.

Finally, Chapter 6 concludes this dissertation with a summary of our contributions and the future work.

# Chapter 2

# Computation-Aware Thread Mapping

In this chapter, we first propose a dynamic load-profiling and *segment-aware* scheduling algorithm with optimized thread dispatching to reduce the computation time in SystemC PDES. Based on a static segment graph from our RISC compiler (Section 1.2), our segment-aware scheduler [57] accurately predicts the run time of the thread segments ahead, and makes better dispatching decisions for load balancing.

## 2.1 Introduction

Discrete Event Simulation (DES) has been in use for decades to validate the functionality of Electronic System Level (ESL) designs. In order to improve the performance of DES, Parallel Discrete Event Simulation (PDES) [27] was proposed to run threads in parallel. With the popularity of multi-core hosts, parallel computing platforms are readily available and provide great potential to achieve better performance.

Currently, the SystemC [37] System-Level Description Language (SLDL) is used for system design as an IEEE standard. However, the reference simulation library of SystemC still relies

on DES, running a single thread at any time, and cannot utilize the computing capabilities of parallel platforms. In recent years, a lot of parallel SystemC simulation approaches [78, 34, 79, 63] have been proposed, which speed up simulation significantly due to parallel execution. However, very few of these approaches [14] address the load balancing problem in their parallel schedulers. In this chapter, we propose a segment-aware multi-core thread dispatch algorithm [57], which can be applied to all work-sharing PDES (SystemC, SpecC, etc.) schedulers. By parsing a design model to a graph of thread segments (a portion of source-code statements between two scheduling points) using static compiler analysis and profiling segment execution at runtime, our approach automatically optimizes the thread dispatch order and consistently achieves a significant speedup over previous thread dispatchers.

The key contributions of this chapter are the following:

- 1. We identify Longest Job First (LJF) as a better than default thread dispatch policy, when thread run time prediction is available.

- 2. We propose a novel technique to accurately predict thread run times based on a static Segment Graph (SG) and the specific segments threads will execute.

- We evaluate our proposed segment-aware approach in comprehensive experiments and show that it consistently improves performance for both synthetic and real-world examples.

The rest of the chapter is organized as follows: Section 2.2 reviews background on parallel SystemC simulation and related work on load-balancing optimizations in PDES. In Section 2.3, we introduce our parallel SystemC implementation, then discuss multi-core scheduling, and propose our optimization algorithm in Section 2.4. In Section 2.5, we evaluate our segment-aware algorithm with both synthetic and real-world examples. Section 2.6 concludes the chapter.

# 2.2 Background and Related Work

Parallel SystemC simulation has been a hot research topic in the past few years. In general, these parallel approaches differ in the simulation strategies they apply, the abstraction levels they target, and the host architectures they use. [78] proposes a conservative synchronous parallel simulation approach in which a master thread performs the update and notification phases and a pool of worker threads execute parallel SystemC processes. [34] compares different parallel SystemC approaches, e.g., synchronous PDES, asynchronous PDES, and cycle based simulation, at the Register Transfer Level (RTL). Both [78] and [34] target shared-memory multi-core host architectures. In order to further boost the simulation speed, [79] partitions mixed-abstraction RTL and Transaction Level Models (TLM) into processes suitable for GPU and CPU execution. In [63], the author proposes an approach that explicitly targets loosely timed systems, and runs parallel processes at different simulation cycles. In comparison, [11] proposes a conservative asynchronous PDES approach that also perserves cycle accuracy. The proposed approaches in [63] and [11] run on multi-core hosts.

In this chapter, we implement a synchronous PDES approach similar to [78], and propose a segment-aware thread dispatcher inside the PDES scheduler. Our proposed dispatcher is orthogonal to the above approaches, and can be applied to any work-sharing PDES schedulers for shared-memory multi-core machines.

Compared with the many parallel SystemC simulation approaches, load-balancing optimizations on thread dispatching in the context of PDES have gained little attention. [73] presents a dynamic load migration algorithm for reducing the total number of rollbacks in an optimistic PDES environment. [14] proposes a novel parallel SystemC simulation approach with hierarchical multithreading, and optimizes load balancing by using workload stealing. In [91], authors improve dynamic load balancing of PDES by using the proposed Random, Communication-based and Load-based (RCL) load migration policies. [38] evaluates dif-

ferent process partition strategies (user defined, hash-based, round-robin, etc.) to improve load balancing of parallel simulation. However, in the previous work, the model is divided into distributed logical OS processes and they are allocated to different processors. To avoid workload imbalance on different processors, all the previous work focuses on algorithms to transfer workload among different processes, which is different from ours for work-sharing simulators. To the best of our knowledge, this chapter proposes the first scheduler for work-sharing SystemC PDES with thread dispatch order optimized based on the static analysis of the model at hand.

# 2.3 Parallel SystemC Simulation