# **ORGANIC FIELD-EFFECT TRANSISTORS ON NOVEL**

# **RENEWABLE SUBSTRATES**

A Dissertation Presented to The Academic Faculty

By

Cheng-Yin Wang

In Partial Fulfillment Of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2016

# **COPYRIGHT© 2016 BY CHENG-YIN WANG**

# **ORGANIC FIELD-EFFECT TRANSISTORS ON NOVEL**

# **RENEWABLE SUBSTRATES**

Approved by:

Dr. Bernard Kippelen, Advisor School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Oliver Brand School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Gee-Kung Chang School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Samuel Graham School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: October 25, 2016

To my family

# ACKNOWLEDGEMENTS

I would like to thank my advisor Dr. Bernard Kippelen for his support and guidance. Without him, I could not finish my PhD degree. I also would like to thank Dr. Oliver Brand, Dr. Saibal Mukhopadhyay, Dr. Gee-Kung Chang, and Dr. Samuel Graham for participating as my committee members giving evaluations and suggestions on my dissertation and oral presentation.

During my PhD study, I enjoyed the time working with all current and former Kippelen Research Group members. I am grateful for having help from all of them, especially our research scientist Dr. Canek Fuentes-Hernandez for mentoring me in many details. I truly appreciate the experience and lessons learning from him. I would like to thank our former group members in OFET subgroup: postdoctoral researchers Dr. Sanjeev Singh and Dr. Minseong Yun for training me at the very beginning, and group member Dr. Sangmoo Choi for helps on e-beam evaporation systems in IEN cleanroom and valuable discussions on my research. I also would like to thank support and assistance from all current and former colleagues: Dr. Yinhua Zhou, Dr. Talha Khan, Dr. Jaewon Shim, Dr. James Hsu, Dr. Amir Dindar, Dr. Michael Gaj, Dr. Keith Knauer, Dr. Ehsan Najafabadi, Dr. Asha Sharma, Alfred Ernst, Vladimir Kolesov, Wen-Fang Chou, Xiaojia Jia, Xiaoqing Zhang, Felipe Larrain, Victor Rodriguez Toro, and our administrative manager Tina Moseley.

Many valuable collaborations and team works during my PhD study were not only within our group, but also with other groups at Georgia Institute of Technology. Therefore, I would like to thank Dr. Raghunath Dasari and Dr. Yulia Getmanenko from Dr. Seth Marder's group, Ankit Singh from Dr. Samuel Graham's group, and Dr. Boyi Fu from Dr. Elsa Reichmanis' group. I also would like to thank collaborations with Dr. Jeffrey Youngblood's group at Purdue University and Dr. Robert Moon at U.S. Forest Service.

This work was partially funded by United States Department of Agriculture, United States Department of Energy, Office of Naval Research, Bay Area Photovoltaic Consortium, and Samsung Display.

Last but not least, I want to thank my wife Yin-Chun Chen for her support from a long distance, my mother Mei-Ying Chen for investing and educating me, my memorable father Wen-Bi Wang, my sister Li-Jing Wang, and all my family. Without you, I would not be able to make all my achievements.

# TABLE OF CONTENTS

|                                                         | Page |

|---------------------------------------------------------|------|

| LIST OF TABLES                                          | vii  |

| LIST OF FIGURES                                         | viii |

| LIST OF SYMBOLS                                         | xii  |

| LIST OF ABBREVIATIONS                                   | xiv  |

| SUMMARY                                                 | xvi  |

| CHAPTER                                                 |      |

| 1 INTRODUCTION                                          | 1    |

| 1.1 Printed electronics                                 | 1    |

| 1.2 An introduction to organic field-effect transistors | 2    |

| 1.2.1 Organic semiconductors                            | 2    |

| 1.2.2 The evolution of OFETs                            | 4    |

| 1.2.3 The basic working principle of OFETs              | 5    |

| 1.2.4 More parameters and modeling of OFETs             | 8    |

| 1.2.5 OFET geometry                                     | 10   |

| 1.3 Organization of this dissertation                   | 12   |

| 2 EXPERIMENTAL METHODOLOGY                              | 13   |

| 2.1 Device fabrication                                  | 13   |

| 2.1.1 Overview                                          | 13   |

| 2.1.2 E-beam evaporation                                | 15   |

| 2.1.3 Thermal evaporation                               | 16   |

| 2.1.4 Atomic layer deposition                           | 17   |

| 2.2 OFET measurements                                   | 20   |

|   | 2.2.1 Transfer characteristics                               | 20 |

|---|--------------------------------------------------------------|----|

|   | 2.2.2 Output characteristics                                 | 21 |

|   | 2.2.3 DC bias stress                                         | 22 |

|   | 2.2.4 Repeated transfer characteristics                      | 23 |

|   | 2.3 Capacitor measurements                                   | 23 |

| 3 | OFETS ON CELLULOSE NANOCRYSTAL SUBSTRATES                    | 26 |

|   | 3.1 Introduction                                             | 26 |

|   | 3.2 Design of experiments                                    | 27 |

|   | 3.3 Device fabrication                                       | 29 |

|   | 3.4 Device characterization                                  | 31 |

|   | 3.4.1 Pristine condition in nitrogen                         | 31 |

|   | 3.4.2 Operational stability in nitrogen and air              | 35 |

|   | 3.4.3 Environmental stability in air                         | 38 |

|   | 3.5 Device modeling                                          | 39 |

|   | 3.6 Summary                                                  | 41 |

| 4 | NANOLAMINATE GATE DIELECTRIC FOR OFETS                       | 42 |

|   | 4.1 Introduction                                             | 42 |

|   | 4.2 Design of experiments                                    | 44 |

|   | 4.3 Device fabrication                                       | 44 |

|   | 4.4 Device characterization                                  | 46 |

|   | 4.4.1 Pristine condition in nitrogen                         | 46 |

|   | 4.4.2 Environmental stability in various critical conditions | 47 |

|   | 4.4.3 Operational stability in air                           | 49 |

|   | 4.4.4 Environmental stability in hot water at 95 °C          | 50 |

|   | 4.5 Device modeling                                          | 53 |

|   | 4.6 Summary                                | 55 |

|---|--------------------------------------------|----|

| 5 | REDUCTION OF CONTACT RESISTANCE ON OFETS   | 56 |

|   | 5.1 Introduction                           | 56 |

|   | 5.2 Design of experiments                  | 57 |

|   | 5.3 Device fabrication                     | 58 |

|   | 5.4 Device characterization                | 60 |

|   | 5.5 Device modeling                        | 65 |

|   | 5.6 Summary                                | 66 |

| 6 | OFETS ON PAPER                             | 68 |

|   | 6.1 Introduction                           | 68 |

|   | 6.2 Design of experiments                  | 70 |

|   | 6.3 Device fabrication                     | 71 |

|   | 6.4 Device characterization                | 73 |

|   | 6.4.1 Pristine condition in nitrogen       | 74 |

|   | 6.4.2 Operational stability in nitrogen    | 80 |

|   | 6.4.3 Bending tests in nitrogen            | 81 |

|   | 6.5 Device modeling                        | 84 |

|   | 6.6 Summary                                | 85 |

| 7 | CONCLUSIONS AND RECOMMENDED FUTURE WORKS   | 86 |

|   | 7.1 Conclusions                            | 86 |

|   | 7.2 Recommendations for future work        | 91 |

|   | 7.2.1 Interface property and crystallinity | 91 |

|   | 7.2.2 Gate dielectric                      | 91 |

|   | 7.2.3 Mechanical tests                     | 92 |

|   | 7.3 Publications                           | 93 |

| 7.3.1 Journal publications    | 93 |

|-------------------------------|----|

| 7.3.2 Conference publications | 94 |

| REFERENCES                    | 96 |

# LIST OF TABLES

| Table I: Device dimensions, average mobility, average threshold voltage, and average on/off current ratio of OFETs. | -  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Table II: Design of experiments of OFETs on HD 230                                                                  | 71 |

| Table III: Statistics of OFETs in each type                                                                         | 73 |

| Table IV: Parameters of a type-2 OFET in the bending test                                                           | 83 |

| Table V: Statistical data of type-2 OFETs in the bending test                                                       | 83 |

# LIST OF FIGURES

| Page                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1. An ethylene molecule                                                                                                                   |

| Figure 2. Bonding and antibonding orbitals                                                                                                       |

| Figure 3. Schematic representation of an OFET6                                                                                                   |

| Figure 4. OFET geometry: (a) Top-gate bottom-contact. (b) Top-gate top-contact. (c)<br>Bottom-gate bottom-contact. (d) Bottom-gate top-contact11 |

| Figure 5. A Branson sonicator for substrate cleaning14                                                                                           |

| Figure 6. A shadow mask for source and drain electrodes of OFETs15                                                                               |

| Figure 7. A schematic of e-beam evaporator system (JEOL Ltd.)16                                                                                  |

| Figure 8. A schematic of thermal evaporator17                                                                                                    |

| Figure 9. An illustration of ALD process of Al <sub>2</sub> O <sub>3</sub> (Ultratech Inc.)                                                      |

| Figure 10. The OFET characterization set-up20                                                                                                    |

| Figure 11. An example of transfer characteristics                                                                                                |

| Figure 12. An example of output characteristics                                                                                                  |

| Figure 13. An example of DC bias stress of an OFET at on-state                                                                                   |

| Figure 14. An example of repeated transfer characteristics                                                                                       |

| Figure 15. An example of measured capacitance at different frequencies under a range of applied DC voltages                                      |

| Figure 16. An example of measured capacitance as a function of frequency at zero bias                                                            |

| Figure 17. An example of capacitance measured at different areas25                                                                               |

| Figure 18. An example of the vertical breakdown field measurement for a capacitor25                                                              |

| Figure 19. A water droplet on (a) Bare and (b) Al <sub>2</sub> O <sub>3</sub> protected CNC:glycerol28                                           |

| Figure 20. Tetralin on (a) Bare and (b) Al <sub>2</sub> O <sub>3</sub> protected CNC:glycerol29                                                  |

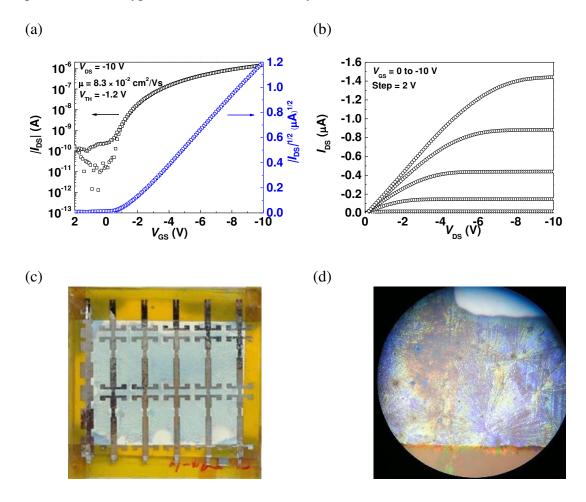

- Figure 22. (a) Transfer characteristics of a D1-type OFET before and after one month in N2. (b) Output characteristics of a D1-type OFET before and after one month in N2. Larger current with larger |V<sub>GS</sub>|, V<sub>GS</sub> from 0 to -10 V, the step is 2 V. (c) Transfer characteristics of a D2-type OFET before and after one month in N2. (d) Output characteristics of a D2-type OFET before and after one month in N2. Larger current with larger |V<sub>GS</sub>|, V<sub>GS</sub> from 0 to -10 V, the step is 2 V. (c) 32. (d) Output characteristics of a D2-type OFET before and after one month in N2. Larger current with larger |V<sub>GS</sub>|, V<sub>GS</sub> from 0 to -10 V, the step is 2 V. (c) 32. (d) 0. (d)

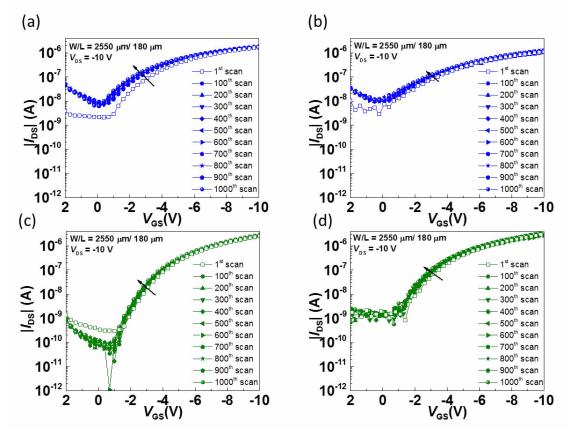

- Figure 25. (a) 1,000 cycles of transfer characteristics measured in N<sub>2</sub> on the D1-type OFET.

(b) 1,000 cycles of transfer characteristic measured at ambient conditions on the D1-type OFET. (c) 1,000 cycles of transfer characteristics measured in N<sub>2</sub> on the D2-type OFET. (d) 1,000 cycles of transfer characteristics measured at ambient conditions on the D2-type OFET.

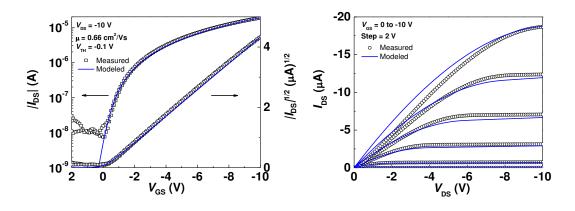

- Figure 29. (a) Fitting of transfer characteristics on a D1-type OFET. (b) Fitting of output characteristics on a D1-type OFET......40

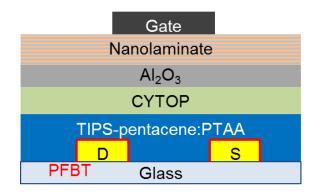

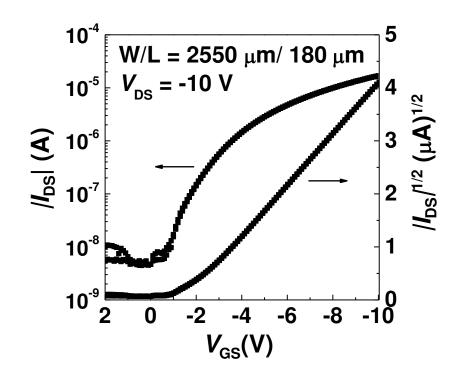

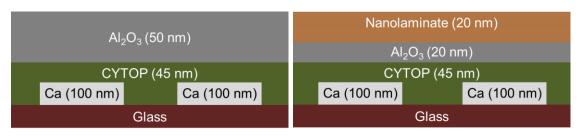

| Figure 31. | The device structure of top-gate OFETs with CYTOP/NL gate dielectric45                                                                                                                                                                                                                                                                                                        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 32. | Transfer characteristics of OFETs with CYTOP/NL gate dielectric47                                                                                                                                                                                                                                                                                                             |

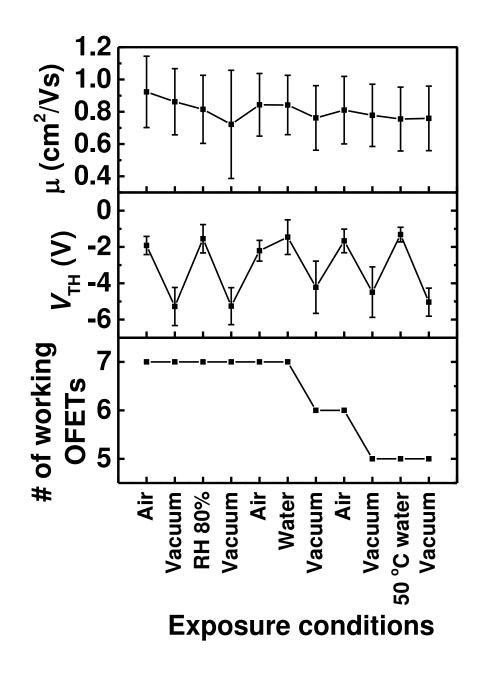

| Figure 33. | Performance of top-gate OFETs exposed to various environments                                                                                                                                                                                                                                                                                                                 |

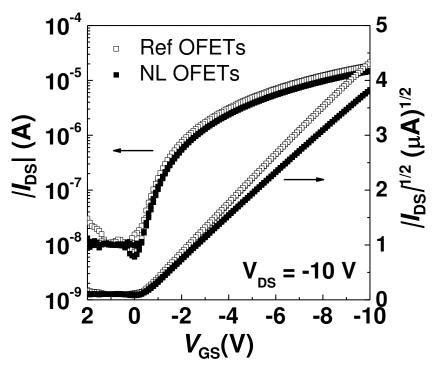

| Figure 34. | Transfer characteristics of Ref- and NL-OFETs with Ag gate49                                                                                                                                                                                                                                                                                                                  |

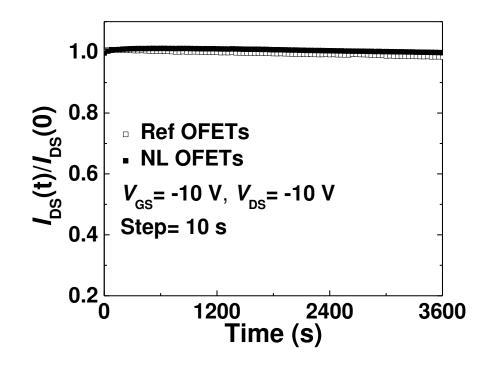

| Figure 35. | DC bias stress in air for 1 h on Ref- and NL-OFETs with Ag gate50                                                                                                                                                                                                                                                                                                             |

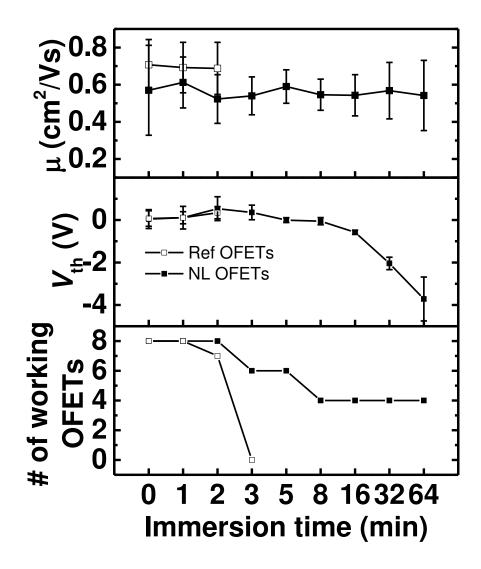

| Figure 36  | 5. Extracted carrier mobility, threshold voltage, and the number of working OFETs                                                                                                                                                                                                                                                                                             |

| Figure 37. | . Ca encapsulated by (a) CYTOP/Al <sub>2</sub> O <sub>3</sub> and (b) CYTOP/NL                                                                                                                                                                                                                                                                                                |

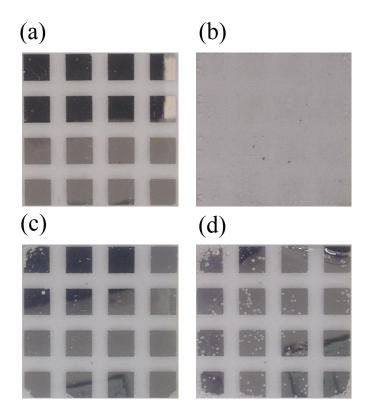

| Figure 38  | 8. Photographs of encapsulated 100 nm Ca samples with (a) Encapsulated by CYTOP/Al <sub>2</sub> O <sub>3</sub> in water at 95 °C for 30 s (b) Encapsulated by CYTOP/Al <sub>2</sub> O <sub>3</sub> in water at 95 °C for 3 min (c) Encapsulated by CYTOP/NL in water at 95 °C for 30 s (d) Encapsulated by CYTOP/NL in water at 95 °C for 3 min                               |

| Figure 39  | 0. (a) Fitting of transfer characteristics on a Ref-OFET. (b) Fitting of output characteristics on a Ref-OFET                                                                                                                                                                                                                                                                 |

| Figure 40  | 0. (a) Fitting of transfer characteristics on a NL-OFET. (b) Fitting of output characteristics on a NL-OFET                                                                                                                                                                                                                                                                   |

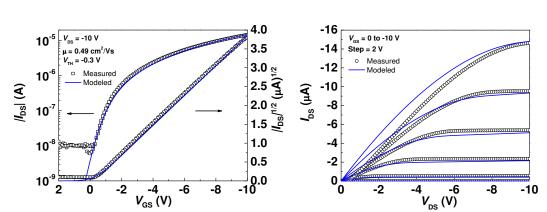

| Figure 41  | . (a) A1, top-gate TIPS-pentacene:PTAA OFETs with bare Au as source/drain electrodes. (b) A2, top-gate TIPS-pentacene:PTAA OFETs with PFBT treated Au as source/drain electrodes and the chemical formula of PFBT. (c) A3, top-gate TIPS-pentacene:PTAA OFETs with Mo(tfd) <sub>3</sub> coated Au as source/drain electrodes and the chemical formula of Mo(tfd) <sub>3</sub> |

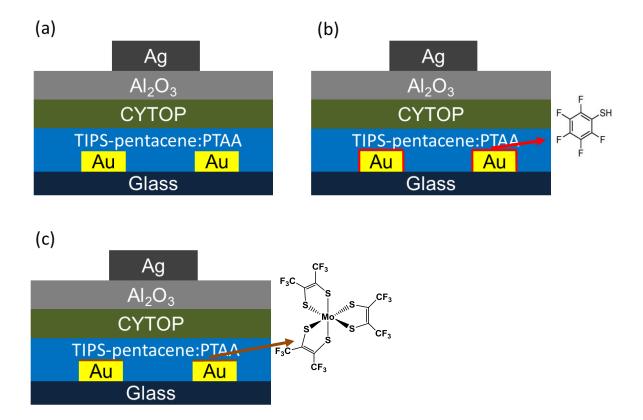

| Figure 42  | . (a) Transfer characteristics of bare Au, PFBT-treated Au, and Mo(tfd) <sub>3</sub> -coated Au OFETs with $W/L = 4500 \ \mu m/190 \ \mu m$ . (b) Transfer characteristics of bare Au, PFBT-treated Au, and Mo(tfd) <sub>3</sub> -coated Au OFETs with $W/L = 4500 \ \mu m/70 \ \mu m$                                                                                        |

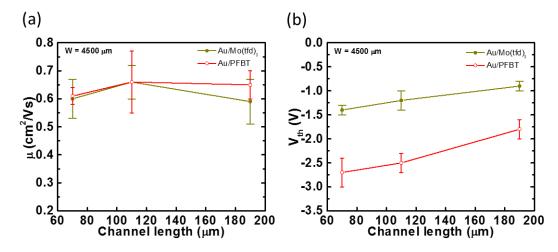

| Figure 43  | . (a) Mobility of PFBT-treated Au and Mo(tfd) <sub>3</sub> -coated Au OFETs at different channel lengths. (b) Threshold voltage of PFBT-treated Au and Mo(tfd) <sub>3</sub> -coated Au OFETs at different channel lengths                                                                                                                                                     |

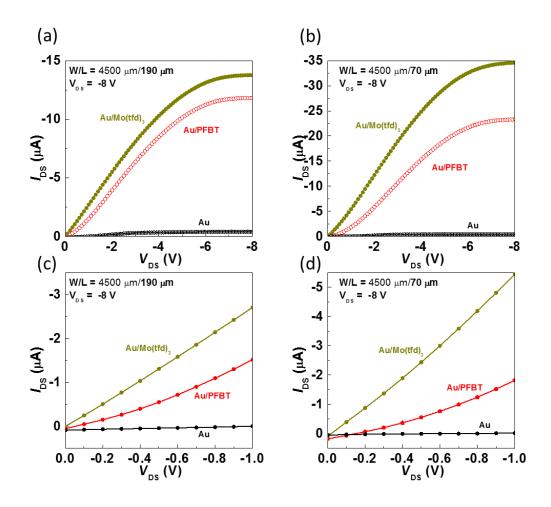

| Figure 44  | (a) On-state output characteristics of bare Au, PFBT-treated Au, and Mo(tfd) <sub>3</sub> -<br>coated Au OFETs with $W/L = 4500 \ \mu m/190 \ \mu m$ . (b) On-state output<br>characteristics of bare Au, PFBT-treated Au, and Mo(tfd) <sub>3</sub> -coated Au OFETs<br>with $W/L = 4500 \ \mu m/70 \ \mu m$ . (c) A zoom-in plot of (a). (d) A zoom-in plot of<br>(b)        |

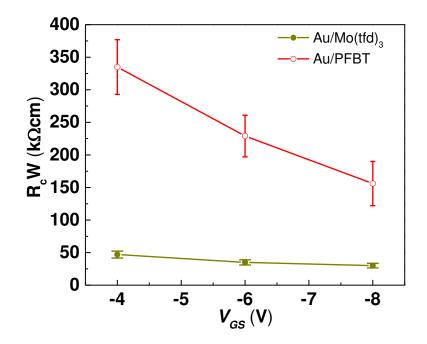

| Figure 45. Normalized contact resistance of PFBT-treated Au and Mo(tfd) <sub>3</sub> -coated Au OFETs at $V_{GS}$ = -4, -6, and -8 V                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

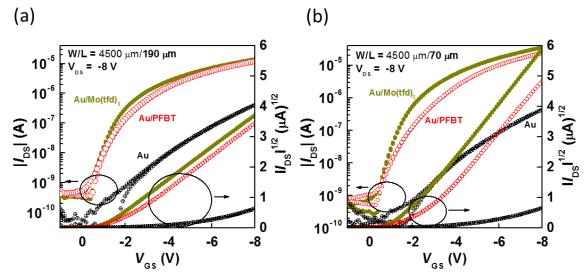

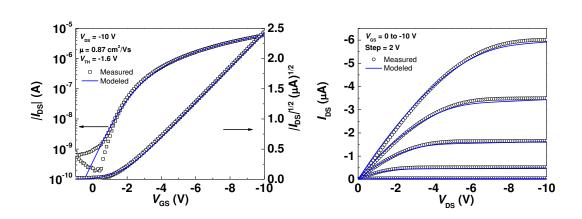

| Figure 46. (a) Fitting of transfer characteristics on an OFET with Au/Mo(tfd) <sub>3</sub> source and drain electrodes. (b) Fitting of output characteristics on an OFET with Au/Mo(tfd) <sub>3</sub> source and drain electrodes |

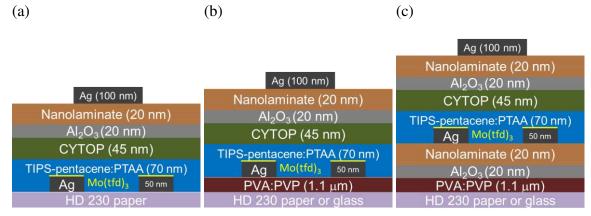

| Figure 47. (a) The OFET structure of type 1. (b) The OFET structure of type 2 and 3. (c) The OFET structure of type 4 and 5                                                                                                       |

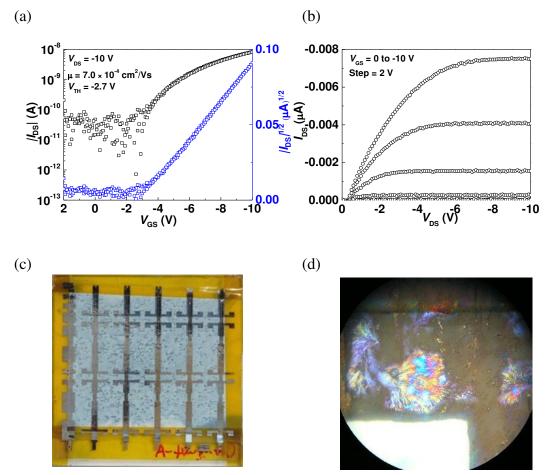

| <ul><li>Figure 48. OFETs on bare HD 230 (a) Transfer characteristics (b) Output characteristics (c) A photograph of OFETs from type 1 (d) A 500× microscope image of an OFET from type 1</li></ul>                                |

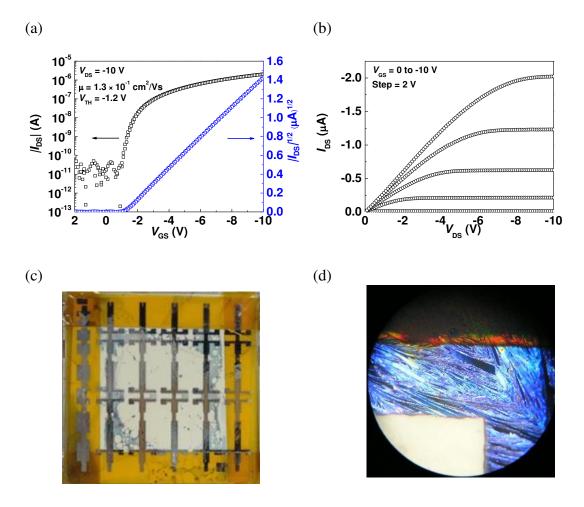

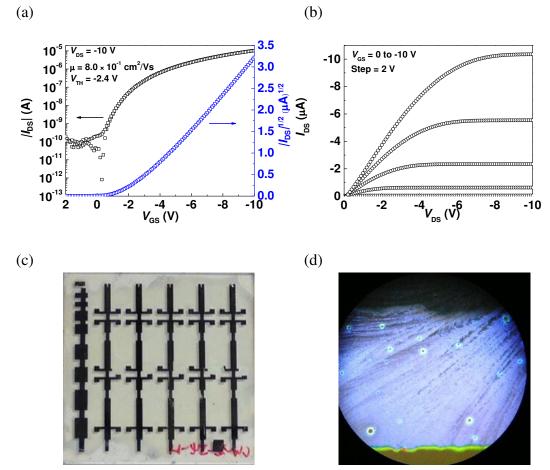

| Figure 49. OFETs on PVA:PVP-coated HD 230. (a) Transfer characteristics. (b) Output characteristics. (c) A photograph of OFETs from type 2. (d) A 500× microscope image of an OFET from type 2                                    |

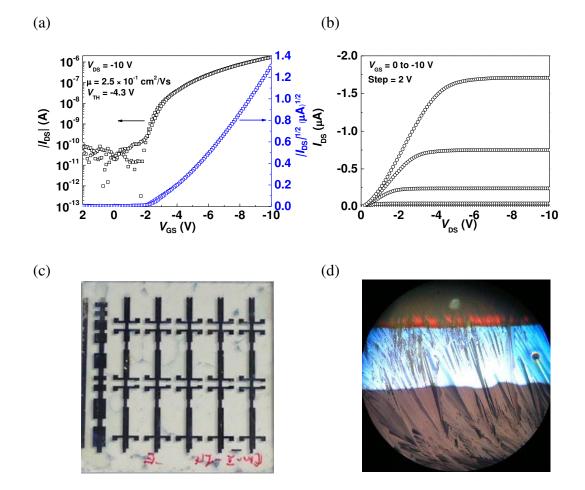

| Figure 50. OFETs on PVA:PVP-coated glass. (a) Transfer characteristics. (b) Output characteristics. (c) A photograph of OFETs from type 3. (d) A 500× microscope image of an OFET from type 3                                     |

| Figure 51. OFETs on PVA:PVP/NL-coated HD 230. (a) Transfer characteristics. (b)<br>Output characteristics. (c) A photograph of OFETs from type 4. (d) A 500×<br>microscope image of an OFET from type 4                           |

| Figure 52. OFETs on PVA:PVP/NL-coated glass. (a) Transfer characteristics. (b) Output characteristics. (c) A photograph of OFETs from type 5. (d) A 500× microscope image of an OFET from type 5                                  |

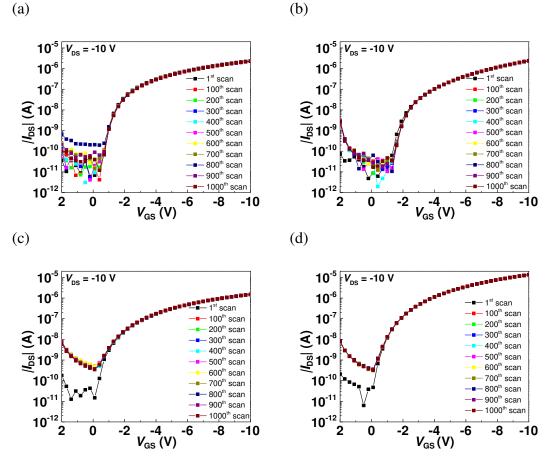

| Figure 53. Comparison of 1,000 consecutive scans of the transfer characteristics of type 2-<br>5 top-gate OFETs                                                                                                                   |

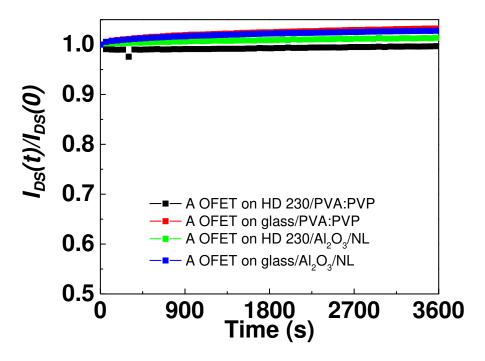

| Figure 54. DC bias stress tests of type 2-5 top-gate OFETs                                                                                                                                                                        |

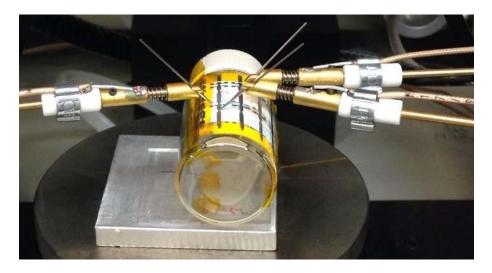

| Figure 55. The set-up of bending tests for OFETs on paper                                                                                                                                                                         |

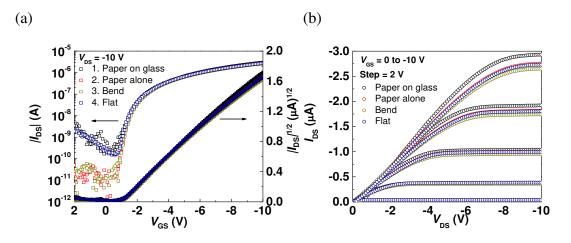

| Figure 56. A type-2 OFET in a bending test. (a) Transfer characteristics. (b) Output characteristics                                                                                                                              |

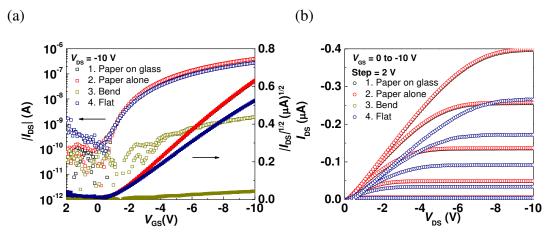

| Figure 57. A type-4 OFET in a bending test. (a) Transfer characteristics. (b) Output characteristics                                                                                                                              |

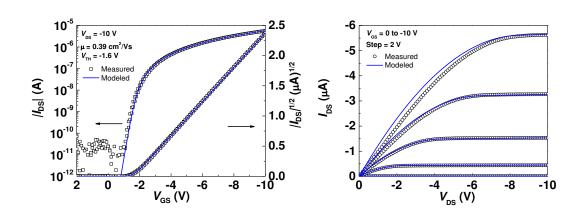

| Figure 58. (a) Fitting of transfer characteristics on a type-2 OFET. (b) Fitting of output characteristics on a type-2 OFET                                                                                                       |

# LIST OF SYMBOLS

| $C_D$           | The capacitance density of depletion region |

|-----------------|---------------------------------------------|

| C <sub>it</sub> | The capacitance density of interface traps  |

| Cox             | The capacitance density of oxide            |

| D <sub>it</sub> | Interface trap density                      |

| γ               | Characteristic exponent                     |

| I <sub>DS</sub> | Drain to source current                     |

| Ion/Ioff        | On/off current ratio                        |

| k               | Boltzmann constant                          |

| λ               | Channel length modulation                   |

| L               | Channel length                              |

| $L_c$           | Characteristic channel length               |

| μ               | Carrier mobility                            |

| q               | Elementary electron charge                  |

| $R_c$           | Contact resistance                          |

| $R_{ch}$        | Channel resistance                          |

| $R_c W$         | Channel width-normalized contact resistance |

| Ron             | On-state resistance                         |

| R <sub>sh</sub> | Sheet resistance                            |

| Т               | Kelvin temperature scale                    |

| Vaa             | Mobility enhancement voltage                |

| V <sub>DS</sub> | Drain to source voltage                     |

| V <sub>GS</sub> | Gate to source voltage                      |

| Vss             | Subthreshold voltage |

|-----------------|----------------------|

| V <sub>TH</sub> | Threshold voltage    |

| W               | Channel width        |

# LIST OF ABBREVIATIONS

| ALD                  | Atomic layer deposition                                         |  |

|----------------------|-----------------------------------------------------------------|--|

| C <sub>8</sub> -BTBT | 2,7-Dioctyl[1]benzothieno[3,2-b][1]benzothiophene               |  |

| CNC                  | CNC Cellulose nanocrysta                                        |  |

| CNF                  | Cellulose nanofiber                                             |  |

| СҮТОР                | Poly [1,1,2,4,4,5,5,6,7,7-decafluor-3-oxa-1,6-heptadiene]       |  |

| CVD                  | Chemical vapor deposition                                       |  |

| DPh-DNTT             | Dinaphtho[2,3- $b$ :2 ',3 ' - $f$ ]thieno[3,2- $b$ ]thiophene   |  |

| EA                   | Electron affinity                                               |  |

| F <sub>4</sub> TCNQ  | Tetrafluoro-tetracyanoquinodimethane                            |  |

| F <sub>6</sub> TCNNQ | 1,3,4,5,7,8-hexafluorotetracyanonaphthoquinodimethane           |  |

| НОМО                 | Highest occupied molecular orbital                              |  |

| IP                   | Ionization potential                                            |  |

| IPA                  | Isopropanol                                                     |  |

| LUMO                 | LUMO Lowest unoccupied molecular orbital                        |  |

| Mo(tfd) <sub>3</sub> | Molybdenum tris-[1,2-bis(trifluoromethyl)ethane-1,2-dithiolene] |  |

| NL                   | Nanolaminate                                                    |  |

| OFET                 | Organic field-effect transistor                                 |  |

| OLED                 | Organic light-emitting diode                                    |  |

| OPV                  | Organic photovoltaic                                            |  |

| OSC                  | Organic semiconductor layer                                     |  |

| PDMS                 | Poly-dimethlysiloxane                                           |  |

| PFBT                 | 2,3,4,5,6-pentafluorothiophenol                                 |  |

| РТАА           | Poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine] |

|----------------|-------------------------------------------------|

| PTCDI          | Perylene tetracarboxylic diimide                |

| PVA            | Polyvinyl alcohol                               |

| PVP            | Polyvinylpyrrolidone                            |

| RH             | Relative humidity                               |

| SS             | Subthreshold swing                              |

| Tetralin       | 1, 2, 3, 4-Tetrahydronaphthalene                |

| TFT            | Thin-film transistor                            |

| TIPS-pentacene | 6, 13-Bis(triisopropylsilylethynyl)pentacene    |

| XPS            | X-ray photoelectron spectroscopy                |

## SUMMARY

With the increasing awareness of environmental impact from electronic waste and increasing demand for flexible electronic devices, novel substrates with both biodegradability and flexibility have been studied in various fields. To develop such electronic devices, organic electronic technology has attracted attention because of its low process temperature at a range of 60 to 100 °C which is compatible with substrates having these two features. Among organic electronic devices, organic field-effect transistors (OFETs) are an important building block because transistors can implement circuits to integrate with other organic electronic devices such as organic light-emitting diodes (OLEDs) and organic photovoltaics (OPVs).

This dissertation reports solution-processed high-performance top-gate OFETs with operational and environmental stability on novel renewable substrates. The first achievement is demonstrating top-gate OFETs with a bilayer CYTOP/Al<sub>2</sub>O<sub>3</sub> gate dielectric on environmentally friendly renewable cellulose nanocrystal (CNC):glycerol substrates. OFETs were fabricated on water soluble CNC:glycerol substrates with a protection layer of Al<sub>2</sub>O<sub>3</sub> by atomic layer deposition. OFETs with that protection layer have better operational and environmental stability compared to that of OFETs on bare CNC:glycerol substrates. The second achievement is reducing contact resistance of top-gate OFETs. By depositing 1.5 nm of Mo(tfd)<sub>3</sub> on source/drain electrodes, contact resistance can be 0.25 of that from contact electrodes using the conventional PFBT treatment. The third achievement is developing a nanolaminate structure comprised of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> to replace Al<sub>2</sub>O<sub>3</sub> in the gate dielectric bilayer in top-gate OFETs to improve their environmental stability while achieving comparable operational stability.

xvi

OFETs with a modified gate dielectric have comparable electrical properties, operational stability, and environmental stability compared to that of OFETs with CYTOP/Al<sub>2</sub>O<sub>3</sub>; furthermore, OFETs with a modified gate dielectric are functioning after storing in hot water at 95 °C for up to 1 h that is much longer than that of OFETs with the original bilayer gate dielectric. The last achievement is presenting top-gate OFETs with modified gate dielectric and reduced contact resistance on cellulose-based paper substrates. OFETs on this type of paper can achieve comparable electrical properties, operational stability, and bending characteristics by the proper choice of a buffer layer coated on top of the paper substrate.

In this dissertation, the development of OFETs on novel substrates have been described, and the future study is suggested.

# CHAPTER 1 INTRODUCTION

### **1.1 Printed electronics**

Electronic waste has been increasing dramatically with economic development for decades. With growing awareness of the environmental impact of electronic waste, the electronics industry is devoting a great deal of attention not only to its profitability but also to establishing environmentally friendly manufacturing processes such as printing techniques.

Electronic devices manufactured by printing techniques are referred as printed electronics. Printed electronic devices can be large, thin, light-weight, and flexible because they are processed from solution at temperatures near room temperature, and they can be fabricated on plastic substrates. The process of printing such electronics has several potential advantages including low production cost, mass production capability, and reduced environmental impact because it potentially avoids using traditional electronics subtractive manufacturing processes such as photolithography and vacuum processes for metallization and etching that consume more energy and materials.

These simplified processes are currently used to produce radio frequency identification tags and printed electrodes for Si solar panels [1, 2]. Novel products such as organic field-effect transistor (OFET) array-based sensors, wearable and bendable displays (electronic papers) using OFETs and organic light-emitting diodes (OLEDs) have been launched in to the market, and devices such as transparent displays and organic photovoltaics (OPVs), using printed electronics, are under development [3]. According to an IDTechEX forecast, the market value of printed electronics is about \$ 30 billion in 2015 and by 2025, is expected to be \$ 70 billion [4].

## 1.2 An introduction to organic field-effect transistors

## 1.2.1 Organic semiconductors

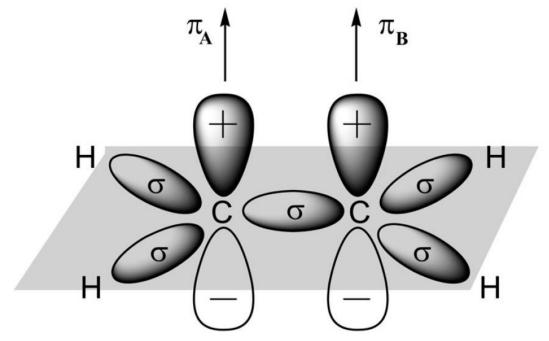

Organic semiconductors are carbon-based organic materials that display semiconducting properties used as the transport layer in OFETs [5]. The semiconducting properties arise from interactions between carbon atoms. When two carbon atoms bind to form a molecule, the orbitals in each carbon atom can hybridize into sp, sp<sup>2</sup>, and sp<sup>3</sup> orbitals. One example of a type of bond that can be formed between two carbon atoms is the bonding in an ethylene molecule. An illustration of such a molecule is presented in Figure 1. In the ethylene molecule, each carbon atom contains one  $p_z$  orbital and three sp<sup>2</sup> hybridized orbitals, which form coplanar  $\sigma$  bonds.

Figure 1. An ethylene molecule.

The linear superposition of wave functions of  $p_z$  electrons leads to the formation of two orbitals in molecules: a bonding orbital, referred to as  $\pi$  (the highest occupied molecular orbital, HOMO), and an antibonding orbital, referred to as  $\pi^*$  (the lowest unoccupied molecular orbital, LUMO), as shown in Figure 2. The  $\sigma$  bonding is stronger than the  $\pi$  bonding, and the electrons participating in this type of  $\pi$  bonding are more delocalized. Electrons on  $\pi$  bonds are generally referred to as  $\pi$  electrons. In organic molecules,  $\sigma$  bonds and  $\pi$  bonds are formed alternatively in structures known as conjugated structures, over which the  $\pi$  electrons are delocalized. Molecules displaying this type of structure are known as conjugated molecules. When molecules coexist in bulk materials, their intermolecular interactions lead to homogeneous broadening of these HOMO-LUMO energy states, forming energy bands. Between the HOMO and LUMO is a gap, which is only an approximation of the fundamental gap, defined as the difference between the ionization potential (IP) and the electron affinity (EA). The IP and EA correspond to the bottom of the conduction band and the top of the valence band. This energy band description of organic semiconductors is analogous to that of inorganic semiconductors.

Figure 2. Bonding and antibonding orbitals.

### **1.2.2 The evolution of OFETs**

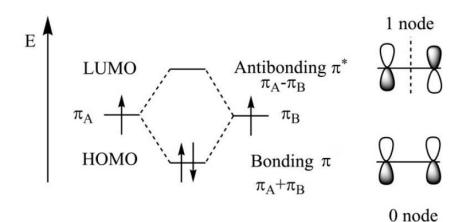

The principle of operation of a field-effect transistor [6] was first proposed by Lilienfeld between 1926 and 1930. The field-effect transistor structure is illustrated in Figure 3: the source and the drain are connected to the two sides of the channel; the gate is isolated from the channel by an insulating layer. By applying the proper voltage on the gate electrode, the capacitor between the gate and the channel can modulate charges inside the channel. However, this idea had not been realized until the first field-effect transistor, a metal-oxide-semiconductor field-effect transistor [7], was demonstrated by Kahng and Atalla in 1960.

In the organic electronic field, the first highly conducting polymer, polyacetylene [8], was discovered in 1977 by Heeger, MacDiarmid, and Shirakawa, who were awarded the Nobel Prize in Chemistry in 2000. This discovery initiated plenty of research on conducting polymers, and the use of organic semiconductors for transistors started in the 1980's. Ebisawa was the first one to use polyacetylene [9] in OFETs with a small current modulation in 1982. The first OFET [10] was realized by Tsumura, Koezuka, and Ando in 1986. They demonstrated the first OFET with a polythiophene thin film. The carrier mobility of the first OFET was of the order of  $10^{-5}$  cm<sup>2</sup>/Vs and the threshold voltage was -13 V. Not only conducting polymers but also small molecules play important roles in organic electronics. The first small-molecule OFET [11], using alpha-sexithienyl film as an active layer, was demonstrated in 1989 by Horowitz *et al.* The carrier mobility was 3.3 ×  $10^{-4}$  cm<sup>2</sup>/Vs, better than the first polymer OFET, and the threshold voltage was only -2 V. Over decades, the carrier mobility of OFETs has made a great progress on both p-channel materials to the range of 10 to 20 cm<sup>2</sup>/Vs [12-15] and n-channel materials to the

range of 1 to 10 cm<sup>2</sup>/Vs [16-18] respectively. Single crystal rubrene-based p-channel OFETs demonstrated carrier mobility on 10.4 to 11.2 cm<sup>2</sup>/Vs [12, 13, 15], and n-channel OFETs also displayed high carrier mobility on small molecules such as PTCDI with 1.7 to 2.1 cm<sup>2</sup>/Vs [16, 17] and C<sub>60</sub> with 2.2 cm<sup>2</sup>/Vs [18]. Furthermore, printed OFETs achieved high average carrier mobility at 16.4 cm<sup>2</sup>/Vs (up to 31.3 cm<sup>2</sup>/Vs) on single crystalline p-channel C<sub>8</sub>-BTBT film [14] and on n-channel polymer P(NDI2OD-T2) with carrier mobility at 0.45 to 0.85 cm<sup>2</sup>/Vs [19]. These evolution makes that OFETs can compete with a-Si and poly-Si thin-film transistors (TFTs).

### 1.2.3 The basic working principle of OFETs

An OFET is an electronic device with three terminals: a gate, a source, and a drain. As shown in Figure 3, an OFET consists of a channel composed of an organic semiconducting material between the drain and the source electrodes and separated from the gate electrode by a gate dielectric layer. The basic principle of an OFET is similar to that of a conventional transistor based on inorganic field-effect transistors. A field-effect transistor is a voltage-controlled electronic device. With a voltage applied between the gate and source electrode ( $V_{GS}$ ), a voltage drop between the gate and source electrodes controls the current flowing through the channel between the source and drain electrodes. In case of an ideal n-channel OFET, when  $V_{GS}$  is below a certain value, known as the threshold voltage  $V_{TH}$ , no current flows between the source and the drain electrodes, and the transistor is turned off. When  $V_{GS}$  is larger than  $V_{TH}$ , current flows between the source and the drain electrodes and the drain, and the transistor is turned on.

Figure 3. Schematic representation of an OFET.

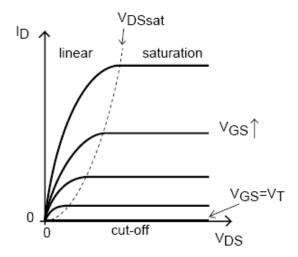

An OFET can display three regimes of operation: the cut-off regime, the linear regime, and the saturation regime. All of the regimes are determined by relationships between the  $V_{GS}$ ,  $V_{TH}$ , and the drain-to-source voltage  $V_{DS}$ . When  $V_{GS} < V_{TH}$ , OFETs are in the cut-off regime, and charges are not induced to form the channel, so drain to source current  $I_{DS}$  equals zero. When  $V_{GS} > V_{TH}$  and  $V_{GS} - V_{TH} > V_{DS}$ , OFETs are in the linear regime, where increased  $V_{GS}$  induces a charge density in the channel, and current  $I_{DS}$  can flow, which increases linearly with  $V_{DS}$ . In this regime the current is given by [20]:

$$I_{DS} = \mu C_{OX} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{1}{2} V_{DS}^{2} \right].$$

(1)

where  $\mu$  is carrier mobility,  $C_{ox}$  is the capacitance density of the gate oxide layer (in our case is gate dielectric layer), W is the channel width, L is the channel length. As  $V_{DS}$  increases, a transition from the linear regime to the so-called saturation regime occurs when the voltage drop between the drain and the gate,  $V_{GS} - V_{DS}$ , at the drain end of the channel equals  $V_{TH}$ . Under this circumstance,  $V_{GS} - V_{DS}$  at the drain end of the channel is barely above the threshold, a condition referred to as "pinch-off." When  $V_{DS} > V_{GS} - V_{TH}$ , the pinch-off point approaches the source end of the channel, and carriers are swept into the pinch-off region at a saturation drift velocity because of the high electric field along

the channel. When  $V_{GS} > V_{TH}$  and  $V_{GS} - V_{TH} \le V_{DS}$ , OFETs operate in the saturation regime, where current  $I_{DS}$  does not increase with  $V_{DS}$  but with  $V_{GS} - V_{TH}$ , and is given by [20]:

$$I_{DS} = \frac{1}{2} \frac{W}{L} \mu C_{OX} \left( V_{GS} - V_{TH} \right)^2.$$

(2)

From the current-voltage relations discussed above, we can investigate many important parameters of OFETs such as the carrier mobility ( $\mu$ ),  $V_{TH}$ , the on/off current ratio, ( $I_{on}/I_{off}$ ), and the contact resistance, ( $R_c$ ). Carrier mobility  $\mu$  and threshold voltage  $V_{TH}$  are extracted in the saturation regime:  $V_{TH}$  is first extracted by linear extrapolation from  $V_{GS} - V_{TH}$  versus the square root of the  $I_{DS}$  plot;  $\mu$  will then be extracted from equation (2) with known channel width W, channel length L, gate dielectric capacitance density  $C_{ox}$ ,  $I_{DS}$ , and  $|V_{GS}| - |V_{TH}|$ . On/off current ratios  $I_{on}/I_{off}$  can be calculated by measuring the off-state  $I_{DS}$  and maximum on-state  $I_{DS}$ . Contact resistance  $R_c$  can be extracted in the linear regime of OFETs with different W/L ratios by using the transfer length method. According to this method, the on-state resistance  $R_{ON}$  is extracted as  $V_{DS}$ approaches 0 V using the following expression [21]:

$$R_{ON} = \frac{\partial V_{DS}}{\partial I_{DS}}\Big|_{V_{DS} \to 0} = R_{ch} + 2R_c = R_{sh} \frac{L}{W} + 2R_c, \qquad (3)$$

where  $R_{ch}$  is the channel resistance and  $R_{sh}$  is the sheet resistance of the channel. The ordinate in the plot of  $R_{ON}$  vs. L when L equals zero corresponds to  $2R_c$ . High  $\mu$ , high  $I_{on}/I_{off}$ , low  $|V_{TH}|$ , and low  $R_c$  are the most common indicators of a high-performance OFET.

### 1.2.4 More parameters and modeling of OFETs

In addition to the basic working principal of OFETs, more parameters are taken into account when it comes to the real world. The first thing will be the subthreshold slope (SS) coming from the leakage current from the source to the drain when gate voltage is below but close to the threshold voltage. SS can be extracted from the transfer characteristic and is defined as:

$$SS \equiv \frac{dV_{GS}}{d(\log(I_{DS}))} \tag{4}$$

and it is approximately [22]:

$$SS \approx ln 10 \frac{kT}{q} \left[ 1 + \frac{C_D + C_{it}}{C_{OX}} \right]$$

(5)

where *k* is Boltzmann constant, *T* is temperature in Kelvin scale, *q* is elementary electron charge,  $C_{ox}$  is the capacitance density of the gate oxide layer (in our case is gate dielectric layer),  $C_D$  is the capacitance of the semiconductor depletion region, and  $C_{it}$  is the capacitance of interface traps equals to  $qD_{it}$  where  $D_{it}$  is the interface trap density. Since there is no depletion region in OFETs,  $C_D$  is zero in equation (5) and the interface trap density can be extracted from equation (5) and given as [22]:

$$D_{it} \approx \left[\frac{qSSlog(e)}{kT} - 1\right] \frac{C_{OX}}{q} \tag{6}$$

In reality, equation (3) and (4) cannot completely describe the current-voltage characteristics of OFETs, for examples: 1) drain current will still increase while OFETs are in the saturation region, therefore the transition from triode region to saturation region and channel length modulation should be considered; 2) the transition below and above threshold will not always be abrupt, therefore subthreshold swing should be considered, too; 3) contact resistance is not negligible on OFETs, therefore the output characteristics

may not be linear in linear region. There have been several compact models consistent with equation (3) and (4) to describe the current-voltage characteristics of OFETs. Three representative compact models were selected and discussed in Kim et. al. [23]: Marino et. al. [24, 25] focusing on a practical below-to-above threshold transition and linear-tosaturation transition by a small number of parameters, Estrada et. al. [26, 27] focusing on the use of a power-law relationship between mobility and gate overdrive voltage, and Li et. al. [28] focusing on the potential barrier between grains in a polycrystalline organic film. Based on the emphasized aspect, the model of Marion et. al. is chosen to fit OFET characteristics here. In their models, empirical fitting parameters are mostly eliminated, and developed models are also in close correspondence to physicals, parametric, and limiting models for current-voltage and mobility characteristics. The mobility is assumed to follow a power-law dependence featuring the characteristic exponent  $\gamma$  and the mobility enhancement voltage  $V_{aa}$ . The choice of a power-law mobility is related to the charge-transport through localized states that have exponential density-of-states. By applying modified carrier mobility in the derivation (not discussed here) of currentvoltage equations of OFETs, the final current-voltage equation is given as:

$$I = \frac{W}{L} \frac{\mu_0}{V_{aa}^{\gamma}} C_{OX} \frac{[f(V_G, V_D)]^{\gamma+2} - [f(V_G, V_S)]^{\gamma+2}}{\gamma+2} (1 + \lambda |V_D - V_S|)$$

(7)

where  $\lambda$  is the channel length modulation parameter, and the effective gate overdrive function is given by:

$$f(V_G, V) = V_{SS} ln \left\{ 1 + e \left[ -\frac{(V_G - V_T) - V}{V_{SS}} \right] \right\}$$

(8)

where  $V_{SS}$  is the subthreshold voltage.

Theories used in these models are based on charge drift in the presence of taildistributed traps (TDTs) [29] and variable range hopping (VRH) [30]. TDTs assumes a significant portion of charge is localized in the exponential tail, and the mobile charge attributed to the conduction or the valence band is only a portion of the total charge, and the effective mobility becomes proportional to the ratio of the free-to-trapped charge. VRH does not separate between free and localized charges, and excess charge is induced in the states by the gate bias voltage in terms of Gauss' law. Therefore, both theories define the dependence of mobility on gate bias voltage.

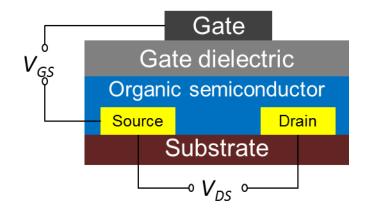

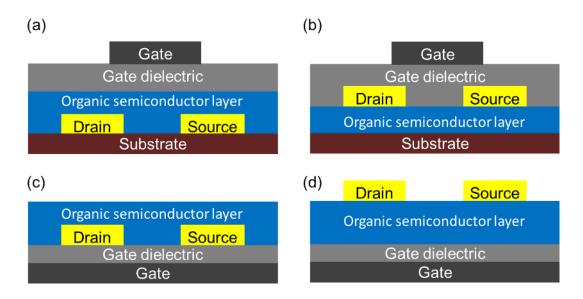

#### **1.2.5 OFET geometry**

As shown in Figure 4, OFETs can be realized in two main geometries: bottomand top-gate geometries. In the so-called bottom-gate geometry the OFET is comprised of a gate electrode at the bottom of a transistor on top of which is a gate dielectric layer, an organic semiconductor layer, and source/drain electrodes. In the top-gate geometry the OFET is comprised of source/drain electrodes at the bottom, an organic semiconductor layer on top, a gate dielectric layer, and a gate electrode. The bottom-gate OFET geometry is the most commonly used, in part because it prevents potential damage to the organic semiconductor layer that may occur if a gate dielectric is solution-processed onto it [31]. However, bottom-gate OFETs have an organic semiconductor layer exposed to the environment, which often leads to reduced environmental and operational stability. To improve the stability of bottom-gate OFETs in air or harsher environments such as high temperature and humidity, either an environmental barrier layer [32] that protects the organic semiconductor layer or a stable organic semiconductor layer [33] that can withhold damage from the environment must be used.

Figure 4. OFET geometry: (a) Top-gate bottom-contact. (b) Top-gate top-contact. (c) Bottom-gate bottom-contact. (d) Bottom-gate top-contact.

In contrast to bottom-gate OFETs, top-gate OFETs, in which a gate dielectric is deposited on top of the organic semiconductor layer, can improve environmental stability in air or harsher environments without an extra protection layer. To prevent damage to the organic semiconductor layer when gate dielectric forming on top of it, fluorinated polymers such as CYTOP have been used. CYTOP is highly chemically stable and hydrophobic, and it dissolves in fluorinated solvents that will not dissolve most organic semiconductor materials. In Hwang *et al.*, top-gate OFETs with a bilayer CYTOP/Al<sub>2</sub>O<sub>3</sub> gate dielectric have shown high environmental and operational stability in air for over two years and under oxygen plasma treatment for five min at 750 W [34]. These OFETs also have displayed recoverable performance on  $\mu$  and  $V_{TH}$  after systematic investigation under exposure to air, oxygen plasma, and water immersion [35].

An important feature of OFET geometries are substrates. The conventional substrates of OFETs and organic electronics are rigid materials such as Si and glass substrates. However, flexible, foldable, and even renewable substrates have been developed for various applications and purposes. Among these substrates, paper is the preferred substrate because it is low-cost, recyclable, and produced from natural feedstock [36] (i.e., it is derived from trees). However, paper is porous, introducing a challenge for solution-based fabrication of organic electronics on top of it; and compared to glass or plastic, this substrate limits the performance of organic electronics. In contrast to traditional cellulosic material such as paper, cellulose nanocrystal (CNC), an emerging material also derived from trees, has been an attractive new material because it can be processed into freestanding films with low surface roughness, good transparency, a low coefficient of thermal expansion, and high thermal stability [37]. Several reports have demonstrated that the performance of organic electronic devices such as OPVs [38, 39] and OLEDs [40] on CNC substrates is comparable to the performance of such devices on glass or plastic substrates.

#### **1.3 Organization of this dissertation**

Chapter 1 introduces printed electronics and OFETs, and Chapter 2 describes the experimental methodology including details of OFET fabrication and equipment used for that. Chapter 3 describes stable low-voltage operation top-gate OFETs on CNC:glycerol. Chapter 4 describes top-gate OFETs using modified bilayer gate dielectric with comparable performance to achieve better environmental stability. Chapter 5 describes a method to reduce contact resistance of OFETs. Chapter 6 describes OFETs on paper. Chapter 7 provides conclusions and future work.

## **CHAPTER 2**

# **EXPERIMENTAL METHODOLOGY**

## **2.1 Device fabrication**

This chapter describes fabrication and measurements for OFETs and capacitors. In the first part of this chapter, an overview will introduce process details of organic electronics, and the differences with conventional lithography will be described; evaporation methods will also be introduced such as e-beam evaporation, thermal evaporation, and atomic layer deposition. In the second part of this chapter, OFET measurements, the measurement system and frequently used characterization will be described. In the third part of this chapter, capacitor measurements will be described.

#### 2.1.1 Overview

For organic device fabrication, additive process is widely used because organic materials usually cannot survive in conventional semiconductor processes such as solvent cleaning, wet/dry etching, chemicals for lithography, etc. In the process used in this dissertation, glass substrates for OFET fabrication were only cleaned at the beginning of the fabrication; for novel substrates other than glass, the cleaning step was skipped to avoid potential damages on substrates. The cleaning steps consisted of putting glass substrates in acetone, distilled water, and isopropanol in a sonicator for five min in each step. The set-up for the cleaning process is shown in Figure 5. After substrate cleaning, source/drain electrodes were patterned through shadow masks. The source/drain electrodes were evaporated by either e-beam evaporation or thermal evaporation. A picture of shadow masks is shown in Figure 6. With shadow masks attached on substrates, metal was only deposited on the open area. After source/drain electrode deposition, contact treatment can be applied at this stage to decrease the energy barrier between an organic semiconductor layer and source/drain electrodes. On top of the source/drain electrodes was the organic semiconductor layer. The preparation of semiconductor layers in this study used spin-coating and then annealing of the organic semiconductor layer.

Figure 5. A Branson sonicator for substrate cleaning.

The organic semiconductor layer was followed by a bilayer gate dielectric layer. The bilayer gate dielectric layer was comprised of a spin-coated and annealed polymer dielectric, CYTOP, and a metal-oxide dielectric layer deposited by atomic layer deposition (ALD) at 110 °C. The last step was the gate electrode deposition on top of the gate dielectric. The gate electrodes were deposited by thermal evaporation because ebeam evaporation may damage the organic semiconductor layer. Patterning of gate electrodes was also done by shadow masks.

For capacitor fabrication, everything was the same except for the organic semiconductor layer. The purpose of capacitor fabrication was to measure the capacitance

density of the OFET gate dielectric layer and to evaluate the quality of the gate dielectric layer. Therefore, layers of structure from the bottom to the top were bottom electrodes, bilayer gate dielectric, and top electrodes. Electrodes were patterned through shadow masks and bilayer dielectric was first spin-coated and then deposited by ALD.

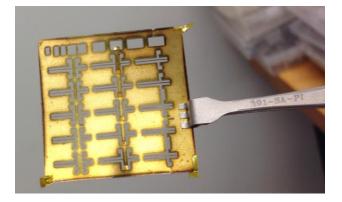

Figure 6. A shadow mask for source and drain electrodes of OFETs.

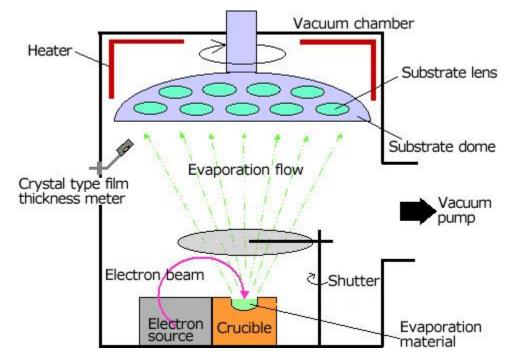

### 2.1.2 Electron beam evaporation

The electron beam (e-beam) evaporator used in this study for source/drain electrode deposition was a Denton Explorer. An e-beam system uses high voltage (kV) electron beam to bombard materials under high vacuum (10<sup>-5</sup> to 10<sup>-7</sup> torr) with a water cooling system underneath the source pocket [41]. The electron beam is generated by an electron gun using the thermionic emission of electrons produced by an incandescent filament. The direction of the electron beam is controlled by a magnetic field. Materials are heated up to the melting point for evaporation by the bombardment. During the deposition process, the material is heated regionally only at the area bombarded by electron beam, and the rest of the source is still solid. Therefore, this method is more sufficient, applicable for high melting point metals and oxides compounds, and creates less contamination. However, X-rays generated during the electron beam hitting the sources may cause device damage. That is the reason that the e-beam system is only used

for source/drain electrode fabrication before the formation of the organic semiconductor layer. A schematic of an e-beam system is shown in Figure 7.

Figure 7. A schematic of e-beam evaporator system (JEOL Ltd.) [42].

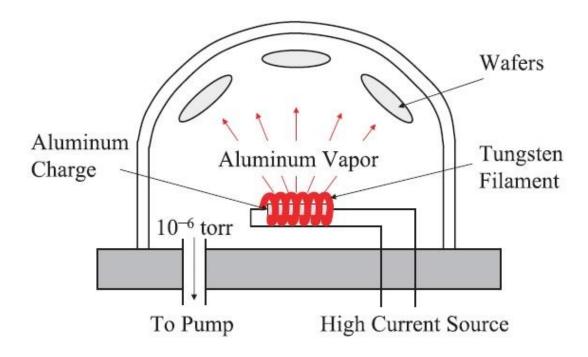

### 2.1.3 Thermal evaporation

The thermal evaporation system used in this study is a SPECTROS 200 system from Kurt J. Lesker. It is connected to an MBraun glovebox avoiding exposure to the atmosphere. Typical vacuum condition of the deposition is below 10<sup>-7</sup> torr. Thermal evaporation is a resistive heating technique using a tungsten boat carrying a material [41]. The material is heated by the heat generated from injecting current through the tungsten boat. After the material reaches its melting point, it vaporizes and deposits on targeted samples. The advantage of this technique is that it won't generate X-rays during the deposition, so it will not cause potential damage to devices. Therefore, thermal evaporation can be used in not only source/drain electrode deposition, but also for the deposition of the gate electrode after organic material formation on the organic electronic devices. However, it cannot use high melting point materials because heating up the whole tungsten boat is not efficient for raising the temperature above 1000 °C, and potential contamination is a possibility because parts other than the materials are also heated. A schematic of a thermal evaporation system is shown in Figure 8.

Figure 8. A schematic of thermal evaporator [41].

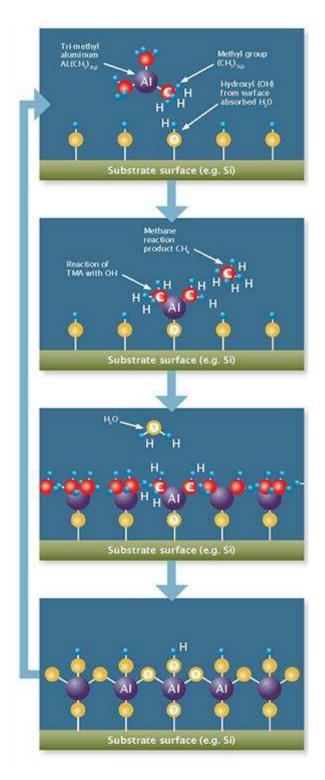

# 2.1.4 Atomic layer deposition

The atomic layer deposition (ALD) system used here is a Savannah S200 ALD from Ultratech Inc. (Cambridge NanoTech Inc.) ALD provides precise control down to the atomic scale. The principle of atomic layer deposition is similar to chemical vapor deposition (CVD) except the ALD reaction breaks the CVD reaction into two halfreactions, keeping the precursor materials separate during the reaction [41]. The sequence of ALD starts from a pulse of water vapor and then a pulse of a metal-organic precursor. An example of ALD for Al<sub>2</sub>O<sub>3</sub> deposition is shown in Figure 9. A layer of Al<sub>2</sub>O<sub>3</sub> forms as described: In the pulse of water vapor, water adsorbs on the substrate surface and then forms a hydroxyl group (Figure 9 (a)); another pulse of precursor, in this case trimethyl aluminum (Al(CH<sub>3</sub>)<sub>3</sub>), flows in and interacts with the hydroxyl group to have bonding between an oxygen atom and an aluminum atom, and a methyl group forms a bonding with hydrogen from a hydroxyl group to yield a by-product, methane (Figure 9 (b)). After a layer of Al<sub>2</sub>O<sub>3</sub> forms, another pulse of water vapor is introduced (Figure 9 (c)), this time water adsorbs on aluminum atoms, and oxygen atoms bonded with aluminum atoms replace all methyl groups connected to aluminum (Figure 9 (d)). Repeated cycles work as described above to form a dielectric.

Figure 9. An illustration of ALD process of Al<sub>2</sub>O<sub>3</sub> (Ultratech Inc.) [43].

# **2.2 OFET measurements**

The measurement set-up of OFET characterization uses a Signatone probe station in a MBraun glovebox. The probe station is connected to an Agilent E5272A system for electrical characterization and to an Agilent 4284A for capacitance characterization. Agilent systems are connected to a computer for remote control by LabVIEW programs. A picture of this measurement set-up is shown as Figure 10.

Figure 10. The OFET characterization set-up.

Characterization of OFETs used in this study includes transfer characteristics, output characteristics, DC bias stress measurements, and repeated scans of transfer characteristics.

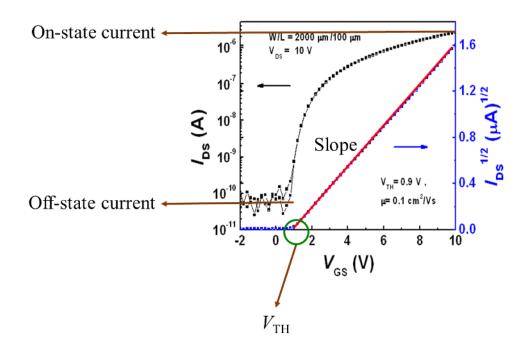

# 2.2.1 Transfer characteristics

The transfer characteristics are drain-to-source current as a function of gate voltage at a certain drain-to-gate voltage. An example is shown in Figure 11. OFETs are

usually measured from off-state (low gate voltage) to on-state (high gate voltage) then on-state to off-state to observe if fabricated OFETs have hysteresis, and the quality of OFETs can be determined. The carrier mobility can be extracted by putting the slope of the linear fitting of the square root of drain current as a function of gate voltage into Equation (2). From the same linear fitting, the threshold voltage can be extracted by the intercept of the gate voltage axis. The on/off current ratio can be extracted by dividing on-state drain current by off-state drain current.

Figure 11. An example of transfer characteristics.

### 2.2.2 Output characteristics

The output characteristics are drain-to-source current as a function of drain-tosource voltage at different gate-to-source voltage. An example is given in Figure 12. From this plot, on-resistance can be extracted by the slope of tangents from each curve at a given drain-to-source voltage as described in Equation (3). With different channel widths at a channel length, different on-resistance changes linearly with different channel widths. The intercept of resistance when channel width equals to zero represents the sum of the contact resistance of a source and a drain.

Figure 12. An example of output characteristics.

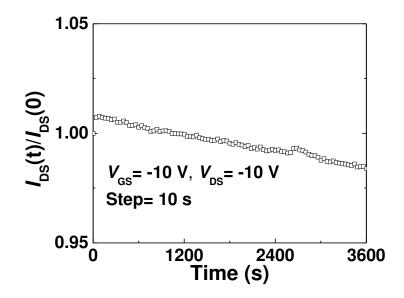

## 2.2.3 DC bias stress

The DC bias stress test here is to monitor the drain-to-source current variation at on-state. It is an indicator of the operational stability of OFETs. An example of this characteristic is shown in Figure 13.

Figure 13. An example of DC bias stress of an OFET at on-state.

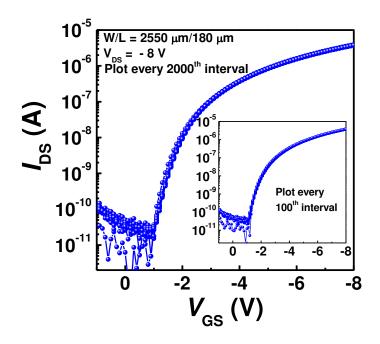

# 2.2.4 Repeated transfer characteristics

The repeated transfer characteristic is another indicator of operational stability of OFETs. It is usually conducted continuously from off-state to on-state to observe if OFETs are stable or degraded during repeated scans.

Figure 14. An example of repeated transfer characteristics.

### **2.3 Capacitor measurements**

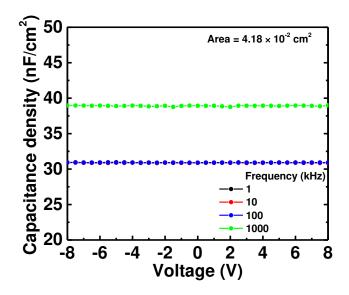

To investigate the quality of capacitors, there are four frequently used measurements to evaluate capacitors. The first measurement is to measure capacitance as a function of applied DC voltage at several given frequencies as shown in Figure 15. In this case, the stability of capacitance will be evaluated at a range of DC biases with several given frequencies.

Figure 15. An example of measured capacitance at different frequencies under a range of applied DC voltages.

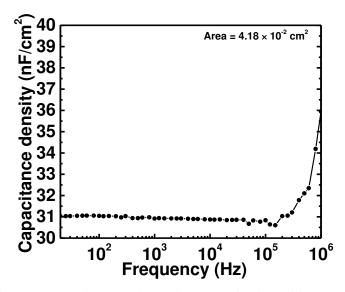

In Figure 16, the second measurement is to measure capacitance as a function of frequency at zero bias. In this case, the quality of a capacitor will be evaluated because the capacitance is usually unstable at high frequency.

Figure 16. An example of measured capacitance as a function of frequency at zero bias.

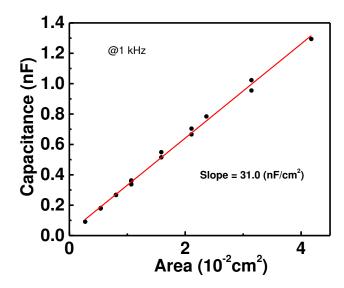

In Figure 17, the third measurement is to measure capacitors with various areas at a given frequency and a given bias. In this case, capacitance will be in a linear relation

with areas of capacitors, and the slope of this linear relation is capacitance density. With this value extracted, carrier mobility can be calculated through Equation (3) in page 6.

Figure 17. An example of capacitance measured at different areas.

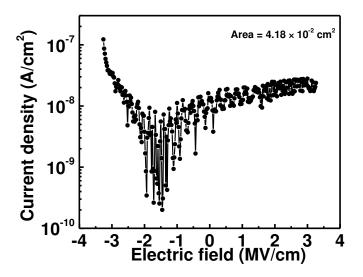

In Figure 18, the last measurement is the current density of a capacitor as a function of applied electric field. It provides a direct observation on a capacitor for its breakdown electric field which is an indicator of the quality of a dielectric.

Figure 18. An example of the vertical breakdown field measurement for a capacitor.

## **CHAPTER 3**

# **OFETS ON CELLULOSE NANOCRYSTAL SUBSTRATES**

#### **3.1 Introduction**

OFETs have the potential for low-cost fabrication and flexibility over large areas which make them important building blocks for the development of flexible electronic applications. With growing awareness of the environmental impact of electronic waste, there is a need for new substrates for emerging flexible organic printed electronic technologies with a small environmental footprint. The replacement of conventional substrates, such as glass and plastic, with substrates made from abundant and environmental-friendly materials can make the recycling and/or disposal of new engineered products potentially more efficient and less polluting. Although OFETs are typically fabricated on glass or plastic substrates, paper would be the preferred substrate [36] because of its low cost, recyclability, and the use of natural materials derived from renewable feedstock. However, the fabrication of electronic components on paper presents several challenges resulting from the high porosity of traditional cellulosic materials, their high surface roughness, and complex surface chemistry. Consequently, performances of OFETs fabricated from solution on paper continue to be limited compared to devices fabricated on glass or plastic substrates.

In recent years, cellulose nanomaterials derived from sustainable feedstock, such as cellulose nanofibers (CNFs) and CNCs, have emerged as an attractive new class of materials for flexible electronic applications because they can be processed into freestanding and flexible films that display low surface roughness, good transparency, a low coefficient of thermal expansion and high thermal stability [37]. Several reports exist on organic electronic devices such as OFETs [44-48], OPVs [38, 39, 49-51], and OLEDs [40, 52-55] fabricated on cellulose nanomaterial substrates. OFETs fabricated on CNFbased substrates have shown good flexibility and transparency [44, 45], and a majority of studies focused on processes using evaporation [46-48] and ink-jet printing [56, 57]. In addition to be a substrate, cellulose materials were also employed as a gate dielectric [58-62] for OFETs. To date, only a few reports demonstrated stability tests [44] and improvements are still needed in lowering the threshold voltage and increasing carrier mobility using cellulose as a part of the OFETs. Solution-processed OFETs containing cellulose with a low threshold voltage [63] and a high carrier mobility with environmental stability remains a goal to be achieved.

In this chapter, stable low-voltage operation top-gate OFETs are demonstrated. OFETs were fabricated on water soluble CNC:glycerol substrates protected by ALDgrown Al<sub>2</sub>O<sub>3</sub>. The carrier mobility of fabricated OFETs has an average value of 0.11 cm<sup>2</sup>/Vs and a highest value of 0.23 cm<sup>2</sup>/Vs. Operational and environmental stability will be demonstrated. For comparison, OFETs on bare CNC:glycerol were also fabricated and measured. The OFETs structure used here was reported by our group [34, 35].

#### **3.2 Design of experiments**

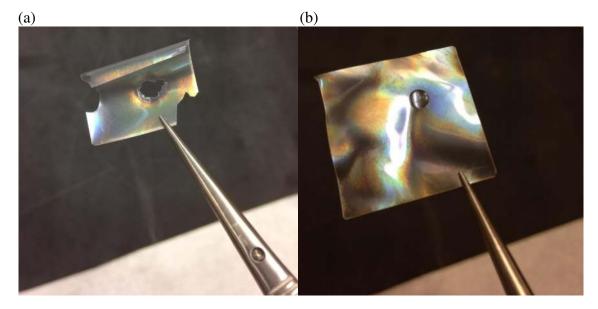

The advantage of this recyclable substrate is its water solubility at room temperature. However, it is also its disadvantage because a droplet of water can form a hole on bare CNC:glycerol within seconds as shown in Figure 19 (a). A proposed solution is to deposit a layer of ALD-grown Al<sub>2</sub>O<sub>3</sub> on top of CNC:glycerol to protect the substrate, and Figure 19 (b) shows a droplet of water staying on the protected CNC:glycerol without dissolving it to make a hole. After deciding to add a protection layer for potential damages, the wettability of tetralin, the solvent we used for the organic semiconductor, was verified by conducting contact angle measurements of tetralin on bare CNC:glycerol and CNC:glycerol with ALD-grown Al<sub>2</sub>O<sub>3</sub>. The results in Figure 20 show that tetralin wets on both CNC:glycerol and CNC:glycerol with ALD-grown Al<sub>2</sub>O<sub>3</sub>; that confirms the film formation on this novel substrate.

Figure 19. A water droplet on (a) Bare and (b) Al<sub>2</sub>O<sub>3</sub> protected CNC:glycerol.

In this section, top-gate OFETs with a bilayer CYTOP/Al<sub>2</sub>O<sub>3</sub> gate dielectric will be characterized. These OFETs used a solution-processed semiconductor channel layer made of a blend of TIPS-pentacene and PTAA fabricated on recyclable CNC:glycerol substrates. These OFETs exhibited low operating voltage between 0 to -10 V, low threshold voltage in the range of -2 V, an average field-effect mobility of 0.11 cm<sup>2</sup>/Vs, and good shelf and operational stability in ambient. In addition to protecting substrates from solution process, the barrier layer of Al<sub>2</sub>O<sub>3</sub> was grown by ALD directly onto the CNC:glycerol substrates, which was also expected to improve the operational stability in ambient air. This same layer was reported contributing stable OFETs in air, therefore it may protect the organic semiconductor film from moisture and other chemicals that can either permeate through or diffuse out of the substrate.

(a)

(b)

Figure 20. Tetralin on (a) Bare and (b) Al<sub>2</sub>O<sub>3</sub> protected CNC:glycerol.

#### **3.3 Device fabrication**

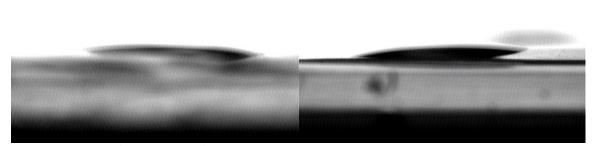

OFETs were fabricated in top-gate bottom-contact geometry, as shown in Figure 21. First, CNC:glycerol substrates were prepared as described in Zhou *et. al.* [38]. OFETs fabricated on bare CNC:glycerol substrates, will be referred to hereafter as D1 devices. OFETs fabricated on CNC:glycerol substrates coated with 300 cycles of ALD-grown Al<sub>2</sub>O<sub>3</sub> at 110 °C (Savannah 100 ALD system, Cambridge Nanotech Inc.), will be referred to as D2 devices.

D1- and D2-type OFETs were fabricated as follows: a 2 mm-thick layer of PDMS (Gelest OE 41 with 1:1 weight ratio) was cast onto 3.8 cm by 3.8 cm glass substrates to hold the CNC:glycerol substrates. CNC:glycerol substrates were attached on top of the PDMS film and secured by Kapton tape at the edges, and 50 nm-thick Au source/drain electrodes were deposited through a shadow mask using an electron-beam deposition system (Denton Explorer), at a deposition rate of 1.0 Å/s and an initial pressure of 9.0 ×  $10^{-7}$  Torr. A TIPS-pentacene (Sigma Aldrich) and PTAA (Sigma Aldrich) blend solution was used as the organic semiconducting layer. The (1:1 weight ratio) TIPS-

pentacene:PTAA solution was dissolved in anhydrous tetralin, (Sigma Aldrich) at a concentration of 30 mg/ml. The TIPS-pentacene:PTAA blended solution was spin-coated at 500 rpm for 10 s (acceleration of 500 rpm/s) and ramped to 2,000 rpm for 20 s (acceleration of 1,000 rpm/s) to yield a ca. 70 nm-thick layer [64]. Spin coated films were then thermally annealed at 100 °C for 15 min on a hot plate in a N<sub>2</sub>-filled glove box. The preparation of a bilayer gate dielectric was starting from diluting CYTOP (Asahi Glass, CTL-809M) with a solvent (Asahi Glass, CTL-SOLV180) to a concentration of 2% by volume.

Figure 21. (a) Cross-section of OFETs on bare CNC:glycerol substrates, D1. (b) Cross-section of OFETs on CNC:glycerol substrates with an Al<sub>2</sub>O<sub>3</sub> barrier layer, D2. (c) Chemical structures of the compounds and polymers used in the OFETs.

A layer of CYTOP was spin-coated on top of the organic semiconducting layer at 3,000 rpm for 60 s (acceleration of 10,000 rpm/s) to yield a ca. 35 nm-thick layer [64]. Samples were then thermally annealed at 100 °C for 10 min on a hot plate in a N<sub>2</sub>-filled

glove box. After that, 500 cycles of ALD-grown Al<sub>2</sub>O<sub>3</sub> were deposited at 110 °C to yield a ca. 40 nm-thick layer [64]. Later, 100 nm-thick Ag gate electrodes were deposited through a shadow mask in a thermal evaporator (Kurt J. Lesker, SPECTROS) with initial pressures below  $1.0 \times 10^{-6}$  Torr and at an average deposition rate of 1.0 Å/s.

#### **3.4 Device characterization**

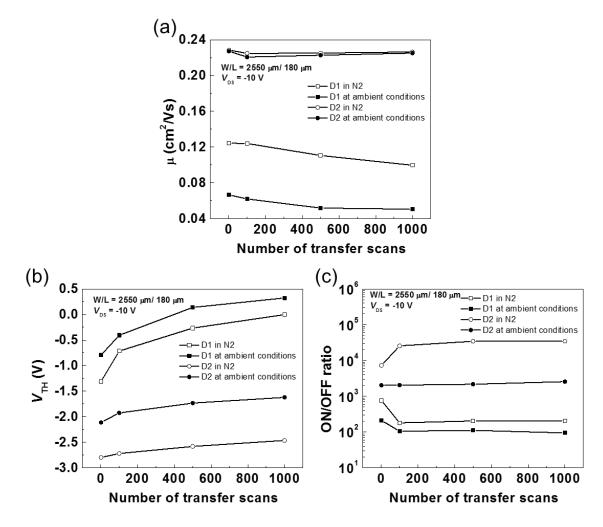

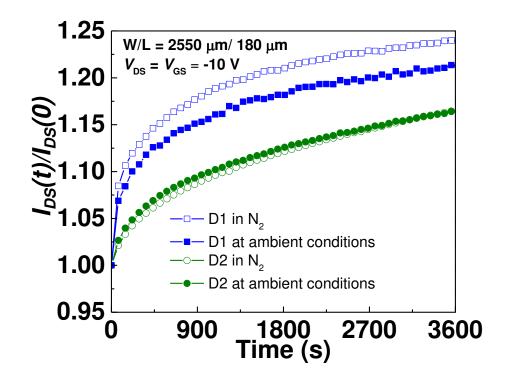

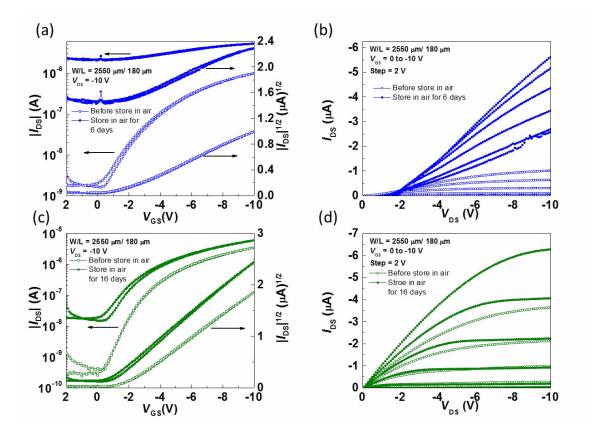

D1- and D2-type OFETs were characterized in a N<sub>2</sub>-filled glove box (O<sub>2</sub> and H<sub>2</sub>O < 0.1 ppm, 25 °C) and at ambient conditions (25 °C and 20% to 40% RH) using an Agilent E5272A source/monitor unit. The operational stability was investigated by performing 1,000 continuous scans of the transfer characteristic and by applying a DC bias stress ( $V_{GS}$  = -10 V,  $V_{DS}$  = -10 V) for 60 min inside a N<sub>2</sub>-filled glove box and at ambient conditions. To investigate environmental stability, devices were stored at ambient conditions and measured periodically over a period of 16 days.

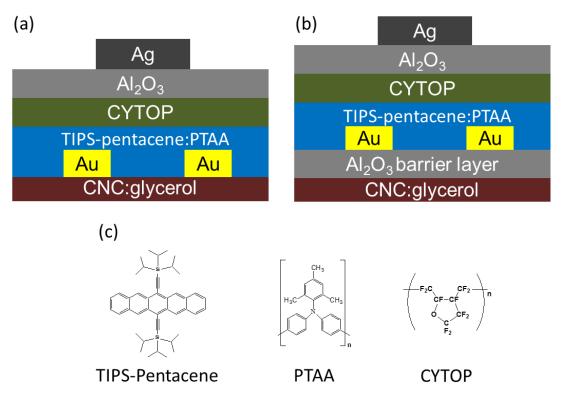

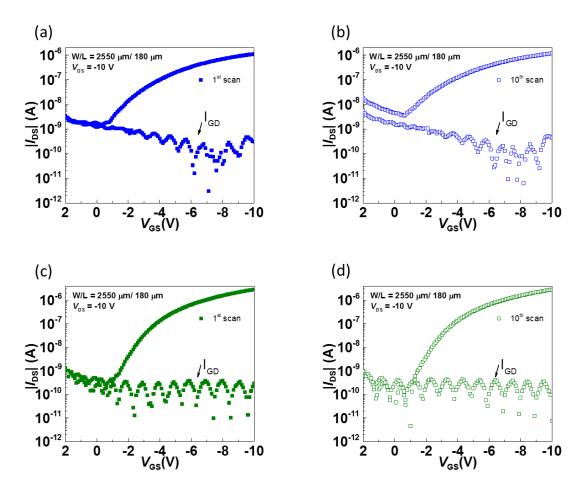

## 3.4.1 Pristine condition in nitrogen

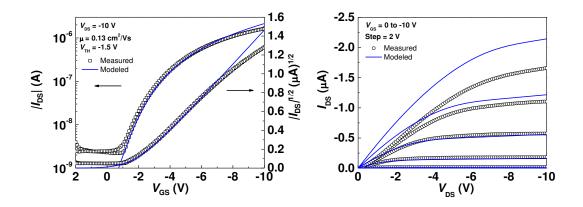

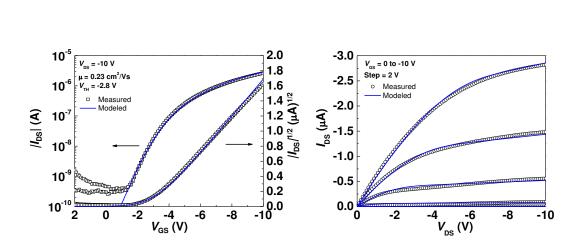

Figure 22 displays the transfer and output characteristics of representative D1and D2-type OFETs. Maximum carrier mobility values of 0.13 cm<sup>2</sup>/Vs and 0.23 cm<sup>2</sup>/Vs were extracted from the transfer characteristics (in the saturation regime) of devices D1 and D2, respectively. Figure 22 also shows the transfer characteristics of the D1- and D2type OFETs kept in N2 for one month. In the D1 OFET, the carrier mobility decreased to 0.08 cm<sup>2</sup>/Vs, while in the D2 OFET the carrier mobility remained unchanged with a value of 0.23 cm<sup>2</sup>/Vs. The decreased mobility in the D1 OFET suggests that chemical or physical interactions occur between the substrate and the organic semiconductor. However, these interactions are clearly suppressed in the D2 OFET. The threshold

voltage of D1- and D2-type OFETs does not change more than 0.1 V within this time frame.

Figure 22. (a) Transfer characteristics of a D1-type OFET before and after one month in N<sub>2</sub>. (b) Output characteristics of a D1-type OFET before and after one month in N<sub>2</sub>. Larger current with larger  $|V_{GS}|$ ,  $V_{GS}$  from 0 to -10 V, the step is 2 V. (c) Transfer characteristics of a D2-type OFET before and after one month in N<sub>2</sub>. (d) Output characteristics of a D2-type OFET before and after one month in N<sub>2</sub>. Larger current with larger  $|V_{GS}|$ ,  $V_{GS}$  from 0 to -10 V, the step is 2 V. (c) Transfer characteristics of a D2-type OFET before and after one month in N<sub>2</sub>. Larger current with larger  $|V_{GS}|$ ,  $V_{GS}$  from 0 to -10 V, the step is 2 V.

Table I displays average values of carrier mobility  $\mu$ , average variation of carrier mobility, threshold voltage  $V_{TH}$ , and on/off current ratio  $I_{on}/I_{off}$  measured on the D1- and D2-type OFETs with labeled dimensions and yield at pristine condition in N<sub>2</sub>, storing in N<sub>2</sub> for one month, and storing in ambient for 6 days on D1-tpye OFETs and 16 days on D2-type OFETs.

| Label | Barrier<br>layer                                          | Measurement<br>time                 | W/L                                            | C <sub>in</sub><br>(nF/cm²) | μ<br>(cm <sup>2/</sup> Vs) | Ave. %<br>change of μ | $V_{th}$ (V)   | I <sub>ON</sub> /I <sub>OFF</sub> |

|-------|-----------------------------------------------------------|-------------------------------------|------------------------------------------------|-----------------------------|----------------------------|-----------------------|----------------|-----------------------------------|

| D1    | None                                                      | Pristine in N <sub>2</sub>          | 2550 μm<br>/180 μm<br>Average<br>(6/6 devices) | - 31.0                      | 0.06<br>(±0.03)            | NA                    | -1.0<br>(±0.4) | 4.8 x 10 <sup>2</sup>             |

|       |                                                           | After one month in N <sub>2</sub>   |                                                |                             | 0.06<br>(±0.02)            | -7.2                  | -0.8<br>(±0.4) | 5.8 x 10 <sup>2</sup>             |

|       |                                                           | 6 days<br>at ambient<br>conditions  |                                                |                             | N/A                        |                       |                |                                   |

| D2    | 300<br>cycles of<br>ALD<br>Al <sub>2</sub> O <sub>3</sub> | Pristine in N <sub>2</sub>          | 2550 μm<br>/180 μm<br>Average<br>(8/8 devices) |                             | 0.11<br>(±0.08)            | NA                    | -2.1<br>(±0.7) | 2.4 x 10 <sup>3</sup>             |

|       |                                                           | After one month in N <sub>2</sub>   |                                                |                             | 0.11<br>(±0.08)            | -2.8                  | -2.2<br>(±0.7) | 2.7 x 10 <sup>3</sup>             |

|       |                                                           | 16 days<br>at ambient<br>conditions |                                                |                             | 0.17<br>(±0.12)            | 45.1                  | -0.3<br>(±0.4) | 2.2 x 10 <sup>2</sup>             |

Table I. Device dimensions, average mobility, average threshold voltage, and average on/off current ratio of OFETs.

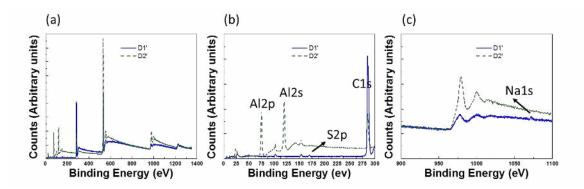

To identify the interactions between the substrate and the organic semiconductor layer, we conducted X-ray photoelectron spectroscopy (XPS) measurements on bare CNC:glycerol substrates (D1') and CNC:glycerol substrates with an ALD-grown Al<sub>2</sub>O<sub>3</sub> barrier layer (D2'). Figure 23 displays the binding energy spectra measured by XPS, wherein clear differences are observed between the spectra obtained for the two substrates. First, Al2p and Al2s peaks are detected on D2' because of the Al<sub>2</sub>O<sub>3</sub> barrier layer deposited by ALD. More notably, sulfur and sodium peaks are detected on D1', but not on D2'.

Figure 23. Binding energy spectra from XPS of a bare CNC:glycerol (D1') substrate and a CNC:glycerol (D2') substrate with ALD-grown  $Al_2O_3$ . (a) Binding energy from 0 to 1,400 eV. (b) Zoomed-in 0 to 300 eV region of binding energy. (c) Zoomed-in 900 to 1,100 eV region of binding energy.