## Organic field-effect transistors with nonlithographically defined submicrometer channel length

Susanne Scheinert<sup>a)</sup> and Theodor Doll

Ilmenau Technical University, Institute of Solid State Electronics, D-98684 Ilmenau, Germany

Axel Scherer<sup>b)</sup>

California Institute of Technology, 1200 East California Blvd. Pasadena, California 91125

Gernot Paasch<sup>c)</sup>

Leibniz Institute for Solid State and Materials Research Dresden, D-01171 Dresden, Germany

Ingo Hörselmann

Ilmenau Technical University, Institute of Solid State Electronics, D-98684 Ilmenau, Germany

(Received 3 December 2003; accepted 6 April 2004; published online 12 May 2004)

We developed an underetching technique to define submicrometer channel length polymer field-effect transistors. Short-channel effects are avoided by using thin silicon dioxide as gate insulator. The transistors with 1 and 0.74  $\mu$ m channel length operate at a voltage as low as 5 V with a low inverse subthreshold slope of 0.4–0.5 V/dec, on–off ratio of 10<sup>4</sup>, and without short-channel effects. The poly(3-alcylthiophene)'s still suffer from a low mobility and hysteresis does occur, but it is negligible for the drain voltage variation. With our underetching technique also device structures with self-aligned buried gate and channel length below 0.4  $\mu$ m are fabricated on polymer substrates. © 2004 American Institute of Physics. [DOI: 10.1063/1.1758775]

Organic field-effect transistors (OFETs) are of interest for many applications including organic displays, complementary circuits, and all-polymer integrated circuits.<sup>1-3</sup> Low-cost fabrication requires the use of solution-processible polymers instead of vacuum deposited low-molecular weight organics. Although mobilities of up to  $0.1 \text{ cm}^2/\text{Vs}$ have been demonstrated for soluble regioregular poly(3alkylthiophene),<sup>3,4</sup> poly-(9,9-dioctylfluorene-bithiophene),<sup>5</sup> and pentacene from soluble precursors,<sup>6</sup> OFETs needed for high-performance circuits still require extremely small gate length to be modulated at competitive frequencies. The cutoff frequency  $f_0 = g_m / (2 \pi C_{GS})$  is determined by the maximum transconductance  $g_m$  and the gate-source capacitance  $C_{GS}$ . Neglecting parasitic capacitances, the latter is approximated by the gate oxide capacitance. Using the simple Shockley current characteristics one obtains as an estimation  $f_0 < \mu U_{GS,eff} / (2\pi L^2)$ , where  $U_{GS,eff}$  is the gate-source voltage relative to the threshold voltage. With a voltage of at most 10 V, a realistic upper value of  $0.01 \text{ cm}^2/\text{V}$  s for the mobility and a lower limit for the cut-off frequency of 100 kHz, one obtains as an upper limit for the channel length L  $<4 \,\mu$ m. Since additional parasitic capacitance cannot be avoided, only submicrometer devices lead to applicable circuits. Demonstrations of different patterning techniques such as screen printing,<sup>7</sup> soft lithographic stamping,<sup>8</sup> or inkjet printing<sup>9</sup> have so far not demonstrated both resolution and alignment accuracy desired. Photolithography<sup>2</sup> is expected to be costly for the submicrometer regime. Recently, Stutzmann et al.<sup>10</sup> used embossing to fabricate vertical-channel fieldeffect transistors with submicrometer channel lengths, but could not observe saturation in the measured output characteristics. These authors also presented a self-aligned gate structure with reduced overlap capacitance. We demonstrate the fabrication of submicrometer field-effect transistor channels by employing an underetching technique for submicrometer patterning, to enable the use of low-resolution photolithographic steps and standard microelectronic processes.

Transistor design and dimensions are closely related to the material properties. At first, in order to reach the off-state and saturation, the active layer thickness must be less than the depletion length.<sup>11</sup> We use poly(3-octylthiophene) (P3OT) and poly(3-hexylthiophene) (P3HT), which are both unintentionally highly doped (of the order  $10^{17}$  cm<sup>-3</sup> Refs. 11-13). To successfully deplete the layers their thickness must be of the order of 30 nm or less, which can be achieved by controlling the solution concentration and the spincoating process.<sup>11</sup> Down-scaling comprises also the gate insulator thickness in order to avoid short-channel effects. They have been analyzed by two-dimensional simulations (method and standard parameters are described in Refs. 12 and 14). With an organic insulator (poly-4-vinylphenol, P4VP) thickness of 400 nm one can prevent leakage currents, but the simulated output characteristics show saturation only for channel length larger than 1  $\mu$ m and a large supralinear current for shorter channels. A reduction of the insulator thickness down to 50 nm for devices with 0.5 and 0.3  $\mu$ m channel length reduces this effect sufficiently. Since such organic insulators are not yet available, we demonstrate the short-channel OFET fabrication here with a hybrid structure: The gate insulator is a 30 nm silicon dioxide layer on a  $n^+$ -silicon wafer serving as the gate electrode.

Undercutting is a phenomenon well known in microelectronics<sup>15</sup> and usually occurs unintentionally leading

4427

Downloaded 14 Dec 2005 to 131.215.225.171. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed; electronic mail: susanne.scheinert@tu-ilmenau.de

<sup>&</sup>lt;sup>b)</sup>Electronic mail: etcher@caltech.edu

<sup>&</sup>lt;sup>c)</sup>Electronic mail: g.paasch@ifw-dresden.de

<sup>© 2004</sup> American Institute of Physics

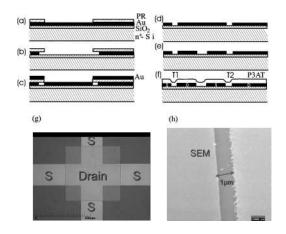

FIG. 1. Fabrication steps for the OFET (a)–(f), cross section of two transistors T1 and T2 (f), optical micrograph (g), and a SEM image of the transistor with  $L=1 \ \mu$ m.

to an increased effective channel length.<sup>16</sup> We used underetching technique, in combination with low-resolution photolithographic steps and further standard microelectronic processes, for the inexpensive and manufacturable definition of the submicrometer channel length devices. The following fabrication steps are carried out. First, a large-area gold layer is sputtered (50 nm) on top of the oxidized highly doped silicon wafer. Then a low-resolution photolithographic step is used to fabricate a structured photoresist layer [Fig. 1(a)]. Subsequently, a wet chemical etching and underetching is applied to remove the gold. We have systematically investigated this etch process to determine the etch rate of gold on different substrates. As a result, the underetched length can be controlled in the submicrometer region and ultimately defines the channel length of the transistor [Fig. 1(b)]. To complete the source/drain structure, a 10-nm-thick chromium and 40-nm-thick gold layer are evaporated [Fig. 1(c)] followed by a lift-off process to remove the photoresist [Fig. 1(d)]. A separation step [Fig. 1(f)] defines an addition electrode by low-resolution photolithography and an etch step. Finally, the active organic layer of a thickness  $\sim 30$  nm is deposited (unpatterned). An example for the cross section of the resulting structure is depicted in Fig. 1(f). For the photolithographic steps, we used a mask layout realizing transistor channels with different widths w in the range of 200 up to 2000  $\mu$ m. The optical micrograph [Fig. 1(g)] shows the source and drain regions as well as the 200  $\mu$ m channel situated in between. In the scanning electron microscopy (SEM) image [Fig. 1(h)] the source and drain are again visible and separated by a 1  $\mu$ m channel length. Considering the uniformity of the channel, even for shorter channels (few hundred nonometers) the variation of the prepared channel length remains small over the channel width.

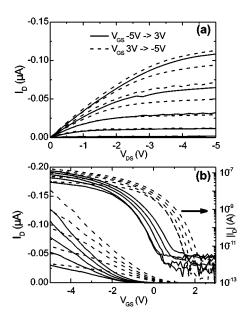

The output characteristics for an OFET with P3HT ( $\approx 30$  nm) as active layer, channel length  $L=0.88 \ \mu$ m, and width  $w=2000 \ \mu$ m [Fig. 2(a)] indicate high performance with the following peculiarities: (i) The transistor operates at the desired voltage below 5 V. (ii) There is a clear transition into saturation indicating that short-channel effects are almost suppressed in the device. From the transfer characteristics [Fig. 2(b)] one obtains (iii) an approximately linear slope in the active region indicating that the contact resistances are negligible (a small curvature at lower drain volt-pownloaded 14 Dec 2005 to 131 215 225 171. Bedistribution subi

FIG. 2. Output (a) and transfer characteristics (b) on a linear and logarithmic scale for a P3HT OFET with  $L=0.88 \ \mu m$ ,  $w=2000 \ \mu m$ . For the output characteristics the gate-source voltage is varied as -5(1)3 V and back as 3(-1)-5 V, depicted are the curves between -5 and 0 V. For the transfer characteristics the drain-source voltage is varied as -7(1)-1 V. For each  $V_{DS}$  the gate-source voltage is varied from  $V_{GS}=-5$  to 3 V and back from 3 to -5 V.

ages is seen for the sweep from positive to negative gate voltage, since this curvature does not occur in the opposite sweep direction, it is unlikely to be caused by contact effects and is probably related to hysteresis), (iv) a high on-off ratio (larger than  $10^4$ ), and (v) a low inverse subthreshold slope of  $S \approx 400$  mV/dec. This performance compares well with the usually unfavorable high values of several V/dec in OFETs.<sup>12,17,18</sup> In all cases, S is larger than estimated solely from the insulator thickness. This deviation may be caused by recharging of interface states.<sup>12</sup> Since we focused on the short-channel fabrication, regioregular P3HT for the active layer was used, purified (by Dr. S. Janietz, IAP Golm, Germany) but without special steps for higher ordering. Correspondingly the hole mobility estimated from the current characteristics is with  $\mu \approx 3 \times 10^{-5}$  cm<sup>2</sup>/V s below the best values mentioned above. We also observe the hysteresis which is well known for OFETs,<sup>14,19,20</sup> but which can be reduced by using a higher-mobility polymer for the active layer as in Ref. 10. However, the hysteresis occurs only in the gate voltage sweep and the difference between the threshold voltages for up and down sweeps of the gatesource voltage is less than 1.5 V for a given drain voltage, much smaller than usually reported. We observe also a drainsource voltage dependence of the subthreshold current, typically attributed to short-channel effects, that can be also caused by rechargeable interfaces or bulk traps.<sup>12,13</sup> For devices with P3OT similar properties are obtained.

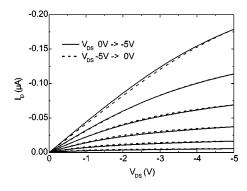

With the underetching technique, the channel length can be defined in a controlled manner well below  $L=1 \ \mu$ m. Figure 3 shows the output characteristics of a P3HT OFET with channel length  $L=0.74 \ \mu$ m and with  $w/L\approx 1350$ . The main features are the same as before, with mobility  $\mu\approx 4 \ \times 10^{-5} \text{ cm}^2/\text{V}$  s. The hysteresis resulting from the variation of the gate voltage sweep direction does occur again. How-

Downloaded 14 Dec 2005 to 131.215.225.171. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 3. Output characteristics for a P3HT OFET with  $L=0.74 \ \mu\text{m}$ ,  $w = 1000 \ \mu\text{m}$ . The gate-source voltage is varied as -5(1)0 V. For each  $V_{GS}$  the drain-source voltage is varied from  $V_{DS}=0$  to -5 V and back from  $V_{DS}=-5 \text{ to } 0 \text{ V}$ .

ever, in Fig. 3 now the influence of the drain voltage sweep direction is shown. For each gate voltage the drain voltage is varied from 0 to -5 V and back from -5 to 0 V. In this case practically no hysteresis is observed, similar to Ref. 10. A possible asymmetry in the I-V characteristics due to the differently prepared contacts was investigated by switching source and drain. The difference in the drain current is very small and it is partly covered by the hysteresis in subsequent measurements.

Underetching in combination with low resolution lithography and simple lift-off processing enables the efficient fabrication of organic field-effect transistors with well-defined and controllable channel lengths in the submicrometer region. Hybrid-design transistors feature low voltage operation, saturation, negligible short-channel effects, high on-off ratio, and low inverse subthreshold slope. A small hysteresis does occur only for the gate voltage sweep. It is expected to become sufficiently small by using improved polymers<sup>3-6,10</sup> with higher mobilities.

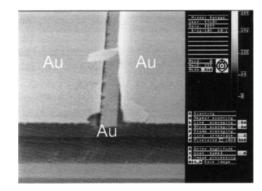

All-organic circuits must ultimately be fabricated on plastic substrates, with an organic gate insulator, and with self-aligned gates. Furthermore, high cut-off frequencies are only possible for transistors with low parasitic capacitances. In our fabricated hybrid OFET [Fig. 1(f)] the silicon wafer is the gate leading to high overlap capacitances. As a first step, using a plastic substrate (Mylar), a self-aligned, buried gate structure has been prepared. The same technological steps as shown in Figs. 1(a)-1(e) are realized to fabricate the source/ drain contacts. Subsequently, a trench between source and drain is prepared by reactive ion etching followed by gold evaporation. A SEM image of such a structure is shown in Fig. 4, with a channel length of 0.37  $\mu$ m and much reduced overlap capacitances. The completion of this transistor requires solution-processable organic insulators better than available at present. For an optically transparent substrate,

FIG. 4. Structure with a self-aligned buried gate on a plastic substrate.

the fabrication of a self-aligned gate could be accomplished by using the source and drain as opaque optical mask for the gate definition as demonstrated recently for wide-channel (20  $\mu$ m) devices.<sup>21</sup>

- <sup>1</sup>A. Dodabalapur, Z. Bao, A. Makhija, J. G. Laquindanum, V. R. Raju, Y. Feng, H. E. Katz, and J. Rogers, Appl. Phys. Lett. **73**, 142 (1998).

- <sup>2</sup>C. J. Drury, C. M. J. Mutsaers, C. M. Hart, M. Matters, and D. M. Leeuw, Appl. Phys. Lett. **73**, 108 (1998).

- <sup>3</sup>H. Sirringhaus, N. Tessler, and R. H. Friend, Science 280, 1741 (1998).

- <sup>4</sup>Z. Bao, A. Dodabalapur, and A. J. Lovinger, Appl. Phys. Lett. **69**, 4108 (1996).

- <sup>5</sup>H. Sirringhaus, R. J. Wilson, R. H. Friend, M. Inbasekaran, W. Wu, E. P. Woo, M. Grell, and D. D. C. Bradley, Appl. Phys. Lett. **77**, 406 (2000).

- <sup>6</sup>A. Afzali, C. D. Dimitrakopoulos, and T. L. Breen, J. Am. Chem. Soc. **12**, 8812 (2002).

- <sup>7</sup>Z. Bao, Y. Feng, A. Dodabalapur, V. R. Raju, and A. J. Loviger, Chem. Mater. **9**, 1299 (1997).

- <sup>8</sup>J. A. Rogers, Z. Bao, A. Makhija, and P. Braun, Adv. Mater. (Weinheim, Ger.) **11**, 741 (1999).

- <sup>9</sup>H. Sirringhaus, T. Kawase, R. H. Friend, T. Shimoda, M. Inbasekaran, W. Wu, and E. P. Woo, Science **290**, 2123 (2000).

- <sup>10</sup>N. Stutzmann, R. H. Friend, and H. Sirringhaus, Science **299**, 1881 (2003).

- <sup>11</sup>S. Scheinert and W. Schliefke, Synth. Met. **139**, 501 (2003).

- <sup>12</sup>S. Scheinert, G. Paasch, M. Schrödner, H.-K. Roth, S. Sensfuß, and Th. Doll, J. Appl. Phys. **92**, 330 (2002).

- <sup>13</sup>S. Scheinert, G. Paasch, and T. Doll, Synth. Met. 139, 233 (2003).

- <sup>14</sup>S. Scheinert, G. Paasch, S. Pohlmann, H.-H. Hörhold, and R. Stockmann, Solid-State Electron. 44, 845 (2000).

- <sup>15</sup>S. M. Sze, Semiconductor Devices Physics and Technology, 2nd ed. (Wiley, New York, 2002).

- <sup>16</sup>E. J. Meijer, G. H. Gelinck, E. van Veenendaal, B.-H. Huisman, D. M. de Leeuw, and T. M. Klapwijk, Appl. Phys. Lett. **82**, 4576 (2003).

- <sup>17</sup> Y.-Y. Lin, D. J. Gundlach, S. F. Nelson, and Th. N. Jackson, IEEE Trans. Electron Devices 44, 1325 (1997).

- <sup>18</sup> H. Sirringhaus, N. Tessler, D. S. Thomas, P. J. Brown, and R. H. Friend, Adv. Solid State Phys. **39**, 101 (1999).

- <sup>19</sup>G. Horowitz, R. Hajlaoui, D. Fichou, and A. El Kassmi, J. Appl. Phys. 85, 3202 (1999).

- <sup>20</sup> A. R. Brown, A. Pomp, D. M. de Leeuw, D. B. M. Klaassen, E. E. Havinga, P. Herwig, and K. Müllen, J. Appl. Phys. **79**, 2136 (1996).

- <sup>21</sup>A. Bonfiglio, F. Mamelli, and O. Sanna, Appl. Phys. Lett. 82, 3550 (2003).