REVIEW

# **Overview of emerging memristor families from resistive memristor to spintronic memristor**

Lei Wang · CiHui Yang · Jing Wen · Shan Gai · YuanXiu Peng

Received: 13 January 2015/Accepted: 15 February 2015/Published online: 1 March 2015 © Springer Science+Business Media New York 2015

Abstract Memristor is a fundamental circuit element in addition to resistor, capacitor, and inductor. As it can remember its resistance state even encountering a power off, memristor has recently received widespread applications from non-volatile memory to neural networks. The current memristor family mainly comprises resistive memristor, polymeric memristor, ferroelectric memristor, manganite memristor, resonant-tunneling diode memristor, and spintronic memristor in terms of the materials the device is made of. In order to help researcher better understand the physical principles of the memristor, and thus to provide a promising prospect for memristor devices, this paper presents an overview of memristor materials properties, switching mechanisms, and potential applications. The performance comparison among different memristor members is also given.

## 1 Introduction

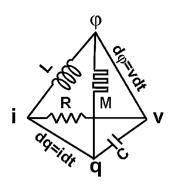

The fundamental circuit elements can be simply classified into resistor, capacitor, inductor, and memristor. Compared to similar components, memristor is a relatively new concept that was theoretically proposed by Leon Chua in 1971 [1]. The presence of the memristor can retrospect to a finding that there is a missing relationship among four fundamental circuit variables (i.e., electric current *i*, electric voltage *v*, electric charge *q*, and magnetic flux  $\varphi$ ) [1]. The existence of the Faraday's law and three other fundamental circuit components has already established five direct relationships among aforementioned variables. However, the relationship that links magnetic flux with electric charge is missing, which can be however interpreted by the fourth fundamental element, i.e., memristor. The consequent six relationships among the four fundamental elements are schematically shown in Fig. 1.

According to Chua's finding, memristor is a two-terminal device that describes a non-linear relationship between magnetic flux and electric charge and its resistance would vary, depending on the amount of charge that flowed through the device. Such a relationship is described mathematically as [1]:

$$\mathrm{d}\phi = M\mathrm{d}q,\tag{1}$$

where *M* is the memristance. As  $\varphi$  and *q* are time integrals of voltage and current, respectively, Eq. (1) can rewritten as:

$$M = \frac{\mathrm{d}\phi/\mathrm{d}t}{\mathrm{d}q/\mathrm{d}t} = \frac{V}{I},\tag{2}$$

According to Eq. (2), the unit of M is obviously the same as resistance, i.e., ohm ( $\Omega$ ). Although this hypothesis was postulated without any experimental evidence at that time, Chua has made use of op amps and discrete non-linear resistors to build a working device that can realize the memristive function [1]. However, this device is bulky and also active due to the requirement for the power supply. A generalized definition of memristive systems evolved from memristor was given by Chua and Kang in 1976 [2] who elucidated a fact that memristive system strongly depend on a state variable. The memristive system can be mathematically defined as [2]:

$$v = R(w)i,\tag{3}$$

$$\frac{\mathrm{d}w}{\mathrm{d}t} = f(w,t),\tag{4}$$

C

L. Wang  $(\boxtimes) \cdot C$ . Yang  $\cdot J$ . Wen  $\cdot S$ . Gai  $\cdot Y$ . Peng School of Information Engineering, Nanchang Hang Kong University, Nanchang 330063, People's Republic of China e-mail: LeiWang@nchu.edu.cn

Fig. 1 The four fundamental circuit elements and their respective relationships

where w can be an internal state variable, and R and f can in general be explicit function of time. Chua and Kang also pointed out that the 'quasi-static' conduction equation that links the voltage across the device with the current through it at any particular time, and the dynamical equation that considers the state variable w as a time varying function of itself and possibly the current through the device, are two critical equations to characterize memristive systems. Based on [2], a memristive system is regarded to have vector state, as compared to memristor having scalar state. Notwithstanding the availability of the mathematic model, memristor has not received much attention from worldwide researchers until Strukov et al. [3] proposed a nanoscale TiO<sub>2</sub> device model to theoretically realize the memristive behaviour in 2008. Since then, massive research enthusiasm has been devoted to the exploration of the innovative memristor technologies, resulting in many technical publications and a large number of US patents. Under this circumstance, the necessity to strictly distinguish memristor from memristive system becomes unimportant, and Chua has therefore recommended that the nomenclature be simplified by referring to both as memristors, since in fact the generalization is a 'trivial extension' [4]. In [4], Chua also gave a broader definition of memristor that includes all 2-terminal non-volatile memories based on resistive switching. However, as the memristive behaviour has been found on a wide variety of systems such as unipolar and bipolar resistive switches, magnetic spin-torque transfer device, and phase-change memories, Chua has further expanded the scope of the memristor to any 2-terminal device that exhibits a pinched hysteresis loop in the *v*-*i* plane when driven by any bipolar periodic voltage or current waveform, for any initial conditions [5]. Such a definition is finally consummated in Chua's most recent publications [6, 7] so as to be suited for the original definition of the idea memristor as well as the generalized definition for memristive system, i.e., 'any 2-terminal black box is called a memristor if, and only if, it exhibits a pinched hysteresis loop for all bipolar periodic input current signals (resp., input voltage signals) which result in a periodic voltage (resp., current) response of the same frequency in the voltage-current (v-i) plane'.

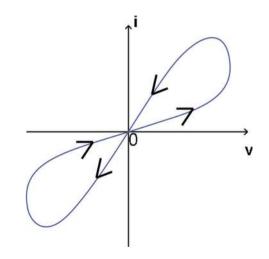

The most representative attribute of the memristor is its current-voltage (I-V) curve that exhibits a pinched hysteresis loop, as shown in Fig. 2. Such a pinched hysteresis loop, which always passes through the origin, plays an essential role in characterizing the v-i relationship of a memristor excited by any periodic current source (resp., voltage source) that spans both positive and negative values over each period. It should be also noted that the shape of the pinched hysteresis loop would vary along with the change of the frequency and the amplitude of the input waveform. In this case, the v-i locus will behave as a normal resistor by increasing frequency towards infinity, but still includes the origin. It is instructive to realize that the pinched hysteresis loop is not derived from a mathematical model, but an inherent feature of the memristor [7]; any device that exhibits a pinched hysteresis loop over any bipolar periodic testing input signals are considered as a memristor, regardless of the shape of the loop.

The reason that memristor has become the current scientific focus arises from its extraordinary properties. First, as suggested by Fig. 2, if the memristor is in its equilibrium state at some certain moment, i.e., v = i = 0, the memristor does not lose the values of the magnetic flux and the electric charge when both voltage and current are zero at the instant when the power is switched off, but rather makes the original values unchanged. This would enable memristor to remember its most recent state when facing a power-off, exhibiting the potential of being a non-volatile memory. In addition, the feasibility of scaling memristor to 10 nm and even below has been demonstrated [8], indicating a potential for much higher integration density than current non-volatile memories. More importantly, the

Fig. 2 A typical pinched hysteresis loop of the memristor

attribute that the resistance dynamically changes according to the applied stimulus would allow memristor to imitate functions of brain synapse whose state can be changed via the interactive strength between two neurons. Therefore, memristor has been utilized for a wide range of applications including non-volatile memory, dynamic load, neuromorphic system, and image processing, and a set of memristor devices have been devised at the laboratory level such as resistive memristor [9–11], polymeric memristor [12–14], ferroelectric memristor [15–17], manganite memristor [18–20], resonant-tunneling diode (RTD) memristor [21, 22], and spintronic memristor [23, 24]. Table 1 shows the performance comparison among these different memristors. In spite of these achievements, a comprehensive review regarding the physical principles of each memristor device and their respective performance merit/weakness was rarely found by the time of writing. In order to help researcher better understand the physics behind these emerging memristors, and thus to push the current memristor technology towards more advanced stage, this paper covers an overview of today's mainstream memristor devices including their materials properties, switching mechanism, and their respective performance superiority/drawback, as detailed below.

# 2 Resistive memristor

Before the advent of the resistive memristor, resistive materials have already been widely utilized in the resistive random access memories (ReRAM) [25–27]. The storage function of ReRAM is realised by an intrinsic physical behaviour observed in ReRAM, namely resistive switching. Because of the resistive switching, the resistive material can be switched between a high resistance state (HRS) and a low resistance state (LRS) under an external electrical stimuli. The switching process from HRS to LRS and the corresponding switching voltage are usually named 'SET' process and  $V_{SET}$ , while the process from LRS to

Table 1 Comparison of different memristors

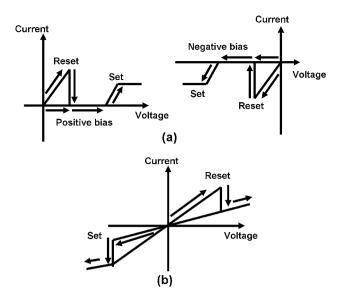

HRS and the required switching voltage are represented by 'RESET' process and  $V_{RESET}$ . It is instructive to mention that in most cases, the current stemming from the external stimuli is restricted to a local region with high conductance during 'SET' process, whereas it flows uniformly through ReRAM during 'RESET' process [28]. It should be also noted that in bistable resistive materials, like some transition metal oxides, there are usually two switching modes, i.e., unipolar switching and bipolar switching, as shown in Fig. 3.

Unipolar switching allows for a switching process that is independent of the voltage/current polarity. Therefore, the 'SET' process and the 'RESET' process is achieved with the same signal polarity. However, the bipolar switching mode gives rise to an opposite signal polarity between the 'SET' process and the 'RESET' process. The comparison between Figs. 2, 3 clearly shows that the resistive material when operated in the bipolar switching mode exhibits an analogous I–V curve to that of the theoretical memristor. As a consequence, considerable research efforts have been recently dedicated to the development of the memristor using resistive materials such as TiO<sub>2</sub> [9, 11, 29], ZnO [30], and TaO<sub>x</sub> [31, 32], thus triggering a presence of some resistive materials-based memristor prototypes.

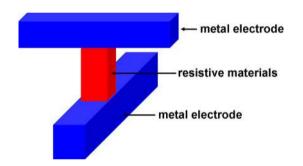

The architecture of the memristor using resistive materials usually consists of an insulator sandwiched by two metals, also known as MIM structure, as illustrated in Fig. 4.

By changing the magnitude and the polarity of the signal applied to the metals (i.e., electrodes here), the sandwiched insulator can be toggled between the 'ON' state and the 'OFF' state so as to realise the memristive function. Although such a resistance transition phenomenon has been found for many years, the correlated physical mechanism is still not well understood. Today, the electric pulse induced resistance switching (EPIR) effect is the most generally accepted mechanism. The most appealing trait of EPIR arises from its strong field-direction dependence, indicating that the resistance of the system can be toggled by the

| Memristor     | ON/OFF ratio | Access time (ns) | Retention       | Endurance        | References          |

|---------------|--------------|------------------|-----------------|------------------|---------------------|

| Resistive     | 2000         | ~10              | Very long       | 10 <sup>9</sup>  | [9–11, 28–43]       |

| Polymeric     | 100          | ~25              | Relatively long | 10 <sup>8</sup>  | [12–14, 44–46]      |

| Ferroelectric | 300          | ~10              | Relatively long | 10 <sup>14</sup> | [15–17, 62]         |

| Manganite     | 100          | $\sim 100$       | long            | $10^{3}$         | [18–20]             |

| RTD           | -            | _                | -               | _                | [21, 22, 54, 55]    |

| Spintronic    | 5            | $\sim 10$        | Very long       | 10 <sup>16</sup> | [23, 24, 56–61, 62] |

Albeit specific properties of RTD memristor are rarely reported to the best of our knowledge, reference numbers are still provided for reader's convenience

Fig. 3 Switching of resistive materials in a unipolar mode, and b bipolar mode. The switching direction of unipolar ReRAM does not depend on the polarity of the external stimuli, while the switching direction of bipolar ReRAM strongly relies on the polarity of the external stimuli

Fig. 4 Resistive memristor based on MIM architecture

applied voltage or current pulses to generate the I-V hysteresis that supplies the function of the resistance memory. Although the secret behind EPIR is still uncovered, the consensus is that the EPIR effect will cause the formation and rupture of a conductive filament (CF) inside the resistive materials [33]. Thermochemical effect has been regarded as one of the most plausible explanations for the CF hypothesis [34-36]. The thermochemical mechanism assumes a large number of  $O^{2-}$  ions accumulated around the electrode, thus leading to a formation of oxygen vacancies. With an application of a negative bias to the top electrode, the  $O^{2-}$  ions are pushed away from the top electrode, while the oxygen vacancies are attracted towards the top electrode. In this case, the vacancy dopants would drift in the electric field through the most favourable diffusion paths, such as grain boundaries, to form a filamentlike path with a high electrical conductivity [37]. Once the CFs are formed, the current flow that would concentrate on the resulting filaments can trigger a fast growth of these filaments due to the local heating by the concentrated current flow, which corresponds to a 'SET' process. The 'RESET' process, is postulated to be realized by the thermal rupture of the filaments according to the heat produced in the presence of a large current flow.

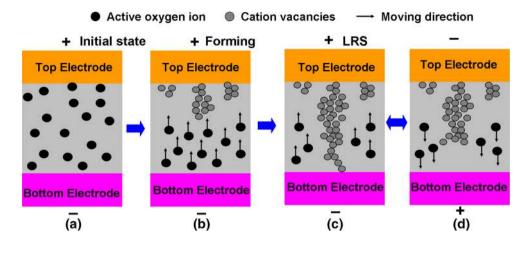

In contrast to the thermochemical effect, another interpretation ascribed the occurring of the CF to the motion of the oxygen ions that usually appear near crystal defects such as oxygen vacancies and grain boundaries [28, 38, 39]. As shown in Fig. 5a, applying a positive bias to the top electrode would drive the oxygen ions towards the top electrode where the oxygen ions will thereby accumulate. This migration would produce abundant cation vacancies therein Fig. 5b. As the cation vacancies that can create an acceptor level near the valence band are the source of the hole carriers in semiconductors, it is possible for these newly created cation vacancies to be transformed into the nuclei of semiconducting CFs. Subsequently these nuclei will grow with the assist of the electric field to form a CF extending through the whole thickness of the storage medium (Fig. 5c), and finally the memory cell would reach the LRS. Due to the fact that the CF actually grows from anode to cathode, the thinnest region of the CF is regarded to be located near the cathode [28]. As a result, more Joule heating will be accumulated at the thinnest part of the CF when negatively biasing the top electrode. Under this circumstance, the oxygen ions at the thinnest part of the CF will be aggressively accelerated towards the bottom electrode and then be trapped at the storage medium/bottom electrode interface or the grain boundaries of the bottom electrode. This motion would destroy the concentration of the cation vacancies in the thinnest part of the CF, thus resulting in the rupture of the CF, as shown in Fig. 5d. The memory cell will consequently be switched into the HRS.

In addition to the thermochemical effect and the ionic effect, other possible mechanisms that include metalsemiconductor transition [29, 40], crystalline TiO<sub>2</sub>-amorphous TiO<sub>2</sub> phase transition via conduction heating and breaking [29, 41], raising and lowering Schottky barriers via bulk or interface transport of the oxygen [29, 42], and conductance heating causing lateral transport of conducting filaments [29, 43], have also been proposed to account for the resistance switching of the resistive memristor. The presence of various switching mechanisms is possibly due to the fact that the resistive materials were fabricated and measured differently among the aforementioned literatures. Therefore, it is very likely to conclude that the switching behaviour of the resistive memristor is not induced by one specific effect, but a result of a combination of all the possible switching mechanisms introduced above.

As resistive materials have been deeply investigated for decades due to their potential applications for ReRAM, a Fig. 5 a The initial state with randomly distributed mobile oxygen ions. b The nucleation and subsequent growth from anode to cathode of CFs composed of cation vacancies during forming process. c The LRS with a full CF whose thinnest region is near the cathode. d The HRS with a partially ruptured conducive filament at its thinnest region. Reprinted with permission from [28]

PEO

meta

atal

wealth of knowledge regarding their basic electrical, thermal and mechanical properties have already been accumulated. With the help of these treasure, the resistive memristor devices have received much more attention than other memristors in perspective of both experimental design and theoretical analysis. Nevertheless, in terms of the original meaning of 'memristor', 'memristor' is a nonlinear analogue device. This is however against the character of the ReRAM whose I–V curves usually include an ohmic conduction part. Therefore, ReRAM can not be strictly recognized as a memristor. In spite of such a difference, scientists still believe that there is at least convergence between them and some researchers even use these two terms interchangeably [29].

# **3** Polymeric memristor

The memristive function of the polymeric device is achieved by switching the electrical conductivity of the polymer film between a highly resistive (also called 'reduced') state and a highly conductive (also called 'oxidized') state through the well-known redox reaction. The structure of the polymeric memristor is schematically shown in Fig. 6.

A thin conducting polymer (polyaniline, PANI) layer is deposited onto an insulating solid substrate with two preformed metal electrodes. An additional lithium perchloride doped polyethylene oxide (PEO) film is formed on the central region of the PANI layer so as to provide ionic flux into (and out of) the PANI layer at the interface. Such a PANI-PEO interface is the main region where the redox reaction occurs and is therefore called active zone. Moreover, as the redox reaction requires the reference potential, a third electrode, i.e., a silver wire, is attached into the PEO layer to behave as a reference electrode.

The working principles of the polymeric memristor are illustrated in Fig. 7.

**Fig. 6** The cell structure of the polymeric memristor. Two metal electrodes are deposited onto insulating substrate (glass) and covered by PANI layer. Solid electrolyte is deposited in the central part of PANI channel and reference electrode is connected to it. Two currents, i.e., total current ( $I_{tot}$ ) and ionic current ( $I_{ion}$ ) are measured. Reprinted with permission from [14]

PANI

As can be seen from Fig. 7a, some region inside the active zone exhibits a higher potential than the oxidizing potential when applying a positive excitation to the initially insulating (blue area) device. In this case the PANI layer can be toggled from the resistive state to the conductive state in this restricted zone only. It should be noted that the resulting potential profile inside the active zone would be changed with the transformation process [12]. As a consequence, the potential inside some previously insulating regions may reach the oxidizing potential, and thus renders these regions conductive. Due to the above reason, a gradual movement of the conductive zone boundary can be observed, which gives rise to a relatively slow conductivity variation. When applying a negative excitation to the initially conducting (green area) device, the whole active zone would be exposed to the reduction potential, as depicted in Fig. 7b. This would allow the reduction and transformation of PANI into the insulating state to take place

Fig. 7 Mechanisms of conductivity variation in the electrochemical polymeric elements. *Green areas* correspond to the PANI in its oxidized conducting state, while *blue areas* represents PANI in reduced insulating form. The *orange dots* represent the Li ions, and the arrows denotes the prevalent direction of motions. **a** Positive potential is applied to the initially insulating (*blue area*) device. Electrical potential profile along the PANI layer is shown in the

simultaneously in the whole active zone [12], thereby inducing a fast switching rate. Therefore, by means of the adjustment of the actual potential of the active zone with respect to the reference potential,  $\text{Li}^+$  ions can be either injected to or removed from the PANI layer, thus providing the polymeric device with a memristive function [12, 44– 46].

Compared with the resistive memristor, the polymeric memristor is operated in a more similar manner to the theoretical memristor, as its resistance is actually governed by the charge transfer. In addition, the phenomenon that the PANI conductivity when subjected to a positive signal excitation is gradually increased is very analogous to the synaptic function (learning) in real biological systems, described in the Hebbian rule [14]. The decrease of the PANI conductivity for a given negative bias also plays an important role on the network applications. Considering a complex network that comprises the designed polymeric memristors, there will be numerous signal pathways between input and output terminals. In this case, the frequent use of this network for a long time would make memristors reach a full conductive state, and thus impairs the memristive function of the device. Under this circumstance, the short term periodic application of the negative bias would effectively prevent the saturation of the system [12, 14]. Moreover, the fact that the relatively long application of the negative bias between input and output terminals can destroy the preferential signal pathways can be used to imitate the so called 'supervised learning' behaviour [12].

Although a rather simple circuit based on the polymeric memristor has already been designed to realize both the supervised and the unsupervised learning of the networks, it should be noticed that a real complex networks devised for decision making may consists of a large number of the elements working for a rather long time (i.e., over thousands of learning cycles) so as to achieve the learning behaviour [13]. As a result, some stringent requirements

4623

central part, and transformation of the PANI into the conducting state will occur only in the zone with higher potential than the oxidizing potential. **b** Negative voltage is applied to the initially conducting element. Electrical potential profile along the PANI layer is shown in the central part. All active zone is under the reduction potential. Reprinted with permission from [12] (Color figure online)

have been imposed to the physical properties of the polymeric memristor. Firstly, the conductivity ratio in the oxidized conducting and reduced insulating states must be as high as possible. Secondly, the absolute value of the conductivity of the memristor in the oxidized sate must be rather high. Most importantly, the memristor needs to have a high stability. Unfortunately, the performance of the current polymeric memristor technologies, to authors' best knowledge, is far behind these requirements, whereby the quest for more innovative technologies to vastly improve the performance of the polymeric memristor becomes very necessary.

# 4 Ferroelectric memristor

It is well known that the polarization of the ferroelectric materials when suffering from an external electric field can be toggled between two distinct states. Therefore, these two opposite polarization states can be used to represent binary bits '0' and '1', thus resulting in the advent of the ferroelectric random access memory (FeRAM). Because of its non-volatile storage function, ferroelectric materials has been widely used in Radio Frequency Identification (RFID), smart card, ID card, and other embedded memory applications such as railway passes, automobile equipments, and domestic electronic appliances [47, 48]. In addition to FeRAM, the discover that the ferroelectricity can be maintained in a thin film down to a nanometer scale has made ferroelectric materials appealing for the ferroelectric tunnel junction (FTJ) that usually consists of a nanometer-thick ferroelectric film sandwiched by two metal electrodes. The fact that the tunneling current through the FTJ with an external electric field can be toggled between two non-volatile states through the reorientation of polarization in the ferroelectric barrier enables the resistance of the FTJ to be tuned continuously. As a

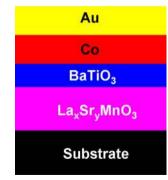

result, the FTJ device has exhibited a tunable, hysteretic, and nonvolatile resistive switching behaviour that resembles the memristive character of the theoretical memristor [15]. Under this circumstance, the concept of the FTJ-based memristor has recently been proposed and been explored intensively. To date, the reported ferroelectric memristor architecture usually comprises a BaTiO<sub>3</sub> film deposited on La<sub>x</sub>Sr<sub>y</sub>MnO<sub>3</sub> layer, which are sandwiched by two electrodes [15, 16]. Figure 8 shows such a heterostructure.

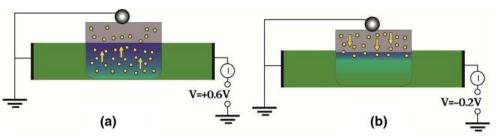

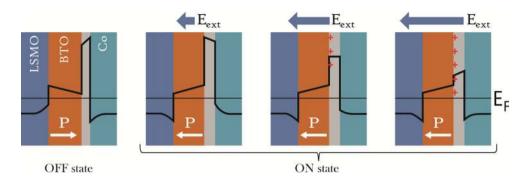

The resistive switching behaviour of the ferroelectric memristor has been commonly considered as a result of the reversal of the dielectric polarization in the ferroelectrics. It should be noticed that for a thin ferroelectric film that can however sustain its ferroelectricity, the surface charge in the ferroelectric are not completely screened by the adjacent metals, thus allowing for a non-zero depolarizing electric field in the ferroelectric layer. The resulting electrostatic potential in adjunction with this field strongly depends on the direction of the dielectric polarization. In this case, as the FTJ is usually made of metal electrodes with different screening lengths, an asymmetric potential profile for the opposite polarization direction is present [49]. This would change the potential seen by transport electrons, thereby leading to the change of the resistance. Nevertheless, a recently proposed hypothesis has ascribed the resistive switching behaviour of FTJ to the field-induced charge redistribution at the ferroelectric/electrode surfaces [16]. This explanation postulates that charge migration and accumulation at the metal/ferroelectric interface facilitated by its defect structure plays a very essential role on the effect of the resistive switching [9, 50]. The oxidation of the metal electrode can give rise to the formation of the passive dielectric layer with an increased density of oxygen vacancies at the top ferroelectric interface in the low based pressure (LBP)-processed FTJ heterostructure. The barrier height associated with this layer is higher in comparison with the barrier of the ferroelectric layer and significantly contributes to the resistance behaviour. In this case, a positive excitation applied

Fig. 8 A cross-section of the FTJ used for ferroelectric memristor

to the top electrode can accumulate the oxygen vacancies at the metal oxide/ferroelectric interface, whereby the barrier height can be effectively reduced and the resistance of the 'ON' state can be also decreased. A negative bias induces a dissipation of accumulated charges at the interface and/or a reduction of metal oxide at the interface, switching the heterostructure into the high-resistance state. Such a mechanism is illustrated in Fig. 9.

## 5 Manganite memristor

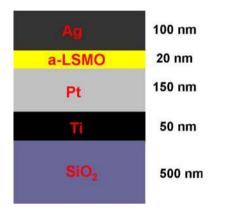

Perovskite manganite material has recently elicited considerable interest mainly due to its extraordinary features including colossal magnetoresistance effect, spin-orbitcharge order, 100 % spin polarization and intrinsic electronic phase separation [51, 52]. However, its capability of providing memristive functionality remains mysterious until very recently an amorphous  $La_{1-x}Sr_xMnO_3$  (a-LSMO)-based memristor has been successfully fabricated. As illustrated in Fig. 10, the layered structure of this manganite memristor comprises an a-LSMO thin film sandwiched by an Ag top electrode and a Pt bottom electrode, which are deposited onto the Ti/SiO<sub>2</sub>/Si substrate via radio frequency magnetron sputtering. Analogous to other memristors, the EPIR switching effect can be also observed in the fabricated device, and the experimentally measured I-V curve has clearly exhibited a pinched hysteresis loop, thereby demonstrating its memristive character.

The resistive switching mechanism of the manganite memristor has been mainly attributed to the forming of the Ag nanobridge [18]. When the Ag top electrode is positively biased, thanks to the electrochemical potential difference, the anode starts to dissolves, resulting in the presence of the Ag<sup>+</sup> cations. Driven by the strong electric field, the Ag<sup>+</sup> cations migrates across the LSMO layer, and reaches the Pt bottom electrode where the neutralization process from Ag<sup>+</sup> cation to Ag atom takes places due to the cathodic deposition reaction. As a consequence, more Ag atoms will be precipitated near the Pt bottom electrode and finally form an Ag nanofilament connecting the top electrode with the bottom electrode, corresponding to LRS. In order to achieve HRS, the top electrode is negatively biased, which would dissolve the Ag nanofilament. The ability to display pinched hysteresis loop under high excitation frequency using the manganite memristor has been demonstrate [19]. In addition, the manganite memristor also shows continuously tuneable synapselike resistance and stable endurance (up to 1000 set-reset pulse cycles) as well as an OFF/ON resistance ratio up to  $10^2$  [20]. These attractive features would endow the manganite memristor with the potential to imitate the biological synapses that is considered as the key component of the brainlike computer.

Fig. 9 Schematic illustration of the energy barrier diagrams for the OFF and ON states as a function on the external electric field  $E_{ext}$ . The *gray layer* between the Co and BTO layers is the passive dielectric layer of  $CoO_x$ . Under a positive bias applied to the top

Fig. 10 The cross-sectional view of the a-LSMO based manganite memristor

## 6 Resonant-tunneling diode memristor

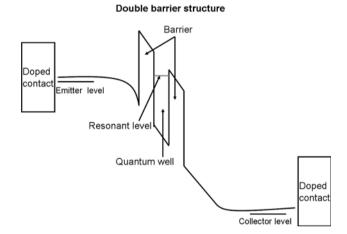

A RTD is a diode with a resonant-tunneling structure in which electrons can tunnel through some resonant states at certain energy levels. RTD can be made of various semiconductor materials and can have different resonant tunnelling structures such as double barrier, triple barrier, quantum wire, and quantum dot [53]. The RTD device configuration with a double layer structure is schematically shown in Fig. 11.

As can be seen from Fig. 11, two contacts made of heavily doped, narrow energy-gap materials sandwich the emitter region, a quantum well between two barriers, and a collector region. Note that the quantum well is fabricated using the small bandgap semiconductor, whereas the barriers are made of the large bandgap materials. When the RTD is biased, the electrons previously trapped in the emitter gain energy from the resulting electric field and can therefore tunnel through the quantum well towards the collector, leading to an increase on the current. Based on the aforementioned mechanism, a double layer structured AlAs/GaAs/AlAs RTD containing special doping design of electrode, oxygen vacancies accumulate at the  $CoO_x/BTO$  interface, effectively reducing the barrier height and decreasing the resistance of the 'ON' state. Reprinted with permission from [16]

Fig. 11 The energy band diagram of the RTD under double barrier structure. Along with the increase of the bias voltage, the emitter level would rise relative to the resonant level, and the maximum current is reached at the instant when the emission level coincides with the resonant level. After that, further increasing voltage would lower the resonant level and the current is reduced, leading to the negative differential resistance (NDR) effect

the spacer layers in the source and drain regions was found to exhibit a bow-tie I–V curve [21, 22], indicating a sine qua non of a memristor. However, no further achievements have been made in this field until 2012 when a programmable quantum-dots memristor based on an analog cellular neural network (CNN) architecture was developed for image processing applications such as edge and line detections [54, 55].

# 7 Spintronic memristor

Differing from aforementioned memristors, spintronic memristor changes its resistance by varying the direction of the spin of the electrons [56]. Research interests in spintronic memristor stem from the recent advances in the

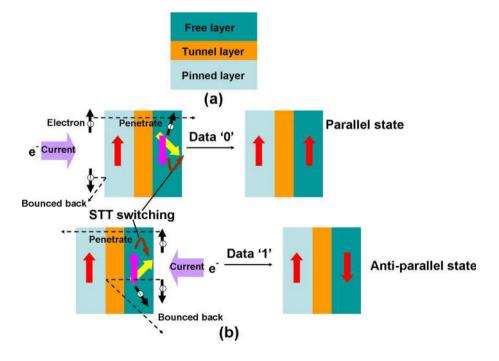

development of the spin-transfer torque (STT) random access memory technologies [57, 58]. The fundamental physics behind STT is that when applying a current through a magnetic layer, the spins of electrons that constitute the current will be aligned to the magnetization orientation, which is known as spin-polarization, and these spins can be repolarized if such a spin-polarized current is directed into another magnet. During the repolarization process, the magnetic layer is subjected to a torque that can stimulate spin-wave excitations or flip the magnetization direction of the magnetic layer at sufficiently high current density [59]. According to this mechanism, the STT based magnetic tunnelling junction (MTJ) can be switched between a LRS and a HRS using the spin-polarized current induced between two ferromagnetic layers. The cell structure shown in Fig. 12a shows the switching of STT-MTJ from the anti-parallel orientation to the parallel orientation [60]. In order to induce such a switching, the electrons should flow from the pinned layer with a fixed magnetization to the free layer whose magnetization can be easily rotated. The electrons that have the same spin direction as that of the magnetization in the pinned layer would remain to form the spin polarized current after they cross through the pinned layer. Subsequently this spin polarized current flows through the free layer that is subjected to the torque resulting from the spin angular momentum of the polarized current. This enables the magnetic state of the free layer to be changed if the torque is sufficiently stronger than the threshold value. To achieve the switching from parallel orientation to anti-parallel orientation shown in Fig. 12b, the electrons should flow from the free layer to the pinned layer. Once the electrons reach the pinned layer, the electrons with the same spin direction as that of the pinned layer would pass through the pinned layer, while others will be reflected at the boundary between the insulator and the pinned layer and bounced back to the free layer. This reflection would produce the spin transfer torque on the free layer and switch the magnetization of the free layer when exceeding the threshold value.

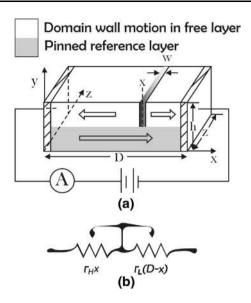

The aforementioned physical mechanism can be directly utilized to build the spintronic memristor. As shown in Fig. 13, the spintronic memristor is still made up of a reference layer and a free layer. The magnetization of the reference layer is fixed via its connection to a pinned magnetization layer, while a domain wall is deployed to split the free layer into two sections with opposite magnetizations against each other. Similar to the STT-MTJ, when the magnetization of the free layer in a section is in a parallel/anti-parallel direction to the reference layer, the resistance per unit length of the section is low/high. As a consequence, applying the polarized current with the same direction as the magnetization of the reference layer would parallel the magnetization orientation between the reference layer and the free layer, thus resulting in a low system resistance. On the other hand, applying the polarized current with the opposite direction to the magnetization of the reference layer would anti-parallel the magnetization orientation between both layers, which therefore gives rise to a high resistance. Based on the above description, the memristance of the spintronic memristor that depends on domain-wall position can be written as [61]:

Fig. 12 a The MTJ structure and **b** spin transfer torque magnetization switching from anti-parallel to parallel (top) and from parallel to anti-parallel (bottom). Note that for both cases, the electrons with the same polarization as the pinned layer will penetrate through the MTJ, while the electrons with the opposite polarization to the pinned layer would be bounced back either at the pinned layer interface or the insulated layer interface. Reprinted with permission from [60]

Fig. 13 A spintronic memristor based on magnetic-domain wall motion. a Structure b equivalent circuit. Reprinted with permission from [61]

$$M(x) = r_{\rm H} \cdot x + r_{\rm L} \cdot (D - x) \tag{5}$$

where  $r_{\rm H}$  and  $r_{\rm L}$  are the resistance per unit length when magnetizations of the free and reference layers are antiparallel and parallel respectively; *x* is the position of the domain wall, and *D* is the length of the free layer. The domain wall velocity *v* in this case is proportional to current density *J*, given as:

$$v = \frac{\mathrm{d}x}{\mathrm{d}t} = \Gamma \cdot J = \frac{\Gamma}{h \cdot z} \cdot \frac{\mathrm{d}q}{\mathrm{d}t} \tag{6}$$

where  $\Gamma$  is the domain wall velocity coefficient depending on the device structure and material property; *h* and *z* represent the thickness and the width of the device. Then the memristance of the spintronic memristor can be reexpressed as:

$$M(q) = r_{\rm L} \cdot D + (r_{\rm H} - r_{\rm L}) \frac{\Gamma}{h \cdot z} q(t)$$

(7)

Accordingly, by moving the position of the domain wall in the free layer, it is possible to continuously change the device memristance. As the writing operation in spintronic memristor is achieved by applying a current through the magnet itself rather than generating a very strong reversal field, it is advantageous for spintronic memristor to offer lower power consumption than the conventional memristor devices. Besides, spintronic memristor has given up the necessity to use an additional metal line as the current path, thus resulting in a better scalability. However, the small resistance ON/OFF ratio remains a big concern for spintronic memristor [40].

#### 8 Conclusion

As the conventional CMOS memories will approach its physical limits in the near future, memristor has recently received considerable attention and been considered as the next generation electronic device due to the inherent nonvolatility, low power consumption, high stability, and good scalability, in conjunction with its widespread applications such as neuromorphic circuit and image processing. Within these emerging memristor devices, more research enthusiasm is currently dedicated to the resistive memristor. This is expected because the key component of the first memristor that can physically realize the theoretical prediction of Chua is made of the resistive material (TiO<sub>2</sub> in this case). In addition, a mundane, but less important fact is that the resistive memristor can benefit from a wealth of previous knowledge on ReRAM technology. Thanks to the aforementioned superiorities to other competitors, resistive memristor is capable of accomplishing most of the memristor traits postulated by Chua. The main challenge that the resistive memristor is facing is that it does not provide a direct relation between the magnetic flux and the charge. Besides, the device fabrication is complex and may face some issues when merged with CMOS technology. In comparison with the resistive memristor, spintronic memristor has directly linked the charge with the magnetic flux. Nevertheless, the feasibility of fabricating spintronic memristor on nano-scale dimension is strongly challenged due to the presence of the moving domain-wall. Moreover, any structure variation on the fabrication process may affect the memristance value, thus influencing the system stability. Polymeric memristor exhibits a closer memristive hehavior to Chua's prediction than the resistive memristor. However, in order for polymeric memristor to rival with the resistive memristor, the resistance ratio and the stability are two main issues that need to be addressed soon. The ability to provide a wide resistance tenability, a large resistance ratio (about 10<sup>3</sup>), long data retention time, and great robustness using ferroelectric memristor has also been demonstrated [62, 63], which makes ferroelectric memristor a very prospective contender for applications in nonvolatile memories and logic devices. Nevertheless, as ferroelectric material will lose its ferroelectric characteristic at a very thin thickness, the difficulty in downscaling ferroelectric memristor cell has posed a strong limit to its density improvement. Manganite memristor and RTD memristor are still in their infancy and it would be difficult for them to rival the mainstream memristors without the advent of some innovative technologies that can remarkably facilitate the performance enhancement.

Acknowledgments The authors acknowledge the financial supports of the National Natural Science Foundation of China under Grant

Nos. 61201439, 61202319, 61402218, the scientific and technical bureau of JiangXi Province under Grant No. 20142BAB217013, the Educational Bureau of JiangXi Province under Grant Nos. GJJ13487, GJJ14540 and the Key laboratory of Image Processing and Pattern Recognition (Nanchang Hangkong University) Grant No. 20142BAB217013.

#### References

- 1. L.O. Chua, IEEE Trans. Circuit Theory 18, 507 (1971)

- 2. L.O. Chua, S.M. Kang, Proc. IEEE 64, 209 (1976)

- D.B. Strukov, G.S. Snider, D.R. Stewart, R.S. Williams, Nature 453, 80 (2008)

- 4. L.O. Chua, Appl. Phys. A 102, 765 (2011)

- 5. L.O. Chua, Proc. IEEE 100, 1920 (2012)

- 6. L.O. Chua, Nanotechnology 24, 383001 (2013)

- 7. L.O. Chua, Semicond. Sci. Technol. 29, 104001 (2014)

- 8. Y.P. Ho, G.M. Huang, P. Li, Proc. IEEE ACM. 485 (2009)

- J.J. Yang, M.D. Pickett, X.M. Li, D.A.A. Ohlberg, D.R. Stewart, R.S. Williams, Nat. Nanotechnol. 3, 429 (2008)

- J. Borghetti, G.S. Snider, P.J. Kuekes, J.J. Yang, D.R. Stewart, R.S. Williams, Nature 464, 873 (2010)

- Y.C. Yang, P. Gao, S. Gaba, T. Chang, X.Q. Pan, W. Lu, Nat. Commun. 3, 732 (2012)

- V. Erokhin, T. Berzina, P. Camorani, M.P. Fontana, Colloids Surf. A 321, 18 (2008)

- T. Berzina, A. Smerieri, M. Bernabo, A. Pucci, G. Ruggeri, V. Erokhin, M.P. Fontana, J. Appl. Phys. 105, 124515 (2009)

- 14. V. Erokhin, ISCAS Tech Dig. 5 (2010)

- A. Chanthbouala, V. Garcia, R.O. Cherifi, K. Bouzehouane, S. Fusil, X. Moya, S. Xavier, H. Yamada, C. Deranlot, N.D. Mathur, M. Bibes, A. Barthelemy, J. Grollier, Nat. Mater. 11, 860 (2012)

- D.J. Kim, H. Lu, S. Ryu, C.-W. Bark, C.-B. Eom, E.Y. Tsymbal, A. Gruverman, Nano Lett. **12**, 5697 (2012)

- Z.H. Wang, W.S. Zhao, W. Kang, Y. Zhang, J.-O. Klein, D. Ravelosona, C. Chappert, Appl. Phys. Lett. **104**, 053505 (2014)

- D.Q. Liu, H.F. Cheng, X. Zhu, G. Wang, N. Wang, ACS Appl. Mater. Interfaces 5, 11258 (2013)

- D.Q. Liu, C.Y. Zhang, G. Wang, Z.Z. Shao, X. Zhu, N. Wang, H.F. Cheng, J. Phys. D Appl. Phys. 47, 085108 (2014)

- M.L. Wu, C.P. Yang, D.W. Shi, R.L. Wang, L.F. Xu, H.B. Xiao, K. Baerner, AIP Adv. 4, 047123 (2014)

- 21. F.A. Buot, A.K. Rajagopal, J. Appl. Phys. 76, 5552 (1994)

- K.K. Gullapalli, A.J. Tsao, D.P. Neikirk, Appl. Phys. Lett. 62, 2971 (1993)

- 23. X.B. Wang, Y.R. Chen, H.W. Xi, H. Li, D. Dimitrov, IEEE Electron Dev Lett. **30**, 294 (2009)

- 24. M. Elshamy, H. Mostafa, M.S. Said, CCECE Tech Dig. 1 (2014)

- 25. R. Waser, R. Dittmann, G. Staikov, K. Szot, Adv. Mater. 21, 2632 (2009)

- A.Q. Jiang, C. Wang, K.J. Jin, X.B. Liu, J.F. Scott, C.S. Hwang, T.A. Tang, H.B. Lu, G.Z. Yang, Adv. Mater. 23, 1277 (2011)

- F. Pan, C. Chen, Z.-S. Wang, Y.-C. Yang, J. Yang, F. Zeng, Prog. Nat. Sci. Mater. Int. 20, 1 (2010)

- 28. F. Pan, S. Gao, C. Chen, C. Song, F. Zeng, Mater. Sci. Engin. R. 83, 1 (2014)

- 29. E. Gale, Semicond Scie Technol. 29, 104004 (2014)

- 30. A. Kumar, M.S. Baghini, Electron. Lett. 50, 1547 (2014)

- A.J. Lohn, J.E. Stevens, P.R. Mickel, M.J. Marinella, Appl. Phys. Lett. 103, 063502 (2013)

- A.C. Torrrezan, J.P. Strachan, G. Medeiros-Ribeiro, R.S. Williams, Nanotechnology 22, 485203 (2011)

- J.S. Meena, S.M. Sze, U. Chand, T.-Y. Tseng, Nanoscale Res. Lett. 9, 526 (2014)

- 34. F. Zhang, X. Gan, X. Li, L. Wu, X. Gao, R. Zheng, Y. He, X. Liu, R. Yang, Electrochem. Solid State Lett. 14, 422 (2011)

- 35. L. Liborio, N. Harrison, Phys. Rev. B. 77, 104104 (2008)

- 36. D.-H. Kwon, K.M. Kim, J.H. Jang, J.M. Jeon, M.H. Lee, G.H. Kim, X.-S. Li, G.-S. Park, B. Lee, S. Han, M. Kim, C.S. Hwang, Nat. Nanotechnol. 5, 148 (2010)

- 37. X. Liu, I. Kim, M. Siddik, S.M. Sadaf, K.P. Biju, S. Park, H. Hwang, J. Korean, Phys. Soc. 59, 497 (2011)

- J.J. Yang, I.H. Inoue, T. Mikolajick, C.S. Hwang, Mater. Res. Soc. Bull. 37, 131 (2012)

- 39. M.D. Ventra, Y.V. Pershin, Materialstoday 14, 584 (2011)

- M.J. Rozenberg, I.H. Inoue, M.J. Sanchez, Appl. Phys. Lett. 88, 033510 (2006)

- 41. B.J. Choi, J. Appl. Phys. 98, 33715 (2005)

- M.H. Tang, Z.P. Wang, J.C. Li, Z.Q. Zeng, X.L. Xu, G.Y. Wang, L.B. Zhang, Y.G. Xiao, S.B. Yang, B. Jiang, J. He, Semicond. Sci. Technol. 26, 075019 (2011)

- D. Ielmini, F. Nardi, C. Cagli, IEEE Trans. Electron Devices 58, 3246 (2011)

- 44. E.T. Kang, K.G. Neoh, K.L. Tan, Prog. Polym. Sci. 23, 277 (1998)

- T. Berzina, V. Erokhin, M.P. Fontana, J. Appl. Phys. 101, 024501 (2007)

- 46. Y. Chen, G. Liu, C. Wang, W.B. Zhang, R.-W. Li, L.X. Wang, Mater. Horiz. 1, 489 (2014)

- 47. L. Wang, S. Gai, Contemp. Phys. 55, 75 (2014)

- L. Wang, C.-H. Yang, S. Gai, J. Wen, Curr. Nanosci. 10, 638 (2014)

- Z.Q. Hu, Q. Li, M.Y. Li, Q.W. Wang, Y.D. Zhu, X.L. Liu, X.Z. Zhao, Y. Liu, S.X. Dong, Appl. Phys. Lett. **102**, 102901 (2013)

- K. Praveena, K.B.R. Varma, J. Mater. Sci. Mater. El. 25, 3103 (2014)

- 51. Y. Tokura, Y. Tomioka, J. Magnet, Magn. Mater. 200, 1 (1999)

- 52. E. Daggoto, T. Hotta, A. Moreo, Phys. Rep. 344, 1 (2001)

- 53. J.P. Sun, G. Haddad, Proc. IEEE 86, 641 (1998)

- 54. Y. Yilmaz, P. Mazumder, Proc. IEEE-NANO. 1 (2012)

- 55. Y. Yilmaz, P. Mazumder, IEEE Trans. Nanotechnol. 12, 879 (2013)

- 56. S.P. Mohanty, IEEE Potentials 32, 34 (2013)

- 57. T. Kawahara, K. Ito, R. Takemura, H. Ohno, Microelectron. Reliab. 52, 613 (2012)

- I.L. Prejbeanu, S. Bandiera, J.A. Herault, R.C. Sousa, B. Dieny, J.P. Nozieres, J. Phys. D Appl. Phys. 46, 074002 (2013)

- 59. N.D. Rizzo, D. Houssameddine, J. Janesky, R. Whig, F.B. Mancoff, M.L. Schneider, M. Deherrera, J.J. Sun, K. Nagel, S. Deshpande, H.-J. Chia, S.M. Alam, T. Andre, S. Aggarwal, J.M. Slaughter, IEEE Trans. Magn. 49, 4441 (2013)

- K.C. Chun, H. Zhao, J.D. Harms, T.-H. Kim, J.-P. Wang, C.H. Kim, IEEE J. Solid-State Circuits 48, 598 (2013)

- 61. Y.R. Chen, H. Li, X.B. Wang, ICCCAS, 811 (2010)

- D.S. Jeong, R. Thomas, R.S. Katiyar, J.F. Scott, H. Kohlstedt, A. Petraru, C.S. Hwang, Rep. Prog. Phys. 75, 076502 (2012)

- L. Wang, C.-H. Yang, J. Wen, S. Gai, J. Nanomaterials 2014, 927696 (2014)

🖉 Springer