Received 2 December 2018; revised 27 January 2019; accepted 30 January 2019. Date of publication 7 February 2019; date of current version 8 March 2019. The review of this paper was arranged by Editor A. G. U. Perera.

Digital Object Identifier 10.1109/JEDS.2019.2897642

# Oxide TFT Rectifiers on Flexible Substrates Operating at NFC Frequency Range

# BHAWNA TIWARI<sup>1</sup>, PYDI GANGA BAHUBALINDRUNI<sup>®</sup><sup>2</sup>, ANA SANTA<sup>3</sup>, JORGE MARTINS<sup>®</sup><sup>3</sup>, PRIYANKA MITTAL<sup>1</sup>, JOÃO GOES<sup>4</sup> (Senior Member, IEEE), RODRIGO MARTINS<sup>®</sup><sup>3</sup>, ELVIRA FORTUNATO<sup>3</sup>, AND PEDRO BARQUINHA<sup>3</sup>

1 Deparment of Electronics and Communication Engineering, Indraprastha Institute of Information Technology Delhi, New Delhi 110020, India 2 School of Electrical Sciences, Indian Institute of Technology Goa, Ponda 403401, India 3 CENIMAT/I3N, Departamento de Ciência dos Materiais, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa, CEMOP, UNINOVA, 2829-516 Caparica, Portugal 4 Department of Electrical Engineering, Universidade NOVA de Lisboa, CTS, UNINOVA, 2829-516 Caparica, Portugal

CORRESPONDING AUTHOR: P. G. BAHUBALINDRUNI (e-mail: bpganga@iitgoa.ac.in)

This work was supported in part by the Fundo Europeu de Desenvolvimento Regional (FEDER, European Regional Development Fund) through the COMPETE 2020 Programme, in part by the National Funds through Portuguese Foundation for Science and Technology under Project POCI-01-0145-FEDER-007688, Project UID/CTM/50025, Project PEST-OE/EEI/UI0066/2013, and Grant SFRH/BD/122286/2016, in part by the European Community H2020 Program under Grant 716510 (ERC-2016-STG TREND) and Grant 692373 (BET-EU), and in part by the Early Career Research Grant under Project ECR/2017/000931.

**ABSTRACT** This paper presents the experimental characterization of different rectifier circuits using indium–gallium–zinc-oxide thin-film transistor technologies either at NFC or a high frequency range (13.56 MHz) of RFID. These circuits include a single ended rectifier, its differential counterpart, a bridge rectifier, and a cross-coupled full wave rectifier. Diodes were implemented with transistors using conventional processing steps, without requiring short channel devices ( $L=15 \mu m$ ). Hence, there is no need for either extra masks or processing steps unlike the Schottky diode-based implementation. These circuits were fabricated on a PEN substrate with an annealing temperature not exceeding 180 °C. This paper finds a direct application in flexible low-cost RFID tags since they enable integration of the required electronics to implement tags with the same fabrication steps.

**INDEX TERMS** a-IGZO TFT, rectifiers, flexible electronics, RFID tags.

## I. INTRODUCTION

RFIDs are playing a vital role in many applications spanning from item level tracking in warehouse, supply chain to security [1]. In near field communication range (< 1 m) high frequency (HF) passive RFID tags can become even more attractive in tremendous applications if they can be implemented on flexible substrates with low cost. Indium-Gallium-Zinc-Oxide Thin-Film Transistors technology (IGZO TFT) is a perfect choice to implement HF passive RFID tags due to unique technology advantages, such as, compatibility with low-cost and low-temperature fabrication techniques [2], [3]. Moreover, robust operation under mechanical stress can be achieved by using thin flexible substrates and considering neutral strain point principles for stack design [4].

A typical RFID or NFC system with a passive tag is shown in Fig. 1. Passive tags do not require on-chip power supply. When the reader sends a signal to the tag, the printed antenna in the tag receives the RF signal. In order to receive maximum power, a proper matching network is needed. This RF energy will be converted into DC with the help of a rectifier circuit, where this DC voltage acts as the supply for the digital circuits in the tag. Based on the data driven by this digital circuit the modulation element (a simple TFT) together with antenna sends the data to the reader for identity verification. It can be noticed that the rectifier is one of the important functional blocks in this passive tag.

Many works have been reported on rectifiers implementation with organic and oxide TFT technology [5]–[12]. The cross-coupled rectifier output amplitude is compromised at 13.56 MHz due to inferior mobility of organic TFTs [5]. Though lower frequency of operation is noticed from [6], cross-coupled designs with oxide TFTs [7], [8] have shown superior performance at this frequency. In fact, the fullwave and halfwave rectifier reported in [9] and [10] are able to

2168-6734 © 2019 IEEE. Translations and content mining are permitted for academic research only. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

FIGURE 1. Typical RFID communication block diagram.

meet UHF range with schottky diodes. While [9] reports rectifier on glass, the rectifier reported in [10] is on flexible substrate. Coming to the schottky diode based implementation, the processing steps and masks are different from the conventional TFT fabrication process, which increases the fabrication cost.

It should be noted that when the complete RFID tag is being implemented with same processing steps without increasing the number of masks, low fabrication cost can be attained, which is the main requirement of many real world applications that need RFIDs. It is also worth to note that all reported works with oxide TFTs [7], [8] are limited to high temperatures (> 300°C) and rigid substrates, whereas, real-world applications mostly demand electronics on flexible substrates. In addition, [11], [12] report interesting works on RFID tags using organic p-type TFTs on foil. Here, the complete system and the rectifiers are operated at a supply voltage > 18 V whereas, low power IOT system demands low supply voltages. As a route to overcome these limitations, the present work reports and compares, for the first time ever, rectifiers with different architectures based on a low-temperature flexible oxide TFT process, able to achieve 13.56 MHz operating frequency with only <6 V supply voltage. The process is fully compatible with polyethylene naphthalate (PEN) substrates and makes use of large-sized transistors (L=15  $\mu$ m), fully compliant with current large area electronics fabrication tools. Note that the adoption of miniaturized devices (e.g., L=2  $\mu$ m), besides imposing many challenges to conventional lithographic tools, can bring undesirable short-channel effects [13].

#### **II. DEVICE AND CIRCUIT FABRICATION**

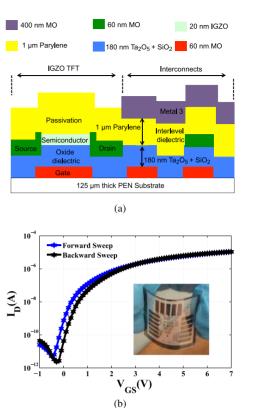

A 60 nm thick Mo gate electrode is sputtered on a  $125 \,\mu$ m thick PEN substrate. Then, a 180 nm thick multilayer/multicomponent dielectric is cosputtered without intentional substrate heating, using SiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> targets, followed by dry etching process in SF<sub>6</sub> atmosphere; A 20 nm thick semiconductor layer is then deposited without intentional substrate heating, using ceramic IGZO target (In:Ga:Zn atomic ratio of 2:1:2) and Ar+O<sub>2</sub> atmosphere and patterned by liftoff. Source and drain electrodes are sputtered with 60 nm thick Mo. Gate, dielectric and source/drain

**FIGURE 2.** (a) Cross sectional view of the TFT and interconnects adopted in this work (b) Linear transfer characteristics of a single TFT with  $W = 320 \,\mu\text{m}$  and  $L = 15 \,\mu\text{m}$  at  $V_{DS} = 0.1 \,V$ . Subset containing individual TFTs, rectifiers and other circuits fabricated on a  $125 \,\mu\text{m}$  thick PEN flexible substrate.

patterning is done by dry etching process in SF<sub>6</sub> atmosphere; The interlevel dielectric is  $1 \,\mu m$  thick parylene layer, patterned using a dry etching process in O<sub>2</sub> atmosphere; On top of this layer, metal 3 is deposited: by sputtering 400 nm thick Mo, followed by dry etching process in  $SF_6$ atmosphere. The devices were annealed at 180°C for 1 hour in air before source/drain deposition and at the end of the process. The cross sectional schematic view of the IGZO TFT and interconnects are presented in Fig. 2(a). In order to minimize the parasitics due to interconnects (overlap of gate to source/drain) and to further improve the yield of the process for circuits operation with this technology, metal 3 (400 nm thick Mo) is being used. This brings the additional advantage of achieving IGZO backchannel surface passivation with the interlevel dielectric, i.e., no extra processing steps are required to assure robust operation of the TFTs. Inset of Fig. 2(b) shows a PEN substrate containing isolated TFTs and various circuits including rectifiers. It also demonstrates linear transfer characteristics of the TFT with W =  $320 \,\mu m$  and L =  $15 \,\mu m$ . These devices are showing a turn-on voltage of -0.5 V, mobility of 12 cm<sup>2</sup>/V.s and on-off ratio exceeding 10<sup>7</sup>. Small clockwise hysteresis, concomitant with charge trapping phenomena at dielectric/semiconductor interface, is noticed from the plot.

Transistor performance is unaffected by bending radius of at least 15 mm [14].

#### **III. CIRCUIT DESIGN**

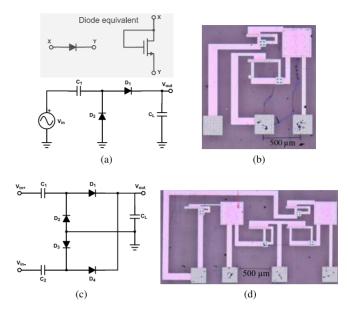

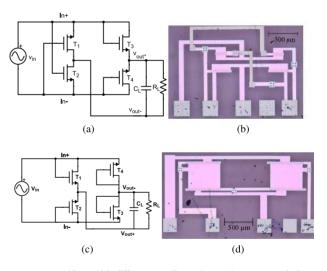

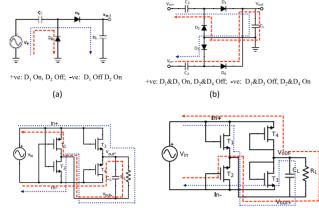

Four rectifier circuits are being considered in this work; (i) Single ended (ii) Differential (iii) Cross-coupled and (iv) Bridge. All these circuits are implemented with the IGZO TFTs and their circuit schematics and micrographs are presented in Figs. 3 and 4. In these circuits, the conductive path during positive and negative half cycles are being demonstrated by red dashed line and violet dotted line, respectively, as can be noticed from Fig. 5. In single ended implementation, the input capacitor  $(C_1)$  blocks the dc value and feeds only signal to diodes  $(D_1 \text{ and } D_2)$ . During positive half cycle,  $D_1$  turns 'ON' and  $D_2$  turns off. The load capacitor charges with the current flowing in the circuit and  $V_{out}$  is almost equal to one threshold voltage ( $V_{TH}$ ) less than  $V_{in}$ , i.e.,  $V_{in} - V_{TH}$ , where  $V_{TH}$  drop is due to diode-connected TFT used for realizing  $D_1$ . During the negative half cycle these diodes interchange their roles and  $C_1$ is connected to ground. When there is a no leakage path at the output, the same voltage level at previous positive half cycle is maintained at the output. The operating principle can be adapted to the differential version implementation (see Fig. 5(b)). This acts as a full wave rectifier. Especially when there is finite resistive load, full wave rectifier gives improved output compared to the single ended or half wave counter part, as there is always a conductive path in the circuit for both positive and negative half cycle of the input. Same analysis can be applied to the cross-coupled and bridge rectifiers. Their conductive paths for different inputs can be observed in Fig. 5(c) and (d). Differential output in case of bridge rectifier is almost  $2(V_{in} - V_{TH})$ , whereas, in the cross-coupled design, one  $V_{TH}$  drop is being replaced with the overdrive voltage  $(V_{OD})$  of  $T_1$  or  $T_2$  (see Fig. 5(c)). By making these TFTs wider, it is possible to reduce the overdrive voltage and improve output dc compared to the bridge rectifier.

#### **IV. RESULTS AND DISCUSSION**

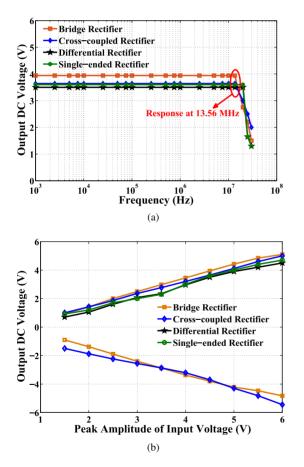

All the measurements were carried out at normal ambient with the help of passive agilent oscilloscope probes ( $10 M\Omega//15 \text{ pF}$ ) and fixed probe with keysight B1500A. The frequency response and voltage transfer characteristics (output dc voltage *versus* input ac voltage peak value) can be noticed at 13.56 MHz from Fig. 6. Expected  $V_{TH}$  drop can be observed from the voltage transfer characteristics, where  $V_{TH}$  variations are within  $\pm 0.2 \text{ V}$ . For these circuits, TFTs have a channel length of 15  $\mu$ m and widths are ranging from 80 to 320  $\mu$ m.

At higher frequencies (> 15 MHz), the output voltage is degraded significantly, since it is expected that the transistors cannot show proper functionality beyond their unity gain current cutoff frequency [13]. At these high frequencies, there is not enough time for the devices to form the

FIGURE 3. Rectifiers with different configurations: (a) Single ended circuit schematic (b) Single ended micrograph (c) Differential rectifier circuit schematic (d) Differential rectifier micrograph. All diodes in these schematics are being implemented with diode-connected transistors as shown in Fig. 3 (a).

FIGURE 4. Rectifiers with different configurations: (a) Cross coupled rectifier circuit schematic (b) Cross-coupled rectifier micrograph (c) Bridge rectifier circuit schematic (d) Bridge rectifier micrograph.

conductive channel in 'ON' state and discharge the complete channel charge, when it moves to the 'OFF' state. Nevertheless, operational yield of the rectifiers at NFC range can be improved by decreasing the TFT's channel length and/or decreasing gate-to-source/drain overlaps [13]. Though bridge rectifier is showing slightly higher voltage at the output compared to other configurations due to nominal  $V_{TH}$ variations, by employing wider devices, cross-coupled configuration can ensure improved output voltage since  $V_{TH}$ drop will be replaced by the  $V_{OD}$  of the TFT. As the device becomes wider,  $V_{OD}$  can be close to zero volts. In fact, by replacing the diode connected TFTs in Fig. 5(c), with

+ve:  $T_2\&T_3$  On,  $T_1\&T_4$  Off; -ve:  $T_2\&T_3$  Off;  $T_1\&T_4$  On +ve:  $T_1\&T_3$  On,  $T_2\&T_4$  Off; -ve:  $T_1\&T_3$  Off;  $T_2\&T_4$  On (c) (d)

FIGURE 5. Circuit operation during positive (conductive path denoted by red line) and negative (conductive path denoted by violet line) half cycle of the input: (a) Single ended (b) Differential (c) Cross-coupled [8] (d) Bridge rectifier.

**FIGURE 6.** Rectifiers measured response: (a) Frequency response with an input signal peak voltage of 4.5 V (b) Amplitude sweep when the input signal frequency is 13.56 MHz.

cross-coupled TFTs, it is possible to eliminate voltage drop in the circuit and output voltage can be equal to the peak value of the input voltage, if there is no discharging path at the output.

# **V. CONCLUSION**

This work analysed different rectifiers from flexible substrates for NFC applications. Expected behaviour can be noticed from measured result at relatively low voltages to ensure low-power operation, without requiring miniaturized devices for 13.56 MHz operation. Since all the rectifiers were fabricated with the same processing steps and masks as the standard oxide TFT fabrication process at low temperature, this work opens a window for low-cost flexible RFID tags that can be used in different applications ranging from item level tracking to security.

### ACKNOWLEDGMENT

The authors would like to thank Prof. Vitor Tavares for the PDK files. This publication is also an outcome of the R&D work undertaken project under the Visvesvaraya Ph.D. Scheme of Ministry of Electronics & Information Technology, Government of India, being implemented by Digital India Corporation.

#### REFERENCES

- K. Finkenzeller, *RFID Handbook: Fundamentals and Applications in Contactless Smart Cards, Radio Frequency Identification and Near-Field Communication.* Chichester, U.K.: Wiley, 2010. doi: 10.1002/9780470665121.

- [2] K. Nomura *et al.*, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, Oct. 2004.

- [3] T. Kamiya, K. Nomura, and H. Hosono, "Present status of amorphous In–Ga–Zn–O thin-film transistors," *Sci. Technol. Adv. Mater.*, vol. 11, no. 4, 2010, Art. no. 044305.

- [4] Y.-H. Kim, E. Lee, J. G. Um, M. Mativenga, and J. Jang, "Highly robust neutral plane oxide TFTs withstanding 0.25 mm bending radius for stretchable electronics," *Sci. Rep.*, vol. 6, May 2016, Art. no. 25734.

- [5] R. Rotzoll *et al.*, "Radio frequency rectifiers based on organic thin-film transistors," *Appl. Phys. Lett.*, vol. 88, no. 12, 2006, Art. no. 123502.

- [6] S. H. Cho *et al.*, "Oxide thin film transistor circuits for transparent RFID applications," *IEICE Trans. Electron.*, vol. E93.C, no. 10, pp. 1504–1510, 2010.

- [7] B. R. McFarlane *et al.*, "AC/DC rectification with indium gallium oxide thin-film transistors," *IEEE Electron Device Lett.*, vol. 31, no. 4, pp. 314–316, Apr. 2010.

- [8] T. Kawamura *et al.*, "Oxide TFT rectifier achieving 13.56-MHz wireless operation," *IEEE Trans. Electron Devices*, vol. 59, no. 11, pp. 3002–3008, Nov. 2012. doi: 10.1109/TED.2012.2213091.

- [9] A. Chasin *et al.*, "An integrated a-IGZO UHF energy harvester for passive RFID tags," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3289–3295, Sep. 2014. doi: 10.1109/TED.2014.2340462.

- [10] J. Zhang *et al.*, "Flexible indium gallium zinc oxide Schottky diode operating beyond 2.45 GHz," *Nat. Commun.*, vol. 6, Jul. 2015, Art. no. 7561.

- [11] E. Cantatore *et al.*, "A 13.56-MHz RFID system based on organic transponders," *IEEE J. Solid-State Circuits*, vol. 42, no. 1, pp. 84–92, Jan. 2007.

- [12] J. Genoe, K. Myny, S. Steudel, and P. Heremans, "Design and manufacturing of organic RFID circuits: Coping with intrinsic parameter variations in organic devices by circuit design," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Design (ICCAD)*, Nov. 2010, pp. 496–499.

- [13] P. G. Bahubalindruni *et al.*, "Influence of channel length scaling on InGaZnO TFTs characteristics: Unity current-gain cutoff frequency, intrinsic voltage-gain, and on-resistance," *J. Display Technol.*, vol. 12, no. 6, pp. 515–518, Jul. 2016.

- [14] P. G. Bahubalindruni *et al.*, "High-gain transimpedance amplifier for flexible radiation dosimetry using InGaZnO TFTs," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 760–765, Jun. 2018.

**BHAWNA TIWARI** received the master's degree in VLSI design from Indira Gandhi Delhi Technical University, New Delhi, India. She is currently pursuing the Ph.D. degree with the Indraprastha Institute of Information Technology Delhi, New Delhi, under Visvesvaraya Research Fellowship. Her Ph.D. thesis is focused on energy efficient SAR ADC design using submicron and large area electronics. Her research interests include analog/mixed signal circuit design with emerging and CMOS technologies, large-area

flexible, and transparent electronics.

**PRIYANKA MITTAL** received the graduation degree in electronics and communication from the Indira Gandhi Institute of Technology. She is currently pursuing the M.Tech. degree in VLSI and embedded systems with the Indraprastha Institute of Information Technology (IIIT) Delhi. She was a Research and Development Engineer with ABB India Pvt. Ltd. for two years. She was a Teaching Assistant with IIIT Delhi. She is currently a Senior ASIC Development Engineer with Western Digital Corporation. Her area of interest includes VLSI design.

**JOÃO GOES** (S'95–M'00–SM'09) received the B.Sc., M.Sc., and Ph.D. degrees in electrical and computer engineering from the Instituto Superior Tcnico (IST), Technical University of Lisbon, Lisbon, Portugal, in 1992, 1996, and 2000, respectively, and the Agregado degree (Habilitation degree) in electronics from the Universidade Nova de Lisboa (NOVA), Caparica, Portugal, in 2012. Since 1998, he has been with the Department of Electrical Engineering, Faculty of Sciences and Technology, FCT NOVA, where he is cur-

rently a Full Professor and has been the Department Head since 2012. Since 1998, he has also been a Senior Researcher, responsible for the Micro/Nanoelectronics Research Unit, with the Centre of Technology and Systems (CTS), Instituto de Desenvolvimento de Novas Tecnologias, where he also became the Director of CTS in 2012. In 2003, he co-founded and served, for four years, as the Chief Technology Officer (and a Board Member) of ACACIA Semiconductor SA, which is a Portuguese engineering company that specializes in high-performance data converters and analog front-end products (acquired by Silicon and Software Systems, S3, in 2007, currently, ADESTO). Since 2007, he has been conducting lectures and performing his research with part-time consultancy for S3. From 1997 to 1998, he was a Project Manager with Chipidea SA (which was acquired by MIPS in 2007 and then by SYNOPSYS in 2009). From 1993 to 1997, he was a Senior Researcher with the Integrated Circuits and Systems Group, IST, doing research on data converters and analog filters. He has also supervised (graduated) 12 Ph.D. theses, 24 M.Sc. theses, and nine graduation projects. He has published over 180 papers in international journals and leading IEEE conferences. He has co-authored six books and several chapters in technical scientific and educational publications. From 2014 to 2015, he was also the Chairman of the IEEE Circuits and Systems Society (CASS) Analog Signal Processing Technical Committee (the largest within CASS). He has served as a Program Co-Chairman, an Organization Co-Chairman, and a Technical Program Committee (TPC) Member for numerous conferences. He was the TPC Co-Chairman of IEEE ISCAS 2015, Lisbon, in 2015, and the TPC Co-Chairman of PRIME 2016. He is currently an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-PART II: EXPRESS BRIEFS from 2016 to 2019. He is a member of the CASS and the Solid-State Circuits Society.

**RODRIGO MARTINS** is a Full Professor with the Faculty of Sciences and Technology, New University of Lisbon, Portugal, where he is the Head of Materials Science Department. He is the Co-Chair of the European Energy Materials Industry Research Initiative, EMIRI. He is the Founder and the Director of the Centre of Excellence in Microelectronics and Optoelectronics Processes, Uninova. He is a Leader of the Materials, Optoelectronics and Nanotechnologies Group, I3N/CENIMAT. Expert

in the field of transparent electronics and on the paper electronics, with over 560 papers published in WoK (Google Scholar). He is a member of the Advisory Board of Horizon 2020 (Advanced Materials, Nanotechnologies, Biotechnologies and Manufacturing); International Advisory Board of Strategic Initiative in Materials, a Flanders industry initiative; Steering Committee of EuMat; Alliance for Materials; Joint Innovation Centre for Advanced Material Sino-Portuguese; an Editorial Board of the *Journal Progress in Natural Science: Materials International* and of Heliyon (Elsevier); Advanced Electronics Materials Journal (Wiley); Administration Board of the nature journal: *npj 2D Materials and Applications*. He is the President of the European Academy of Sciences. He is a member of the Portuguese Academy of Engineering and the Portuguese Order of Engineers.

**PYDI GANGA BAHUBALINDRUNI** received the Ph.D. degree from the Department of Electrical and Computer Engineering, FEUP/INESC in 2014. She was an Assistant Professor with the ECE Department, Indraprastha Institute of Information Technology Delhi in 2016. She is currently an Assistant Professor with the School of Electrical Sciences, Indian Institute of Technology Goa. She was a Post-Doctoral Researcher with CENIMAT, FCT-UNL until 2016, where she was actively involved in various EU projects. She has pub-

lished over 35 articles, including international journals and conferences. Her research interests include analog/mixed signal circuit design with emerging and CMOS technologies, large-area flexible and transparent electronics, devices and device modeling. She was a recipient of the Early Career Research Grant.

**ANA SANTA** received the master's degree in physics engineering from the Universidade Nova de Lisboa in 2014. Since 2014, she has been a Researcher with CENIMATII3N, where she worked with oxide thin-film transistors. Her current work in oxide electronics is focused on deposition and characterization of multicomponent oxides, optimization of lithographic processes and thin-films deposition, fabrication and characterization of no oxide TFTs, and their integration in circuits on flexible substrates.

**JORGE MARTINS** received the master's degree in physics engineering from the Universidade Nova de Lisboa in 2012, where he is currently pursuing the Ph.D. degree in nanotechnologies and nanosciences with I3N/CENIMAT. The main topic of his research is the improvement of oxide TFT technologies by TCAD simulation tools. He has co-authored four peer-reviewed papers and one book chapter. His scientific interests are oxide thin-film transistors, oxide memristors, flexible and transparent electronics, circuit characteriza-

tion, and TCAD simulation.

**ELVIRA FORTUNATO** received the bachelor's degree in physics and materials engineering in 1987 and the Ph.D. degree in microelectronics and optoelectronics in 1995. She is a Full Professor with the Faculty of Science and Technology, NOVA University. She is the Vice-Rector with NOVA and the Director of the Materials Research Center (CENIMAT) of the Associated Laboratory i3N, the Institute of Nanostructures, Nanomodeling and Nanofabrication. Since 1998, she leads the research team of the Materials

Research Center (CENIMAT) which has been distinguished for the important discovery of the paper transistor. She was a recipient of the First Prize of 2.25 million euros with the highest score in the league table in 2008 by the European Research Council, the Second Advanced Grant of the European Research Council with a maximum amount of 3.5 million euros, being the Highest Prize Ever Awarded to a Researcher in Portugal in 2018, and the Czochralski Medal (Science of Materials) assigned by the Polish Academy of Sciences and the Blaise Pascal Medal conferred by the European Academy of Sciences. Since 2016, she is part of the European Commission's Scientific Advisory Board. Since 2018, she has been a member of the Lisbon Academy of Sciences.

**PEDRO BARQUINHA** received the Ph.D. degree in nanotechnologies and nanosciences from the Universidade Nova de Lisboa in 2010. He is currently an Associate Professor with the Materials Science Department, FCT-NOVA. He has been working in oxide electronics since 2004, participating in over 30 national and international research projects in the area, with academia and industry. His work involves design, deposition, and characterization of multicomponent thin films (metals, oxides, and polymers), fabrication and

characterization of transistors and their integration in circuits on flexible substrates. He has co-authored over 140 peer-reviewed papers (with an *H*-index of 37, as 2018), three books and three book chapters in this area. His current research focus is to take transparent electronics to performance and integration levels suitable for future multifunctional concepts. This involves pursuing reproducible and low temperature synthesis routes of oxide nanostructures and nanodevice/nanocircuit integration, complemented by device modeling/simulation. He received an ERC Starting Grant (TREND) to advance this research topic in 2016.