549522 P200

September 1989

-

NAG1-613

UILU-ENG-89-2231 CSG-108

# **COORDINATED SCIENCE LABORATORY**

College of Engineering

LANGLEY GRANT 1N+62-CR 239266 1878.

# PARALLEL ARCHITECTURES AND PARALLEL ALGORITHMS FOR INTEGRATED VISION SYSTEMS

# **Alok Nidhi Choudhary**

(NASA-CR-185990) PARALLEL ARCHITECTURES AND PARALLEL ALGORITHMS FOR INTEGRATED VISION SYSTEMS Ph.D. Thesis (Illinois Univ.) 187 p CSCL 098

N90-12215

Unclas G3/62 0239266

# UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

Approved for Public Release. Distribution Unlimited.

# PARALLEL ARCHITECTURES AND PARALLEL ALGORITHMS FOR INTEGRATED VISION SYSTEMS

BY

### ALOK NIDHI CHOUDHARY

B.E.(Hons.), Birla Institute of Technology and Science, 1982 M.S., University of Massachusetts, 1986

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1989

Urbana, Illinois

# PARALLEL ARCHITECTURES AND PARALLEL ALGORITHMS FOR INTEGRATED VISION SYSTEMS

Alok Nidhi Choudhary, Ph.D. Department of Electrical and Computer Engineering University of Illinois, Urbana-Champaign, 1989

Computer vision has been regarded as one of the most complex and computationally intensive problems. An integrated vision system (IVS) is a system that uses vision algorithms from all levels of processing to perform for a high level application (e.g, object recognition). An IVS normally involves algorithms from low level, intermediate level and high level vision. Designing parallel architectures for vision systems has been of a tremendous interest to researchers. This thesis addresses several issues in parallel architectures and parallel algorithms for integrated vision systems.

First, a model of computation for IVSs is presented. The model captures computational requirements, defines spatial and temporal data dependencies between tasks, and shows what types of interactions may occur between tasks from different levels of processing. The model is used to develop features and capabilities of a parallel architecture suitable for IVSs. It is concluded that an architecture for IVS must be reconfigurable into different modes, be partitionable, allow dynamic resource allocation and task scheduling, provide flexible and fast communication between processing elements, provide efficient I/O and be fault-tolerant.

A multiprocessor architecture for IVSs (called NETRA) is presented. NETRA is highly flexible without the use of complex interconnection schemes. NETRA is recursively defined hierarchical architecture whose leaf nodes consist of clusters processors connected with a programmable crossbar with a selective broadcast capability. Hence, it is easily scalable from small to large systems. Homogeneity of NETRA permits fault tolerance and graceful degradation under faults. Several refinements in the architecture over the original design are also proposed. Performance of several vision algorithms when they are mapped on one cluster is presented. It is shown that SIMD, MIMD and systolic algorithms can be easily mapped onto processor clusters, and almost linear speedups are possible. For some algorithms, analytical performance results are compared with those obtained using an implementation. It is observed that the analysis is very accurate.

An extensive analysis of inter-cluster communication strategies in NETRA is presented. A methodology to evaluate performance of algorithms on NETRA is described. Performance analysis of parallel algorithms when mapped across clusters is presented. The parameters are derived from the characteristics of the parallel algorithms, which are then, used to evaluate the alternative communication strategies in NETRA. The effects of communication interference on the performance of algorithms are studied. It is observed that if communication speeds are matched with the computation speeds, almost linear speedups are possible when algorithms are mapped across clusters.

Finally, several techniques to perform data decomposition, and static and dynamic load balancing for IVS algorithms are described. These techniques can be used to perform load balancing for intermediate and high level, data dependent vision algorithms. These techniques are novel because they use knowledge about the data when it is produced and use knowledge about the computation in the next task to perform load balancing in an integrated environment. They are shown to perform well, using them on an implementation of a motion estimation system on a hypercube multiprocessor.

Index Terms - Multiprocessor Architectures, Parallel Algorithms, Parallel Processing, Computer Vision, Image Processing

# ACKNOWLEDGMENTS

I would like to express my sincere appreciation and gratitude to my thesis advisor, Professor Janak Patel, for providing me with an opportunity to work under his supervision. His guidance, support and suggestions were invaluable contributions to this work. I would like to thank Professors Narendra Ahuja, Prithviraj Banerjee and Thomas Huang for their comments, suggestions and constant encouragement. I am particularly thankful to Subhodev Das and Mun Leung for providing their helpful suggestions and sharing their knowledge, which have helped me expand the scope of this work.

I would like to thank my friends and colleagues in the Computers Systems Group as well as in the Vision Group of the Coordinated Science Laboratory for their assistance and suggestions. It has been a pleasant experience to have spent time with all of them both at work and otherwise. Finally, I would like to extend my appreciation to all the secretaries in our group for their help.

# TABLE OF CONTENTS

# PAGE

,

.

| 1. INTRODUCTION                                                   |  |

|-------------------------------------------------------------------|--|

| 1.1. Motivation and Scope                                         |  |

| 1.2. Review of Multiprocessor Architectures                       |  |

| 1.2.1. Mesh connected computers                                   |  |

| 1.2.2. Pyramid computers                                          |  |

| 1.2.3. Hypercube multiprocessors                                  |  |

| 1.2.4. Shared memory machines                                     |  |

| 1.2.5. Systolic arrays                                            |  |

| 1.2.6. Partitionable and hierarchical architectures               |  |

| 1.3. Organization of the Thesis                                   |  |

| 2. MODEL OF COMPUTATION FOR INTEGRATED VISION SYSTEM              |  |

| 2.1. Parallelism in IVSs                                          |  |

| 2.2. Data Dependencies                                            |  |

| 2.3. Features and Capabilities of Parallel Architectures for IVSs |  |

| 2.4. Examples of Integrated Vision Systems                        |  |

| 2.4.1. Image understanding benchmark                              |  |

| 2.4.2. Motion estimation and object recognition                   |  |

| 3. ARCHITECTURE OF NETRA                                          |  |

| 3.1. Processor Clusters                                           |  |

| 3.1.1. Crossbar design                                            |  |

| 3.1.2. Scalability of crossbar                                    |  |

| 3.2. The DSP Hierarchy                                            |  |

| 3.3. Global Memory                                                |  |

| 3.4. Global Interconnection                                       |  |

| 3.4.1. Interconnection network                                    |  |

| 3.4.2. Global bus                                                 |  |

| 3.5. IVS Computation Requirements and NETRA                       |  |

| 3.6. Comparison of NETRA with Other Architectures                 |  |

| 4. PARALLEL ALGORITHMS ON A CLUSTER                               |  |

| 4.1. Classification of Common Vision Algorithms                   |  |

| 4.2. Issues in Mapping an Algorithm                               |  |

|                                                                   |  |

| 4.3. Performance     | Evaluation of Parallel Algorithms                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | .1. 2-D convolution                                                                                                                                      |

|                      | 2. Separable convolution                                                                                                                                 |

|                      | 3.3. Two-dimensional FFT (2D-FFT)                                                                                                                        |

|                      | .4. Hough transform                                                                                                                                      |

|                      | ementation Results                                                                                                                                       |

| •                    | .1. 2-D FFT                                                                                                                                              |

| 4.4                  | 2. Separable convolution                                                                                                                                 |

| 4.4                  | .3. Benchmark Algorithms                                                                                                                                 |

|                      | 4.4.3.1. Sobel                                                                                                                                           |

| -                    | 4.4.3.2. Median filtering                                                                                                                                |

| 4.5. Summary         |                                                                                                                                                          |

| 5. INTER-CLUSTER CON | IMUNICATION IN NETRA                                                                                                                                     |

|                      | for Inter-cluster Communication                                                                                                                          |

|                      | .1. Multistage interconnection network and global memory                                                                                                 |

|                      | .2. DSP tree links                                                                                                                                       |

|                      | .3. Global bus                                                                                                                                           |

|                      | inter-cluster Communication                                                                                                                              |

| •                    | Performance Evaluation of Algorithms                                                                                                                     |

| ••                   | of Parallel Algorithms on Multiple Clusters                                                                                                              |

| 5.4                  | 1. Two-dimensional Fast Fourier Transform (2-D FFT)                                                                                                      |

|                      | 2. 2-D separable convolution                                                                                                                             |

|                      | .3. Hough transform                                                                                                                                      |

|                      | ~                                                                                                                                                        |

| i. DATA DECOMPOSITI  | ON AND LOAD BALANCING TECHNIQUES                                                                                                                         |

|                      | thms from Motion Estimation System                                                                                                                       |

|                      | .1. Feature points                                                                                                                                       |

|                      | .2. Matching                                                                                                                                             |

|                      | 6.1.2.1. Stereo matching                                                                                                                                 |

|                      |                                                                                                                                                          |

|                      | 6.1.2.2. Time matching                                                                                                                                   |

|                      | <ul><li>6.1.2.2. Time matching</li><li>6.1.2.3. Elimination of multiple matches</li></ul>                                                                |

| 6.2. Data Decom      | <ul><li>6.1.2.2. Time matching</li><li>6.1.2.3. Elimination of multiple matches</li></ul>                                                                |

|                      | 6.1.2.2. Time matching<br>6.1.2.3. Elimination of multiple matches<br>position and Load Balancing Techniques                                             |

| 6.2                  | 6.1.2.2. Time matching<br>6.1.2.3. Elimination of multiple matches<br>position and Load Balancing Techniques<br>2.1. Uniform partitioning                |

| 6.2<br>6.2           | 6.1.2.2. Time matching<br>6.1.2.3. Elimination of multiple matches<br>position and Load Balancing Techniques<br>2.1. Uniform partitioning<br>2.2. Static |

| 6.2<br>6.2<br>6.2    | 6.1.2.2. Time matching<br>6.1.2.3. Elimination of multiple matches<br>position and Load Balancing Techniques<br>2.1. Uniform partitioning                |

| 6.3.1. Hypercube multiprocessor | 151 |

|---------------------------------|-----|

| 6.3.2. Feature extraction       | 152 |

| 6.3.3. Matching features        | 154 |

| 6.3.4. Time match               | 159 |

| 6.3.5. Second stereo match      | 161 |

| 6.3.6. Summary                  | 164 |

| 7. CONCLUSIONS                  | 166 |

| 7.1. Summary and Discussion     | 166 |

| 7.2. Future Work                | 169 |

| REFERENCES                      | 171 |

| VITA                            | 175 |

.

.

# LIST OF FIGURES

# FIGURE

# PAGE

| 1.1 : | A 4-Connected Mesh Computer                                       | 8   |

|-------|-------------------------------------------------------------------|-----|

| 1.2 : | A Pyramid Multiprocessor                                          | 11  |

| 1.3 : | A Hypercube Multiprocessor                                        | 13  |

| 1.4 : | Warp System Overview                                              | 18  |

| 2.1 : | Model of Computation for an Integrated Vision System              | 30  |

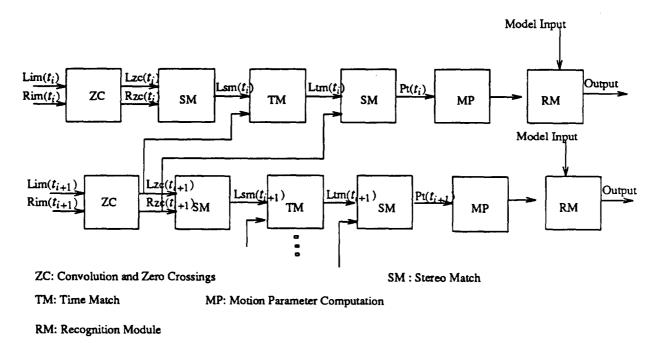

|       | Computation Flow for Motion Estimation                            | 37  |

| 3.1 : | Organization of NETRA                                             | 40  |

| 3.2 : | Organization of Processor Cluster                                 | 42  |

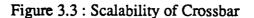

| 3.3 : | Scalability of Crossbar                                           | 44  |

| 3.4 : | An Alternative Strategy for Inter-Cluster Communication           | 48  |

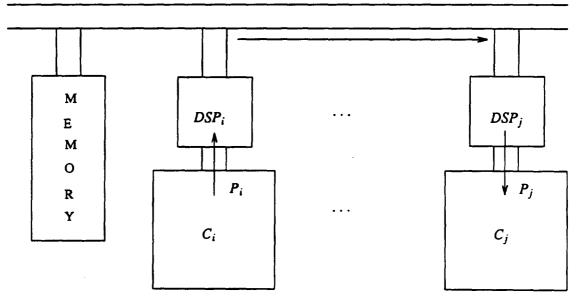

| 3.5 : | An Example of SIMD and Systolic Modes of Computation in a Cluster | 52  |

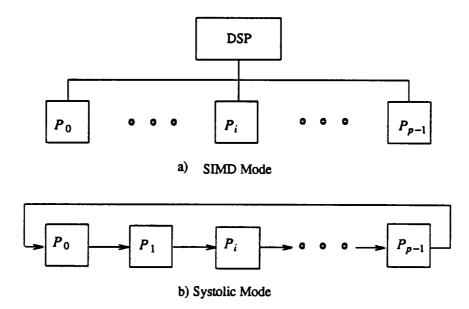

| 4.1 : | Classification of Common Vision Algorithms                        | 65  |

| 4.2 : | Mapping Algorithms on One Cluster                                 | 67  |

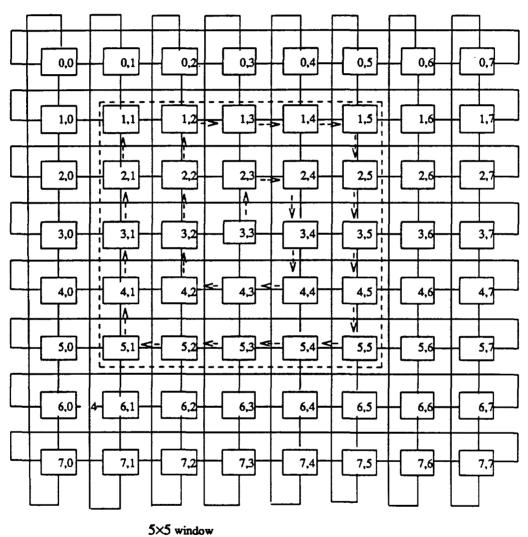

| 4.3 : | Mapping on the Cluster for Convolution                            | 70  |

| 4.4 : | 2-D Convolution                                                   | 72  |

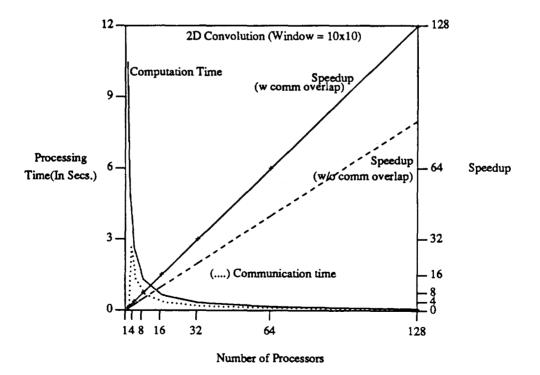

| 4.5 : | Performance of 2D Convolution on a Processor Cluster              | 73  |

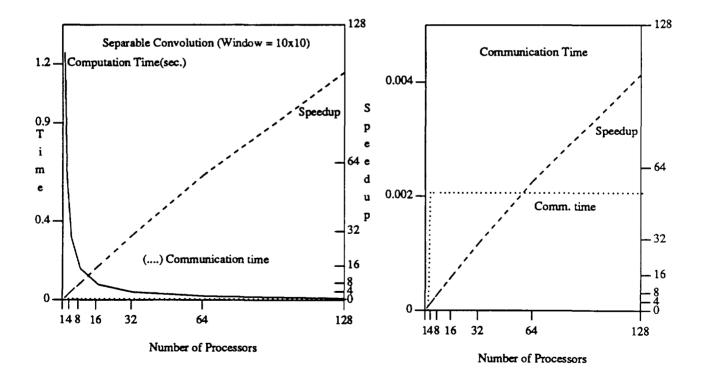

| 4.6 : | Performance of Separable Convolution on a Processor Cluster       | 75  |

| 4.7 : | 2D-FFT                                                            | 77  |

| 4.8:  | An Example of Mapping 2D-FFT onto Four Processors                 | 78  |

| 4.9 : | Performance of 2D FFT on a Processor Cluster                      | 79  |

| 4.10: | Communication Time for 2D FFT on a Processor Cluster              | 80  |

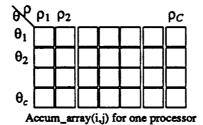

| 4.11: | Accumulator array for Hough Transform                             | 82  |

| 4.12: | Algorithm to Compute Votes in Hough Transform                     | 82  |

| 4.13: | Algorithm to Accumulate the Vote Count                            | 83  |

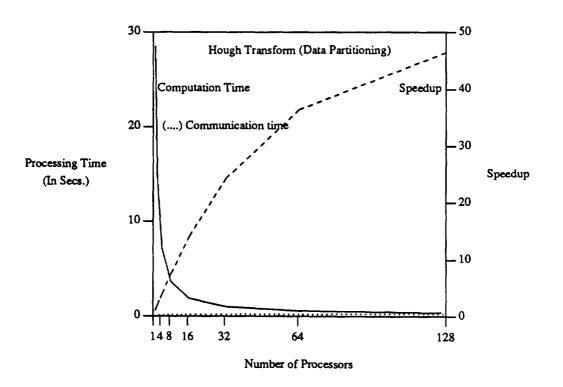

| 4.14: | Performance of Hough Transform (Data Partitioning)                | 85  |

| 4.15: | Performance of Hough Transform (Parameter Partitioning)           | 89  |

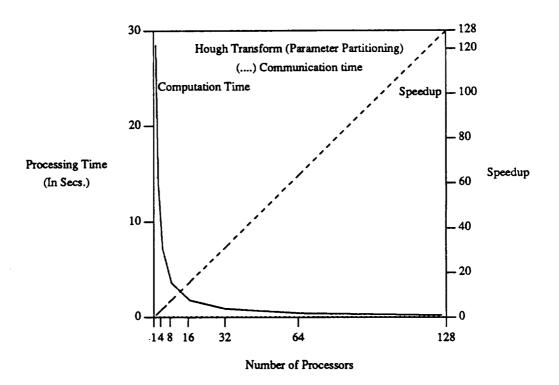

| 4.16: | Comparison of Performance of PP and DP for Hough Transform        | 90  |

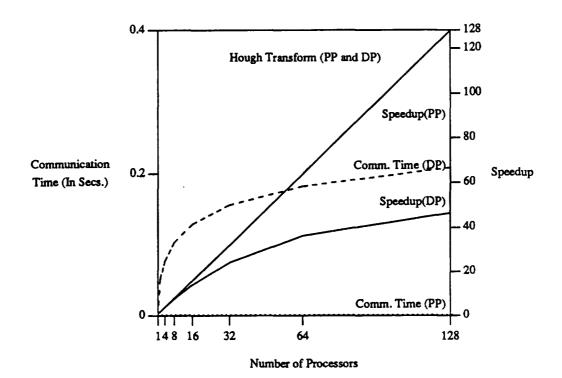

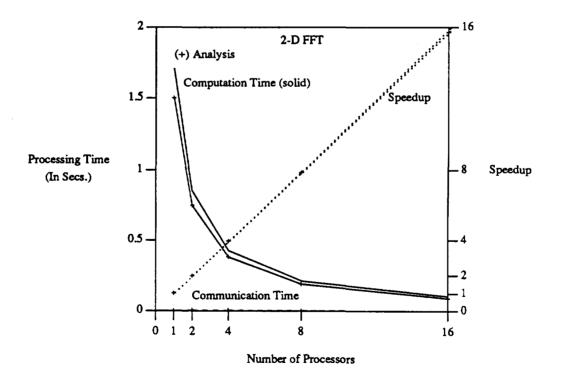

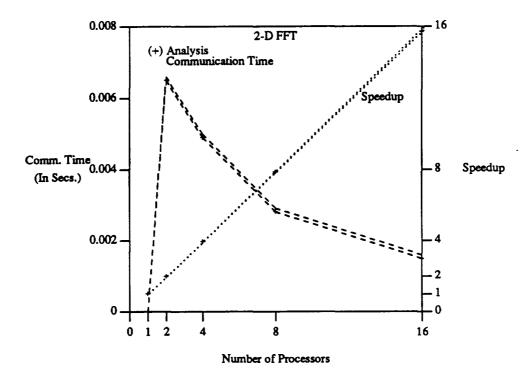

| 4.17: | Performance of 2-D FFT on a cluster (Analysis and Implementation) | 91  |

| 4.18: | Communication Time for 2-D FFT                                    | 92  |

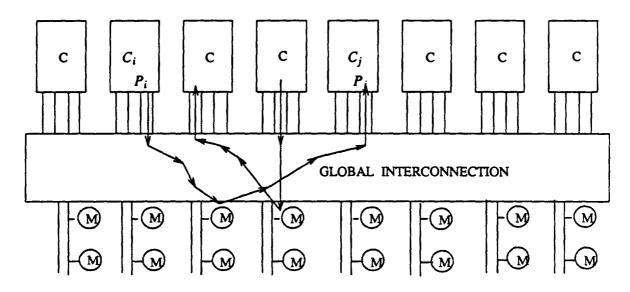

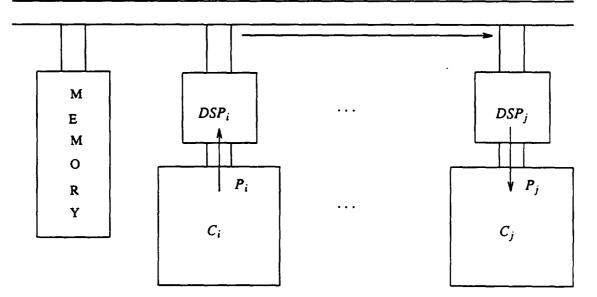

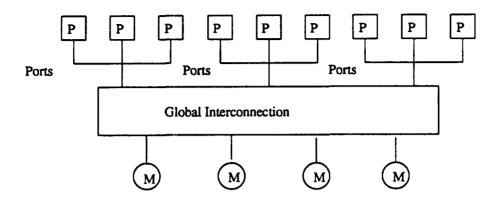

| 5.1 : | Inter-Cluster Communication Using Global Memory                   | 98  |

| 5.2 : | Inter-Cluster Communication Using the Global Bus                  | 99  |

| 5.3 : | Equivalent Model for Global Communication                         | 101 |

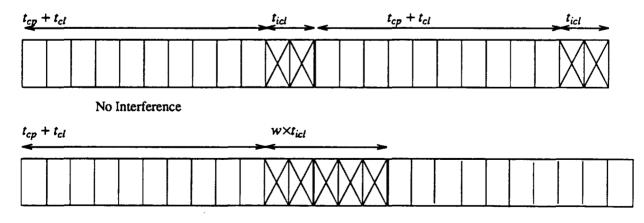

| 5.4 : | Computation and Communication Activities of a Processor           | 101 |

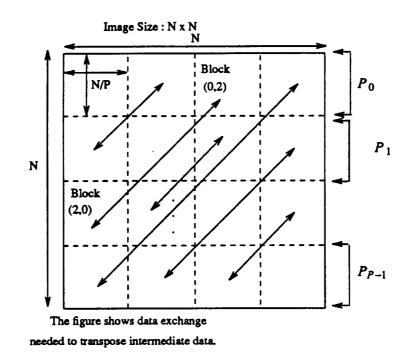

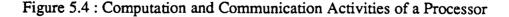

| 5.5 : | An Example of Mapping 2-D FFT on Three Clusters                   | 108 |

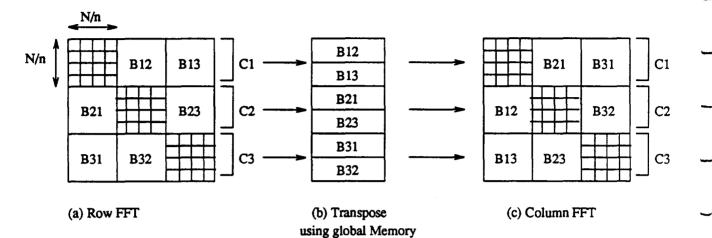

| 5.6 : | Speedup for 2-D FFT (Multistage Network)                                 | 109 |

|-------|--------------------------------------------------------------------------|-----|

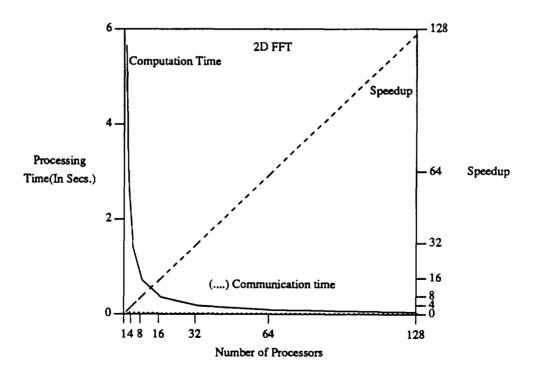

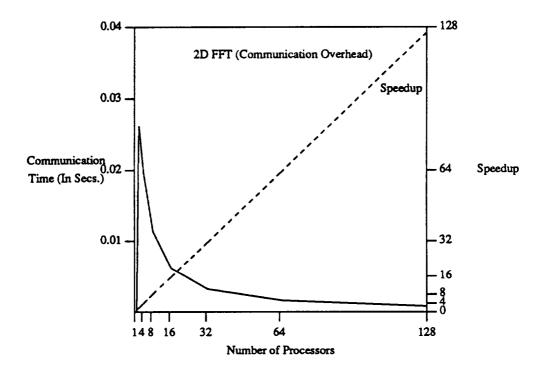

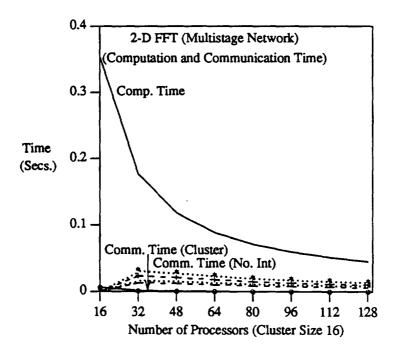

| 5.7 : | Computation and Communication Times for 2-D FFT (Multistage Network)     | 110 |

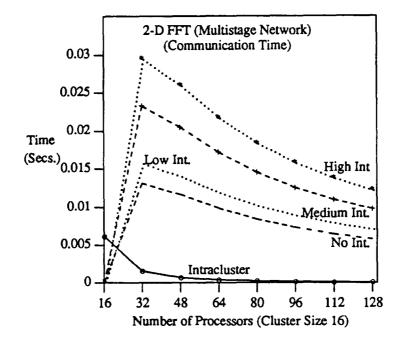

| 5.8:  | Communication Times for 2-D FFT (Multistage Network)                     | 111 |

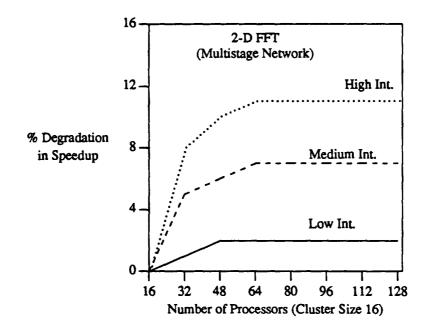

| 5.9 : | Degradation in Speedup Due to Conflicts for 2-D FFT (Multistage Network) | 112 |

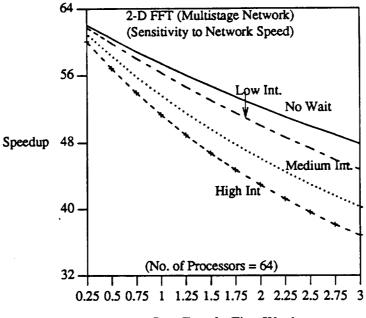

| 5.10: | Speedup vs. Network Speed                                                | 113 |

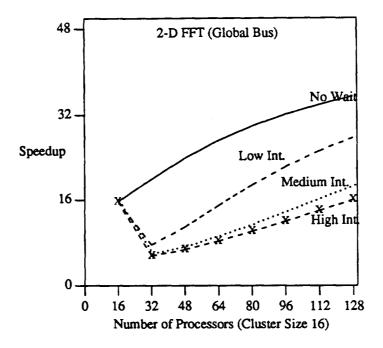

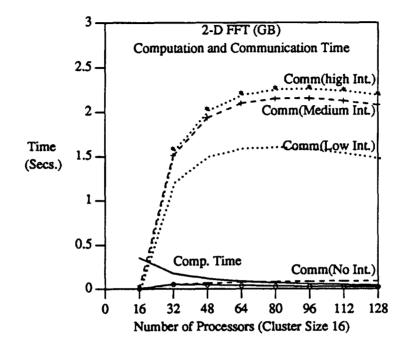

| 5.11: | Speedup for 2-D FFT (Global Bus)                                         | 115 |

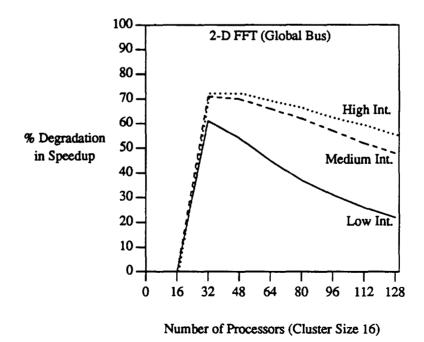

| 5.12: | Computation and Communication Times for 2-D FFT (Global Bus)             | 116 |

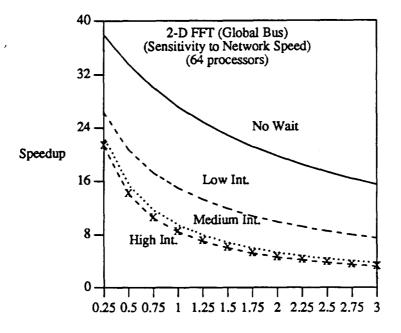

| 5.13: | Degradation in Speedup Due to Conflicts 2-D FFT (Global Bus)             | 116 |

| 5.14: | Speedup vs. Network Speed (Global Bus)                                   | 117 |

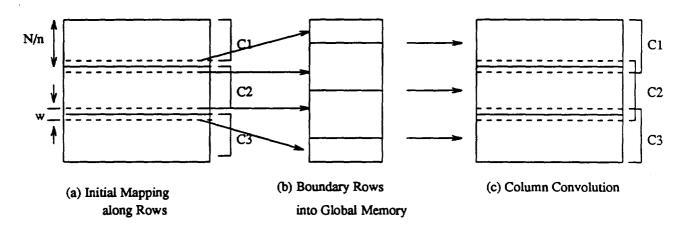

| 5.15: | An Example of Mapping 2-D Separable Convolution on Three Clusters        | 118 |

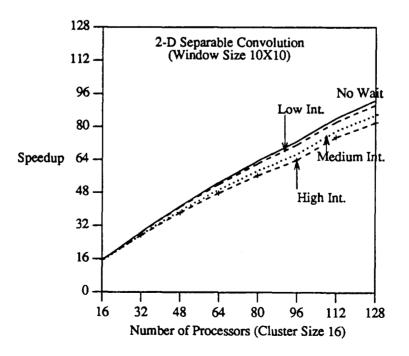

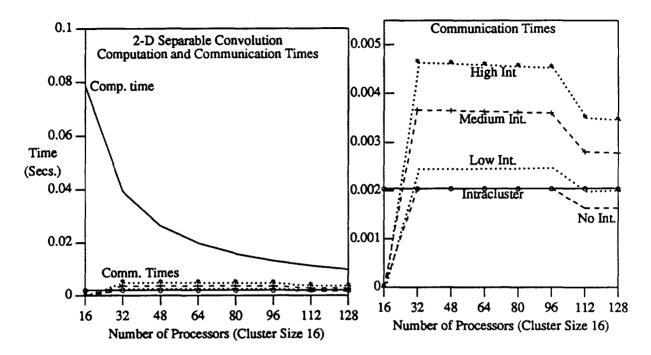

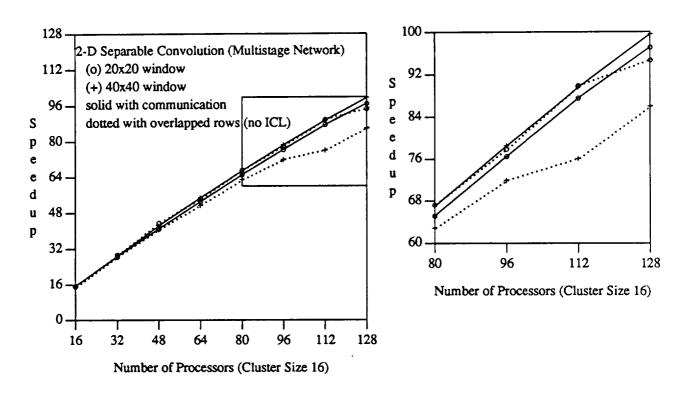

| 5.16: | Speedup for 2-D Convolution (Multistage Network)                         | 119 |

| 5.17: | 2-D Convolution (Multistage Network)                                     | 120 |

| 5.18: | Figure 5.18 : Overlapped Computation vs. Communication Trade-off         | 121 |

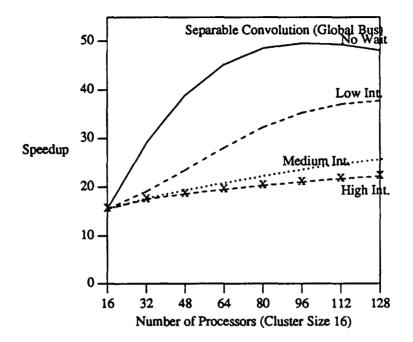

| 5.19: | Speedup for 2-D Convolution (Global Bus)                                 | 122 |

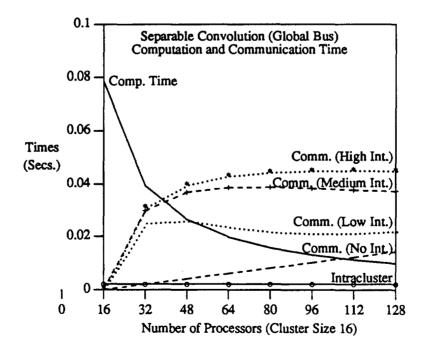

| 5.20: | Computation and Communication Times for 2-D Convolution (Global Bus)     | 122 |

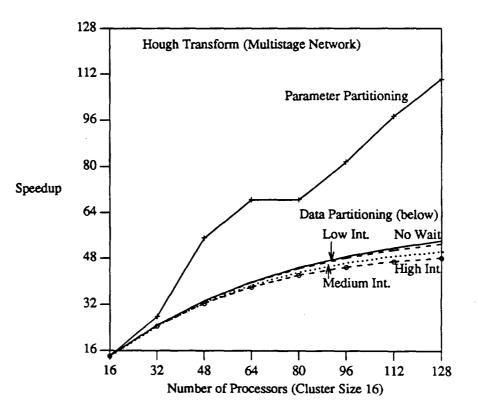

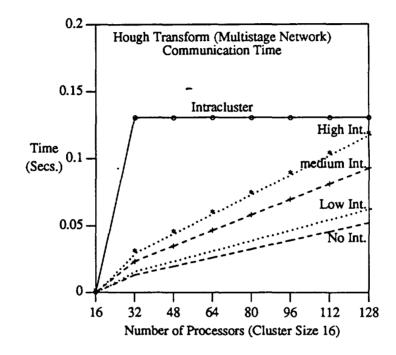

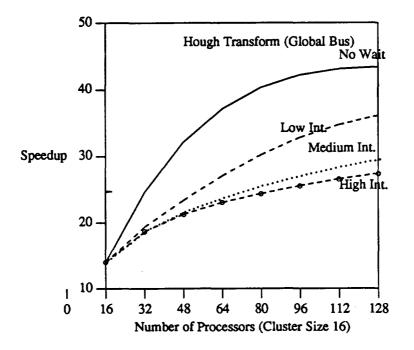

| 5.21: | Speedup for Hough Transform (Multistage Network)                         | 125 |

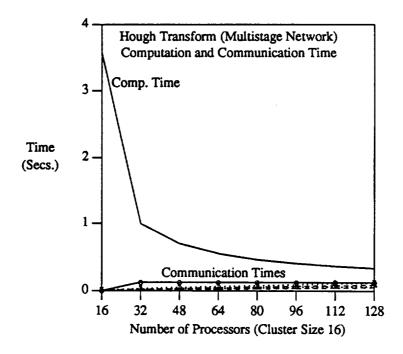

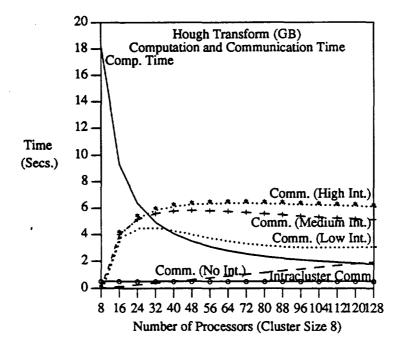

| 5.22: | Computation and Communication Times for Hough Transform                  | 126 |

| 5.23: | Communication Times for Hough Transform                                  | 127 |

| 5.24: | Speedup for Hough Transform (Global Bus)                                 | 128 |

| 5.25: | Computation and Communication Times Hough Transform (Global Bus)         | 128 |

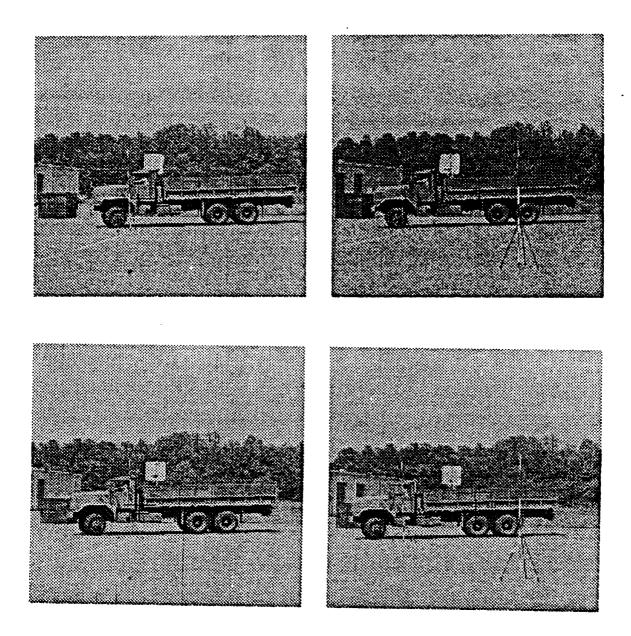

| 6.1 : | Stereo Image Pairs at t7 and t8                                          | 133 |

| 6.2 : | Zero Crossings of the Images in Figure 6.1                               | 134 |

| 6.3 : | Unambiguous Matched Points of the t7 Stereo Image                        | 142 |

| 6.4:  | Unambiguous Time Matched Points between the left t7 and t8 Images        | 143 |

| 6.5 : | Unambiguous Matched Points of the Images in Figure 6.1                   | 144 |

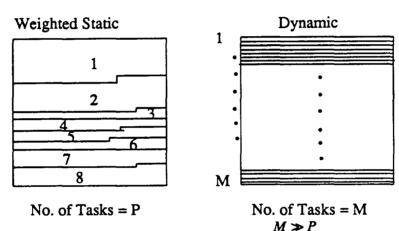

| 6.6 : | Load Balancing Strategies                                                | 152 |

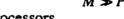

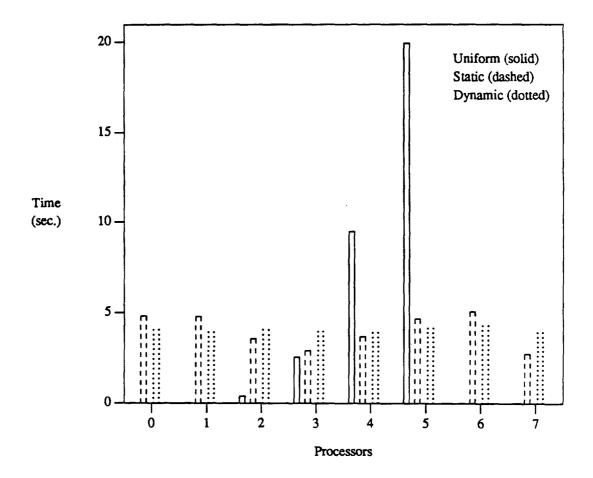

| 6.7:  | Distribution of Computation Times for Stereo Match (P=8)                 | 156 |

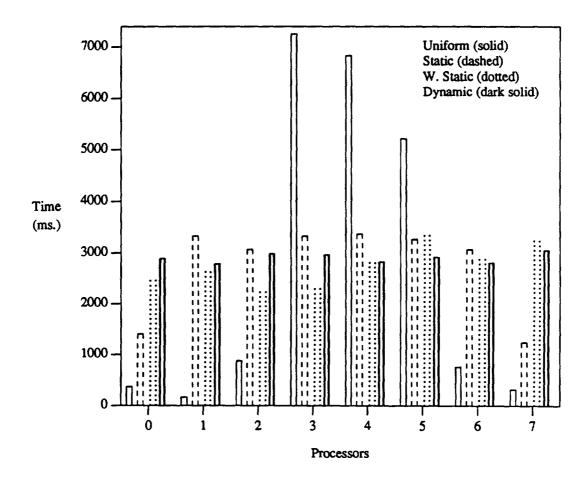

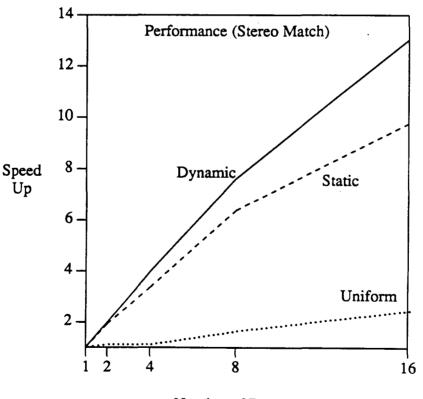

| 6.8 : | Speedups for Stereo Match Computation                                    | 158 |

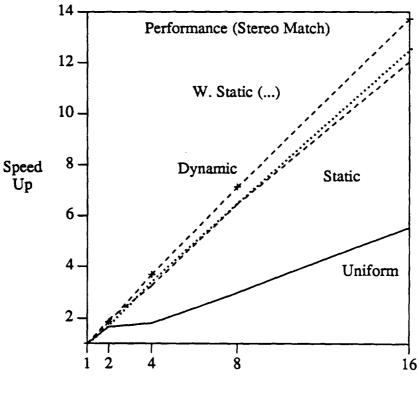

| 6.9 : | Speedup for Time Match                                                   | 161 |

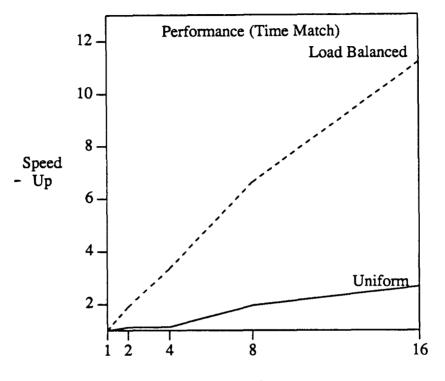

| 6.10: | Distribution of Computation Times for Second Stereo Match (P=8)          | 162 |

| 6.11: | Speedups for Second Stereo Match                                         | 163 |

# LIST OF TABLES

# TABLE

- 5

# PAGE

| 4.1 : | Parameters for Performance Evaluation               | 68  |

|-------|-----------------------------------------------------|-----|

| 4.2 : | Separable Convolution Implementation Results        | 93  |

| 4.3 : | Sobel Edge Detection                                | 94  |

| 4.4 : | Median Filtering                                    | 95  |

| 5.1:  | Parameters for Performance Evaluation               | 106 |

| 6.1 : | Performance for feature Extraction (Zero Crossings) | 154 |

| 6.2 : | Distribution of Computation Times for Stereo Match  | 157 |

| 6.3 : | Distribution of Computation Time for Time Match     | 160 |

## CHAPTER 1.

## INTRODUCTION

#### 1.1. Motivation and Scope

One of the most important, difficult and computationally intensive problems in the field of artificial intelligence is computer vision. There is no consensus today on the definition and scope of computer vision. The problem of artificial vision is as old as the field of computer science and engineering. Researchers have devoted much time in attempting to define and solve parts of the problems for many years. However, to say that computer vision is in its infancy today is a correct judgment of the state of the art in artificial vision. Furthermore, nobody knows the answer to the question of whether it is possible to make artificial vision as powerful and general as human vision. One of the many reasons for not knowing the answer is that little is understood about human vision itself.

There are several approaches to tackling the computational problems in computer vision. One of the approaches, which is also the oldest, is to use the computational powers of computers and their development in various fields of computer science and engineering, such as signal processing, mathematical and scientific algorithms, and graph theory. The other approach, which is relatively recent, is to somehow mimic the computations performed in the human brain. This approach is termed as the neural network

approach. However, tremendous computational power in one form or another is needed in both the approaches.

Computer vision and image understanding algorithms employ a very broad spectrum of techniques from several areas such as signal processing, advanced mathematics, graph theory, and artificial intelligence. The computational requirements to perform algorithms from these fields are tremendous when executed individually, and when they need to be integrated in a meaningful way to perform a broader function in a reasonable amount of time, the computation becomes almost intractable. For example, consider interpretation of a changing scene at 30 frames per second. The amount of data to be handled per second itself is almost 25 Mbytes (million bytes) assuming a moderate resolution of 512×512 pixels per frame with each pixel of three bytes (one byte for each color and 256 grey level). The amount of computation required for simple image transformations, labeling, grouping, surface reconstruction or motion analysis is very difficult to estimate; however, for many applications it can be in the range of 100 - 10,000 billion instructions per second [1]. This is raw processing power and does not include the complexities involved in a system such as interactions among various algorithms, input-output of data, managing system resources, and fault-tolerance. Therefore, the vision problem is of tremendous interest to computer architects and it presents them with great challenges.

Having discussed that the need to provide tremendous processing power in an architecture for computer vision, the next question is how can that processing power capability be provided? Parallel processing, which has progressed tremendously in the past decade, seems to be the consensus approach to providing the necessary computational power. Fortunately, most algorithms that are part of a vision system are in general,

characterized by massive parallelism. For low level processing, spatial decomposition of an image provides a natural way of generating parallel tasks. For higher level analysis operations, parallelization may also be based on other image characteristics and may be data dependent. In fact, parallel processing has been suggested as the approach to provide computational power needed for most computational intensive problems such as scientific, vision or any other because technological limits are being reached in how fast a serial processor can perform. But the next question is what form of parallel processing, and what type of multiprocessor architectures are suitable for vision application? It may be easier to provide raw processing power by parallel processing, but the more important and difficult question is how to design multiprocessors so that the available processing power can be used efficiently. Since there is no consensus as to what a vision system consists of, another problem is how to evaluate or compare one architecture with another. Recently, efforts have been made to provide a framework and benchmark to evaluate multiprocessor architectures for vision which not only attempt to measure the processing power of an architecture but also test other architectural issues such as I/O, ability to perform algorithms with varying characteristics, and effect on the performance due to interactions between tasks [1].

This thesis attempts to identify various issues in multiprocessor architectures and parallel algorithms for computer vision. The approach is to consider the computational requirements for vision in an integrated environment rather than to propose architectural solutions to perform one or more algorithms efficiently and fast. We attempt to define the computational requirements for an Integrated Vision System (IVS), for which there is no general definition. However, an application dependent definition of an IVS is possible. For example, object recognition, a system that takes an image (or a set of images) as input and produces an output that describes the object can be considered an IVS. However, a system (or an algorithm) that takes an image input and produces its Discrete Fourier Transform (DFT) is not considered an Integrated Vision System, though computing DFT itself may be a step or a part of an IVS. In fact, it is important to distinguish between image processing and computer vision (or IVS). Image processing involves transforming images by applying one or more algorithms to the input in order to make it more useful for interpretation by humans. For example, image enhancement, noise reduction, scaling, and thresholding constitute image processing operations. Integrated Vision System, on the other hand, involves interpretation and recognition by the system itself using input data, parameters and knowledge base without any interference from humans. That is, the system is completely an automated vision system in the ideal case. Therefore, IVS can be defined as a system which employs a subset of vision algorithms in a systematic way to produce a meaningful output. The computational requirements for such an integrated vision system are tremendous [2].

Vision algorithms are normally divided into three levels: low level, intermediate level and high level. Low level algorithms are mostly image processing algorithms. These algorithms, in general, are very regular in structure, involve data independent and local computations, and involve pixel data. Available parallelism is normally on the pixel level. Intermediate level algorithms perform computations on the output produced by low level algorithms and involve more complex data structures, data dependent algorithms, symbolic processing, and involve varying degree of parallelism which itself depends on the data and the nature of the computation. Finally, high level algorithms not

only exhibit most of the properties of intermediate level algorithms but also involve topdown processing in which knowledge based interpretation is performed. Therefore, the algorithms may involve accessing databases, performing enormous searches and include other artificial intelligence algorithms.

An Integrated Vision System will normally consist of algorithms from all levels of processing. Therefore, in addition to providing tremendous raw processing power an architecture must be capable of the following. It must have the ability to transform pixel data into a set of meaningful symbols that describe it, to process pixels, symbol data and other complex data structures in parallel, and the ability to simultaneously perform low, intermediate, and high level algorithms, and fast I/O. These requirements and others mean that an architecture must be reconfigurable, provide flexible and fast communication structures between processing elements, provide different types of processing (such as SIMD, MIMD) to most efficiently execute algorithms from different levels of processing, be efficient in performing dynamic resource allocation and task scheduling, be partitionable into independent subsystems which can work on different computations simultaneously, be fault-tolerant and provide fast I/O bandwidth to keep up with a tremendous amount of data flow.

Design of multiprocessor architectures for IVSs, therefore, must address the requirements posed by the above discussed characteristics of algorithms that are part of an IVS. In this thesis, we present a model of computation for IVSs for parallel processing. The model attempts to capture the properties of IVS algorithms, data flow and interactions between various tasks. Our model not only captures the computation requirements presented in the Image Understanding Benchmark presented in [1] but it also provides for another dimension (time) of computation which is absent in the benchmark. Then we present an architecture for integrated vision systems called "NETRA." NETRA, in its original form, was first proposed by Sharma, Patel and Ahuja in [3]. We propose several refinements to the architecture based on our understanding of computational requirements for IVSs. An elaborate discussion is presented that gives the rationale behind the design. Several common vision algorithms are used to evaluate the performance of the architecture and alternative communication strategies. The algorithms are mapped using the multidimensional divide-and-conquer paradigm [4] which is an attractive mechanism for providing parallelism in all levels of processing.

### 1.2. Review of Multiprocessor Architectures

The advent of VLSI technology has enabled architects to produce high performance chips to perform specific applications. But these special purpose chips can only be used in an IVS as accelerators of specific algorithms. Another use of VLSI technology has been to create massively parallel Single Instruction Multiple Data (SIMD) processors for vision and other applications. There are also Multiple Instruction Multiple Data (MIMD) processors in which the number of processors are normally a few orders of magnitude less than that in SIMD (massively parallel) machines', however, each processor is a powerful general purpose processor with its own program and data memory. Normally, MIMD machines fall into two categories: shared memory and distributed memory machines, though many architectures exhibit both paradigms. Within these classifications, multiprocessors are distinguished according to the interconnection topology between processors or processor-memories. Finally, there are systolic arrays,

hierarchical, partitionable multiprocessor architectures that have been proposed and studied for vision applications. Many of the architectures have been proposed just for vision application but almost all multiprocessors have been studied for vision applications. In the following discussion, we examine many of the architectures, describe the topology, salient features and limitations, and discuss their advantages and disadvantages with respect to solving vision problems. We use the topology as the main classification of the architectures in describing them; however, within a topology, if machines exist that can be further classified, then we will present a discussion on them.

#### **1.2.1.** Mesh connected computers

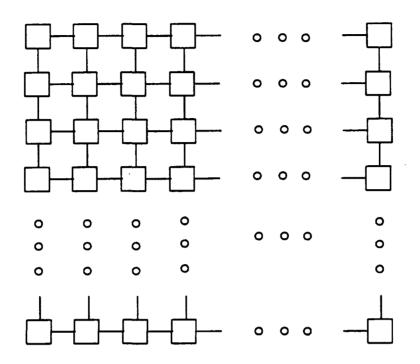

Mesh connected multiprocessors have been one of the first multiprocessors proposed for computer vision and image processing applications. For image processing applications, meshes seem to be an obvious choice because the images map quite naturally onto its structure. Figure 1.1 shows the topology of a mesh-connected computer. A typical machine consists of a large number of processing elements (PEs) arranged in a square array. Most typical is a 4-connected mesh in which each processor is connected to its four nearest neighbors. However, 6 (hexagonal) and 8 connected meshes have also been proposed. Most machines built on this topology are SIMD type of machines. Each PE has its local memory, and it responds in SIMD mode to the instructions broadcast by a controller. The PEs can be selectively masked using mask registers.

The advantage of this architecture is that images map quite naturally onto its structure. When the image size matches the size of the multiprocessor (e.g.,  $N \times N$  mesh for  $N \times N$  image), maximum parallelism can be obtained for those operations that require

Figure 1.1 : A 4-Connected Mesh Computer

computations on individual pixels or a very small neighborhood of pixels. However, this type of architecture has several limitations. There are many low and intermediate level vision algorithms that involve grouping or matching of image structures which are spatially distant in an image. But in meshes, communication across large distances is expensive and inefficient. Therefore, unless the computation is regular and local, meshes do not perform well. Furthermore, meshes have been proposed only as SIMD machines, and that means lack of MIMD processing capability that is necessary to support high level vision. In order to cost-effectively build a multiprocessor with thousands of processors, individual processors must be small, given the technological limitations. Normally, a typical machine will have PEs with 1-bit ALUs and a small memory, which may be sufficient for small pixel based operations but definitely lacks the power that is needed for intermediate

and high level operations. Finally, to most efficiently use a mesh, it is required that the data size exactly match the processor size, which is a severe limitation.

Several mesh-connected multiprocessors have been built. Examples of meshconnected computers include CLIP-4 [5,6,7], GRID [8], GAPP [9], and the MPP [10, 11, 12]. Each of these machines has its own special features, but all of them have the same general form. One major drawback of these machines has been the inefficiency of collecting results and rapid evaluation of the results due to communication bottlenecks. This reflects the fact that they were designed and built as stand-alone image processors used primarily for image enhancements in which the results of processing are intended for interpretation by humans rather than forming the first stage of an autonomous vision system. Several enhancements to a mesh have been proposed to alleviate the global communication problems. Wrapped around connections of the boundary PEs is one of them in which top row PEs are connected to the bottom row PEs and the first column PEs are connected to the last column PEs. This arrangement is called Torus. This reduces the long distance communication time, but the order still remains the same. Other enhancements include connecting PEs in rows and columns by busses to broadcast common data, but these enhancements do not alter the basic structure, advantages and limitations of a mesh-connected computer.

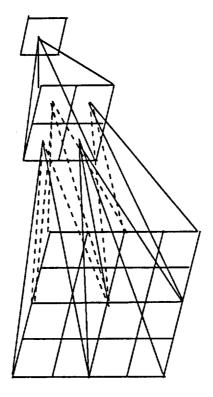

#### **1.2.2.** Pyramid computers

The concept of pyramid computers is essentially an extension of meshes in the third dimension. This structure has been proposed in various forms, but the main idea is that an image sized mesh-connected array is augmented by layers of successively lower resolution mesh-connected arrays as shown in Figure 1.2. Each array in a pyramid is typically one fourth as large as the array below it. Except for the bottom array, each PE in a pyramid is connected to four processors in the level below it, in addition to the neighbor connections in the same level. Formally, a pyramid consists of  $(1/2)\log N + 1$  levels, where the i-th level,  $0 \le i \le (1/2)\log N$ , is a mesh with N/4<sup>i</sup> PEs. Each level has connections to the level above and below, giving each internal PE 9 connections: 4 to its children in the level below, 4 to its nearest neighbors at the same level, and 1 to its parent in the level above. All the PEs operate in SIMD mode under the directions of a single controller. Several pyramids have been proposed and built and examples include PAPIA [13], SPHINX [14], MPP Pyramid [15], HCL Pyramid [16,17], and others [18, 19, 20, 21].

Pyramid multiprocessor architecture provides straightforward implementation of the divide-and-conquer based approach. Such pyramids are natural candidates for executing divide-and-conquer algorithms, as they most closely mirror the flow of information in these algorithms. The pyramid processor provides the capability for quickly changing the resolution of an image, which can significantly improve the execution speed of some low level algorithms, especially for those that depend upon communication between cells that are spatially distant in an image. However, pyramid processors are more difficult to build than meshes because of the more complex arrangement for communication links and require twice the number of processing elements for the same image resolution. Hence, no pyramid multiprocessor has been built commercially.

Despite the fact that a pyramid machine has multiple levels of processing elements, it should not be concluded that a pyramid is suitable for implementing the multiple levels

Figure 1.2 : A Pyramid Multiprocessor

of processing required in an integrated vision system. The pyramid only implements an image resolution hierarchy, whereas vision requires an architecture that implements a hierarchy of abstraction levels. In a pyramid machine, all the processors are identical and execute in SIMD fashion. A vision machine, on the other hand, requires a different type of processing at different levels and in a variety of modes of parallelism including both SIMD and MIMD. Furthermore, from a purely architectural point of view, utilization of pyramid processors, in general, tends to be very low because at each level the slowest processor(s) is (are) the bottleneck, and the pipeline of computation (bottom-up) is limited by the slowest processor, thereby limiting the utilization at all the levels. Therefore,

the pyramid machines, like meshes, are mostly suitable for early low level vision algorithm only and lack the flexibility for and processing capabilities needed for complex vision applications.

The effectiveness and performance of architectures such as pyramid, array processors, and meshes are limited as architectures for integrated vision systems due to several reasons. First, they are mostly suitable for SIMD types of algorithms which only constitute low level vision operations. Second, the architectures are inflexible due to the rigid interconnections. Third, the number of processors needed to solve a problem of reasonable size is thousands. Such a large number of processors is not only cost prohibitive, but the processors themselves cannot be very powerful and can have only limited features due to technological limitations. Fourth, it is normally assumed that the problem size exactly matches the number of processors available. Most of the time it is not clear how to adapt algorithms so that problems of different sizes can be solved on the same number of processors. Finally, the problem of input-output of data and fault-tolerance is rarely addressed in any of these architectures. It is important to note that no matter how fast or powerful a particular architecture is, its utilization can be limited by the bandwidth of the I/O. Furthermore, due to rigidity of most architectures, a failure normally either results in the failure of the entire system, or the performance degrades tremendously. It is important that any architecture for such a complex problem should provide for graceful degradation which can be achieved by flexibility of the interconnect and capabilities to efficiently reconfigure and partition the architecture.

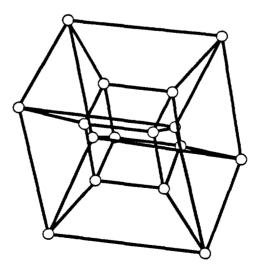

#### 1.2.3. Hypercube multiprocessors

Hypercube multiprocessors provide more efficient long distance communication that is absent in meshes or pyramids. Machines in this class consist of processors connected by communication links whose arrangement is topologically equivalent to an ndimensional cube. A hypercube consists of  $N=2^n$  PEs for an *n* dimensional cube. Each PE is connected to *n* other PEs such that their binary representations differ in exactly one bit position. Therefore, any PE can communicate with any other PE using at most *n* communication links. Figure 1.3 illustrates the organization of a hypercube multiprocessor.

Several commercially available machines have been built that use the hypercube topology. Both SIMD and MIMD types of machines have been built. The Connection machine is an SIMD hypercube multiprocessor [22]. However, in a connection machine, two communication networks are provided. Each PE is connected to its four NEWS neighbors through a NEWS network, and groups of processors are connected in a hyper-

Figure 1.3 : A Hypercube Multiprocessor

cube fashion that provides efficient long distance communication. Such a machine can be used for most low level vision algorithms and some intermediate vision algorithms. However, like in other SIMD machines, lack of MIMD processing capability precludes its use for high level vision. Furthermore, low and intermediate processing cannot occur simultaneously, which is a necessity for complex, real-time vision systems.

MIMD hypercube multiprocessors are also commercially available. In fact, several companies have built MIMD hypercubes of large sizes (up to 1024 processors). Examples include Intel Hypercube [23], NCube [24], and Cosmic cube [25]. A typical processor node in a machine consists of a general purpose microprocessor (e.g., 80386 and coprocessor 80387 in Intel iPSC/2), local memory and routing hardware. Each multiprocessor is controlled by a host processor. The advantage of the hypercubes is that they provide efficient long distance communication between processors. Although hypercube machines with large dimensionality have been built, current systems are not very efficient due to slow communication bandwidths and tremendous overheads of running an application. However, a hypercube machine can be used for some intermediate level and high level vision applications. One major disadvantage with hypercubes is that in order to efficiently utilize the machine, the algorithms running should somehow use the underlying topology. Nevertheless, of most existing machines, hypercubes (especially MIMD) have proved to be the most cost effective machines for research and development of scientific as well as vision applications and have helped tremendously in learning issues in parallel processing in general. But we think that due to rigidity of the architecture, lack of global control and inefficient communication (especially in large machines) will prohibit hypercubes from being multiprocessors for complex vision applications.

#### 1.2.4. Shared memory machines

Shared memory multiprocessors proposed and built are normally MIMD machines. Each PE is a general purpose processor with a small local memory. Each PE has access to a large global memory through an interconnection structure that connects the PEs and the global memory. The design of an interconnection network itself has been a huge area of research. Almost all the machines built today have variations of two common interconnection networks: bus-based and multistage interconnection networks. All the interconnections (in the machines built) are a variation of the two approaches. Bus-based systems have a limitation on the number of processors, due to the bus access bottlenecks, and therefore, are not easily scalable. However, design is relatively simple and costeffective. Machines have been built using up to 32 processors in such a system. Sequent Balance [26] and Encore Multimax [27] are two good examples of bus-based, shared memory multiprocessors that are commercially available.

Another class of shared memory multiprocessors use multistage interconnection networks for processor-processor or processor-memory interconnections. Some bottlenecks of bus based systems are alleviated in such a system; however, the interconnection networks are complex to build. Scalability in such architectures is much better than that in bus-based systems, and machines with up to 128 processors have been built. Most machines built or being built have been for research purposes. Examples of these machines include BBN Butterfly (Commercially available) [28], IBM RP-3 [29], and Cedar, which is being developed at University of Illinois [30]. The main advantage of shared memory architecture is the ease of programming and uniform view of the system. In other words, control of information and synchronization is much easier compared to that in distributed memory systems. Therefore, this class of machine is best suited for high level vision tasks. However, since communication between processor and all the interaction between cooperative tasks is done through the global memory there are bottlenecks, and hot spots occur. Furthermore, accessing global memory is at least an order of magnitude higher than accessing local memories, and therefore, communication speed is very slow compared to computation speed. Hence, such machines are efficient for only large grain parallelism tasks which have little interactions and exhibit regular memory access patterns. Since processes interact with each other using global memory shared variables, the comparative overhead of synchronization is very high and also results in hot spots. Because the actual image processing operations execute relatively quickly when they are divided among multiple processors, the process start-up and synchronization overhead rapidly grows to dominate the processing time. Therefore, scalability is definitely a problem in any shared memory multiprocessors. It is possible to build big machines, but the return of using larger sized shared memory multiprocessors to solve a problem becomes negative beyond a certain size.

### 1.2.5. Systolic arrays

Originally systolic arrays were proposed for special purpose computations. A systolic array multiprocessor consists of processors connected in a certain fashion in which on each machine cycle each processor takes values from its input ports, performs the required computation, and passes the results and data onto its output ports. A systolic array can be perceived as a pipeline of a series of processing stations. Once the pipe is filled with data, all of the processing stations operate on values in parallel. Systolic array

elements can be either general purpose programmable function units or special purpose fixed function units. The latter are not useful for vision applications because of their inflexibility. The primary advantage provided by a programmable systolic array is high performance for low cost. They are, however, best suited for image processing tasks, but can work well with any application that involves large arrays of data and regular computation. The main disadvantage of a systolic array is that any evaluation of processing results must wait until all the data has passed through the array. If a systolic array processes an image in one frame time, then this restriction has the effect of allowing the controlling process to make the decision and change the array's programmed functions once each frame time. In a systolic array, it is thus much more difficult for a vision system to quickly and flexibly adapt its processing strategy to the actual characteristics of an image.

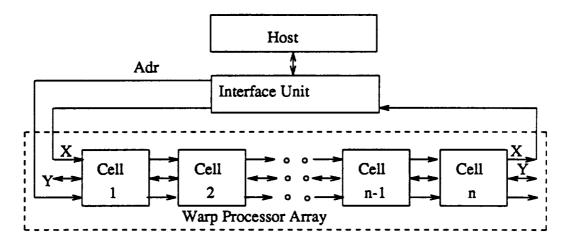

CMU Warp systolic processor is an example of a programmable systolic array designed and built for scientific and image processing applications [31, 32, 33, 34, 35]. The Warp machine is a systolic array computer of linearly connected cells, each of which is a programmable processor capable of performing 10 MFLOPS. Figure 1.4 shows the organization of the Warp computer (taken from [35]). A typical Warp array includes 10 cells, though it is claimed that it can be extended if more cells are needed [35]. The Warp array consists of identical cells called Warp cells, as shown in Figure 1.4 Data flow through the array on two communication channels (X and Y). Those addresses for cells' local memories and control signals that are generated by the Interface Unit propagate down the Adr channel. The direction of Y is statically reconfigurable. For more details the reader is referred to [35]. The Warp array can be used for both fine-grain and large-

Figure 1.4 : Warp System Overview

grain parallelism. It is efficient for fine-grained parallelism because of its high inter-cell bandwidth. It is also claimed to be efficient for large-grain parallelism because it is composed of powerful cells. Each cell is capable of operating independently; it has its own program sequencer and program memory. Even though Warp can perform in many modes, it is mostly suitable for low and intermediate level vision and does not have the desired flexibility, due to its organization, for efficiently performing high level vision algorithms.

### 1.2.6. Partitionable and hierarchical architectures

There have been numerous architectures designed and developed for vision that cannot be put in any of the classes discussed above. Some of the architectures include PM4 [36], PASM [37], REPLICA [38], INSPECTOR [39], and IUA [40]. Design of these architectures has addressed the issues of flexibility, partitionability, and reconfigurability which are needed in an architecture for an IVS. The following is a brief

discussion on some of these architectures, their merits and limitations. An important and common characteristic of these architectures is that they are capable of being partitioned into one or more independent SIMD and MIMD subsystem.

#### **PM4 : A Reconfigurable Multiprocessor :**

The PM4 represents one of the first proposals for a reconfigurable multiprocessor capable of executing several MIMD and SIMD processes concurrently [36]. It includes a large number of processing units constituting a pool. This pool of processing units can be partitioned into groups, each one of which can operate independently in either SIMD or MIMD mode. Reconfiguration of system resources is dynamic and is primarily software controlled. The components of the system include 1) N identical Processor-Memory Units (PMUs), 2) K identical Vector Control Units (VCUs), and 3) A three-level hierarchical memory connected by a set of interconnection networks and memory managements units.

The PMUs are the basic processing units and they include a microprocessor, a local memory and a Local Memory Management Unit (LMMU). The local memory is composed of interleaved memory modules and serves as a local cache for the microprocessor. The VCUs control groups of processors operating in an SIMD mode. The Inter-Processor Communication Network (IPCN) implements permutation functions during the execution of an SIMD process. Management of the shared memory is accomplished by a Shared Memory Management Unit (SMMU), which communicates with the LMMUs and with the File Management Control Unit. The Processor-Memory Interconnection Network transfers bursts of data or instructions between the shared memory and the PMUs.

#### PASM :

The PASM, a Partitionable SIMD MIMD Multiprocessor, is also a dynamically reconfigurable into one or more independent SIMD and/or MIMD machines [37]. The system is composed of Parallel Computation Unit (PCU) which includes N microprocessors, N memory modules and an Interconnection Network (IN) connecting them. There is a set of Q Microcontrollers (MC), each controlling N/Q processors. Memory management tasks are distributed over a set of processors constituting the Memory Management System (MMS). The system is to operate under control of a uniprocessor System Control Unit or SCU which would be responsible for job scheduling and for coordinating loading memory modules within the PCU. Only higher levels of these tasks need to be executed on the SCU; the details can be distributed over the MCs and MMS.

Two processor-memory configurations are being examined for the PCU. In the PEto-PE configuration, each processor has a local memory and the composite processormemory units (PEs) communicate via the IN. When data is to be obtained from the memory of another PE, the two PEs involved cooperate to effect the transfer. Two processors are, therefore, involved for any non-local reference. In the P-to-M configuration, processors are connected on one side of the Interconnection Network and memory modules on the other. The processors do not have a local memory and can access any of the modules on the other side of the network. As a result, no explicit data transfers from one processor to another are required. However, all references now have to go via the Interconnection Network. The system can be partitioned into one or more partitions, each with RN/Q processors, where  $R = 2^r$ . Each partition can operate in either an SIMD or an MIMD mode.

The code required to be transferred to more than one MCs (for execution on corresponding sets of N/Q processors) is broadcast to the selected MCs over a bus.

#### The REPLICA :

The REPLICA was designed as a special purpose computer for multi-sensory perception of 3-D objects [38]. Its main features include support for clean and flexible partitionability with minimal fragmentation and modularity. The machine consists of the following components: 1) A pool of N processing elements, each with a local memory, 2) A two-level control hierarchy. At level-1 are the controllers and at level-2 are monitors. The monitor layer is responsible for scheduling tasks and reconfiguring and partitioning the system. The set of M controllers is uniformly distributed over the system- one for each group of N/M processors, 3) A memory management system controlling a large shared memory and a secondary memory and 4) Four interconnection networks. One network handles communication between monitors and controllers. A second one, a capability enhanced crossbar, connects the controller to the PEs. Shift-register rings are used for communication between PEs within a partition. Finally, a high bandwidth bus is suggested for communication between the PEs, controllers, sensors and memory. This bus is to support I/O and the transfers of data and programs between main memory and the local memories of the PEs.

The clean partitionability is attributed to the capabilities of controller-processor and processor-processor interconnection networks. It is claimed that these networks allow variable size partitions composed of arbitrary subsets of processors. Partitions can be set up rapidly and are totally isolated from each other (i.e., the partitions are clean).

### The Image Understanding Architecture :

The Image Understanding Architecture (IUA) integrates parallel processors operating simultaneously at three levels of computational granularity in a tightly-coupled architecture [40]. Each level of the IUA is a parallel processor that is distinctly different from the other two levels, in order to best meet the processing needs for different levels of algorithms in a computer vision application. Communication between levels takes place via parallel data and control paths.

The bottom level of the architecture contains an associative processor called the Content Addressable Array Parallel Processor (CAAPP). The CAAPP is a 512×512 array of 1-bit serial processors designed to operate on arrays of pixels and to construct intermediate-level tokens from events in an image. At the intermediate level, an array of 64×64 16-bit processors, called the Intermediate Communications and Associative Processor (ICAP), are used for the intermediate level of processing. Specifically, the processors are used for retrieving, comparing and matching tokens, computing geometric relationships between tokens, and constructing new tokens that describe more abstract entities. At the top level (called high level) is the Symbolic Processing Array (SPA) which is a set of 64 processors capable of executing LISP programs. Their function is to support computation involving inference, hypothesis generation and verification, analysis of uncertainty, model-based processing and control of processing at the lower levels. Currently, a 1/64th of the IUA is currently being constructed by the University of Massachusetts and Hughes Research Laboratories.

#### **1.3.** Organization of the Thesis

This thesis contains 7 chapters. The following is an overview of the contents of each chapter and the organization of this thesis.

Chapter 2 presents a model of computation for IVSs. The model is presented from parallel processing perspective. An attempt is made to capture the computation requirements, to recognize data dependencies between tasks, and capture the temporal flow of computation. The model is used to develop architectural requirements for multiprocessors for IVSs applications. These requirements broadly describe features that should be present in a multiprocessor design in order for it to be efficient for IVSs.

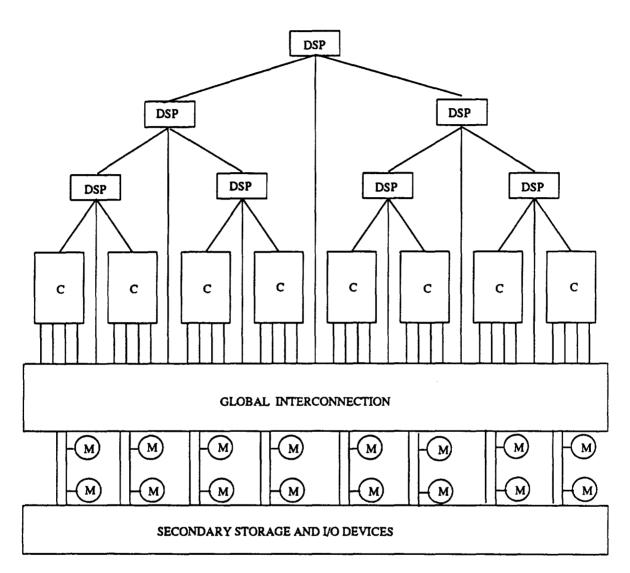

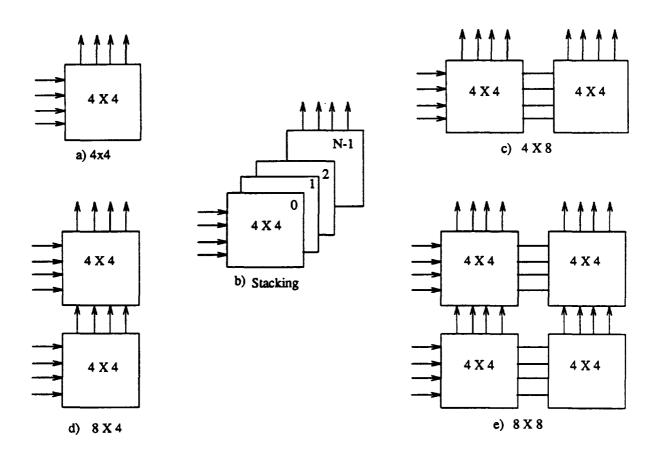

Architecture of NETRA is presented in Chapter 3. NETRA is a recursively defined tree-type hierarchical architecture whose leaf nodes consist of a cluster of processors connected with a programmable crossbar with selective broadcast capability to provide for desired flexibility. The internal nodes are scheduling processors and their function is task scheduling, load balancing, and global memory management. All the scheduling processors and the cluster processor are connected to a global memory through a multistage circuit switched network. The processors in clusters can operate in SIMD, MIMD or systolic mode, and therefore, suitable for both low level as well as high level vision algorithms. A discussion is presented that critically examines the features of NETRA in the light of architectural requirements developed in Chapter 2.

Chapter 4 presents how to map an algorithm on a processor cluster in NETRA in various modes such as SIMD and MIMD. Then performance evaluation of algorithms when mapped on one cluster is presented. The algorithms are chosen so that they exhibit

different communication requirements when mapped in parallel. Performance of some algorithms on a simulated cluster is also presented. It is concluded that good speedups and performance can be obtained on a cluster because of the availability of a programmable crossbar which provides the necessary flexibility in mapping algorithms with varying characteristics.

Inter-cluster communication is discussed in Chapter 5. A general method of analysis of inter-cluster communication is presented. Two alternative inter-cluster communication networks, namely, bus and multistage, are evaluated. The analysis of inter-cluster communication is used to evaluate performance of various algorithms when mapped across multiple clusters. When algorithms are mapped onto multiple clusters, the performance is affected by conflicts and interference in the global interconnection networks. These effects are incorporated in the analysis, and it is concluded that if interconnection bandwidth is fast enough then good performance results can be obtained even in the presence of high conflicts.

Chapter 6 presents data decomposition, load balancing and task scheduling techniques for data dependent algorithms. The techniques exploit the knowledge about the data gathered from the current task and use the knowledge about involved computations in the next task in order to partition the data onto the available processors so that load balancing and high utilization are achieved. In an IVS, in most cases, such information can be available because the flow of tasks and their dependencies are known in advance. In order to evaluate the performance, implementation results for a few algorithms that are part of a motion estimation system are presented when implemented on a hypercube multiprocessor system. The reason for choosing a hypercube multiprocessor is that using an existing machine helps capture the overheads associated with such techniques.

Summary, conclusions and directions for future work are presented in Chapter 7.

# CHAPTER 2.

# MODEL OF COMPUTATION FOR INTEGRATED VISION SYSTEM

Computer vision transcends a wide range of representations and forms of processing. Despite advances in many sub-areas of computer vision, there is no consensus on a unified approach to vision. However, one can define certain general characteristics of an Integrated Vision System (IVS) from computational perspective. For example, it is known that a "vision system" must be able to perform diverse sets of complex operations on a massive amount of data at high speeds. Motion sequences at moderate resolution  $(512\times512 \text{ pixels})$  and typical frame rate (30 frames/sec) in color (3 bytes) involve more than 20 Mbytes of data per second. The amount of computation required for dynamic scene interpretation including labeling objects, surface reconstruction and motion analysis is difficult to estimate; however, for many applications computational power in the range of  $10^{12-14}$  instructions per second is required [40]. Not only are the raw processing needs tremendous, but varying the type of processing capabilities (such as number crunching, symbol manipulation, and data processing ) are required.

Parallel processing in some form has been accepted as the approach to providing the necessary computational power to solve complex vision problems. But several questions remain. What type of parallel processing is best suited? What architectural features are needed? How is the performance of a multiprocessor architecture measured and how is its effectiveness as an architecture for IVSs evaluated? Several attempts have been made

to define benchmarks that capture processing needs for vision tasks [41, 42, 43]. Recently Weems et al. designed a benchmark for integrated vision systems that attempts to capture different forms of processing, and includes algorithms with different characteristics and their interactions [1]. However, the benchmark does not include "time" dimension in the sense that motion and time varying information are omitted from the benchmark.

In this chapter, we attempt to define a model of computation for integrated vision systems (IVS) from parallel processing perspective. The model also includes the time dimension and is more general. It can be used to critically examine a multiprocessor architecture proposed for IVSs. However, it is not a benchmark that can be used to evaluate architectures. Using the model we attempt to identify the architecture requirements for IVSs as well as provide a framework to design new benchmarks to evaluate architectures.

# 2.1. Parallelism in IVSs

Available parallelism in integrated vision systems can be placed in two broad categories: namely, *Spatial* and *Temporal Parallelism*. Within the categories, the available parallelism can be further sub-divided into different classes. The classes depend on the type of tasks (or algorithms) constituting the system, the type of architectures on which the tasks are to be implemented, the methodology used to implement tasks, interactions between the tasks, and control and data flow between the tasks. For example, a task may exhibit suitability for data parallelism at the lowest level and can be implemented on a massively parallel SIMD architecture; or a task may exhibit data dependent, non-uniform computation, and therefore, be suitable for implementation on an MIMD architecture in a sub-tasks parallelism mode in which sub-tasks cooperate to produce results.

Spatial Parallelism is one in which similar operations are applied in all parts of the image data. That is, the data can be divided into many granules and distributed to subtasks which may execute on different processors in parallel. Most vision algorithms exhibit this type of parallelism. In an IVS, each task operates on the output data of the previous task in the system. Therefore, the type of data, and data structures may be different for each task in the system but each form of data can be partitioned into several granules to be processed in parallel. For example, consider an IVS that performs object recognition. The input image is smoothed using some filtering operation, then on the smoothed image an operator is applied for feature extraction, features with similar characteristics are grouped, then matching with the models is performed. Each of these tasks takes the output of the previous tasks as its input and produces an output which becomes the input for the next task. Note that within spatial parallelism, depending on the computation involved, an algorithm implementation may be suitable for data parallelism or both.

Temporal Parallelism is available when these tasks are repeated on a time sequence of images or on different resolutions of images. For example, the system in which motion of a moving object is estimated takes a sequence of images of the moving object and performs the same set of computation on all image frame(s). The processing of each frame or a set of frames can be done in parallel with the processing of frames of other time instances.

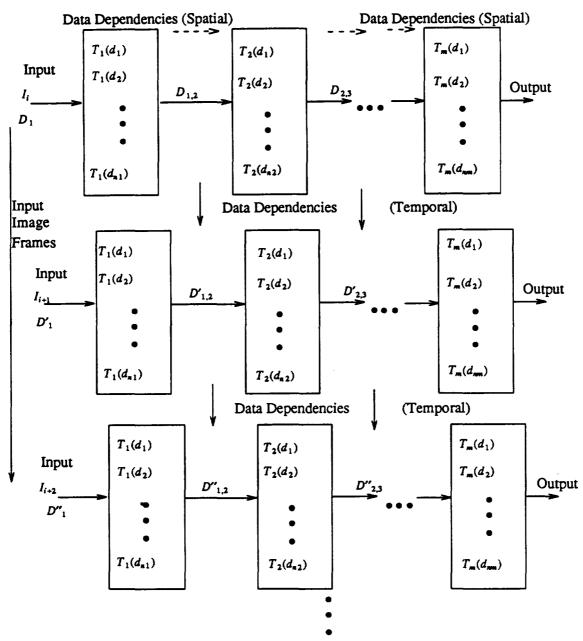

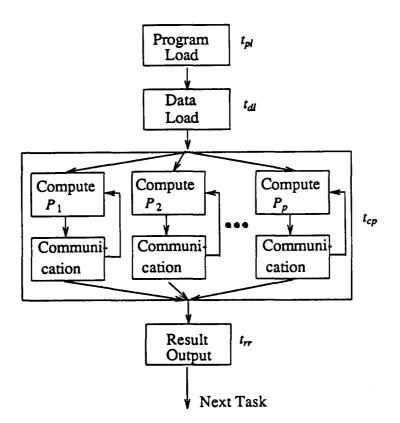

Figure 2.1 shows the computational model for IVS which illustrates the above mentioned characteristics of an IVS. Each pipeline shows a number of tasks applied to a set of inputs. The input to the first task in a pipeline is the image, and the input to the rest of the tasks is the output of the previous task. The set of pipelines illustrates that the entire pipeline of tasks is repeated on different images in time and/or resolution. Each block in the pipeline represents one task. Each task is decomposed into subtasks to be performed in parallel. For example,  $T_1$  is one task, and  $T_1(d_1)$  is a subtask of  $T_1$  operating on data granule  $d_1$ . The figure shows m tasks in the pipeline. The number of subtasks depends on the amount of data in a granule and number of available processors.  $D_{i,i+1}$  represents data transfer from task  $T_i$  to task  $T_{i+1}$  in the pipeline. The model does not make any assumptions about a particular implementation of a task.

### 2.2. Data Dependencies

Existence of spatial and temporal parallelism may also result in two types of data dependencies, namely, *spatial data dependency* and *temporal data dependency*. Spatial data dependency can be classified into intratask data dependency and intertask data dependency. Intratask data dependencies arise when a set of subtasks needs to exchange data in order to execute a task in parallel. The exchange of data may be needed during the execution of the algorithm, or to combine the partial results, or both. Therefore, each task itself is a collection of subtasks which may be represented as a graph with nodes representing the subtasks and edges representing communication between subtasks. Intertask data dependency denotes the transfer and reorganization of data to be passed onto the next task in the pipeline. The mode of communication may be subtasks of the current

Figure 2.1 : Model of Computation for an Integrated Vision System

tasks to the subtasks of the next task, or collection and reorganization of the output data of the current task and then redistribution of the data for the next task. The choice and method depend on the underlying parallel architecture and mapping of algorithms. Tem-

poral data dependency is similar to spatial data dependency except that some form of output generated by tasks executed on the previous image frames may be needed by one or more tasks executing on the current image frames. A simple example of such a dependency is the IVS of motion estimation in which features from the previous image frames are needed in the processing of the current image frames so that features can be matched to establish correspondence between features of different time frames.

The total computation to execute one pipeline includes time to input data, time to output data and results, sum of the times to execute all tasks in the pipeline (which includes computation time of subtasks and communication time between subtasks) and, data transfer and reorganization time between two successive tasks. Let's denote  $t_{cp}$  as computation time for a subtask,  $t_{comm}$  as total communication time for a task,  $t_{in}$  as data input time,  $t_{out}$  as data output time, and  $t_d$  as data transfer and reorganization time. Then time to complete task *i*, denoted as  $\tau_i$  is given by

$$\tau_i = \underset{1 \le j \le ni}{MAX} t_{cp}(T_i(d_j)) + t_{comm}(T_i)$$

(2.1)

Total time to execute one pipeline including the input and output of data is given by

$$t_{tot} = \sum_{i=1}^{i=m} \tau_i + \sum_{i=1}^{i=m-1} t_d(D_{i,i+1}) + t_{in} + t_{out}$$

(2.2)

Let us now consider some characteristics of the algorithms involved in IVS, and using the above model determine desired features and capabilities of a multiprocessor architecture suitable for IVS. First, an IVS involves algorithms from all levels of processing, i.e., an IVS normally includes low, medium and high level vision algorithms. Typically, the first few tasks of the pipeline are low level algorithms and the last few are high level algorithms. The low level algorithms are well understood and well defined. They are normally data independent, have regular structure, and spatial parallelism is mostly available at pixel level. They are well suited for both SIMD and MIMD type of processing. If communication between processors is fast enough, almost linear speedups are possible. Therefore, an architecture for IVS should be capable of efficiently executing low level algorithms and algorithms suited for SIMD type of processing. Also, data I/O should not be a bottleneck because otherwise, speedups through parallelism can be nullified. Examples of low level algorithms include most transforms, filtering algorithms, and convolution algorithms.

High level algorithms are not well understood. They are normally global data dependent, involve more complex data structures (compared to pixel representation), and need varying communication for parallel processing. These type of algorithms are more suited for MIMD type of processing. Hence, the architecture should be capable of executing MIMD algorithms efficiently.

# 2.3. Features and Capabilities of Parallel Architectures for IVSs

The following are the architecture requirements for a multiprocessor architecture to be suitable for integrated vision systems. First, the ability to transform image data (pixel data) into a set of meaningful symbols that describe it. Second, the ability to process pixel and symbol data in parallel as well as concurrently. Third, the ability to simultaneously maintain low, intermediate and high level representations, and the ability to perform low, intermediate and high level algorithms simultaneously on inter-related or independent data. Fourth, fast I/O and processing rates for huge amounts of data at all levels of computations. Fifth, the ability to select particular subsets of data for varying types of processing. Finally, the ability to perform top-down as well as bottom-up processing efficiently, and the ability to report the results efficiently. These are some of the broad requirements for an architecture for integrated vision systems. From the above discussion we can transform the requirements into specific architecture requirements as presented below.

- (1) Reconfigurability: From the model and the preceding discussion it is clear that multiple levels of representations and stages of processing are essential and require very different types of processing. Hence, the architecture should be capable of executing both SIMD and MIMD type computations efficiently. That is, it should be possible to reconfigure the architecture such that each algorithm can be implemented efficiently using the most suited mode of computation.

- (2) Flexible Communication: Fine grained and high speed communication is required both among the processes at each level and between the different processing levels. The communication requirements vary for different algorithms. The communication pattern between processors executing subtasks of a larger task depends on the algorithm involved in the task. If the connectivity between processors is too rigid then the communication overhead of intratask and intertask communication may become prohibitive. Therefore, it is desirable that the communication be flexible in order to provide the most efficient communication with low overhead.

- (3) Resource Allocation and Partitionability: As we discussed earlier, there are several tasks with vastly different characteristics and computational requirements in an IVS. These tasks need to exist simultaneously in the system. Therefore, the system

should be partitionable into many independently controlled subsystems to execute each task. Since the high level algorithms exhibit varying level of parallelism and data dependent performance, it should be possible to allocate resources (such as processors, memory) dynamically to meet the performance requirements.

- (4) Load Balancing and Task Scheduling: Load balancing and task scheduling are very important, especially for high level vision algorithms, which are data dependent, and therefore, in order to obtain better utilization of resources and better speedups, dividing the computation equally among the processor is critical [44]. The underlying architecture on which load balancing is done and the type of algorithm(s) involved contribute significantly to how well load balancing can be achieved. In low level algorithms since the computations are data independent, partitioning data equally among the processors normally balances the load among them. However, for high level algorithms, more sophisticated load balancing and scheduling strategies are needed. The architecture should include features such that it is easy to perform load balancing and task scheduling and that the overhead of doing so is minimal.

- (5) Topology and Data Size Independent Mapping: For a system as complex as an IVS, if the underlying architecture and its interconnect is rigid such that the problem size that can be solved on it or how it can be mapped is tied to the interconnection, the effectiveness of the architecture will diminish as an architecture for an IVS.

- (6) Fault-Tolerance: Fault-tolerance is an important part of a system of such complexity. A failure in a processor or communication structure should not affect the per-

formance drastically, which is normally the case when rigid interconnections are present between processors. The architecture should provide for graceful degradation in case of failures.

(7) Input-Output: It is most often the case that an architecture is able to perform very well on some algorithms, and high speedups are obtained, but input-output (I/O) of data is inefficient. I/O is an integral part of a system and if it is a bottleneck then performance of the system will be limited.

#### **2.4.** Examples of Integrated Vision Systems

#### **2.4.1.** Image understanding benchmark