#### PARALLEL BLOCK-DIAGONAL-BORDERED SPARSE LINEAR SOLVERS FOR POWER SYSTEMS APPLICATIONS

by David P. Koester

#### Abstract of Dissertation October, 1995

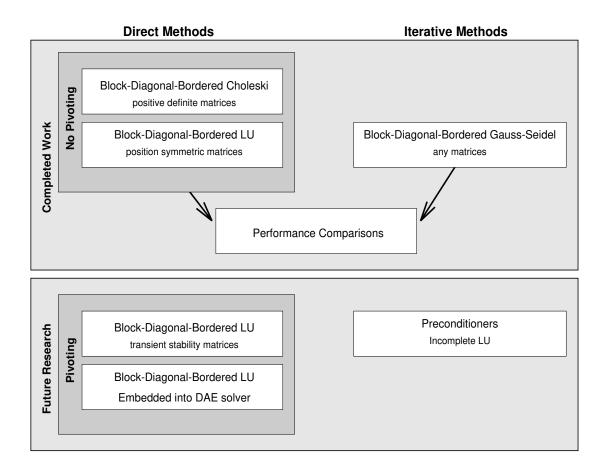

This thesis presents research into parallel linear solvers for block-diagonal-bordered sparse matrices. The block-diagonal-bordered form identifies parallelism that can be exploited for both direct and iterative linear solvers. We have developed efficient parallel block-diagonal-bordered sparse direct methods based on both LU factorization and Choleski factorization algorithms, and we have also developed a parallel block-diagonal-bordered sparse iterative method based on the Gauss-Seidel method. Parallel factorization algorithms for block-diagonal-bordered form matrices require a specialized ordering step coupled to an explicit load balancing step in order to generate this matrix form and to distribute the computational workload uniformly for an irregular matrix throughout a distributed-memory multi-processor. Matrix orderings are performed using a diakoptic technique based on node-tearing-nodal analysis. Parallel Gauss-Seidel algorithms for block-diagonal-bordered form matrices require a two-part matrix ordering technique — first to partition the matrix into block-diagonal-bordered form, again, using the node-tearing diakoptic techniques. The ordered matrices have extensive parallelism, while maintaining the strict precedence relationships in the Gauss-Seidel algorithm.

Empirical performance measurements for real power system networks are presented for implementations of a parallel block-diagonal-bordered LU algorithm, a similar Choleski algorithm, and a parallel block-diagonal-bordered Gauss-Seidel algorithm run on a distributed memory Thinking Machines CM-5 multi-processor. We have compared the performance of the direct and iterative parallel implementations on the CM-5, and show that significant algorithmic speedup may be possible for the Gauss-Seidel algorithm versus Choleski factorization for positive definite matrices. We have developed a simple technique that uses empirical data to predict the performance of these algorithms on future architectures. We apply these techniques to develop algorithm performance predictions for future Scalable Parallel Processing (SPP) architectures.

#### PARALLEL BLOCK-DIAGONAL-BORDERED SPARSE LINEAR Solvers for Power Systems Applications

by DAVID P. KOESTER M.A.S., The Ohio State University, 1978 B.A., Augustana College, 1977

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer and Information Science in the Graduate School of Syracuse University

October, 1995

Approved \_

Professor Geoffrey C. Fox

Approved \_

Professor Sanjay Ranka

Date \_\_\_\_\_

© Copyright 1995 David P. Koester To my loving wife

## Ann

and my super children

Yuri, Zachary, Naomi, and Abram

# Acknowledgments

I am deeply indebted to the late Professor Yehuda Wallach, my first advisor, for both inspiring me to pursue my degree and providing me with my initial insights into the use of diakoptics to provide parallelism in power systems network applications. To say that Professor Wallach was passionate about diakoptics would have been an understatement!

I am grateful that Professor Wallach accommodated my part-time student status with weekend meetings at his home. These meetings invariably included the gracious hospitality of tea and snacks provided by his wife, Rachel. I worked with Professor Wallach during the Gulf War (Spring semester 1991), and several meetings were interrupted as Yehuda and Rachel anxiously awaited telephone calls from their daughter in Israel to indicate that she was safe after Iraqi Scud missile attacks. After a telephone call confirmed his daughter's safety, Professor Wallach would resume our meeting.

My research confirmed that Professor Wallach's intuition was correct concerning the applicability of diakoptic techniques as the basis for efficient parallel linear solver algorithms for power systems network applications. May this research stand as a testament to his memory.

\* \* \*

There are many individuals in the academic community to whom I am deeply indebted. First, I would like to thank my co-advisors, Professors Geoffrey C. Fox and Sanjay Ranka, for their assistance and guidance during my years of work on my research. As co-advisors, they provided a good balance of interest in my research. Professor Nancy McCracken, the third member of my research committee, provided guidance and much needed support as I attempted to balance a (nearly) full-time job, my academic research, and my family. I would like to thank Professor Tony Skjellum of Mississippi State University and Professor Chis Pottle of Cornell University for their contributions to this research: their comments helped me make notable improvements to this work. Special thanks go to Alvin Leung, a Graduate Research Assistant at the Northeast Parallel Architectures Center (NPAC), for porting software developed for the Thinking Machines CM-5 to the IBM SP1 and SP2 and for running benchmarks of the software on that architecture. Lastly, I would like to express my gratitude to Dr. Paul Coddington, Senior Researcher Scientist at NPAC, for his contributions to this research and for his friendship.

I owe additional thanks to Professor Fox, who as director of NPAC provided me with the infrastructure, an office, a workstation, travel funds, and access to parallel computer resources, to pursue my research. This support was funded in part by Niagara Mohawk Power Corporation, the New York State Science and Technology Foundation, the NSF under co-operative agreement No. CCR-9120008, and ARPA under contract #DABT63-91-K-0005. I am also grateful to have had the opportunity to professionally associate with the many fine intellects that Geoffrey has assembled at Syracuse University.

\* \* \*

I gratefully acknowledge the financial assistance and the time provided me to work on my research by my employer, The MITRE Corporation, through their Advanced Graduate Degree program.

\* \*

Finally, I wish to express my special gratitude for the many years of support from my loving wife, Ann, and my super children: Yuri, Zachary, Naomi, and Abram. I hope that my children are as proud of me as I, at the age of thirteen, was of my father when he received his high school equivalency diploma.

Ann, I love you so very much.

# Contents

| A        | ckno           | wledgments                                                       | iv       |

|----------|----------------|------------------------------------------------------------------|----------|

| Li       | st of          | Tables                                                           | x        |

| Li       | st of          | Figures                                                          | xi       |

| 1        | Inti           | roduction                                                        | 1        |

|          | 1.1            | The State of Parallel Power Systems Linear Solver Research       | <b>2</b> |

|          | 1.2            | Block-Diagonal-Bordered Power System Matrices                    | 3        |

|          |                | 1.2.1 Block-Diagonal-Bordered Direct Linear Solvers              | 5        |

|          |                | 1.2.2 Block-Diagonal-Bordered Iterative Linear Solvers           | 6        |

|          | 1.3            | Low-Latency Communications                                       | 6        |

|          | 1.4            | Embedded Software Applications                                   | 7        |

|          | 1.5            | Organization of this Thesis                                      | 8        |

| <b>2</b> | Pov            | ver System Applications                                          | 10       |

|          | 2.1            | Load-Flow Analysis                                               | 10       |

|          | 2.2            | Transient Stability Analysis                                     | 11       |

|          | 2.3            | Power System Network Matrices                                    | 12       |

|          | 2.4            | Pseudo-Images Representing Sparse Power Systems Network Matrices | 14       |

| 3        | $\mathbf{Lin}$ | ear Solvers                                                      | 17       |

|          | 3.1            | Direct Methods                                                   | 17       |

|          |                | 3.1.1 LU Factorization                                           | 18       |

|          |                | 3.1.2 Choleski Factorization                                     | 18       |

|          |                | 3.1.3 Ordering Sparse Matrices for Direct Methods                | 21       |

|          |                | 3.1.4 A Survey of the Literature for Parallel Direct Methods     | 23       |

|          | 3.2            | Iterative Methods                                                | 25       |

|          |                                         | 3.2.1   | Gauss-Seidel                                                                        | 25 |

|----------|-----------------------------------------|---------|-------------------------------------------------------------------------------------|----|

|          |                                         | 3.2.2   | Ordering Sparse Matrices for Iterative Methods                                      | 27 |

|          |                                         | 3.2.3   | A Survey of the Literature for Parallel Iterative Methods                           | 28 |

| 4        | Αvε                                     | ailable | Parallelism                                                                         | 29 |

|          | 4.1                                     | Availa  | able Parallelism in Block-Diagonal-Bordered Form Matrices for Direct Methods        | 30 |

|          | 4.2                                     | Availa  | able Parallelism in Block-Diagonal-Bordered Form Matrices for Iterative Methods     | 35 |

|          |                                         | 4.2.1   | Parallelism in Block-Diagonal-Bordered Matrices                                     | 36 |

|          |                                         | 4.2.2   | Parallelism in Multi-Colored Matrices                                               | 38 |

| <b>5</b> | $\mathbf{T}\mathbf{h}\mathbf{\epsilon}$ | e Prep  | rocessing Phase                                                                     | 41 |

|          | 5.1                                     | The P   | Preprocessing Phase for Direct Methods                                              | 42 |

|          |                                         | 5.1.1   | Ordering                                                                            | 42 |

|          |                                         | 5.1.2   | Pseudo-Factorization                                                                | 43 |

|          |                                         | 5.1.3   | Load Balancing                                                                      | 44 |

|          | 5.2                                     | The P   | reprocessing Phase for Iterative Methods                                            | 45 |

|          |                                         | 5.2.1   | Ordering                                                                            | 46 |

|          |                                         | 5.2.2   | Pseudo-Solution                                                                     | 47 |

|          |                                         | 5.2.3   | Load Balancing                                                                      | 47 |

| 6        | Par                                     | allel S | parse Matrix Solver Implementations                                                 | 49 |

|          | 6.1                                     | Seque   | ntial Code Optimization                                                             | 49 |

|          | 6.2                                     | Parall  | el Sparse Direct Solver Implementations                                             | 51 |

|          |                                         | 6.2.1   | The Hierarchical Data Structure                                                     | 53 |

|          |                                         | 6.2.2   | Parallel Blocked-Diagonal-Bordered LU Factorization                                 | 56 |

|          |                                         | 6.2.3   | Forward Reduction and Backward Substitution                                         | 59 |

|          | 6.3                                     | Parall  | el Sparse Iterative Solver Implementations                                          | 61 |

|          |                                         | 6.3.1   | The Hierarchical Data Structure                                                     | 62 |

|          |                                         | 6.3.2   | Parallel Blocked-Diagonal-Bordered Gauss-Seidel                                     | 63 |

| 7        | $\mathbf{Em}$                           | pirical | Results for Parallel Linear Solvers                                                 | 67 |

|          | 7.1                                     | Empir   | rical Results for Parallel Direct Linear Solvers                                    | 67 |

|          |                                         | 7.1.1   | Ordering Power Systems Network Matrices into Block-Diagonal-Bordered Form           | 68 |

|          |                                         | 7.1.2   | Parallel Direct Sparse Solver Performance                                           | 72 |

|          |                                         |         | 7.1.2.1 Selecting Partitioned Matrices with <i>Best</i> Parallel Solver Performance | 75 |

|          |                                         |         | 7.1.2.2 Timing Performance Comparisons                                              | 76 |

|          |                                         |         | 7.1.2.3 Examining Speedup                                                           | 78 |

|   |     | 7.1.2.4 Analyzing Algorithm Component Performance 81                                   |

|---|-----|----------------------------------------------------------------------------------------|

|   |     | 7.1.3 Comparing Communications Paradigms                                               |

|   |     | 7.1.4 Algorithm Performance for the IBM SP1 and SP2                                    |

|   |     | 7.1.5 Conclusions                                                                      |

|   | 7.2 | Empirical Results for the Parallel Iterative Linear Solver                             |

|   |     | 7.2.1 Ordering Power Systems Network Matrices into Block-Diagonal-Bordered Form 90     |

|   |     | 7.2.2 Parallel Sparse Gauss-Seidel Performance                                         |

|   |     | 7.2.2.1 Selecting Partitioned Matrices with <i>Best</i> Parallel Solver Performance 95 |

|   |     | 7.2.2.2 Timing Performance Comparisons                                                 |

|   |     | 7.2.2.3 Examining Speedup                                                              |

|   |     | 7.2.2.4 Analyzing Algorithm Component Performance                                      |

|   |     | 7.2.3 Convergence Rate 102                                                             |

|   |     | 7.2.4 Comparing Communications Paradigms                                               |

|   |     | 7.2.5 Conclusions                                                                      |

|   | 7.3 | Comparing Parallel Direct and Iterative Algorithms                                     |

|   |     | 7.3.1 Parallel Choleski versus Parallel Gauss-Seidel                                   |

|   |     | 7.3.2 Parallel LU Solvers versus Parallel Gauss-Seidel                                 |

|   |     | 7.3.3 Conclusions                                                                      |

| 8 | Alg | orithm Performance on Future SPP Architectures 115                                     |

|   | 8.1 | Parallel Computing for the Power Utility Industry                                      |

|   | 8.2 | Overhead-Based Performance Estimates                                                   |

|   | 8.3 | Performance Predictions for Direct Solvers                                             |

|   |     | 8.3.1 Model Validation                                                                 |

|   |     | 8.3.2 Performance Predictions                                                          |

|   | 8.4 | Performance Predictions for Iterative Solvers                                          |

|   | 8.5 | Low-Latency Communications Considerations                                              |

|   | 8.6 | Conclusions                                                                            |

| 9 | Cor | nclusions 127                                                                          |

|   | 9.1 | Direct Methods                                                                         |

|   | 9.2 | Iterative Methods                                                                      |

|   | 9.3 | Comparisons of Direct and Iterative Methods                                            |

|   | 9.4 | Future Architectures                                                                   |

|   | 9.5 | Future Research Opportunities                                                          |

| $\mathbf{A}$ | Nomenclature                                            | 138 |

|--------------|---------------------------------------------------------|-----|

|              | A.1 Parallel Processor Architectures                    | 138 |

|              | A.2 Parallel Computing Analysis                         | 138 |

| в            | Node-Tearing Nodal Analysis                             | 142 |

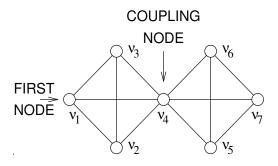

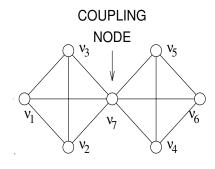

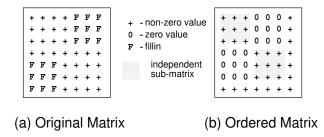

|              | B.1 The Node-Tearing Algorithm                          | 142 |

|              | B.2 An Example of Node-Tearing                          | 145 |

|              | B.3 The Node-Tearing Implementation                     | 148 |

| $\mathbf{C}$ | Minimum-Degree Ordering                                 | 150 |

| D            | Graph Coloring                                          | 152 |

|              | D.1 The Basic Greedy Graph Coloring Heuristic           | 152 |

|              | D.2 The Saturation Degree Ordering Heuristic            | 153 |

| Е            | Implementation Pseudo-Code                              | 155 |

|              | E.1 Parallel Blocked-Diagonal-Bordered LU Factorization | 155 |

|              | E.2 Parallel Blocked-Diagonal-Bordered Gauss-Seidel     | 156 |

| $\mathbf{F}$ | Network Ordering Performance Statistics                 | 174 |

|              | F.1 Parallel Direct Solver Statistics                   | 174 |

|              | F.2 Parallel Iterative Solver Statistics                | 174 |

# List of Tables

| 2.1  | Comparison of Power System Matrices and Boeing-Harwell Structural Matrices | 16  |

|------|----------------------------------------------------------------------------|-----|

| 7.1  | EPRI6K - IBM SP1 and $SP2$ Performance Data - Complex Variate LU Solver    | 88  |

| 7.2  | Convergence for the BCSPWR09 Power Systems Network                         | 102 |

| 7.3  | Convergence for the BCSPWR10 Power Systems Network                         | 103 |

| F.1  | BCSPWR09 - LU and Choleski Factorization Ordering Statistics               | 175 |

| F.2  | BCSPWR10 - LU and Choleski Factorization Ordering Statistics               | 175 |

| F.3  | EPRI6K — LU and Choleski Factorization Ordering Statistics                 | 176 |

| F.4  | NiMo-OPS — LU and Choleski Factorization Ordering Statistics               | 176 |

| F.5  | NiMo-PLANS — LU and Choleski Factorization Ordering Statistics             | 177 |

| F.6  | BCSPWR09 — Gauss-Seidel Ordering Statistics                                | 177 |

| F.7  | BCSPWR10 — Gauss-Seidel Ordering Statistics                                | 178 |

| F.8  | EPRI6K — Gauss-Seidel Ordering Statistics                                  | 179 |

| F.9  | NiMo-OPS — Gauss-Seidel Ordering Statistics                                | 180 |

| F.10 | NiMo-PLANS — Gauss-Seidel Ordering Statistics                              | 181 |

# List of Figures

| 1.1 | Summary of Completed and Future Research                                                                                | 4  |

|-----|-------------------------------------------------------------------------------------------------------------------------|----|

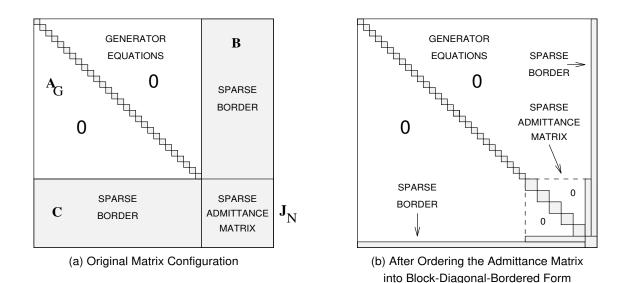

| 2.1 | Ordering the Admittance Sub-Matrix in Transient Stability Differential-Algebraic                                        |    |

|     | Equations                                                                                                               | 11 |

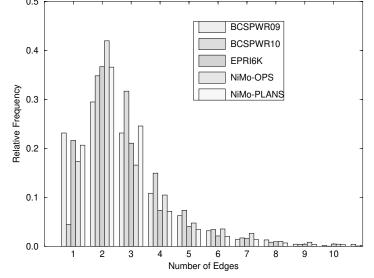

| 2.2 | Relative Frequency Histogram of Edges per Graph Node                                                                    | 14 |

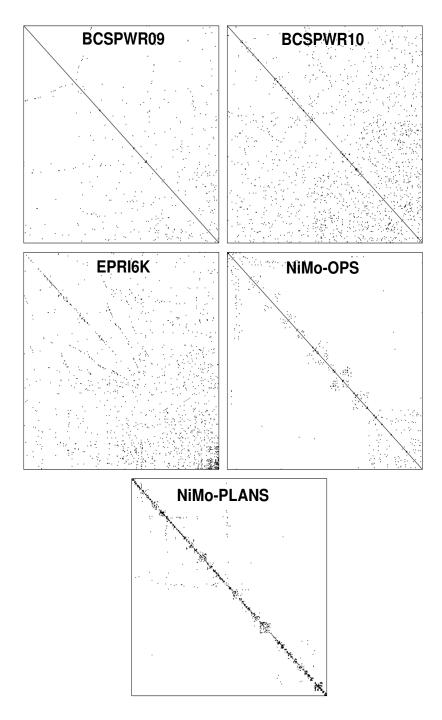

| 2.3 | Pseudo-Images of Original Sparse Power Systems Matrices                                                                 | 15 |

| 3.1 | Sparse LU Factorization — Doolittle Algorithm                                                                           | 19 |

| 3.2 | Sparse Forward Reduction for Doolittle Factorization                                                                    | 19 |

| 3.3 | Sparse Backward Substitution for Doolittle Factorization                                                                | 20 |

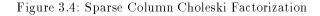

| 3.4 | Sparse Column Choleski Factorization                                                                                    | 20 |

| 3.5 | Sparse Forward Reduction for Choleski Factorization                                                                     | 21 |

| 3.6 | Sparse Backward Substitution for Choleski Factorization                                                                 | 21 |

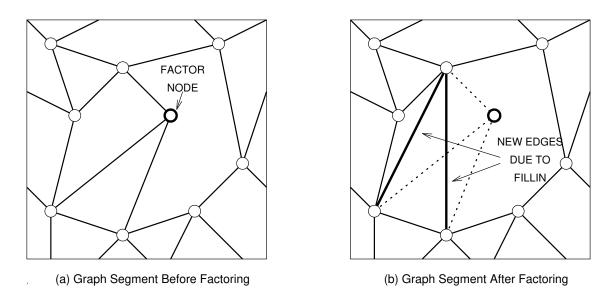

| 3.7 | Graph Theoretical Explanation of Fillin                                                                                 | 23 |

| 3.8 | Sparse Gauss-Seidel Algorithm                                                                                           | 27 |

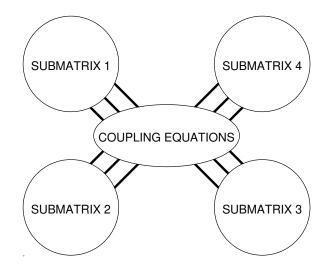

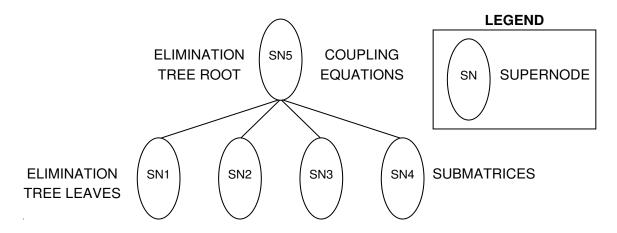

| 4.1 | Graph with Four Independent Sub-Matrices                                                                                | 31 |

| 4.2 | Elimination Tree with Four Supernode Leaves                                                                             | 31 |

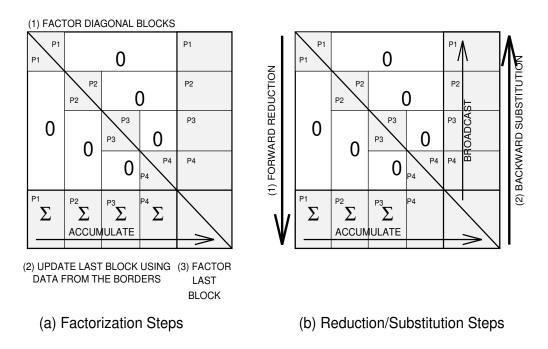

| 4.3 | Block Bordered Diagonal Form Sparse Matrix Solution Steps                                                               | 36 |

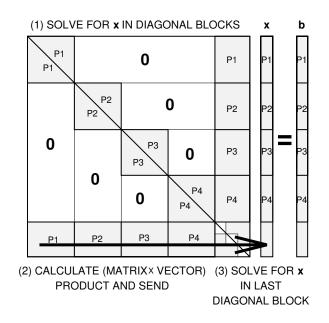

| 4.4 | Block-Bordered-Diagonal Form Gauss-Seidel Method                                                                        | 39 |

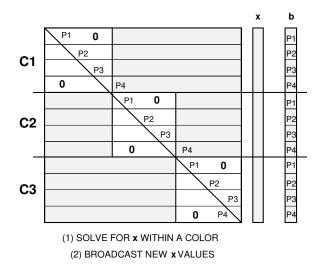

| 4.5 | Multi-Colored Gauss-Seidel Method for the Last Diagonal Block                                                           | 40 |

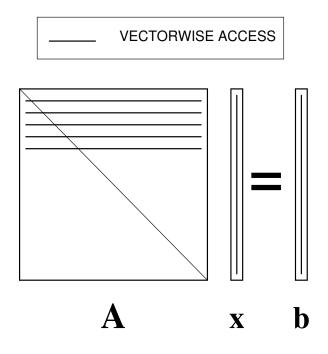

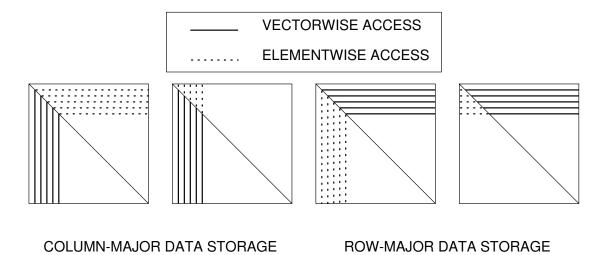

| 6.1 | Optimal Row-Major Data Storage for Gauss-Seidel Algorithms                                                              | 50 |

| 6.2 | Optimal Data Storage for Dense Factorization                                                                            | 51 |

| 6.3 | Optimal Data Storage for Sparse Factorization — Doolittle's Algorithm $\ldots \ldots \ldots$                            | 52 |

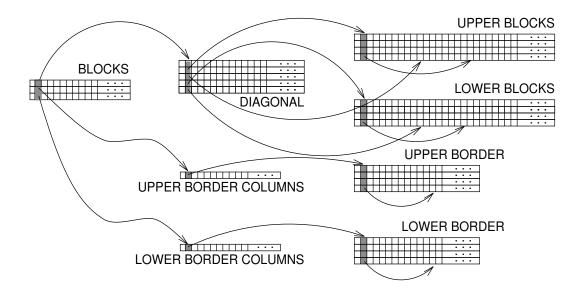

| 6.4 | The Hierarchical Data Structure for Parallel LU Factorization                                                           | 54 |

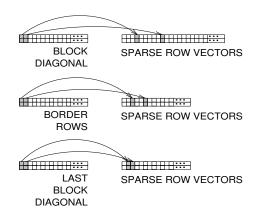

| 6.5 | The Hierarchical Data Structure for Parallel Gauss-Seidel Methods                                                       | 63 |

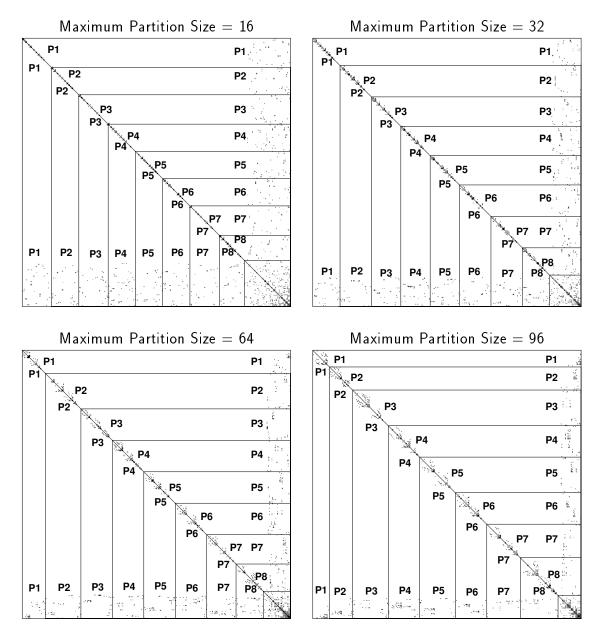

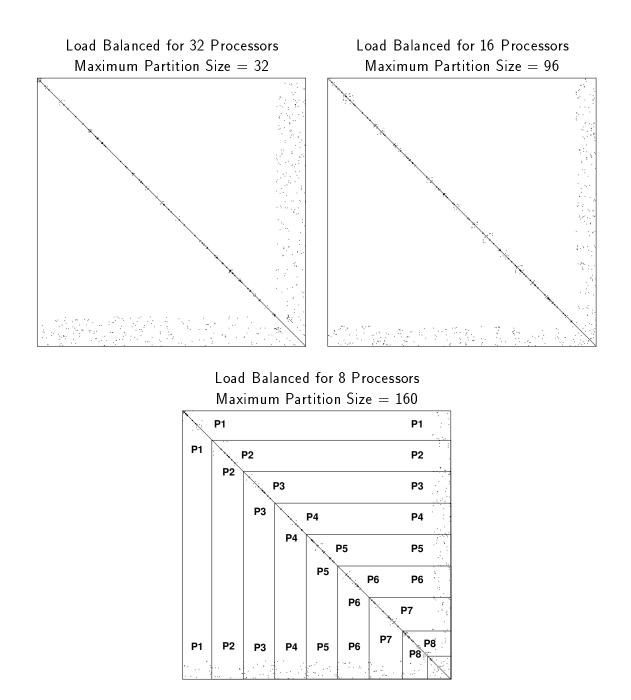

| 7.1 | $\operatorname{BCSPWR09}$ — Block-Diagonal-Bordered Form — Load Balanced for 8 Processors $% \operatorname{BCSPWR09}$ . | 70 |

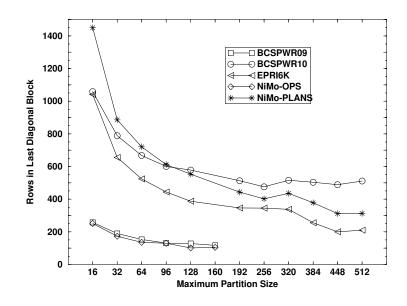

| 7.2 | Last Diagonal Block Size after Partitioning                                                                             | 71 |

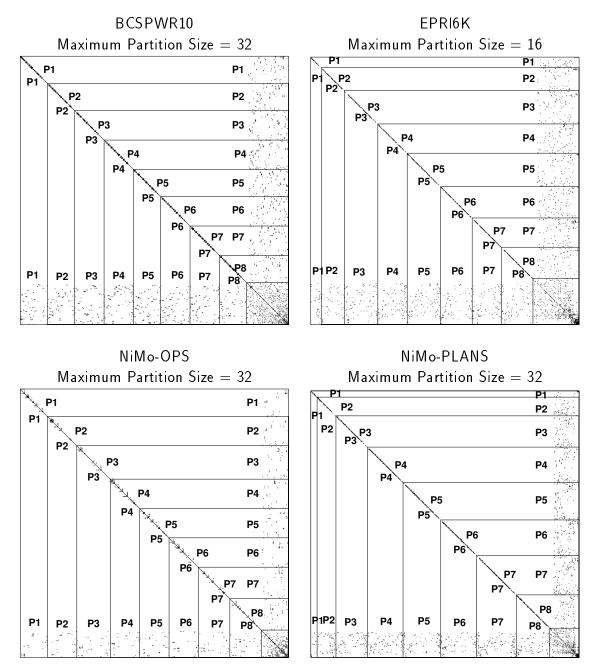

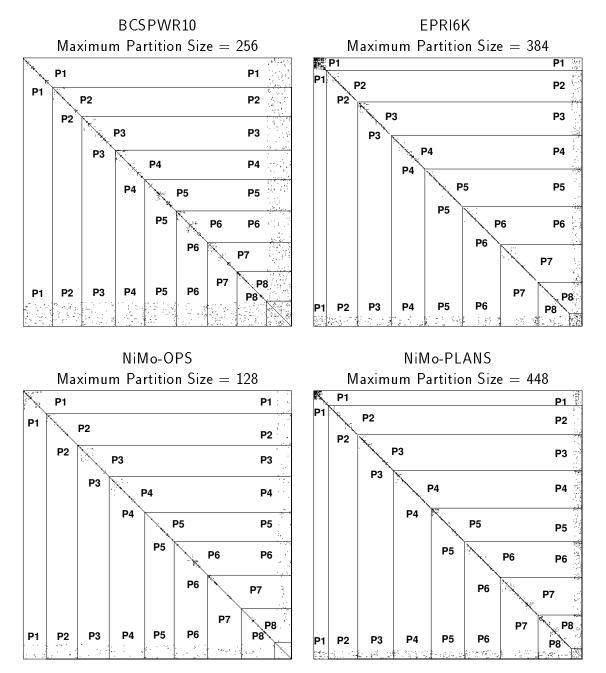

| 7.3 | Block-Diagonal-Bordered Form Matrices — Load Balanced for 8 Processors $\ldots$ .                                       | 73 |

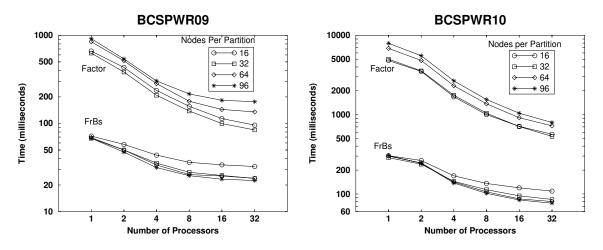

| 7.4 | Parallel LU Factorization Timing Data — Double Precision                                                                | 75 |

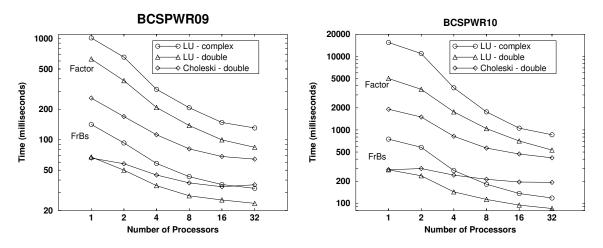

| 7.5         | Parallel Choleski and LU Timing Comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

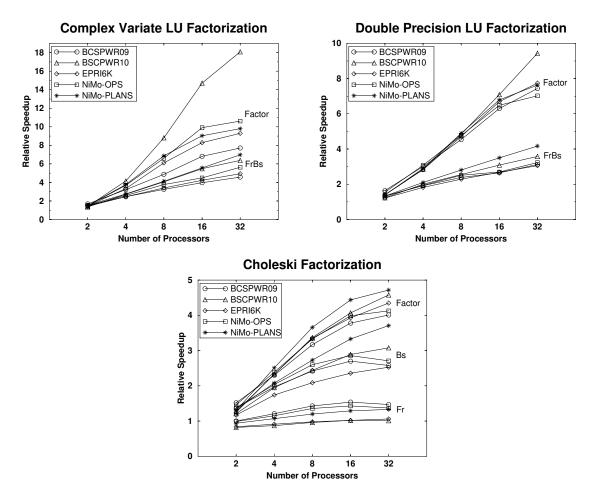

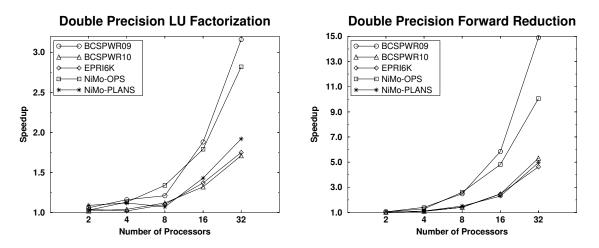

| 7.6         | Relative Speedup — Parallel Direct Solvers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78  |

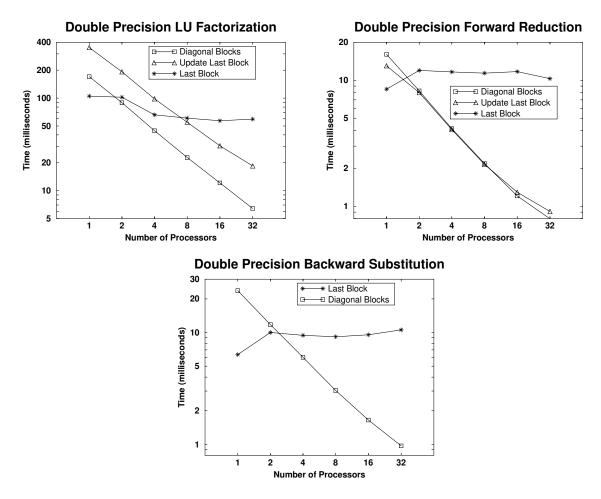

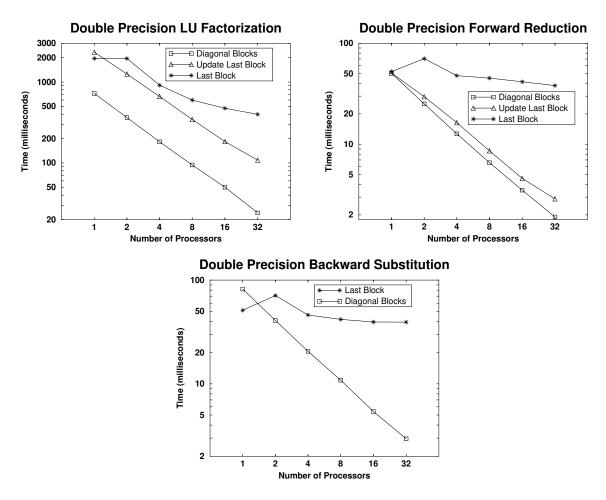

| 7.7         | BCSPWR09 — Algorithm Component Timing Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82  |

| 7.8         | BCSPWR10 — Algorithm Component Timing Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83  |

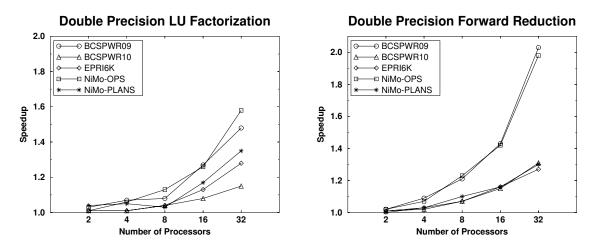

| 7.9         | Speedup — Low-Latency versus Buffered Communications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85  |

| 7.10        | ${ m Speedup} - { m Low-Latency} \ { m versus} \ { m Buffered} \ { m Communications} - { m Update} \ { m Last} \ { m Block}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86  |

| 7.11        | BCSPWR09 — Block-Diagonal-Bordered Form for Parallel Gauss-Seidel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92  |

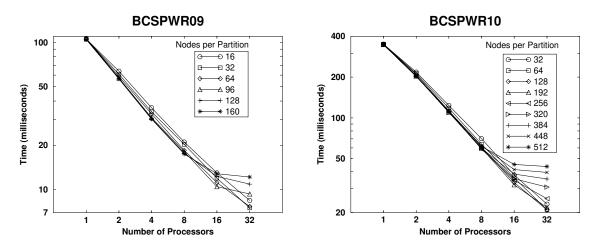

| 7.12        | Block-Diagonal-Bordered Form for Parallel Gauss-Seidel — Load Balanced for 8 Pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|             | cessors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94  |

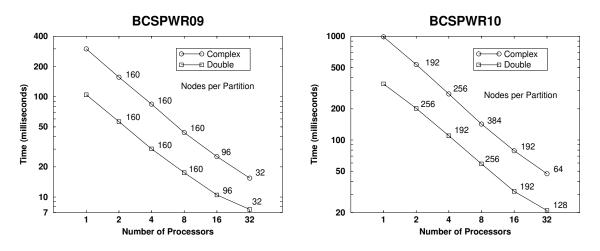

| 7.13        | Parallel Gauss-Seidel Timing Data — Double Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 96  |

| 7.14        | Best Empirical Performance for Parallel Gauss-Seidel Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98  |

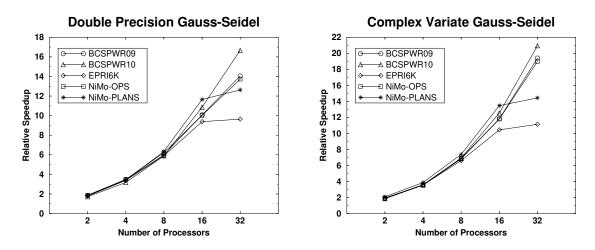

| 7.15        | Relative Speedup — Parallel Gauss-Seidel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99  |

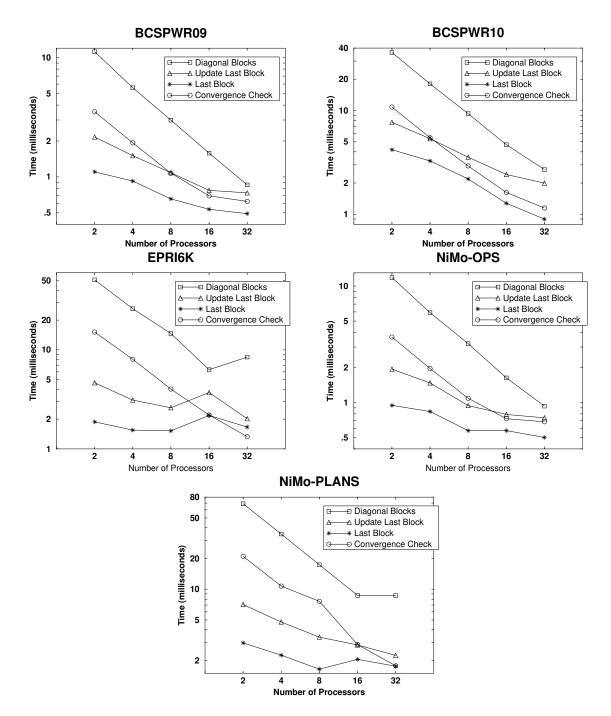

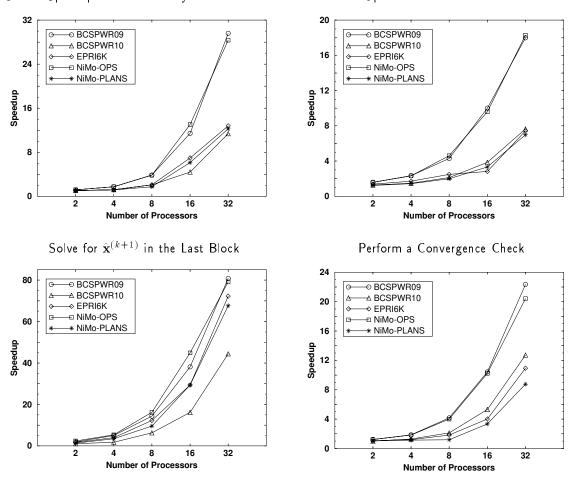

| 7.16        | Algorithm Component Timing Data — Double Precision Gauss-Seidel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 101 |

| 7.17        | Relative Speedup — Double Precision Parallel Gauss-Seidel $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104 |

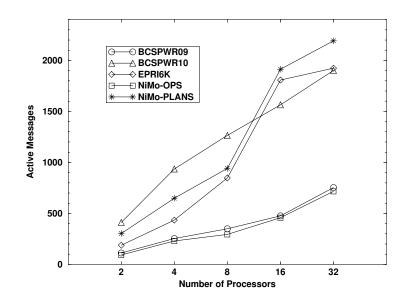

| 7.18        | Number of Low-Latency Messages Required to Distribute $\hat{\mathbf{x}}^{(k+1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105 |

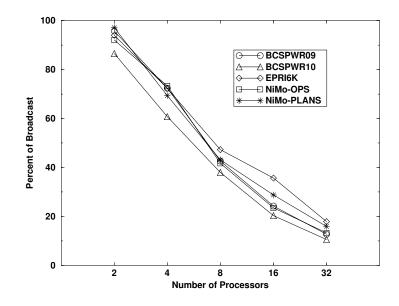

| 7.19        | Percentage of Broadcast Values Required to Distribute $\hat{\mathbf{x}}^{(k+1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 106 |

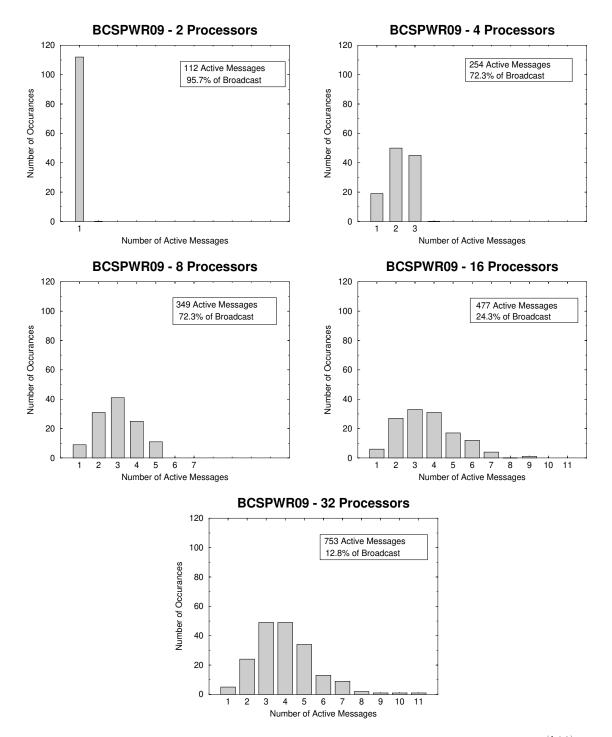

| 7.20        | BCSPWR09 — Histograms of the Number of Messages to Distribute $\hat{\mathbf{x}}^{(k+1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107 |

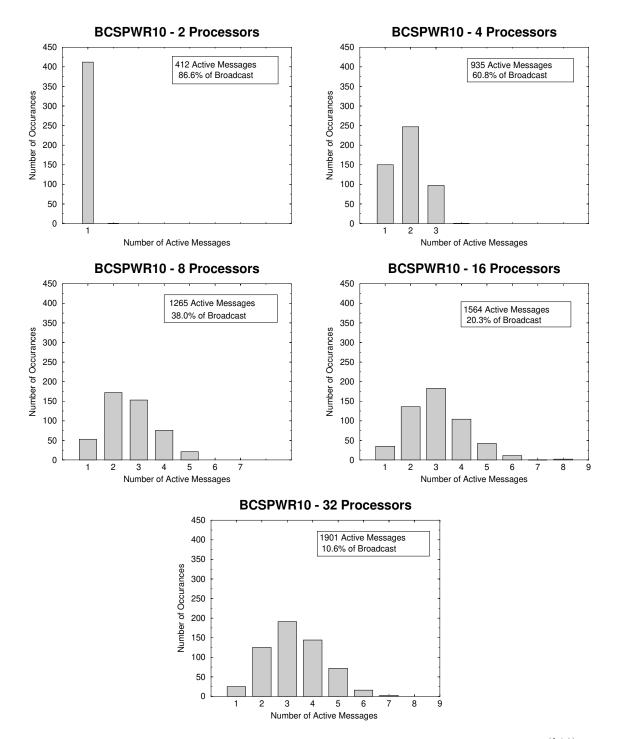

| 7.21        | BCSPWR10 — Histograms of the Number of Messages to Distribute $\hat{\mathbf{x}}^{(k+1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

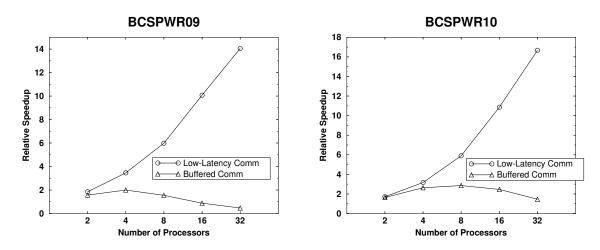

| 7.22        | Low-Latency Communications Speedup — Parallel Gauss-Seidel $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 109 |

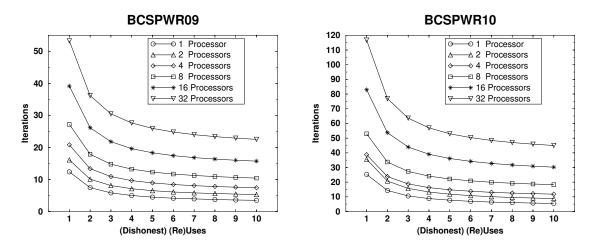

| 7.23        | Gauss-Seidel Iterations as a Function of Dishonest Reuses of the Choleski $\mathbf{L}\mathbf{L}^T$ Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112 |

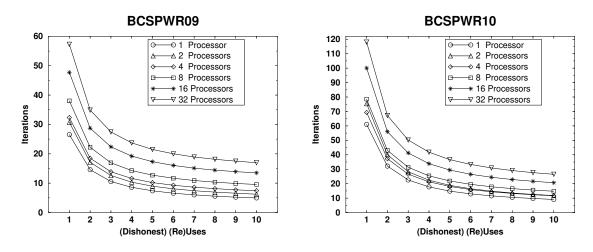

| 7.24        | Gauss-Seidel Iterations as a Function of Dishonest Reuses of the Double Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|             | LU Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 113 |

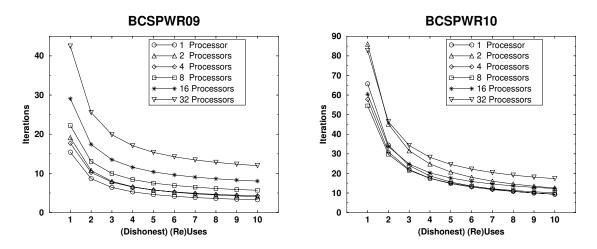

| 7.25        | Gauss-Seidel Iterations as a Function of Dishonest Reuses of the Complex ${\bf LU}$ Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114 |

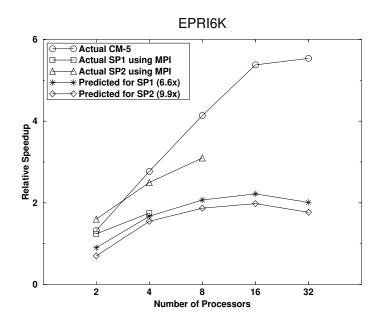

| 8.1         | Performance Validation for Parallel Complex LU Factorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 120 |

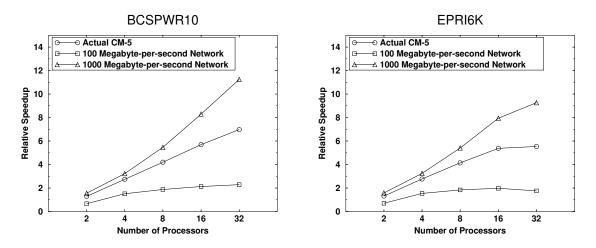

| 8.2         | Performance Predictions for Parallel Complex LU Factorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 121 |

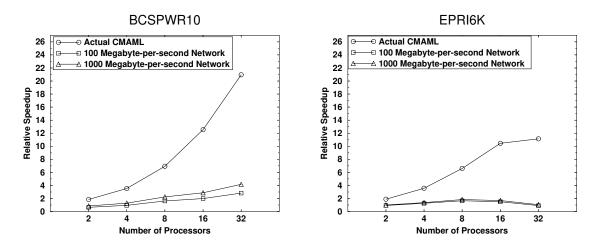

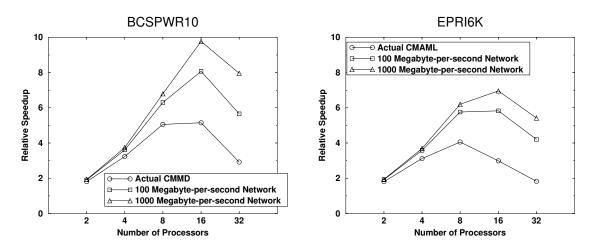

| 8.3         | $Performance\ Predictions\ for\ Parallel\ Complex\ Gauss-Seidel\\ Low-Latency\ Community\ Commu$ |     |