University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2015

# Parallel Fabrication and Transport Properties of Carbon Nanotube Single Electron Transistors

Muhammad Islam University of Central Florida

Part of the Physics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS** Citation

Islam, Muhammad, "Parallel Fabrication and Transport Properties of Carbon Nanotube Single Electron Transistors" (2015). *Electronic Theses and Dissertations, 2004-2019.* 1486. https://stars.library.ucf.edu/etd/1486

## PARALLEL FABRICATION AND TRANSPORT PROPERTIES OF CARBON NANOTUBE SINGLE ELECTRON TRANSISTORS

by

MUHAMMAD RAKIBUL ISLAM M.S. University of Central Florida, 2011

A dissertation submitted in partial fulfillment of requirements for the degree of Doctor of Philosophy in the Department of Physics in the College of Sciences at the University of Central Florida Orlando, Florida

Spring Term 2015

Major Professor: Saiful I. Khondaker

© 2015 Muhammad Rakibul Islam

### ABSTRACT

Single electron transistors (SET) have attracted significant attention as a potential building block for post CMOS nanoelectronic devices. However, lack of reproducible and parallel fabrication approach and room temperature operation are the two major bottlenecks for practical realization of SET based devices. In this thesis, I demonstrate large scale single electron transistors fabrication techniques using solution processed single wall carbon nanotubes (SWNTs) and studied their electron transport properties. The approach is based on the assembly of individual SWNTs via dielectrophoresis (DEP) at the selected position of the circuit and formation of tunnel barriers on SWNT. Two different techniques: i) metal-SWNT Schottky contact, and ii) mechanical templating of SWNTs were used for tunnel barrier creation.

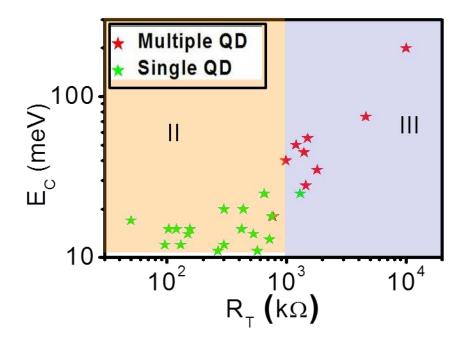

Low temperature (4.2K) transport measurement of 100 nm long metal-SWNT Schottky contact devices show that 93% of the devices with contact resistance  $(R_T) > 100 \text{ K}\Omega$  show SET behavior. Majority (90%) of the devices with 100 K $\Omega < R_T < 1 \text{ M}\Omega$ , show periodic, well-defined Coulomb diamonds with a charging energy ~ 15 meV, represents single electron tunnelling through a single quantum dot (QD), defined by the top contact. For high  $R_T$  (> 1M $\Omega$ ), devices show multiple QDs behaviors, while QD was not formed for low  $R_T$  (< 100 K $\Omega$ ) devices. From the transport study of 50 SWNT devices, a total of 38 devices show SET behavior giving an yield of 76%.

I also demonstrate room temperature operating SET by using mechanical template technique. In mechanical template method individual SWNT is placed on top of a  $Al/Al_2O_3$  local gate which bends the SWNT at the edge and tunnel barriers are created. SET devices fabricated

with a template width of  $\sim 20$  nm shows room temperature operation with a charging energy of  $\sim 150$  meV. I also discussed the detailed transport spectroscopy of the devices.

To my wife and parents

### ACKNOWLEDGMENTS

I would like to express my sincere gratitude my supervisor, mentor, and guide, Dr. Saiful Khondaker, for encouraging me to pursue a topic of my choice and helping me in every possible way. His constructive comments, wisdom and commitment to the highest standards inspired and motivated me. Without his active help and support this thesis could not have been written. Dr. Lee Chow, Dr. Sergei Stolbov, and Dr. Lei Zhai thank you for the encouragement, time and attention.

I would like to thank my fellow coworkers. In particular, I would like to acknowledge Dr. Paul Stokes who taught me the low temperature measurement for SET. I would also like to thank Dr. Daeha Joung for teaching me the device fabrication as soon as I join this group, as well as working together on many research projects. Thanks to Dr. Biddut Sarker, Dr. Feras Alzubi, Narae Kang, Udai Bhanu, Kristy Kormondy, Eliot Silbar, Dr. Shashank Shekhar, Dr. Mohammad Arif, Dr. Surajit Ghosh, Dr. Tanusri Pal, for sharing their enthusiasm and comments on my work.

I have many friends who have encouraged and supported me during the five years of graduate school. I would like to thanks Alamgir Kabir, Abrar Quadery, Rizvi, and Satez for their warmth and generosity.

I would like to thank my parents for their persistent support and sacrifice for my education and research, I cannot thank you enough. Last but not the least; I would like thank Zareen, my wife, for enduring my irregular working hours as a graduate student. Her emotional support was of immense help. This thesis is dedicated to you.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                    | xi  |

|--------------------------------------------------------------------|-----|

| LIST OF TABLES                                                     | XX  |

| LIST OF ABBREVIATIONS                                              | xxi |

| CHAPTER 1: INTRODUCTION                                            | 1   |

| 1.1 Motivation                                                     | 1   |

| 1.2 Outline of the thesis                                          | 6   |

| 1.3 References                                                     | 8   |

| CHAPTER 2: BACKGROUND                                              |     |

| 2.1 Carbon nanotubes                                               | 13  |

| 2.1.1 Structure of carbon nanotubes                                | 14  |

| 2.1.2 Electronic properties of carbon nanotubes                    | 16  |

| 2.2 Single electron transistor                                     | 19  |

| 2.2.1 Electron transport through single electron transistor        |     |

| 2.2.2 Fabrication of different type of single electron transistors |     |

| 2.2.3 Carbon nanotube quantum dots                                 |     |

| 2.2.4 Fabrication of carbon nanotube quantum dots                  |     |

| 2.3 Assembly of SWNTs                                              |     |

| 2.3.1 Find 'em and wire 'em technique                              |     |

| 2.3.2 Chemical vapor deposition (CVD) growth of SWNTs              |     |

| 2.3.3 Post growth techniques                                       |     |

| 2.3.3.1 Dielectrophoresis                                          | 34  |

| 2.3.3.2 Theory of Dielectrophoresis                                | 35  |

| 2.3.3.3 Parameters controlling the assembly of individual SWNT     | 39  |

| 2.4 References                                                     | 43  |

| CHAPTER 3: DEVICE FABRICATION AND EXPERIMENTAL METHODS             | 55  |

| 3.1 Introduction                                                   | 55  |

| 3.2 Electrode fabrication                                                                                  |            |

|------------------------------------------------------------------------------------------------------------|------------|

| 3.2.1 Optical lithography                                                                                  | 57         |

| 3.2.1.1 Double layer photo resist                                                                          | 57         |

| 3.2.1.2 Metallization                                                                                      | 59         |

| 3.2.1.3 Lift-off                                                                                           | 59         |

| 3.2.2 Electron beam lithography                                                                            | 60         |

| 3.2.3 Aluminum local gate fabrication                                                                      |            |

| 3.3 Dielectrophoresis of SWNTs for device fabrication                                                      | 63         |

| 3.3.1 SWNT solution for DEP                                                                                |            |

| 3.3.2 Experimental setup for DEP:                                                                          | 64         |

| 3.4 Setup for electrical measurement                                                                       |            |

| 3.5 References                                                                                             | 69         |

| CHAPTER 4: HIGH YIELD ASSEMBLY OF CARBON NANOTUBE FABRICAION                                               |            |

| 4.1 Introduction                                                                                           | 71         |

| 4.2 Optimization of DEP parameters for high yield assembly of SWNTs                                        |            |

| 4.2.1 Optimization of DEP parameters: solution concentration                                               | 74         |

| 4.2.2 Optimization of DEP Parameter: DEP time                                                              | 75         |

| 4.2.3 Assembly of individual SWNT via DEP                                                                  | 77         |

| 4.3 Room temperature transport properties of SWNT devices                                                  |            |

| 4.3.1 Transport properties of metallic SWNT devices                                                        |            |

| 4.3.2 Transport properties of semiconducting SWNT devices                                                  |            |

| 4.4 General approach for the assembly of all semiconducting carbon nanotube                                | devices 82 |

| 4.4.1 Electron transport measurements of 1-5 s-SWNT devices                                                |            |

| 4.4.2 Electron transport measurements of 1-10 SWNT devices                                                 | 86         |

| 4.5 Conclusion                                                                                             | 87         |

| 4.6 References                                                                                             | 89         |

| CHAPTER 5: TOWARDS PARALLEL FABRICATION OF SINGLE<br>TRANSISTOR USING TOP METAL CONTACT OF CARBON NANOTUBE |            |

| 5.1 Introduction                                                                                           |            |

| 5.2 Device design and sample preparation                                                                 |     |

|----------------------------------------------------------------------------------------------------------|-----|

| 5.2.1 Dielectrophoretic assembly of individual SWNT                                                      |     |

| 5.2.2 Deposition of metal contact on individual SWNT                                                     | 101 |

| 5.3 Room temperature electron transport properties                                                       | 102 |

| 5.4 Low temperature electron transport measurement of top contact device                                 | 105 |

| 5.4.1 Electron transport measurement of Device A                                                         | 105 |

| 5.4.2 Electron transport measurement of Device B                                                         | 106 |

| 5.4.3 Electron transport measurement of Device C                                                         | 111 |

| 5.5 Discussion and Summary                                                                               | 113 |

| 5.6 Conclusion                                                                                           | 116 |

| 5.7 References                                                                                           | 117 |

| CHAPTER 6: PARALLEL FABRICATION OF SINGLE ELECTRON TRANSISTC<br>MECHANICAL TEMPLATING OF CARBON NANOTUBE |     |

| 6.1 Introduction                                                                                         | 123 |

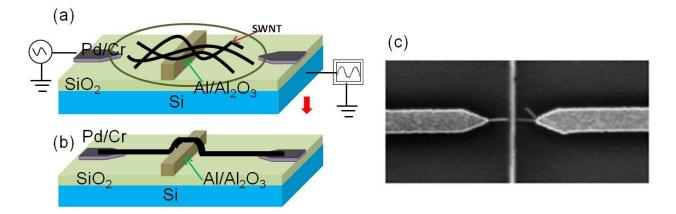

| 6.2 Design and fabrication of mechanical template deices                                                 | 126 |

| 6.3 Room temperature transport of mechanical template devices                                            | 128 |

| 6.4 Effect of electronic structure on the low temperature transport spectroscopy:                        | 130 |

| 6.4.1 Low temperature transport of mechanical template metallic SWNT                                     | 131 |

| 6.4.2 Low temperature transport of mechanical template semiconducting SWNT                               | 135 |

| 6.5 Discussion                                                                                           | 137 |

| 6.6 Conclusion                                                                                           | 138 |

| 6.7 References                                                                                           | 139 |

| CHAPTER 7: ROOM TEMPERATURE OPERATING CARBON NANOTUBE ELECTRON TRANSISTOR                                |     |

| 7.1 Introduction                                                                                         | 142 |

| 7.2 Device design and fabrication                                                                        | 143 |

| 7.3 Electron transport measurements of RT SET                                                            | 145 |

| 7.4 Conclusion                                                                                           | 151 |

| 7.5 References                                                                                           | 153 |

| CHAPTER 8: CONCLUSION                                                                                    | 155 |

| 8.1 Summary                                                  | 155 |

|--------------------------------------------------------------|-----|

| 8.2 Future Directions                                        |     |

| 8.2.1 SET fabrication via DEP assembly of ultra-short SWNT   | 156 |

| 8.2.2 SET fabrication using atomically thin MoS <sub>2</sub> | 157 |

| 8.3 References                                               |     |

### **LIST OF FIGURES**

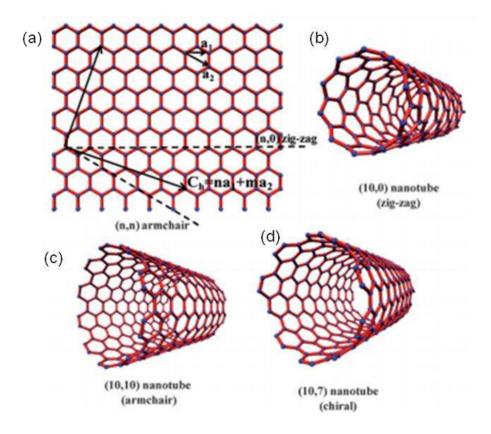

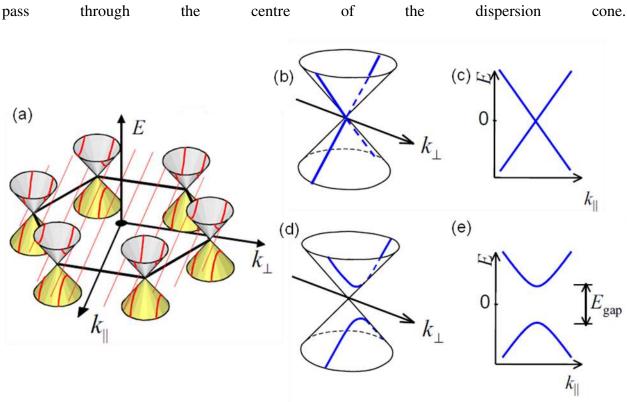

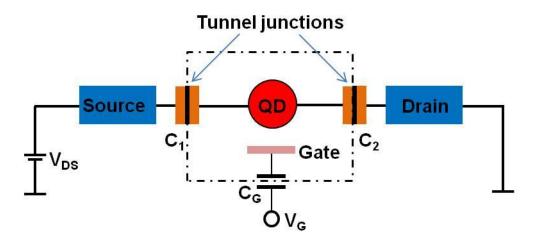

Figure 2.1 A few examples of the stable forms of carbon with the different dimensionalities and various forms. They range from (a) 0D fullerene to (b) 1D nanotube to (c) 2D graphene to 3D (d) Figure 2.2 (a) A graphene sheet that can be folded into a seamless cylinder by cutting out the sheet along the dashed lines and rolling it up along vector  $C_h$ .  $a_1$  and  $a_2$  are the unit vectors of the hexagonal graphene sheet (b) Example of a "zig-zag" nanotube. (c) Example of a "armchair" nanotube. (d) Example of a "armchair" nanotube. Adpated from ref [9]. ..... 15 Figure 2.3 (a) Band structure of graphene. It shows that the one dimensional subbands of nanotubes can be determined by applying boundary conditions. Low energy band structure of carbon nanotube: (b) For p = 0, there is an allowed value of  $\vec{k}_{\perp}$  whose subband passes through the middle of the dispersion cone which results in a metallic nanotube. (c) Energy dispersion for a metallic nanotube. (d) For p = 0, there is an allowed value of  $\vec{k}_{\perp}$  whose subband misses the middle of the dispersion cone which results in a metallic nanotube. (e) Energy dispersion for a semiconducting nanotube. Figure adopted from ref [10]......17 Figure 2.4 Schematic of a single electron transistor with the electrical connection. A conducting island often called quantum dot (QD) coupled to the source and drain leads via tunnel barriers

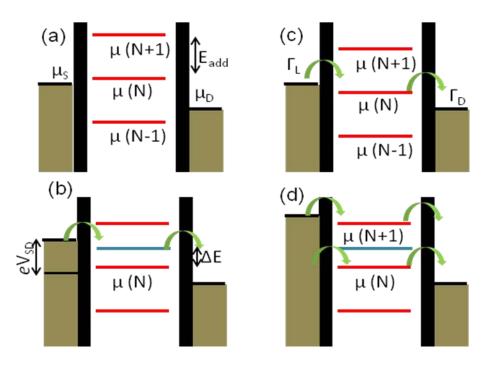

Figure 2.5 Cartoon for the electrochemical potential of the SET at different voltage configuration. (a) The electrochemical potential of QD does not falls inside the bias window which cuses current blockade. (b) The electrochemical potential of the QD is drag inside bias window by sweeping gate voltage and electron tunneling occurs. (c) Application of bias voltage rises the electrochemical potential of the drain and electron tunneling occur once the electrochemical potential of the QD fall inside dias window. (d) Excited energy levels are Figure 2.6 Typical low temperature electron transport behavior of SET (a) at gate voltage,  $V_{G1}$ , current is suppressed and is called Coulomb blockade (CB). Electron tunneling occur when a gate voltage to  $V_{G2}$  is applied. (b) Tuning the gate voltage gives current oscillation known as Coulomb Oscillation (CO) (c) Stability plot, where conductance vs source-drain voltage vs gate Figure 2.7 Popular SET fabrication techniques: (a) surface pattering of 2DEG heterostructure [31] (b) self assembly of CdSe colloidal nanocrystal [32] (c) Etching Si substrate [34] (d) patterning of InAs nanowire with InP barriers.[42] (e) Nanotube SET defined by metal Figure 2.8 Schematic diagram of a carbon nanotube quantum dot which can be formed by depositing metal electrodes, source (S) and drain (D), on top of the tube separated by a distance L. The nanotube is capacitively coupled to the gate, (usually the back gate plane of the silicon Figure 2.9 Carbon nanotube single electron transistors fabrication techniques. (a) Bending carbon nanotube by AFM tip [48] (b) Modification of nanotube by oxygen (O<sub>2</sub>) plasma [49] (c)

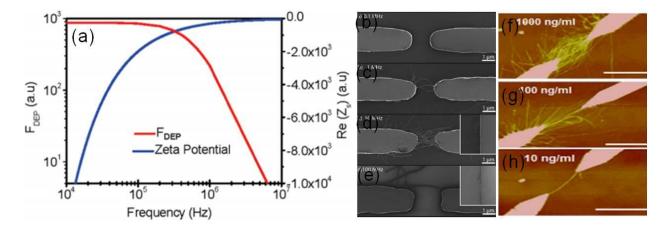

Bombardment of nanotube by Ar ion beam [57] (d) Fabrication of tunnel barrier by focused ion bean (FIB) defects by Ar ion [75] (e) Creation of defects by O<sub>2</sub> plasma [56] (f) Introducing Figure 2.10 (a) Field effect transistor fabricated where SWNT was randomly placed between metal electrodes by the 'find' em and 'wire' technique[80]. (b) Complex SWNT structure Figure 2.11 a) CVD growth of individual SWNT from Patterned catalytic[81] (b) Zoom in image Figure 2.12 Schematic for the nanotube assembly via DEP. In a non-uniform electric field opposite charges are induced at the opposite end of the SWNT and a dipole moment is created Figure 2.13 Effect of the presence of catalysit particle on DEP assembly of individual SWNT (a) from DMF solution, (b) from DCE solution, and (c) the Brewer Science solution. Scale bar: 1µm[91]. Reprinted (d) Statistics of electrode connection yield after dielectrophoresis of CNTs dispersed in cyclohexanone, water, and IPA Representative SEM micrographs are presented for Figure 2.14 (a) Plot of DEP force (left axis) and zeta- potential (right axis) as a function of frequency [103]. Frequency dependent DEP deposition yield studies at constant potentials. (b) 100 kHz (c) 1 MHz. (d) 10 MHz, and (e) 100 MHz [104]. Dependence of solution concentration on the assembly of SWNT (f) 1000 ng/ml (g) 100 ng/ml, and (h)10 ng/ml in the solution. Scale

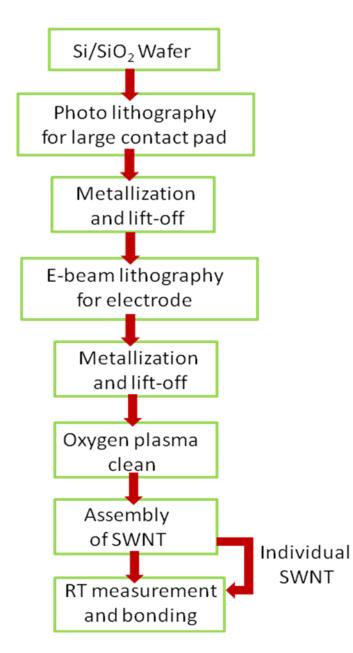

| Figure 3.1 Flow-chart of the experimental procedures. Photolithography is used to define larger             |

|-------------------------------------------------------------------------------------------------------------|

| contact pads, followed by evaporation of Cr and Au, and standard lift-off. Electron beam                    |

| lithography (EBL) is used to define smaller feature electrode followed by evaporation of Cr and             |

| Pd, and standard lift-off. Then the devices are, exposed to O <sub>2</sub> plasma etching for 15 minutes to |

| remove residual resists. Individual SWNTs are then integrated between this metal electrodes via             |

| dielecrophoresis (DEP). Yield for SWNT assembly is checked via scanning electron microscope.                |

| Subsequently, the electron tranpoort meaurements of the devices are carried out at room and low             |

| temperature                                                                                                 |

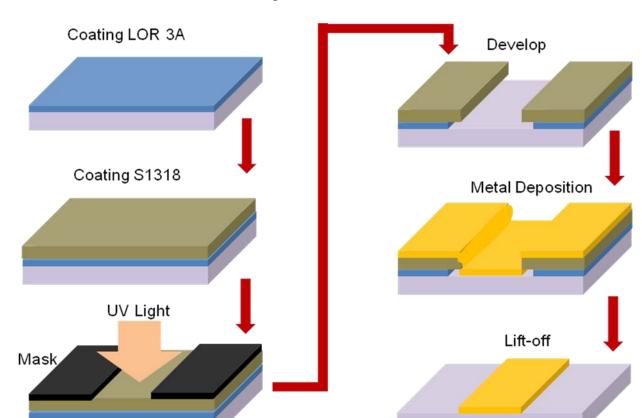

| Figure 3.2 Schematic diagram of the photolithography process using double layer photoresist. 58             |

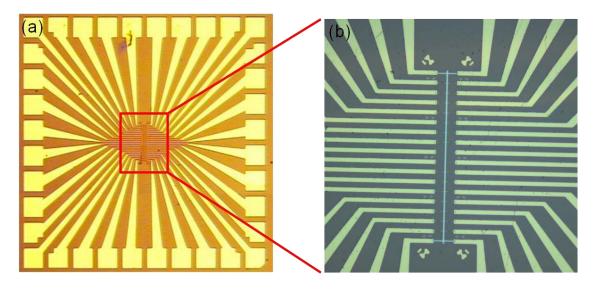

| Figure 3.3 (a) Optical photograph of large contact pad defined by photolithography. (b) Zoom in             |

| image of the selected part of figure 3.3 (a)                                                                |

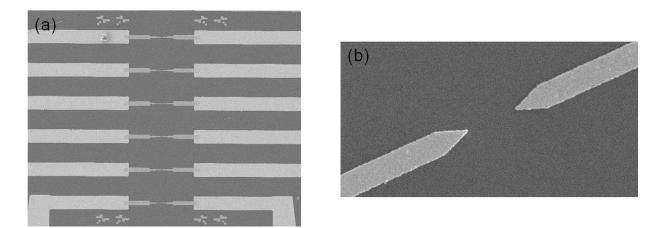

| Figure 3.4 Scanning electron micrograph (SEM) of (a) metal electrode arrays defined by EBL (b)              |

| single electrode pair with a separeted by 1 µm61                                                            |

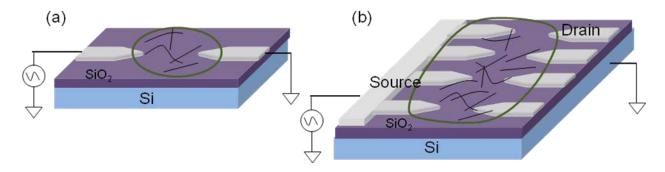

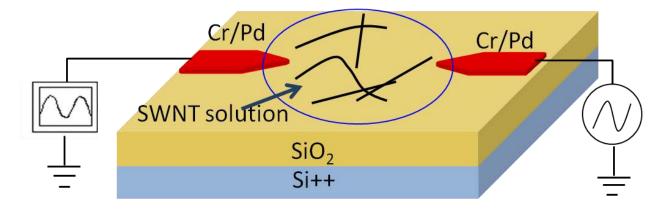

| Figure 3.5 (a)Schematic of the DEP assembly set-up for the assembly of carbon nanotube. (a)                 |

| Point-to-point deposition and (b) simultaneous deposition                                                   |

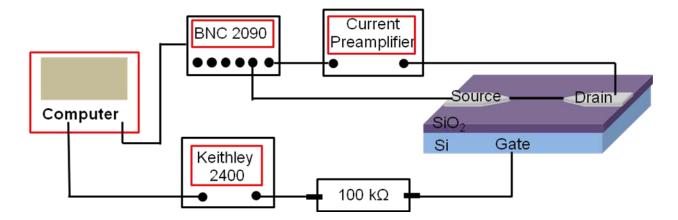

| Figure 3.6 Schematic for the room temperature electron transport measurement set-up of SWNT                 |

| devices                                                                                                     |

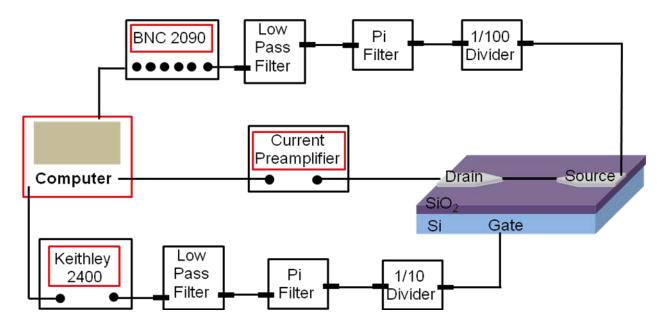

| Figure 3.7 Low temperature measurements setup for SWNT SET at low temperature                               |

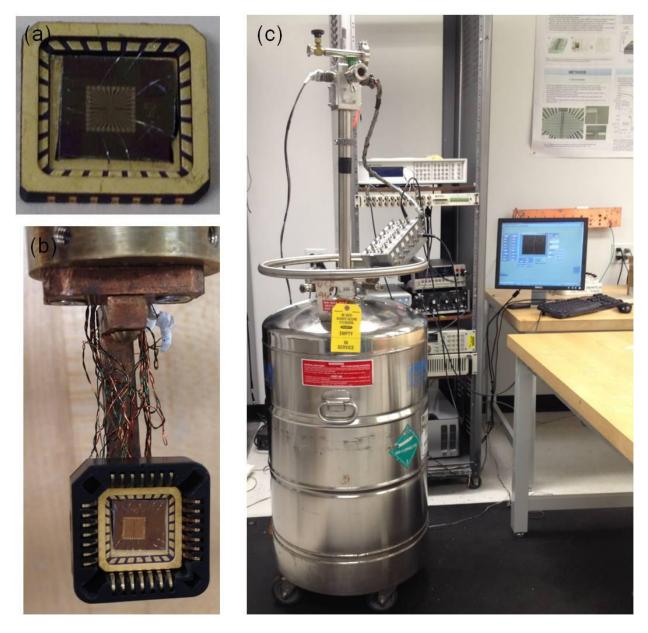

| Figure 3.8 Low temperature measurements set up (a) Chip containing SET devices bonded to a                  |

| chip carrier via aluminium wire (b) bonded chip loaded into a variable temperature <sup>4</sup> He cryostat |

| (c) The cryostat is loaded into a 30 liter He dewar                                                         |

| Figure 4.1 Schematic diagram of the DEP assembly set up73                                                   |

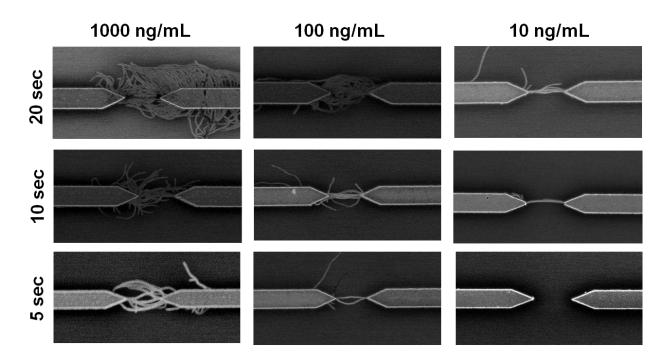

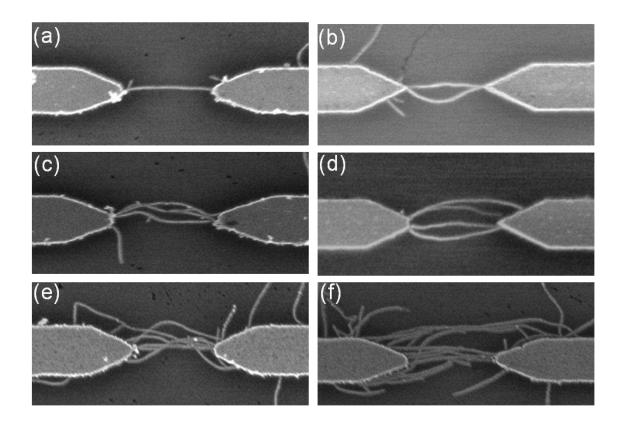

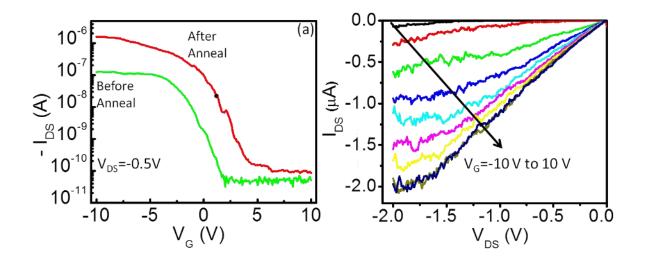

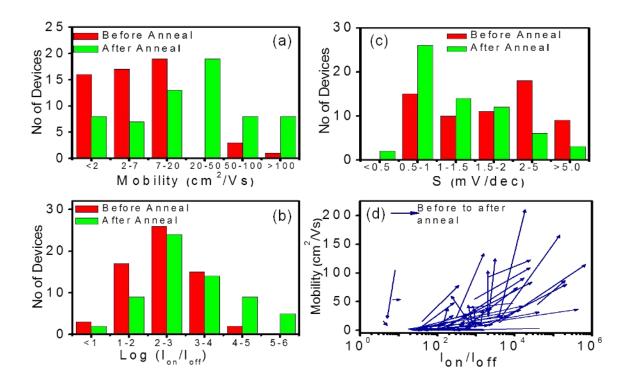

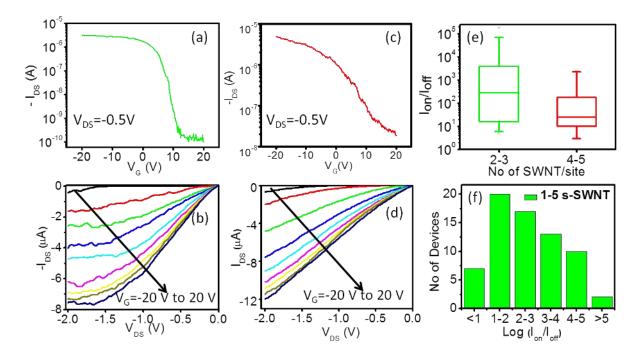

Figure 4.2 Scanning electron micrographs (SEM) image of a number of individual SWNT deposited by dielectrophoresis (DEP) at three different concentration 1000 ng/mL, 100 ng/mL and 10 ng /mL and a DEP time ~ 20sec, 10 sec and 5 sec. Distance between adjacent electrodes is 1 µm for all images.....74 Figure 4.3 Results of DEP assembly for 10 sec DEP time and a solution concentration of 10 ng/mL. SEM images for the DEP assembled devices containing (a) one (b) two (c) three (d) four (e) six and (f) eight s-SWNTs between the electrodes..Separation between the electrodes in each Figure 4.4 Scanning electron micrographs (SEM) image of a number of individual SWNT Figure 4.6 (a) Transfer characteristics of a representative individual SWNT FET device before Figure 4.7 Summary of FET properties for all individual s-SWNT devices before and after anneal. Histogram of mobility(a), Ion/Ioff (b), subthreshol swing S (c), and Vector diagram of Figure 4.8 (a) Transfer characteristics of a FET device with 2 s-SWNT. (b) output characteristics of the same device for different gate voltages ranging from +20 V to -20 V. (c) Transfer and (d) and output characteristics of a device with 4 s-SWNT. (e) Box plot of  $I_{on}/I_{off}$  for 2-3 and 4-5 s-SWNT showing the range and median value. (f) Histogram of the  $I_{on}/I_{off}$  for all devices with 1-5

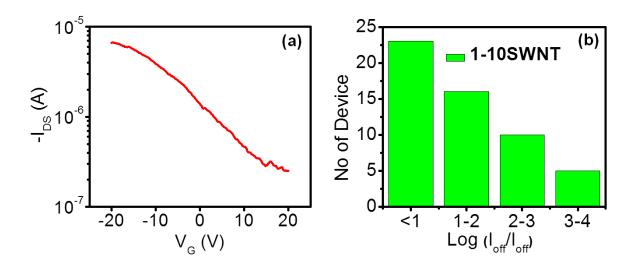

| Figure 4.9 (a)Transfer characteristics of a representative FET device with 6 s-SWNT. (b)                                       |

|--------------------------------------------------------------------------------------------------------------------------------|

| Histogram of the Ion/Ioff for device with 1-10 s-SWNT devices                                                                  |

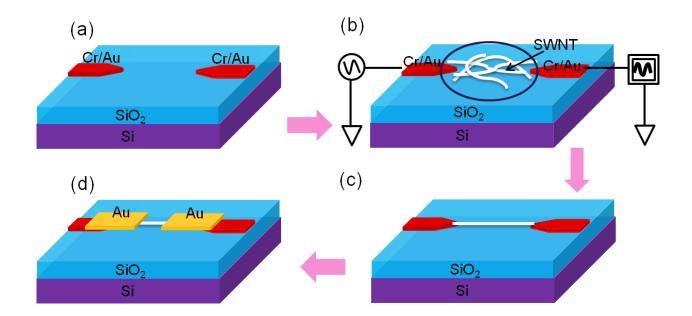

| Figure 5.1 Three-dimensional illustration of the device fabrication steps: (a) Source and drain                                |

| electrode pattern (b) DEP assembly set up. (c) Individual SWNT assembled between electrodes.                                   |

| (d) Fabrication of top electrode contact on individual SWNT                                                                    |

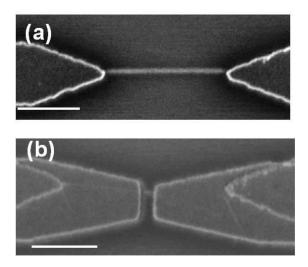

| Figure 5.2 (a) SEM image of (a) aligned SWNT between electrode with a separation of 1 $\mu$ m and                              |

| (b) top contact device with 100 nm separation. Scale bar: 500 nm 102                                                           |

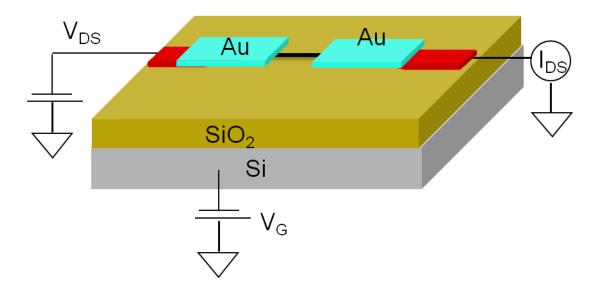

| Figure 5.3 Schematic diagram of top contact SWNT device geometry and measurement setup                                         |

| showing a SWNT between Pd top contacts                                                                                         |

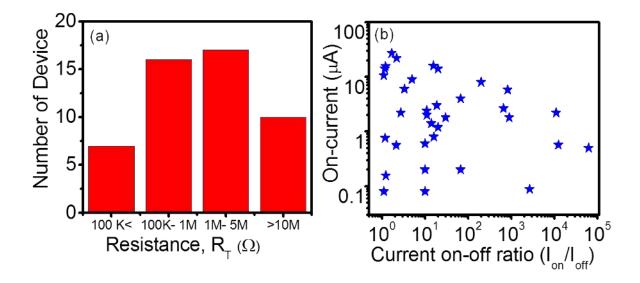

| Figure 5.4 (a)Histogram of the contact resistance for top contact SWNT devices after annealing.                                |

| (b) Current on-off ratio and on-current of the top contact devices at room temperature 104                                     |

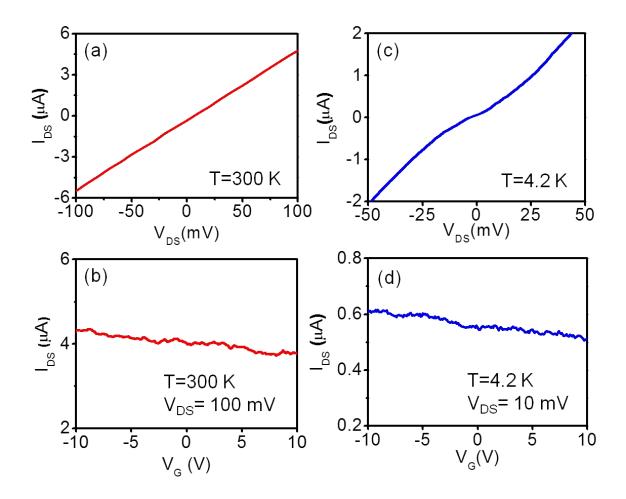

| Figure 5.5 Electron transport characteristics of devices A. $I_{DS}$ - $V_{DS}$ curve (a), and $I_{DS}$ - $V_G$ (at $V_{DS}$ = |

| 100 mV) curve of the device at room temperature; (c) $I-V_{DS}$ curve of the device at 4.2 K does not                          |

| show coulomb oscillation. (b) $I$ - $V_G$ curve of the device and Coulomb oscillation is not observed.                         |

|                                                                                                                                |

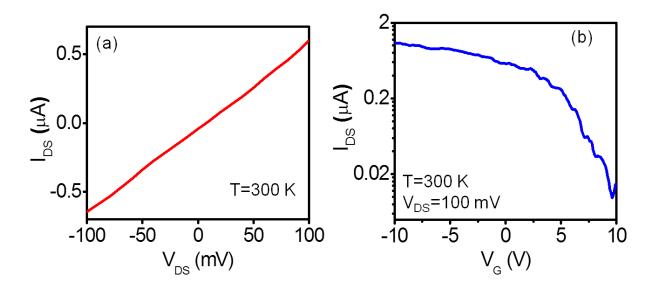

| Figure 5.6 Room temperature electron transport characteristics of devices B: $I_{DS}$ - $V_{DS}$ curve (a),                    |

| and $I_{DS}-V_G$ (at $V_{DS} = 100 \text{ mV}$ )                                                                               |

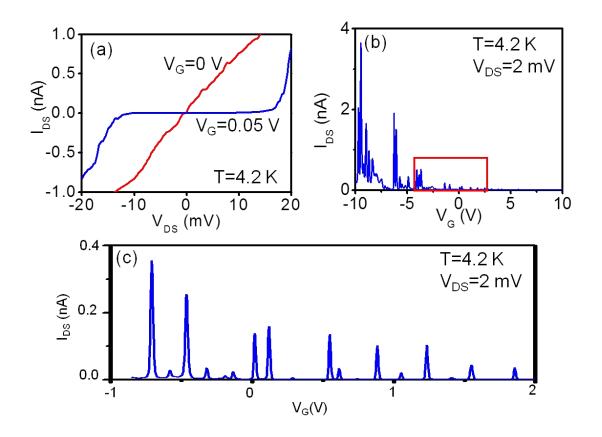

| Figure 5.7 Electron transport properties of device B at at T=4.2 K. (a) $I_{DS}$ - $V_{DS}$ at two different                   |

| gate voltages at T=4.2 K, showing coulomb blockade and single electron tunelling (b) $I_{DS}-V_G$                              |

| curve of the device at 4.2 K at $V_{DS} = 2 \text{ mV}$ showing coulomb oscillation. (c) Expanded view of                      |

| the $I-V_G$ curve showing periodic oscillations                                                                                |

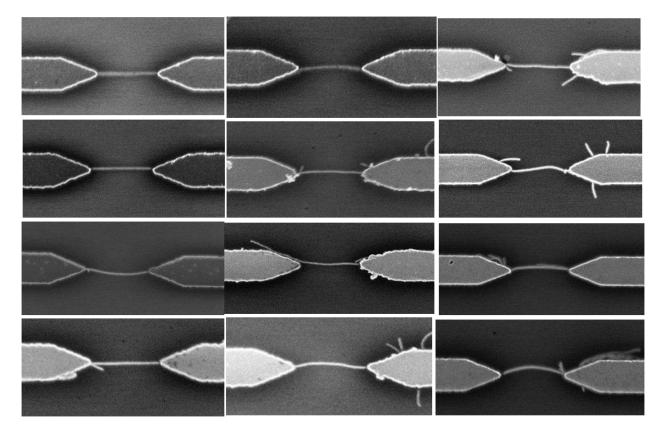

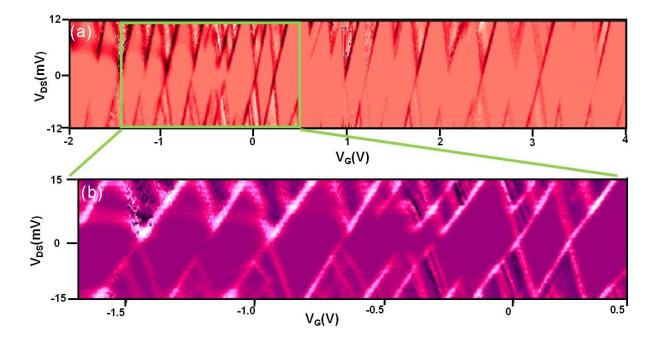

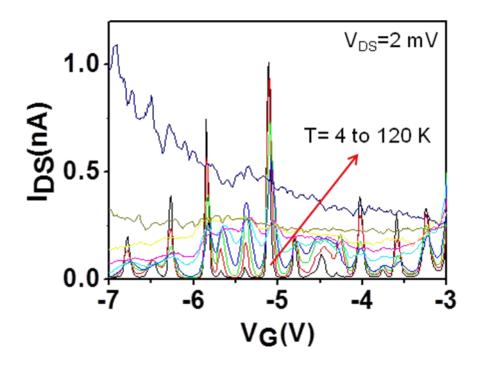

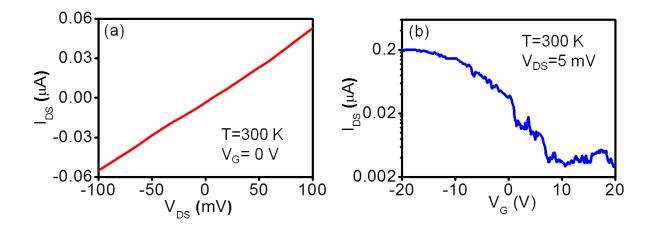

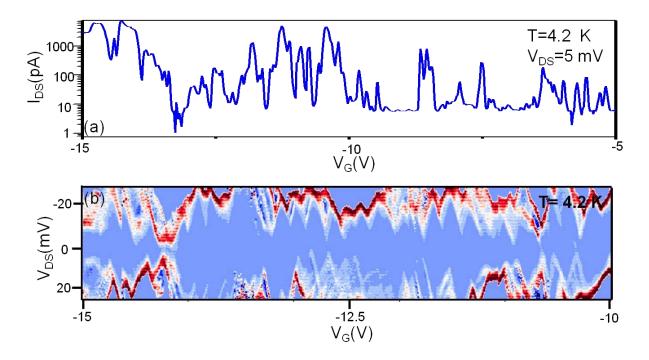

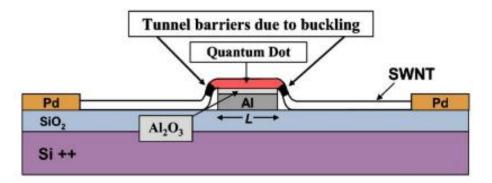

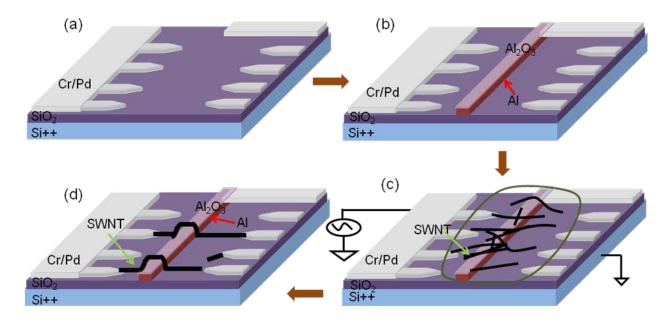

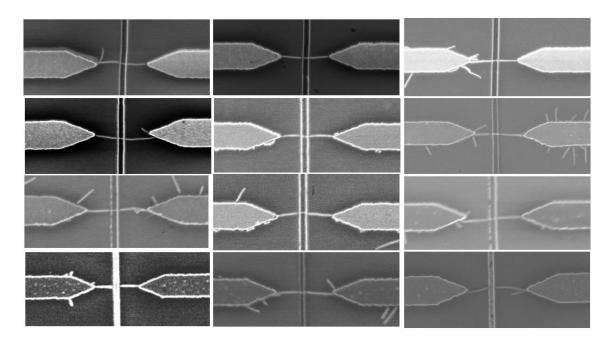

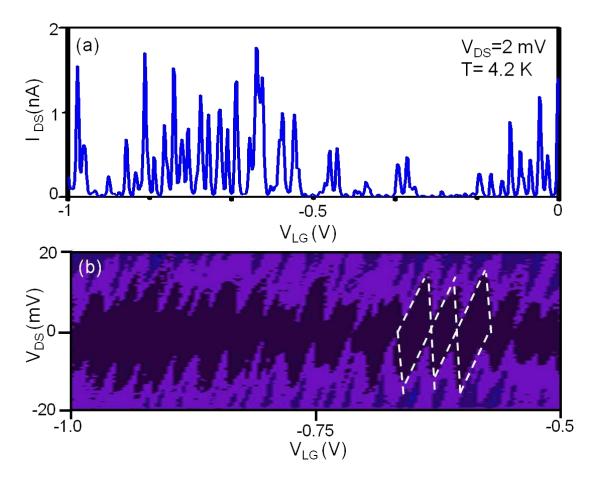

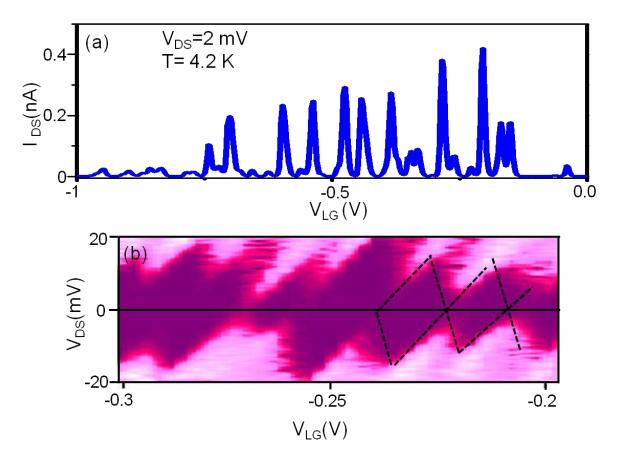

Figure 5.8 (a) Color scale plot of differential conductance  $(dI/dV_{DS})$  as a function of  $V_G$  and  $V_{DS}$ at T= 4.2 K, showing regular diamond patterns. (b) Expanded view of the Coulomb diamond Figure 5.9 Plot of  $I_{DS}$ - $V_G$  for  $V_{DS}$  = 2 mV at various temperatures from 4.2 up to 120 K. ..... 111 Figure 5.10 Room temperature electron transport characteristics of devices C: I<sub>DS</sub>-V<sub>DS</sub> curve (a), Figure 5.11 Electron transport characteristics of device C at T= 4.2 K. (a)  $I-V_G$  curve of the device at 4.2 K at  $V_{DS} = 5$  mV showing irregular coulomb oscillation. (b)  $dI/dV_{DS}$  plotted as a function of  $V_G$  and  $V_{DS}$  showing irregular diamond patterns characteristics of multiple QDs... 113 Figure 5.12 Summary of the devices at three different resistance ranges. Inset of the figure shows Figure 6.1 Schematic diagram of mechanical template based SWNT SET device [15]. Tunnel barriers are created at the edge of the local gate and a the size of the quantum dot is equal to the Figure 6.2 Fabrication of SWNT SET using mechanical template technique. (a) Source - drain electrodes with a separation of 1  $\mu$ m. (b) Mechanical template is defined by EBL and few nm  $Al_2O_3$  is formed by oxygen plasma treatment. (c) DEP assembly of SWNT by simultaneous deposition. (d) After DEP a number of devices assembled on the same chip. ..... 127 Figure 6.3 Scanning electron micrographs (SEM) image of mechanically templated individual SWNT devices deposited by dielectrophoresis (DEP). Distance between adjacent electrodes is 1

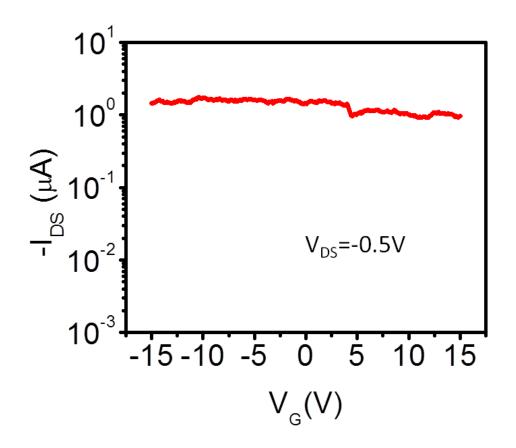

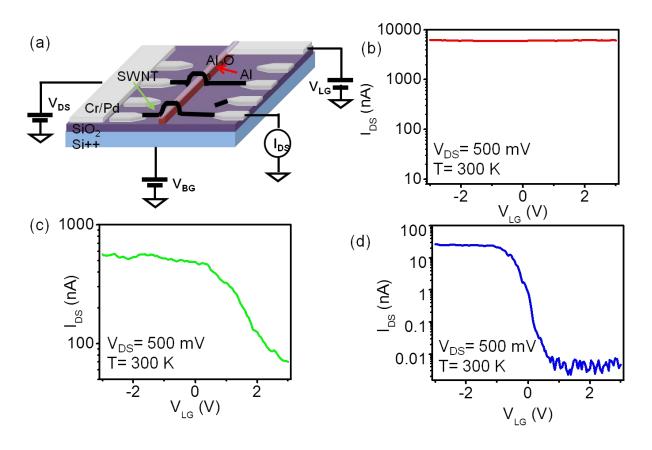

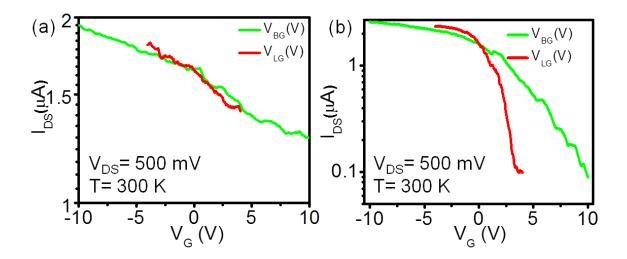

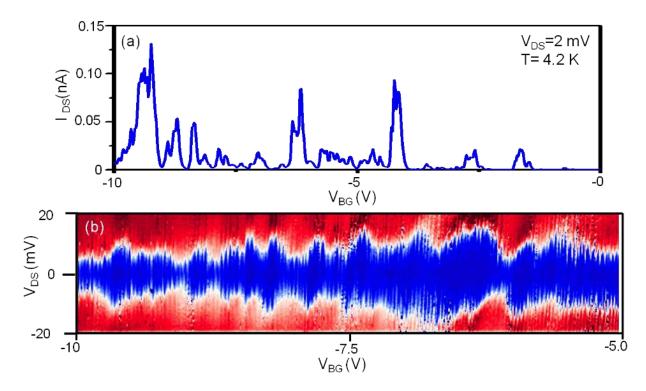

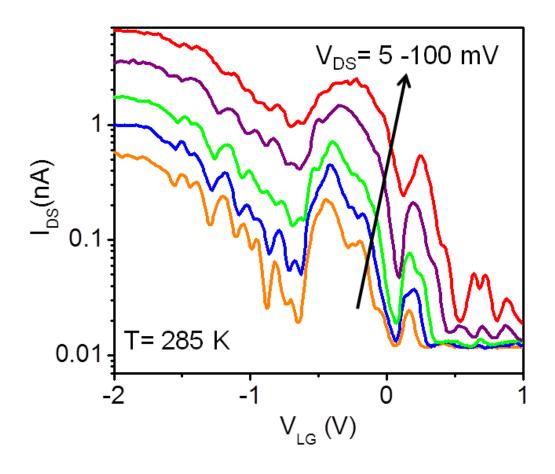

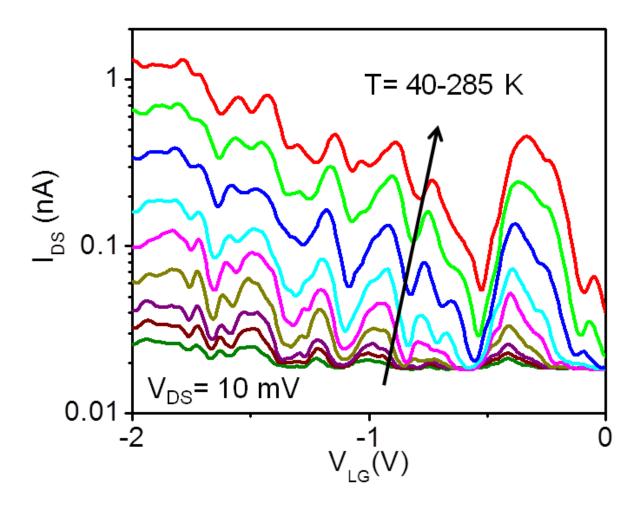

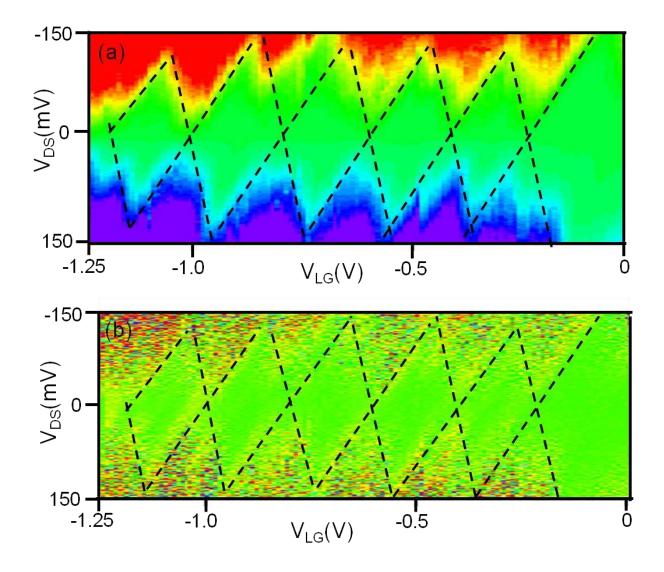

Figure 6.4 Schematic diagram of measurement setup for mechanical template local gated device. Current ( $I_{DS}$ ) versus local gate voltage ( $V_{LG}$ ) at  $V_{DS}$ = 0.5 V of representative (b) metallic, (c) Figure 6.5 Comparision in device performance between the local gated and back gated device. (a) metallic SWNT, and (b) semiconducting SWNT. VDS= 0.5 V for both curves. ..... 131 Figure 6.6 (a)  $I-V_{BG}$  curve of a metallic SWNT the device at 4.2 K at  $V_{DS} = 2$  mV showing current oscillation, typical of a SET behavior (b) color scale plot,  $dI/dV_{DS}$  vs  $V_{BG}$  vs  $V_{DS}$  plotted Figure 6.7 Low temperature electron transport properties of a representative mechanically templated metallic SWNT device (a)  $I_{DS}$ - $V_G$  curve of the device at 4.2 K at  $V_{DS}$  = 3 mV showing periodic coulomb oscillation. (b) Color scale plot of  $dI_{DS}/dV_{DS}$  vs  $V_G$  vs  $V_{DS}$  at  $V_{LG}$  between -1.0V Figure 6.8 Low temperature electron transport properties of a representative mechanically templated semiconducting SWNT device (a)  $I_{DS}$ - $V_G$  curve of the device at 4.2 K at  $V_{DS} = 2 \text{ mV}$ showing periodic coulomb oscillation. (b)Color scale plot  $dI_{DS}/dV_{DS}$  vs  $V_{LS}$  at T= 4.2 K. Figure 7.2 (a) Schematic for assembly of SWNT for the fabrication of RT SET by SWNT via dielectrophoresis (b) fabricated device agter assembly (c) Scannin electron micrograph of Figure 7.3 Drain current ( $I_{DS}$ ) plotted by sweeping local gate voltage ( $V_{LG}$ ) at room temperature

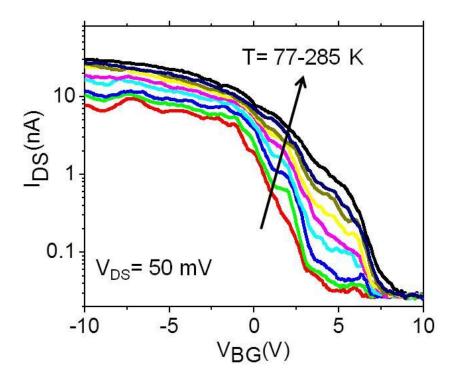

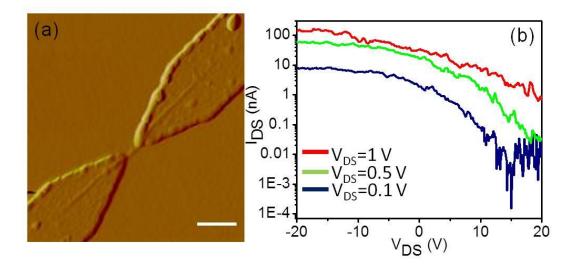

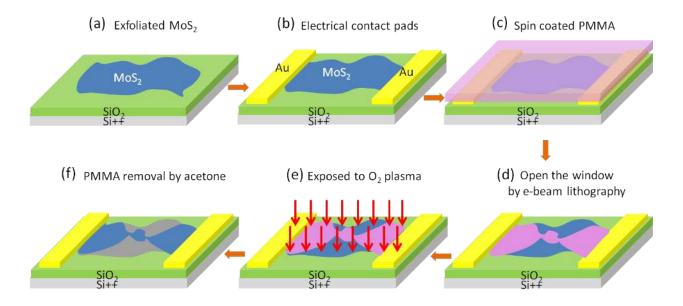

Figure 7.4 Drain current  $(I_{DS})$  plotted by sweeping local gate voltage  $(V_{LG})$  for different temperature (T) = 40, 50, 78, 125, 100, 150, 200, 250, 285 K). at fixed bias voltage ( $V_{DS}$ )= 10, mV......147 Figure 7.5 (a) Plot of  $I_{DS}$  as a function of  $V_{LG}$  and  $V_{DS}$  at T=78K showing Coulomb blockade (b) Figure 7.6 Drain current (I<sub>DS</sub>) Plotted as a function of back gate voltage (V<sub>BG</sub>) at different temperature (T) = 40, 50, 78, 125, 100, 150, 200, 250, 285 K). at fixed bias voltage ( $V_{DS}$ )= 10, Figure 8.1 (a) Atomic force microscope (AFM) image of individual SWNT assemble between a 100 nm channel length electrode separation vai dielectrophoresis. (b) Transfer characteristics of Figure 8.2 Schematics of the quantum dot fabrication on MoS<sub>2</sub>. (a) Exfoliation of MoS<sub>2</sub> on Si/SiO<sub>2</sub> substrate (b) Metallization of gold (Au) electrode on the selected flake (c) spin-coating PMMA resist, (d) opening a window of nanoscale dimension on the  $MoS_2$  flake via EBL (e) the sample is exposed to oxygen plasma (f) removing PMMA using acetone and nano-constriction is created at exposed portion of MoS<sub>2</sub>......158

# LIST OF TABLES

| Table    | 5.1   | The                 | SET    | behavior  | of    | 100   | nm    | top   | contact  | devices   | at   | different | room | temperature |

|----------|-------|---------------------|--------|-----------|-------|-------|-------|-------|----------|-----------|------|-----------|------|-------------|

| resistar | nce ( | (R <sub>T</sub> ) 1 | ranges | 5         | ••••• | ••••• | ••••• | ••••• |          |           |      |           |      | 115         |

| Table 6  | 5.1 S | Sumn                | nary o | f.the SET | yie   | ld fo | r me  | chan  | ical tem | plate dev | vice |           |      | 138         |

# LIST OF ABBREVIATIONS

| AFM    | Atomic Force Microscopy                  |

|--------|------------------------------------------|

| CB     | Coulomb Blockade                         |

| СО     | Coulomb Oscillation                      |

| CD     | Coulomb Diamond                          |

| CMOS   | Complementary Metals Oxide Semiconductor |

| CNT    | Carbon Nanotube                          |

| CVD    | Chemical Vapor Deposition                |

| DEP    | Dielectophoreis                          |

| DI     | Deionized                                |

| EBL    | Electron Beam Lithography                |

| FET    | Field Effect Transistor                  |

| IPA    | Isopropyl-alcohol Methyl-isobutyl-ketone |

| LOR    | Lift-off-Resist                          |

| MIBK   | Methyl-isobutyl-ketone                   |

| MOS    | Metals Oxide Semiconductor               |

| m-SWNT | Metallic single walled carbon nanotube   |

| MWNT   | Multiwalled cabon nanotube               |

| NPGS   | Nano-Patterned- Generation-System        |

| NPs    | Nanoparticles                            |

| QD     | Quantum Dot                              |

| SET    | Single electron transistor                   |

|--------|----------------------------------------------|

| SWNT   | Single walled carbon nanotube                |

| s-SWNT | Semiconducting single walled carbon nanotube |

| SB     | Schottky Barrier                             |

| SEM    | Scanning Electron Microscopy                 |

### **CHAPTER 1: INTRODUCTION**

#### 1.1 Motivation

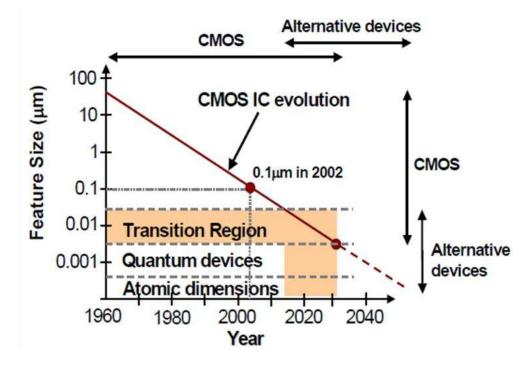

The origin of modern electronics traces back to the innovation of transistor by Bardeen, Brattain and Shockley in 1947. This leads to the discovery of integrated circuit (IC) in 1958-59, which provides a means of logic and computation. Shortly after that Metal oxide semiconductor (MOS) transistor and Complimentary MOS (CMOS) (1963) were demonstrated which lead to a revolution in the field of electronics. Since then progress has made for scaling down the size of the transistors to increase the density of logic and memory in the chip. The number of transistor per chip is doubling roughly in every 18 month as devised by Moore's law [1] leading to the device fabrication upto submicron level (figure 1.1). The miniaturization of transistor size together with the ease of fabrication made Si-based CMOS technology as workhorse for modern electronics. However, scaling down of transistor below sub 100 nm generates several fundamental challenges including short channel effects, gate oxide leakage, increased off state current, high field mobility degradation, and high power dissipation etc [2-4]. By introducing new gate oxide materials, and innovative circuit design, researches are able to overcome those problems and thus transistor size as small as 14 nm is expected to be available by the end of 2014. If the Moore's law continues unabated and the miniaturization of transistor continues at this rate, by 2030 the size of transistor would reach atomic dimension. At such small device geometry, the quantum nature of electron will play significant role in the device operation and classical laws would no longer be applicable [5]. With the miniaturization of transistor, high

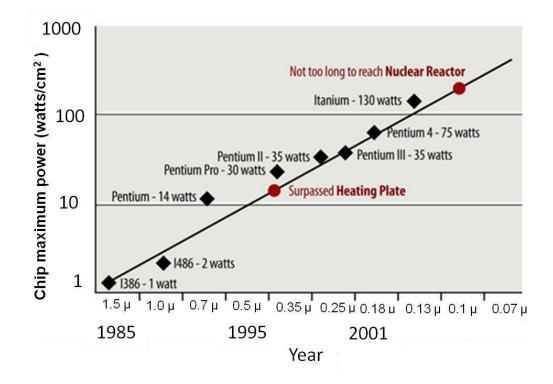

speed operation is achieved by increasing the density of components; however it leads to an increased generation of heat.

Figure 1.1 History and future of CMOS scaling. Image taken from ref [6].

Figure 1.2 shows the amount of power dissipated per unit area, with successive technology nodes. The reliability and performance of the devices are greatly affected by the increased amount of heat generation. With reduction of device size, electron tunnel through the barriers leading to an unexpectedly high leakage current. In addition, fabrication of such minuscule devices require complex design, high resolution lithography, and tight process controls which increases the manufacturing cost of the devices.

Thus, in the near future Moore's law will reach a dead end and the CMOS technology will lose its dominance in modern semiconductor industry. An innovative approach with new device physics and promising device architecture is required which could replace the conventional CMOS technology.

Figure 1.2 Power dissipation with technology node. Images are taken from ref [7]

The device operation should implement the quantum mechanical phenomena that arise during nanoscale dimensions. A number of emerging technologies and devices including, single electron transistors (SET), resonance tunnel diodes (RTD), spin transistor, molecular devices have been proposed for memory and logic operation as a replacement of current CMOS technology [8]. Among them SETs are considered as most promising replacement for the post CMOS era electronic devices. In an SET the electron transport is controlled by quantum tunneling [9, 10].

SET has several advantages over the conventional Si technology which includes ultra-low power consumption, scalability down to the sub-nanometer range, and ability to detect an extremely small amount of charge (single electron) [5, 10]. SET has shown potential for different device application including logic circuits, memory devices, and sensors [11-20]. Therefore, those advantages make SET a potential candidate as the basic element for quantum information processing system.

Although SETs have shown great potential, practical implementation of SET based devices is still in its infancy and face several challenges. The major challenge in the fabrication involves controlled fabrication of reproducible quantum dot (QD), the basic component of SET. So far different techniques has been developed to fabricate SET which includes lithographically defined QD in a GaAS/AlGaAs heterojunctions, direct etching of Si substrate, silicon on insulator (SOI) with pattern dependent oxidation, metallic grains in nanopore, and chemically synthesized colloidal nanocrystals [21-27]. However, such techniques involve complex fabrication steps, lack of reproducibility, low temperature operation, and inability for large scale fabrication, which have made those techniques unsuitable for practical application of SET based devices. For the practical realization of SET based devices several issues need to be addressed : i) the fabrication method need to be controllable and should give reproducible results, ii) the fabrication technique should be compatible with the conventional large-scale integration techniques, and iii) the SET devices should work at room temperature. In particular, parallel and controllable SET fabrication technique together with reproducible size of QD is also necessary to meet those challenges.

A possible route for the scalable and CMOS-compatible fabrication of SET is to use single wall carbon nanotubes (SWNTs) as QD. SWNTs, atomically thin layer of graphite (graphene) rolled up into a cylinder, is a true 1D material, show unique electronic, mechanical, and optical properties [28-34]. The very small dimension (diameter ~ 1-2 nm) of SWNT makes them a

suitable choice for SET as such a small feature is unattainable by conventional lithography techniques. Although SWNTs have shown potential as a QD, for the practical realization of SWNT based SET devices several issues need to be resolved. One of the major challenges is to find out reliable techniques for the assembly of individual SWNT which is compatible with the conventional CMOS technologies. Besides, absence of scaled up and reliable tunnel barrier fabrication technique is another major concern. Different techniques including AFM manipulation, deposition of top gate, FIB or ion induced damage etc. had been used to create tunnel barrier on SWNT to fabricate SET.[35-38] However in those technique SWNTs are assembled either by the chemical vapor deposition (CVD) growth or by random dispersion. During CVD process SWNTs grows at a high temperature (~ 900 °C) and hence is not CMOS-compatible. On the other hand, a large scale assembly is not possible using random dispersion as the alignment of individual SWNT depends on luck. Besides, their complicated design and lack of controllability on QD size make them only useful for proof-of-concept fabrication techniques and is unsuitable for parallel fabrication of SET based device.

In this thesis, I will demonstrate scalable, CMOS-compatible fabrication of SET using SWNT. We will use AC-dielectrophoresis, a large scale assembly technique to align individual SWNT between prefabricated source, and drain electrodes. I will use two different techniques to create tunnel barrier on SWNT: *i*) metal-SWNT Schottky contact, and *ii*) mechanical template. Subsequently, the low temperature transport measurement demonstrates that large scale assembly of SWNT based SET is possible using those techniques. Furthermore, I will demonstrate fabrication of SET that works even at room temperature by scaling down of the size of QD using the mechanical template technique.

#### 1.2 Outline of the thesis

Chapter 2 provides the background and basic theoretical concepts. I will begin with a detailed discussion on the electronic structure and properties of carbon nanotubes: the active material used for the fabrication of SET in our research. Subsequently, a short description of the components of SET including the concept of Coulomb blockade and the basic theory of single-electron tunneling will be introduced. Since high yield SET fabrication depends on the successful assembly of individual SWNT, the chapter will end with a discussion of different types of SWNT assembly techniques.

In chapter 3, I will discuss the device fabrication processes and electron transport measurement setups. In particular, I will discuss different steps of the fabrication of electrode patterns for the device integration using optical and electron beam lithography. This will be followed by the dielectrophoresis (DEP) assembly set-up used for the integration of the individual SWNT. Subsequently, the measurement setup will be discussed, including measurements needed for the electronic transport properties at cryogenic temperatures using <sup>4</sup>He cryostat.

In Chapter 4, I will demonstrate a technique for large scale assembly of SWNT devices. I use DEP to assemble SWNT between prefabricated contacts. By optimizing the DEP parameters it is possible obtain highest assembly yield. I will discuss the detailed electron transport properties of the SWNT devices.

In Chapter 5, I will discuss an approach for scalabale and CMOS-compatible technique for the fabrication of SET. The approach includes assembly of individual SWNT via DEP followed by deposition of metal top contact. Details about the design, fabrication steps will be discussed in this chapter. The detailed electron transport properties of the top contact SET device at low temperature will also be discussed. In chapter 6, we will present another novel technique for the scalable fabrication of SWNT SET by the mechanical template technique. Using this method large scale fabrication of SET is possible by aligning SWNT on mechanical template via DEP. We will explore the effect chirality on the mechanical templating of the SWNT by studying their transport properties at low temperature.

Technique for the fabrication of room temperature operating SET will be discussed in chapter 7. This can be achieved by scaling down the size of carbon nanotube to sub-40 nm. We scale down the width of mechanical template to reduce and control the size of QD.

In Chapter 8, I will suggest future research directions related to my work and also discuss possible experiments.

#### 1.3 References

1. Moore, G. E., Cramming more components onto integrated circuits. *Electronics Magazine* **1965**, 4.

2. Vassighi, A.; Semenov, O.; Sachdev, M.; Keshavarzi, A.; Hawkins, C., CMOS IC technology scaling and its impact on burn-in. *IEEE Transactions on Device and Materials Reliability* **2004**, 4, (2), 208-221.

3. Henson, W. K.; Yang, N.; Kubicek, S.; Vogel, E. M.; Wortman, J. J.; De Meyer, K.; Naem, A., Analysis of leakage currents and impact on off-state power consumption for CMOS technology in the 100-nm regime. *Ieee Transactions on Electron Devices* **2000**, 47, (7), 1393-1400.

4. Nowak, E. J., Maintaining the benefits of CMOS scaling when scaling bogs down. *Ibm Journal of Research and Development* **2002**, 46, (2-3), 169-180.

5. Devoret, M. H.; Schoelkopf, R. J., Amplifying quantum signals with the single-electron transistor. *Nature* **2000**, 406, (6799), 1039-1046.

6. Plummer, J. D.; Griffin, P. D., Materials and process limits in silicon VLSI technology. *Proceedings of the IEEE* **2001**, 89, (3), 240-258.

7. Feng, W.; The Importance of Being Low Power in High Performance Computing. *CTWatch Quarterly*, **2005**, 1(3).

8. International technology roadmap for semiconductor, **2007**.

8

9. Kastner, M. A., The single electron transistor. *Reviews of Modern Physics* **1992**, 64, (3), 849-858.

10. Likharev, K. K., Single-electron devices and their applications. *Proceedings of the IEEE* **1999**, 87, (4), 606-632.

11. Chen, R. H.; Korotkov, A. N.; Likharev, K. K., Single-electron transistor logic. *Applied Physics Letters* **1996**, 68, (14), 1954-1956.

12. Degawa, K.; Aoki, T.; Higuchi, T.; Inokawa, H.; Takahashi, Y., A single-electrontransistor logic gate family for binary, multiple-valued and mixed-mode logic. *Ieice Transactions on Electronics* **2004**, E87C, (11), 1827-1836.

13. Uchida, K.; Koga, J.; Ohba, R.; Toriumi, A., Programmable single-electron transistor logic for future low-power intelligent LSI: Proposal and room-temperature operation. *Ieee Transactions on Electron Devices* **2003**, *50*, (7), 1623-1630.

14. Maeda, K.; Okabayashi, N.; Kano, S.; Takeshita, S.; Tanaka, D.; Sakamoto, M.; Teranishi, T.; Majima, Y., Logic Operations of Chemically Assembled Single-Electron Transistor. *Acs Nano* 6, (3), 2798-2803.

15. Guo, L. J.; Leobandung, E.; Chou, S. Y., A silicon single-electron transistor memory operating at room temperature. *Science* **1997**, 275, (5300), 649-651.

16. Takahashi, Y.; Fujiwara, A.; Yamazaki, K.; Namatsu, H.; Kurihara, K.; Murase, K., A Si memory device composed of a one-dimensional metal-oxide-semiconductor field-effect-transistor switch and a single-electron-transistor detector. *Japanese Journal of Applied Physics Part 1-Regular Papers Short Notes & Review Papers* **1999**, 38, (4B), 2457-2461.

17. Knobel, R. G.; Cleland, A. N., Nanometre-scale displacement sensing using a single electron transistor. *Nature* **2003**, 424, (6946), 291-293.

18. Schoelkopf, R. J.; Wahlgren, P.; Kozhevnikov, A. A.; Delsing, P.; Prober, D. E., The radio-frequency single-electron transistor (RF-SET): A fast and ultrasensitive electrometer. *Science* **1998**, 280, (5367), 1238-1242.

Yoo, M. J.; Fulton, T. A.; Hess, H. F.; Willett, R. L.; Dunkleberger, L. N.; Chichester, R.

J.; Pfeiffer, L. N.; West, K. W., Scanning single-electron transistor microscopy: Imaging individual charges. *Science* 1997, 276, (5312), 579-582.

20. Feldheim, D. L.; Keating, C. D., Self-assembly of single electron transistors and related devices. *Chemical Society Reviews* **1998**, 27, (1), 1-12.

21. Fulton, T. A.; Dolan, G. J., Observation of single-electron charging effects in small tunnel junctions. *Physical Review Letters* **1987**, 59, (1), 109-112.

22. Ralph, D. C.; Black, C. T.; Tinkham, M., Spectroscopic measurements of discrete electronic states in single metal particles. *Physical Review Letters* **1995**, 74, (16), 3241-3244.

23. Klein, D. L.; Roth, R.; Lim, A. K. L.; Alivisatos, A. P.; McEuen, P. L., A single-electron transistor made from a cadmium selenide nanocrystal. *Nature* **1997**, 389, (6652), 699-701.

24. Meirav, U.; Kastner, M. A.; Wind, S. J., Single-electron charging and periodic conductance resonance in GaAS nanostructures. *Physical Review Letters* **1990**, 65, (6), 771-774.

25. Fujisawa, T.; Hirayama, Y.; Tarucha, S., AlGaAs/InGaAs/GaAS single electron transistors fabricated by focused ion beam implantation. *Applied Physics Letters* **1994**, 64, (17), 2250-2252.

10

Bjork, M. T.; Thelander, C.; Hansen, A. E.; Jensen, L. E.; Larsson, M. W.; Wallenberg,

L. R.; Samuelson, L., Few-electron quantum dots in nanowires. *Nano Letters* 2004, 4, (9), 16211625.

27. Nilsson, H. A.; Duty, T.; Abay, S.; Wilson, C.; Wagner, J. B.; Thelander, C.; Delsing, P.; Samuelson, L., A radio frequency single-electron transistor based on an InAs/InP heterostructure nanowire. *Nano Letters* **2008**, *8*, (3), 872-875.

Iijima, S.; Ichihashi, T., Single-shell carbon nanotubes of 1-nm diameter. *Nature* 1993, 363, (6430), 603-605.

Avouris, P.; Chen, Z.; Perebeinos, V., Carbon-based electronics. *Nature Nanotechnology* 2007, 2, (10), 605-615.

30. Frank, S.; Poncharal, P.; Wang, Z. L.; de Heer, W. A., Carbon nanotube quantum resistors. *Science* **1998**, 280, (5370), 1744-1746.

31. Bockrath, M.; Cobden, D. H.; McEuen, P. L.; Chopra, N. G.; Zettl, A.; Thess, A.; Smalley, R. E., Single-electron transport in ropes of carbon nanotubes. *Science* **1997**, 275, (5308), 1922-1925.

Bockrath, M.; Cobden, D. H.; Lu, J.; Rinzler, A. G.; Smalley, R. E.; Balents, L.; McEuen,

P. L., Luttinger-liquid behaviour in carbon nanotubes. *Nature* 1999, 397, (6720), 598-601.

33. Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. J., Ballistic carbon nanotube fieldeffect transistors. *Nature* **2003**, 424, (6949), 654-657.

34. Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; McIntyre, P.; McEuen, P.; Lundstrom, M.; Dai, H. J., High-kappa dielectrics for advanced carbon-nanotube transistors and logic gates. *Nature Materials* **2002**, 1, (4), 241-246.

35. Postma, H. W. C.; Teepen, T.; Yao, Z.; Grifoni, M.; Dekker, C., Carbon nanotube singleelectron transistors at room temperature. *Science* **2001**, 293, (5527), 76-79.

36. Ishibashi, K.; Suzuki, M.; Tsuya, D.; Aoyagi, Y., Fabrication of single electron transistors in multi-wall carbon nanotubes using Ar beam irradiation. *Microelectronic Engineering* **2003**, 67-8, 749-754.

37. Maeda, M.; Iwasaki, S.; Kamimura, T.; Murata, K.; Matsumoto, K., Room-temperature carbon nanotube single-electron transistor with defects introduced by La(NO3)(3) process. *Japanese Journal of Applied Physics* **2008**, 47, (7), 5724-5726.

38. Maehashi, K.; Ozaki, H.; Ohno, Y.; Inoue, K.; Matsumoto, K.; Seki, S.; Tagawa, S., Formation of single quantum dot in single-walled carbon nanotube channel using focused-ion-beam technique. *Applied Physics Letters* **2007**, 90, (2), 3.

## **CHAPTER 2: BACKGROUND<sup>1</sup>**

#### 2.1 Carbon nanotubes

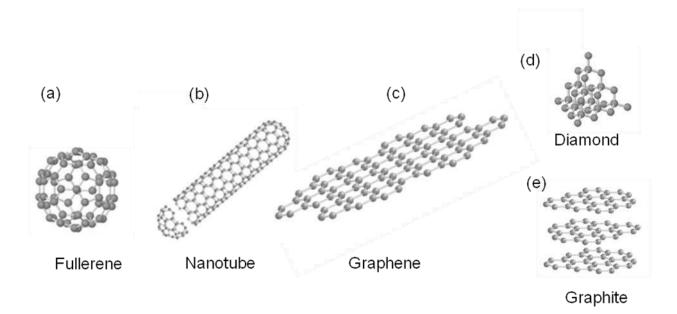

Carbon, a remarkable element, offers the extraordinary opportunity to investigate a material in all possible dimensionalities. It has many different stable forms ranging from 0D fullerenes, to1D nanotubes, to 2D graphene, and finally 3D diamond and graphite. The different forms of carbon are in presented in Fig. 2.1.

Figure 2.1 A few examples of the stable forms of carbon with the different dimensionalities and various forms. They range from (a) 0D fullerene to (b) 1D nanotube to (c) 2D graphene to 3D (d) diamond and (e) graphite. Images are taken from ref [1].

<sup>&</sup>lt;sup>1</sup> Part of the work presented in this chapter are extensions of Muhammad R. Islam and Saiful I. Khondaker, Recent progress in parallel fabrication of individual single walled carbon nanotube devices using dielectrophoresis. Materials Express 4, 263 (2014) (Cover article).

The history of carbon nanotube (CNT) begins with the discovery of first carbon based nanostructure, fullerene. The first fullerene molecule named, buckyball ( $C_{60}$ ), shown in Fig. 2.1 (a) was discovered in 1985 [2]. It is a hollow sphere made of carbon atoms in the form of soccer ball. The discovery of fullerenes greatly influenced the carbon nanostructure based research.

CNTs was discovered in 1991 by Iijima during synthesis of fullerenes by electric arc discharge technique [3]. CNTs observed by Iijima were called multi-walled carbon nanotubes (MWNTs). In an MWNT several concentric cylinders made of graphene are placed with an interlayer spacing of 3.4 Å and a diameter of varying between 10 to 20 nm. Two years later, researchers from NEC [4] and IBM [5] independently synthesized single-walled carbon nanotubes (SWNTs) as shown in Fig. 2.1b. In contrast to MWNT, a SWNT consist of a single sheet of graphene rolled up into a seamless hollow cylinder. Since its discovery, SWNT have created huge interest in different areas of science and technology because of their exceptional electronic, optical and mechanical properties. In short SWNT is a unique material providing a combination of superlative electronic, optical, mechanical and thermal properties. In this theis will discuss the fabrication and electron transport measurements of SWNT based SETs.

# 2.1.1 Structure of carbon nanotubes

The basic configuration of a carbon nanotube can be described as a seamless cylinder made by rolling a graphene sheet with fullerene cap at ends [6]. Graphene is a single atomic layer of SP<sup>2</sup> bonded carbon atoms arranged into a honeycomb lattice [7]. The graphene sheet can be rolled in different way to give different type of SWNT. Depending on the rolling of the graphene sheets, the SWNTs give different geometrical and electrical properties which are known as chirality. Figure 2.3(a) presents an arbitrary way to construct a SWNT from a graphene sheets. A nanotube

is uniquely described by the vector (chiral vector)  $\vec{c} = n\vec{a}_1 + m\vec{a}_2$  where,  $\vec{a}_1$  and  $\vec{a}_2$  are primitive translation lattice vectors and *n* and *m* are integers. The circumference of tube can be expressed by the vector  $\vec{c}$  and radius *r*, of the tube [8]:

Figure 2.2 (a) A graphene sheet that can be folded into a seamless cylinder by cutting out the sheet along the dashed lines and rolling it up along vector  $C_h$ .  $a_1$  and  $a_2$  are the unit vectors of the hexagonal graphene sheet (b) Example of a "zig-zag" nanotube. (c) Example of a "armchair" nanotube. (d) Example of a "armchair" nanotube. Adpated from ref [9].

$$r = \frac{|\vec{c}|}{2\pi} = \frac{a}{2\pi} \sqrt{n^2 + m^2 + nm}$$

(2.1)

Here *a* is the lattice constant defined by,  $a = \sqrt{3}a_{cc}$ ,  $a_{cc}$  is the C-C bond length. Also the chiral angle  $\varphi$ , which is the tilt angle between the hexagon and the nanotube axis can be described using the chiral vector:

$$\varphi = \arccos\left(\frac{\sqrt{3}(n+m)}{2\sqrt{n^2 + m^2 + nm}}\right)$$

(2.2)

Because of the hexagonal symmetry of graphene structure  $\varphi$  lies in the range between 0 to 30°.

Nanotubes are generally labeled using the (m,n) indices. For example, (n, 0) nantubes have carbon-carbon bond along the axial direction of nanotube giving a chiral angle  $\varphi = 0^{\circ}$ . These nanotubes are called zigzag nanotube (Fig 2.2(b)). For nanotubes labeled (n,n), the chiral angle is  $\varphi = 30^{\circ}$  with the carbon-carbon bond normalr to the length of the nanotube, and is called armchair nanotube shown in Fig 2.2 (c) [8]. All the remaining configurations (n, m  $\neq$  n  $\neq$  0) are called chiral nanotube shown in figure 2.2(d).

### 2.1.2 Electronic properties of carbon nanotubes

Since rolling of graphene gives single wall carbon nanotube, we can obtain the band structure of nanotube from the band structure graphene. By applying proper boundary conditions on the momentum wave vectors of graphene structure it is possible to derive the band structure of SWNT. For an infinite long nanotube the wavevector along the tube axis,  $\vec{k}_{\mu}$  is continuous and the wavevector perpendicular to  $\vec{k}_{\mu}$ ,  $\vec{k}_{\perp}$  follow the periodic boundary condition  $\vec{k}_{\perp} \cdot \vec{c} = 2\pi q$ , where q = 0, 1, 2, ..., n. This boundary condition leads to a quantized value allowed for the  $\vec{k}_{\perp}$ , which satisfy the relation,  $d\vec{k}_{\perp} = 2/d$  where d is diameter of SWNT. We can obtain the 1D subband of nanotube by cutting of the graphene band structure along the cross-sectional

direction with the allowed  $\vec{k}_{\perp}$  values (fig 2.3(a)). Under certain conditions the allowed  $\vec{k}_{\perp}$  states

Figure 2.3 (a) Band structure of graphene. It shows that the one dimensional subbands of nanotubes can be determined by applying boundary conditions. Low energy band structure of carbon nanotube: (b) For p = 0, there is an allowed value of  $\vec{k}_{\perp}$  whose subband passes through the middle of the dispersion cone which results in a metallic nanotube. (c) Energy dispersion for a metallic nanotube. (d) For p = 0, there is an allowed value of  $\vec{k}_{\perp}$  whose subband misses the middle of the dispersion cone which results in a metallic nanotube. (e) Energy dispersion for a semiconducting nanotube. Figure adopted from ref [10].

In this case the energy dispersions show bands crossing the Fermi level without any band gap and hence the nanotube (Fig 2.3 (b)) shows metallic behavior. If the  $\vec{k}_{\perp}$  states miss the middle of dispersion cone (Fig 2.3 (d)) then there have two parabolic bands results in a bandgap near Fermi level giving a semiconducting nanotube [11-13]. Thus depending on the quantization of  $\vec{k}_{\perp}$  either semiconducting or metallic transport can be obtained. In fact the wrapping indices (m, n) of the nanotube determines the electronic properties of SWNT. For any arbitrary (m, n) nanotube, n-m = 3a+b, where a is an integer and b is -1, 0, or 1 [14]. If b=0 then the allowed  $\vec{k}_{\perp}$  is such that it pass through the middle of the dispersion zone and the nanotube is metallic. The slope of the dispersion cone, for metallic SWNT, depends on the Fermi velocity,  $dE/dK = \hbar v_F$ , where  $v_F \sim 8 \times 10^5$  m/s [15]. If b= +1 or -1 then the  $\vec{k}_{\perp}$  states miss the middle of dispersion cone, gives semiconducting nanotube. For a semiconducting nanotube the  $\vec{k}_{\perp}$  vector misses the middle of dispersion cone by,  $\Delta \vec{k}_{\perp} = \pm \frac{2}{3d}$ . Therefore the bandgap of the semiconducting nanotube is given by,

$$E_g = 2 \times \left(\frac{dE}{dK}\right) \times \frac{2}{3d} = 2\hbar v_F \left(\frac{2}{3d}\right) \approx 0.7 eV/d(nm)$$

(2.3)

Therefore the bandgap of the semiconducting nanotube (d = 0.8-3 nm) varies between 0.2 eV to 0.9 eV and is proportional to the reciprocal of the diameter. For a more detailed description of the structural and electronic properties of carbon nanotube including the band structure calculation reader can explore the review article [16-19].

# 2.2 Single electron transistor

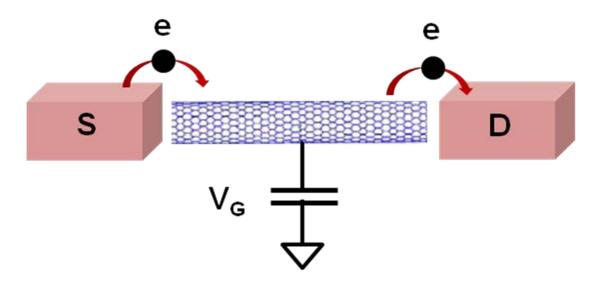

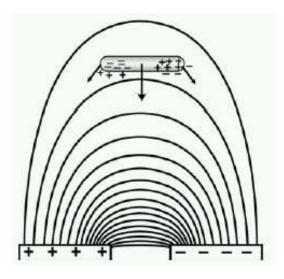

Figure 2.4 Schematic of a single electron transistor with the electrical connection. A conducting island often called quantum dot (QD) coupled to the source and drain leads via tunnel barriers and capacitively connected to a gate.

Figure 2.4 describes the schematic diagram of a single electron transistor (SET) with all its important components and parameters. An SET consists of a small conducting island often called quantum dot (QD) which is resistively attached to the source and drain reservoirs, through which charge particle transfer takes place. QD is capacitively coupled to nearby gate electrodes. The gate voltage tune the entire ladder of electrochemical potential of the QD up and down with respect to the bias voltage [20-22]. There exist tunnel coupling between the QD and the reservoir that allows electrons to flow between the QD and electrodes via single electron tunneling. If N is the number of electrons in the QD then the charges on the island are quantized and equal to Ne. If an electron tunnel through the QD the number of electrons, N in the QD is adjusted to minimize the energy in the circuit.

During tunneling the charges of QD is change by ne (n = 1, 2, ...). This changes the electrostatic potential energy of the QD by,  $Ec = e^2/C_{\Sigma}$ , where capacitance  $C_{\Sigma} = C_1 + C_2 + C_3$ ,

is the total capacitance of the SET. In order to observe single electron tunneling this charging energy  $E_C$  needs to be greater than the thermal energy ( $K_BT$ ). Also the tunnel barrier needs to be sufficiently opaque so that the electrons are located either in the source, drain or on the QD [20, 21, 23]. This means that the quantum fluctuation in the number N of electron tunnel through the island must be much smaller than the inverse of time. This criterion sets a lower limit for the tunnel resistance  $R_t$ , which can be found from the uncertainty principle. The charging or discharging time for the QD is  $\Delta t = R_t C$ . Applying uncertainty principle we get,  $\Delta E\Delta t = (e^2/C)R_t C > h$ . This implies  $R_t$  should be much larger than the quantum resistance  $h/e^2=25.81$  K $\Omega$  in order to minimize the energy uncertainty. Therefore the two conditions for observing single electron tunneling are:

$$R_t \gg h/e^2 = 25.81K\Omega \tag{2.4}$$

$$E_c = e^2 / C_{\Sigma} >> k_B T \tag{2.5}$$

By weekly coupling the island to the source and drain leads, the first condition can be met. The second condition can be met by making the QD very small since the capacitance of any object scales with its dimension. Typically the size of QD ranges between few nanometer to few micron which yields capacitance of the order of aF. Therefore in order to satisfy the second condition and observe the single electron tunneling, measurements need to be performed at cryogenic temperatures.

# 2.2.1 Electron transport through single electron transistor

The electronic transport through a single electron transistor can be usually described by the constant interaction (CI) model [24, 25]. This model is based on two assumptions: (1) the

$E_{add}$  is called addition energy. Coulomb interaction among the electrons inside the dot and between the electrons in the dot and somewhere else in the circuit are parameterize by a capacitance *C*. Here  $C = C_S + C_D + C_G$ , is the total capacitance where  $C_S$ ,  $C_D$ , and  $C_G$  are the capacitance of the source, drain and gate respectively. (2) The quantum energy levels and *C* are independent of the number of electrons on the QD. The total energy of a *N*-electron dot using CI model is given by

$$U_{n} = \frac{\left[-\left|e\right|(N-N_{0}) + C_{S}V_{s} + C_{D}V_{D} + C_{G}V_{G}\right]^{2}}{2C} + \sum_{n=1}^{N} E_{n}(B)$$

(2.6)

Where, |e| is the charge of electron and  $N_0$  is the number of electrons in the QD at  $V_G$ =0, and  $V_S$ ,  $V_D$ , and  $V_G$  are the voltage applied to the source, drain, and gate, respectively. The term  $C_S V_S$ ,  $C_D V_D$ , and  $C_G V_G$  represent the induced charge and electrostatic potential on the dot. And the last term of Eq. 2.6 is the sum over the occupied single-particle energy levels  $E_n(B)$ , and it depend on the characteristics of the confinement potential.

The transport of QD can be more conveniently described using the idea of electrochemical potential,  $\mu$  which is the minimum energy needed to populate the QD with an additional carrier:

$$\mu(N) = U(N) - U(N-1) = (N - N_0 - \frac{1}{2})E_C - \frac{E_C}{|e|}(C_S V_S + C_D V_D + C_G V_G) + E_N$$

(2.7)

Where,  $E_C = e^2/C$  is the charging energy. Here,  $\mu(N)$  is the potential when the number of electron in the minimum energy state changes from N-1 to N. Spacing between two consecutive energy states are given by:

$$E_{add}(N) = \mu(N+1) - \mu(N) = E_{C} + \Delta E$$

(2.8)

Figure 2.5 Cartoon for the electrochemical potential of the SET at different voltage configuration. (a) The electrochemical potential of QD does not falls inside the bias window - which cuses current blockade. (b) The electrochemical potential of the QD is drag inside bias window by sweeping gate voltage and electron tunneling occurs. (c) Application of bias voltage rises the electrochemical potential of the drain and electron tunneling occur once the electrochemical potential of the QD fall inside dias window. (d) Excited energy levels are obtained for application of large bias voltage.

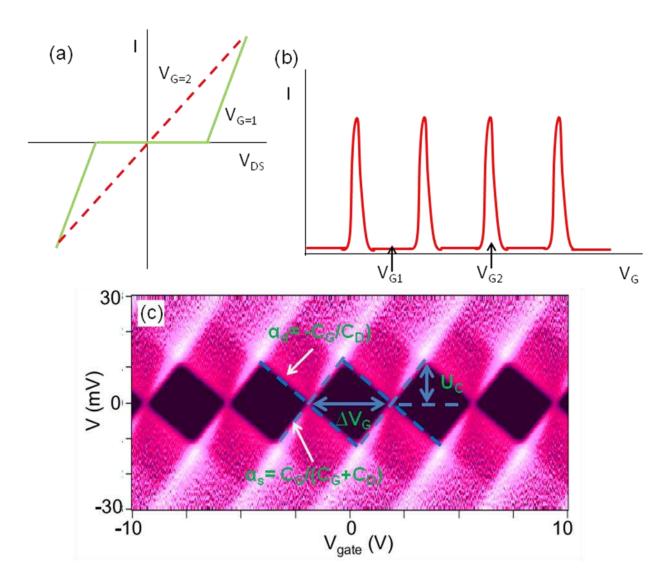

The addition energy is defined as  $E_{add} = E_C + \Delta E$ . Where  $\Delta E$  is separation between two quantized energy levels and is zero if the energy levels are degenerate. Single electron tunneling through a QD depends on the relative position of electrochemical potentials of dot, source, and drain. When voltage is applied at source then a "bias window" is open up. The energy in the bias window is between  $\mu_S$  and  $\mu_D$  ( $\mu_S \ge \mu \ge \mu_D$ ), and  $\mu_S - \mu_D = -|e|V_{SD}$ . When the electrochemical potential of QD lies in the bias window, electrons can tunnel from the source to the drain. If this condition does not met then no electron can flow through the island and is known as Coulomb blockade (fig 2.5 (a)). Single electron tunneling can also be observed by sweeping the gate voltage. This shifts the energy levels of QD up or down. When the electrochemical potential of QD fall inside the bias window single electron tunneling occur and the number of electrons by one as shown in Fig. 2.5 (b). By measuring the current while sweeping the gate voltage, we obtain a trace as presented in Fig 2.6 (b), which is known as Coulomb oscillation. Coulomb oscillation gives aluable information about SET. The distance between the peaks gives  $E_C + \Delta E$ . The space between two peaks represents Coulomb blockade and electron transfer does not occur here. Thus by tuning the gate voltage, it is possible to control the electron tunneling through the QD.

Coulomb blockade can also be lifted by applying bias  $V_{SD}$  (see Fig. 2.5 (c). Bias voltage changes the electrochemical potential the source and drain. When the electrochemical potential of the QD is between the bias windows an electron tunneling occurs. By increasing  $V_{SD}$  further it is possible to observe excited state of QD (Fig. 2.5 (d)).

A plot of the conductance versus source- drains voltage, and gate voltage is shown in fig 2.6 (c). This is known as "stability plot". The blue outlined diamond structures are known as Coulomb diamonds. Inside the coulomb diamond no current flows due to Coulomb blockade. Outside the diamonds, single-electron tunneling take place and Coulomb blockade is lifted. The stability plot contains all the information of the SET and the SET parameters can be extracted from this plot. For example the gate capacitance can be obtained using the relation  $C_G = e/\Delta V_G$  where,  $\Delta V_G$  is separation between two diamond. The source and drain capacitances can be derived from the slopes of the Coulomb diamonds using the relation,  $\alpha_S = -C_G/C_S$  and  $\alpha_D = C_G/(C_G + C_D)$ . The charging energy defined as  $U_C = e^2/C_{\Sigma}$  can be obtained once we know all different capacitances. Also the height of Coulomb diamond gives the charging energy of the QD.

Figure 2.6 Typical low temperature electron transport behavior of SET (a) at gate voltage,  $V_{G1}$ , current is suppressed and is called Coulomb blockade (CB). Electron tunneling occur when a gate voltage to  $V_{G2}$  is applied. (b) Tuning the gate voltage gives current oscillation known as Coulomb Oscillation (CO) (c) Stability plot, where conductance vs source-drain voltage vs gate voltage is plotted.

# 2.2.2 Fabrication of different type of single electron transistors

Single electron tunneling was first observed about sixty years ago in extremely thin film consist of discontinuous grain. High resistance observed in these films at low temperature was explained by Gorter et al. in 1951 [26]. The field and temperature dependent resistance was considered to be an effect of the separation of positive and negative charge. Similar effect was observed in discontinuous gold film by Neugebauer et. al. in 1962 [27]. They derived a conductivity based on the creation of charge and field dependent tunneling between islands. Charge transport through a layer of tin particles in embedded oxide was investigated by Giaever et. al. several years letter [28]. They explain the high resistance behavior at low bias using a capacitor-charging model.

Several decades later, innovations in nanolithography and thin film processing enabled better-controlled fabrication of artificial structures small enough to demonstrate single electron effects at cryogenic temperatures. The first experimental demonstration of an SET was done by Fulton and Dolan in 1987 [29]. In their work tunnel junctions were formed in overlapping layer of aluminum thin film by controlling the shadow evaporation angle.

Coulomb oscillations in semiconductors were first observed in 1989 [30]. Current oscillations was observed in narrow 1D channel on dual gated Si MOSFET. The upper gate forms an inversion channel in the Si and a narrow gap is created by the other gate create a horizontal confinement, for the electron gas to move in only one direction. Electrostatic potential originating from the random charges at the Si/SiO<sub>2</sub> interface create tunnel barrier. In 1990 SET was fabricated in a GaAs/AlGaAs 2-DEG by Meirav et. al.[31]. They patterned a constriction in a channel which creates the potential barriers for electrons moving down the channel using a gate potential. The potential barriers in this case were defined lithographically.

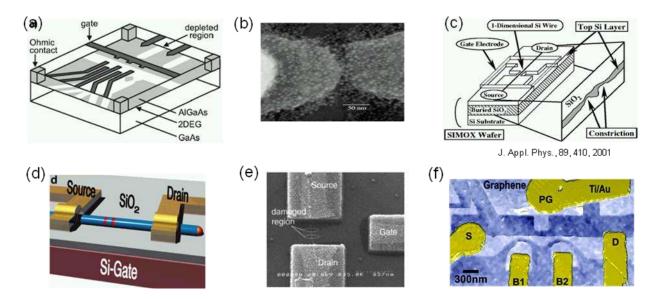

25

Figure 2.7 Popular SET fabrication techniques: (a) surface pattering of 2DEG heterostructure [31] (b) self assembly of CdSe colloidal nanocrystal [32] (c) Etching Si substrate [34] (d) patterning of InAs nanowire with InP barriers.[42] (e) Nanotube SET defined by metal contacts[48] (f) Graphene SET [64].

Several other techniques including metallic grains or particle in nanopore [32, 33], direct etching of Si substrate [34], colloidal nanocrystals [35-38], focused ion beam [39-41] had been used for the fabrication of SET. Lithography defined dots in 2DEG or Si MOSFETs typically require ultra-low (sub-Kelvin) temperatures for operation. Higher operating temperature (~100 K) and reproducible SET behavior can be obtained by metallic grains and colloidal nanocrystals. However it is very difficult to place nanoparticles or metallic grains inside the nanopore.

Recently, nanowires [42-45] and carbon nanotubes including both MWNT [46, 47] and SWNT [48-63] are considered as promising candidates for the QD of SETs because of their ultra-small diameters (~ 1nm) along with the unique one dimensional nature. Besides 2D graphene are also used as active materials for fabrication of SET very recently [64-67].

Fabrication of SWNT based SET relies on the creation of tunnel barriers along the axial direction of the tube, which will be discussed in more detail in the next section.

2.2.3 Carbon nanotube quantum dots

Figure 2.8 Schematic diagram of a carbon nanotube quantum dot which can be formed by depositing metal electrodes, source (S) and drain (D), on top of the tube separated by a distance L. The nanotube is capacitively coupled to the gate, (usually the back gate plane of the silicon substrate). The QD is formed in the segment of nanotube in between the electrodes.

We described the basic electronic properties of SWNT in section 2.1. Due to the momentum quantization along traverse direction nanotubes are considered as one dimensional object. At low temperatures for the nanotubes with short lengths, discrete energy levels originating from the zero-dimensional nature of the nanotubes electronic states manifest itself and nanotubes behave as quantum dots [68].

In SWNT tunnel barriers can be created by depositing metal electrodes. The size of the QD is defined by the separation between two such barriers (metal contact), *L*, (Fig. 2.8). This

results in quantized energy levels in the longitudinal direction, with an energy level separation  $\Delta$ . The strength of the tunnel barriers determines the degree of confinement of electrons in the nanotube QD.

For very strong (opaque) barriers, the tunnel rate between the QD and the reservoirs ( $\Gamma$ ) is very small which results in a large lifetime of the electrons in the QD. If the barriers become more transparent, the energy levels get ' $\Gamma$ -broadened'. Depending on the ratio between the lifetime broadening and the charging energy *Ec*, there are three different types of QD regimes (with different typical phenomena associated with them):

1. Closed QD regime: ( $h\Gamma < < E_C$ ): Charging effects dominate transport (Coulomb blockade). Single electron transistors operates in the Coulomb blockade regime.

2. Intermediate transparency regime: ( $h\Gamma \leq E_C$ ): Charging effects are important in this regime (co-tunneling and Kondo effect).

3. Open QD regime: ( $h\Gamma >> E_C$ ): Quantum interference of non-interacting electrons dominates in this regime (Fabry-Perot like interference).

Metal-SWNT coupling depends on the metal contact, diameter and type of the nanotube (metallic/semiconducting). In general metals such as Au or Pd [69-71] make good contact to nanotubes. Whereas Al or Cr make bad contact to nanotubes. It has also been demonstrated that the nanotubes with larger diameter give very small contact resistance [69, 72]. Also the metallic nanotube gives batter contact (lower contact resistance) compare to the semiconducting ones. Usually Schottky barriers are created at the nanotube-metal interface for semiconducting SWNT.

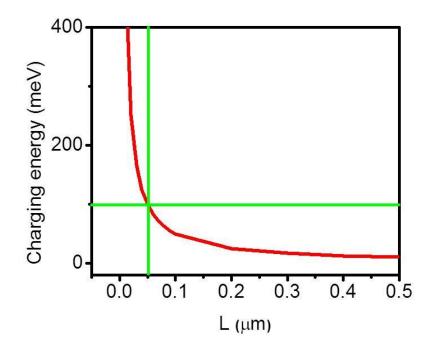

Charging energy  $E_C$  of the SWNT quantum dots are generally high, and is inversly proportional to the capacitance, C of the device. For a nanotube QD, of length L the capacitance can be expressed by considering the formula of a coaxial cable,

$$C = \frac{2\pi\varepsilon_0\varepsilon_r}{\ln(2h/r)}L$$

(2.9)

where  $\varepsilon_r = 3.9$  is the average dielectric constant of Si [73], *h* is the thickness of gate oxide and *r* is the radius of the nanotube.

We can approximate the charging energy of a nanotube between two leads by a simple model,

$$E_C = \frac{e^2}{C} \approx \frac{e^2}{\varepsilon_0 \varepsilon_r L} \approx \frac{5meV}{L(nm)}$$

(2.10)

Using the particle in a box model we can also approximate the single particle energy levels by,

$$\Delta E = \frac{h\nu_F}{2L} \approx \frac{1meV}{L(\mu m)} \tag{2.11}$$

Where L is the length of the QD, h is planks constant and  $v_F$  is the Fermi velocity[73].

# 2.2.4 Fabrication of carbon nanotube quantum dots

In order to fabricate carbon nanotube single electron transistor using we have to create quantum dot in the nanotube. In a nanotube quantum dot can be created by creating tunnel barrier along the nanotube. Tunnel barrier are usually created by crating defects in the nanotube. Carbon nanotube single electron transistors have been demonstrated by several techniques by creating tunnel barrier.

The first attempt to fabricate nanotube based single electron transistor was performed using multiwall carbon nanotube. In 1999, L Roscheir et. al. had employed scanning probe manipulation for the fabrication of single electron transistor using semiconducting multiwall nanotube [46]. AFM tip was used to drag MWNT on metal electrode and the portion of MWNT between the electrodes act as QD. For those devices SET behavior was observed at 15 mK and it shows a charging energy of 15 meV. SET was also fabricated by placing MWNT on top of another MWNT [47].

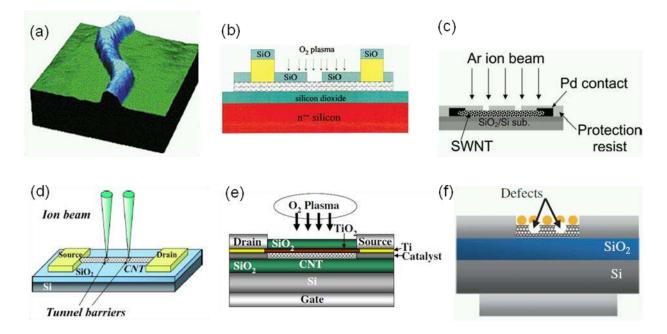

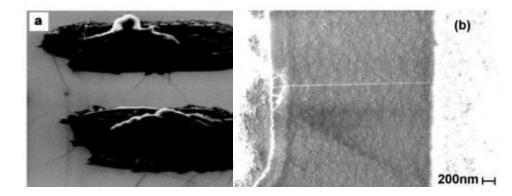

Figure 2.9 Carbon nanotube single electron transistors fabrication techniques. (a) Bending carbon nanotube by AFM tip [48] (b) Modification of nanotube by oxygen ( $O_2$ ) plasma [49] (c) Bombardment of nanotube by Ar ion beam [57] (d) Fabrication of tunnel barrier by focused ion bean (FIB) defects by Ar ion [75] (e) Creation of defects by  $O_2$  plasma [56] (f) Introducing defects by ion La particles [58].

In 2001 AFM manipulation technique was used to create SWNT based SET [48]. AFM tip was used to bend the SWNT at selected position as shown in figure 2.9 (a). The bend act as tunnel barrier and two such barriers define a QD and the device show SET characteristics at room temperature. A QD of size 25nm was created by this technique which gives a charging energy of 120 meV which is higher than room temperature thermal energy (~26 meV). It is

possible to fabricate single QD using this technique, however creating bend in SWNT using AFM tip is difficult and controlling the size of QD is also challenging.

QD was also defined by modifying the SWNT locally via chemical treatment [49]. In this technique QD is defined by placing a nanowire on top of a SWNT. The entire substrate is then coated with polymer and a gap is created on top of the SWNT by removing the nanowire as shown in figure 2.9 (b). The open window is plasma etched to create QD. The device shows room temperature SET operation.

Tunnel barrier in SWNT can also be created by making defects via ion irradiation [55, 56, 58, 59, 74]. SWNT are bombarded by low energy particle or gas ion (La, Ar, N<sub>2</sub>) as shown in figure 2.9 (c)-2.9 (f). Generally MQD are created in this techniques and the size of the device cannot be controlled. Focused ion beam (FIB) was also used for the creation of tunnel barrier in nanotube [75]. The devices show SET behavior with high charging energy. Mostly multiple QD are created in this technique and due to the high energy processing nanotube got damaged.

#### 2.3 Assembly of SWNTs

Assembly of SWNT is one of the most important parts to fabricate nanotube based devices. Fabrication of SET using SWNT has two major steps: 1) assembly of individual SWNT to the circuit, and 2) creation of tunnel barrier to the SWNT. In particular large scale assembly of individual SWNT is required for the assembly of individual SWNT. Here in this section we will discuss techniques for the assembly of SWNT.

# 2.3.1 Find 'em and wire 'em technique

Find 'em and wire 'em technique is technique is oldest and widely used methods for the integration of SWNT. Many novel physics associated with individual SWNT has been observed with devices fabricated using this approach [76-79]. In this technique SWNT are randomly dispersed on silicon substrate containing marker. The SWNT on which the device needs to be fabricate is located by scanning electron microscopy (SEM) or atomic force microscopy (AFM). Once the position of the SWNT is located electrode pattern are defined by electron beam or optical lithography. Different electronic and optical devices were made using this approach. Figure 2.10 (a) shows the images of SWNT device fabricated by placing individual SWNT the metal electrodes [80]. The advantage of the find 'em and wire 'em technique is that it can customized the devices.

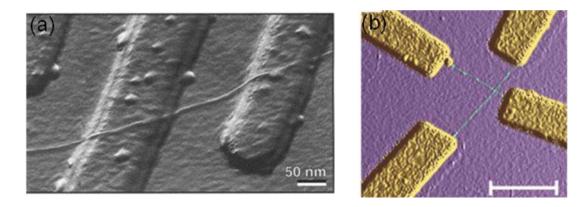

Figure 2.10 (a) Field effect transistor fabricated where SWNT was randomly placed between metal electrodes by the 'find' em and 'wire' technique[80]. (b) Complex SWNT structure (crossing of two SWNT) assembled by 'find' em and 'wire' technique[79]

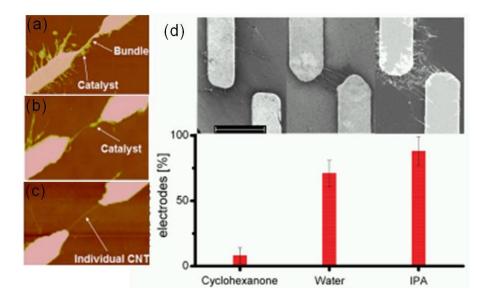

Figure 2.10 (b) shows an AFM image of device with customized design where, crossed SWNTs are contacted between two metal (Au) contacts using the "find 'em and wire 'em" technique in order to study interaction between two SWNT [79]. The disadvantages of the find 'em and wire