Linköping Studies in Science and Technology. Dissertations, No. 1385

## Low Complexity Techniques for Low Density Parity Check Code Decoders and Parallel Sigma-Delta ADC Structures

Anton Blad

## Linköping University INSTITUTE OF TECHNOLOGY

Department of Electrical Engineering Linköping University SE–581 83 Linköping Sweden

Linköping 2011

# Low Complexity Techniques for Low Density Parity Check Code Decoders and Parallel Sigma-Delta ADC Structures

Anton Blad

Linköping Studies in Science and Technology. Dissertations, No. 1385

Copyright © 2011 Anton Blad

ISBN 978-91-7393-104-5 ISSN 0345-7524

e-mail: anton.blad@gmail.com thesis url: http://urn.kb.se/resolve?urn=urn:nbn:se:liu:diva-69432

Department of Electrical Engineering Linköping University SE–581 83 Linköping Sweden

Printed by LiU-Tryck, Linköping, Sweden 2011

### Abstract

In this thesis, contributions are made in the area of receivers for wireless communication standards. The thesis consists of two parts, focusing on implementations of forward error correction using low-density parity-check (LDPC) codes, and highbandwidth analog-to-digital converters (ADC) using sigma-delta modulators.

LDPC codes have received wide-spread attention since 1995 as practical capacity-approaching code candidates. It has been shown that the class of codes can perform arbitrarily close to the channel capacity, and LDPC codes are also used or suggested for a number of current and future communication standards, including the 802.16e WiMAX standard, the 802.11n WLAN standard, and the second generation of digital TV standards DVB-x2. The first part of the thesis contains two main contributions to the problem of decoding LDPC codes, denoted the early-decision decoding algorithm and the check-merging decoding algorithm. The early-decision decoding algorithm is a method of terminating parts of the decoding process early for bits that have high reliabilities, thereby reducing the computational complexity of the decoder. The check-merging decoding algorithm is a method of reducing the code complexity of rate-compatible LDPC codes and increasing the efficiency of the decoding algorithm, thereby offering a significant throughput increase. For the two algorithms, architectures are proposed and synthesized for FPGAs and the resulting performance and logic utilization are compared with the original algorithms.

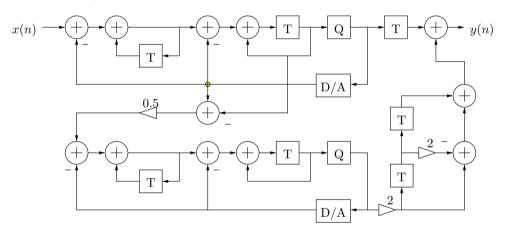

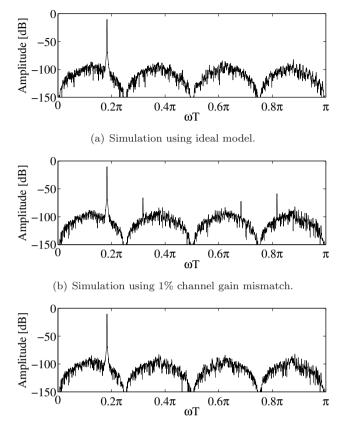

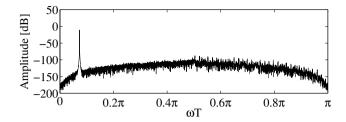

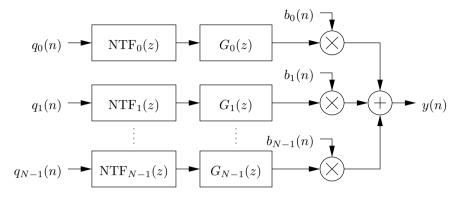

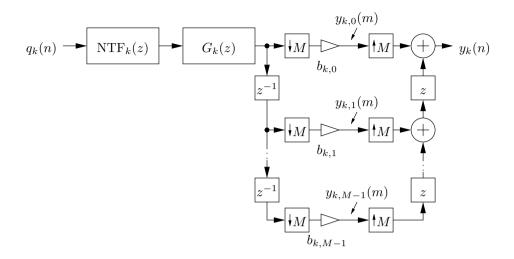

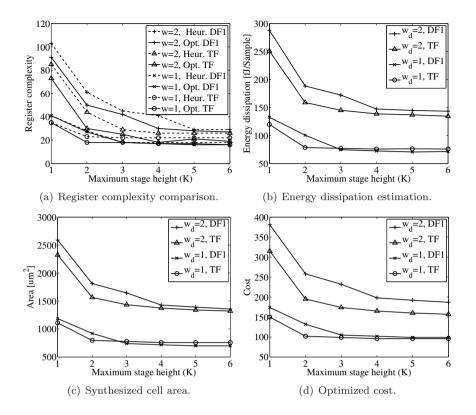

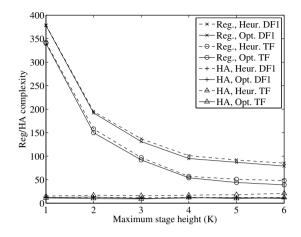

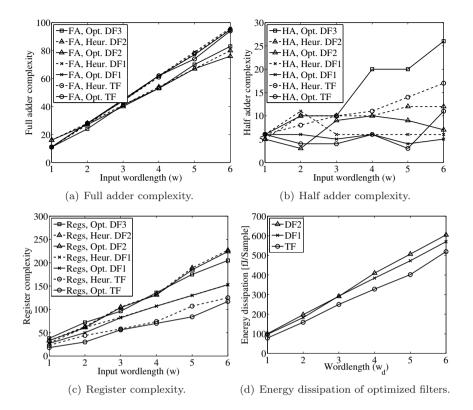

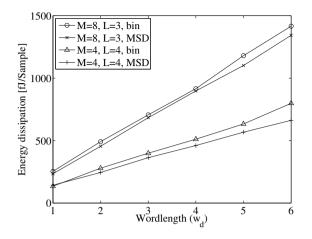

Sigma-delta ADCs are the natural choice of low-to-medium bandwidth applications that require high resolution. However, suggestions have also been made to use them for high-bandwidth communication standards which require either high sampling rates or several ADCs operating in parallel. In this thesis, two contributions are made in the area of high-bandwidth ADCs using sigma-delta modulators. The first is a general formulation of parallel ADCs using modulation of the input data. The formulation allows a system's sensitivity to analog mismatch errors in the channels to be analyzed and it is shown that some systems can be made insensitive to certain matching errors, whereas others may require matching of limited subsets of the channels, or full matching of all channels. Limited sensitivity to mismatch errors reduces the complexity of the analog parts. Simulation results are provided for a time-interleaved ADC, a Hadamard-modulated ADC, a frequencyband decomposed ADC, as well as for a new modulation scheme that is insensitive to channel gain mismatches. The second contribution relates to the implementation of high-speed digital filters, where a typical application is decimation filters for a high-bandwidth sigma-delta ADC. A bit-level optimization algorithm is proposed that minimizes a cost function defined as a weighted sum of the number of full adders, half adders and registers. Simulation results show comparisons between bit-level optimized filters and structures obtained using common heuristics for carry-save adder trees.

### Populärvetenskaplig sammanfattning

De flesta av dagens trådlösa kommunikationssystem bygger på digital överföring av data. Denna avhandling innehåller två delar, vilka ger bidrag till två olika delar i moderna mottagare för digitala kommunikationssystem.

I den första delen behandlas energieffektiv avkodning av felrättande koder. Felrättande kodning är en av de främsta fördelarna med digital kommunikation gentemot analog kommunikation, och bygger på att man i överföringen lägger till redundans till informationen man skickar. Under överföringen blir det ovillkorligt fel, men med hjälp av redundansen är det möjligt att räkna ut var det gick fel, och man kan på så sätt öka pålitligheten i överföringen. Felrättande koder med stor förmåga att upptäcka och rätta fel är lätta att konstruera, men att bygga praktiska implementeringar av en avkodare är svårare, och avkodaren använder ofta en stor del av strömförbrukningen i IC-kretsar för mottagare. I den här avhandlingen behandlas en specifik typ av felrättande koder (LDPC-koder) som kommer mycket nära den teoretiska gränsen för felrättande förmåga, och två förbättringar av avkodningsalgoritmer föreslås. I båda fallen är de föreslagna algoritmerna mer komplexa, men minskar effektförbrukningen i en implementering.

I den andra delen av avhandlingen behandlas en specifik typ av analog-tilldigital-omvandlare (ADC), som omvandlar den mottagna signalen till digital information. Sigma-delta är en typ av ADC som lämpar sig särskilt väl för integration med digitala system på en gemensam IC-krets. Nackdelen idag är dock att konverteringshastigheten är relativt låg. Ett sätt att öka hastigheten är att använda flera omvandlare parallellt, som då tar hand om delar av insignalen var för sig. Nackdelen är att sådana system ofta blir känsliga för variationer mellan de olika omvandlarna, och i den här avhandlingen föreslås en metod att modellera flera parallella sigma-delta-ADC:er för att analysera känslighetskraven. Det visar sig att vissa system är känsliga för variationer, medan andra kan kräva anpassning av begränsade delmängder av omvandlarna. Ett annat problem är att utdata från sigma-delta-omvandlare består av en dataström med mycket hög datatakt och mycket kvantiseringsbrus. För att kunna använda dataströmmen i en applikation måste den först decimeras. Avhandlingen innehåller också en metod att formulera skapandet sådana decimeringsfilter som ett optimeringsproblem, för att på så vis skapa filter med låg komplexitet.

### Acknowledgments

It is with mixed feelings I look back at the 5+ years as a PhD student at Electronics Systems. This thesis is the result of many hours of work in a competent and motivating environment, an environment promoting independence and individualism while still offering abundant support and opportunities for discussion. Being a PhD student has been hard at times, but looking back I cannot imagine conditions better suited for a researcher at the start of his career.

There are many people who have given me inspiration and support through these years, and I want to take the opportunity here to say thanks to the following people:

- My supervisor Dr. Oscar Gustafsson for being a huge source of motivation by always taking his time to discuss my work and endlessly offering new insights and ideas.

- My very good friends Dr. Fredrik Kuivinen and M.Sc. Jakob Rosén for all the fun with electronics projects and retro gaming sessions in the evenings at campus.

- Prof. Christer Svensson for getting me in contact with the STMicroelectronics research lab in Geneva.

- Dr. Andras Pozsgay at the Advanced Radio Architectures group at STMicroelectronics in Geneva, for offering me the possibility of working with "practical" research for six months during spring 2007. It has been a very valuable experience.

- All the other people in my research group at STMicroelectronics in Geneva, for making my stay there a pleasant experience.

- Prof. Fei Zesong at the Department of Electrical Engineering at Beijing Institute of Technology in China, for giving me the possibility of two three-month PhD student exchanges in spring 2009 and winter 2010/2011.

- M.Sc. Wang Hao and M.Sc. Shen Zhuzhe for helping me with all the practicalities for my visits in Beijing.

- M.Sc. Zhao Hongjie for the cooperation during his year as a PhD student exchange at Linköping University.

- All the others at the Modern Communication Lab at Beijing Institute of Technology for their kindness and support in an environment that was very different to what I am used to.

- Dr. Kent Palmkvist for help with FPGA- and VHDL-related issues.

- M.Sc. Sune Söderkvist for the big contribution to the generally happy and positive atmosphere at Electronics Systems.

- All the other present and former colleagues at Electronics Systems.

- All the colleagues at the Electronic Components research group during my time there from 2006 to 2008.

- All the colleagues at Communications Systems during my time there as a research engineer in spring 2010.

- All my friends who have made my life pleasant during my time as a PhD student.

- Last but not least, I thank my parents Maj and Bengt Blad for all their encouragement and time that they gave me as a child, which is definitely part of the reason that I have come this far in life. I also thank my sisters Lisa and Tove Blad, who I don't see very often but still feel I am very close to when I do.

Anton Blad Linköping, July 2011

# ABBREVIATIONS

| ADC    | Analog-to-Digital Converter                           |

|--------|-------------------------------------------------------|

| AWGN   | Additive White Gaussian Noise                         |

| BEC    | Binary Erasure Channel                                |

| BER    | Bit Error Rate                                        |

| BLER   | Block Error Rate                                      |

| BPSK   | Binary Phase Shift Keying                             |

| BSC    | Binary Symmetric Channel                              |

| CFU    | Check Function Unit                                   |

| CIC    | Cascaded Integrator Comb                              |

| CMOS   | Complementary Metal Oxide Semiconductor               |

| CNU    | Check Node processing Unit                            |

| CSA    | Carry-Save Adder                                      |

| CSD    | Canonic Signed-Digit                                  |

| DAC    | Digital-to-Analog Converter                           |

| DECT   | Digital Enhanced Cordless Telecommunications          |

| DFT    | Discrete Fourier Transform                            |

| DTTB   | Digital Terrestrial Television Broadcasting           |

| DVB-S2 | Digital Video Broadcasting - Satellite 2nd generation |

|        |                                                       |

| $E_b/N_0$    | Bit energy to noise spectral density (normalized SNR)   |

|--------------|---------------------------------------------------------|

| ECC          | Error Correction Coding                                 |

| ED           | Early Decision                                          |

| FIR          | Finite Impulse Response                                 |

| FPGA         | Field Programmable Gate Array                           |

| GPS          | Global Positioning Satellite                            |

| ILP          | Integer Linear Programming                              |

| $k	ext{-SE}$ | k-step enabled                                          |

| $k	ext{-SR}$ | k-step recoverable                                      |

| LAN          | Local Area Network                                      |

| LDPC         | Low-Density Parity Check                                |

| LUT          | Look-Up Table                                           |

| MPR          | McClellan-Parks-Rabiner                                 |

| MSD          | Minimum Signed-Digit                                    |

| MUX          | Multiplexer                                             |

| OSR          | Oversampling ratio                                      |

| PSD          | Power Spectral Density                                  |

| QAM          | Quadrature Amplitude Modulation                         |

| QC-LDPC      | Quasi-Cyclic Low-Density Parity-Check                   |

| QPSK         | Quadrature Phase Shift Keying                           |

| RAM          | Random Access Memory                                    |

| ROM          | Read-Only Memory                                        |

| SD           | Signed-Digit                                            |

| SNR          | Signal-to-Noise Ratio                                   |

| USB          | Universal Serial Bus                                    |

| VHDL         | VHSIC (Very High Speed Integrated Circuit) Hardware De- |

|              | scription Language                                      |

| VLSI         | Very Large Scale Integration                            |

| VMA          | Vector Merge Adder                                      |

| VNU          | Variable Node processing Unit                           |

| WLAN         | Wireless Local Area Network                             |

| WPAN         | Wireless Personal Area Network                          |

## Preface

### Thesis outline

In this thesis, contributions are made in two different areas related to the design of receivers for radio communications, and the contents are therefore separated into two parts. Part I consists of Chapters 1–6 and offers contributions in the area of low density parity check (LDPC) code decoding, whereas Part II consists of Chapters 7–13 and offers contributions related to high-speed analog-to-digital conversion using  $\Sigma\Delta$ -ADCs.

The outline of Part I is as follows. In Chapter 1, a short background, possible applications and the scientific contributions are discussed. In Chapter 2, the basics of digital communications are described and LDPC codes are introduced. Also, two decoder architectures are described, which are used as reference implementations for the contributed work. In Chapter 3, early decision decoding is proposed as a method of reducing the computational complexity of the decoding algorithm. Performance issues related to the algorithm are analyzed, and solutions are suggested. Also, an implementation of the algorithm for FPGA is described, and the resulting estimations of area and power dissipation are included. In Chapter 4, an improved algorithm for decoding of rate-compatible LDPC codes are proposed. The algorithm offers a significant reduction of the average number of iterations required for decoding of punctured codes, thereby offering a significant increase in

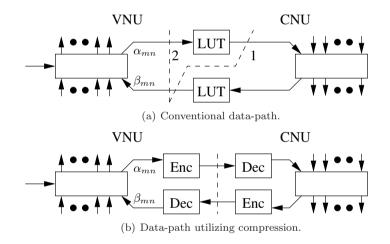

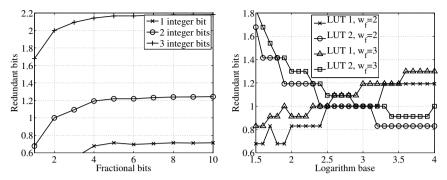

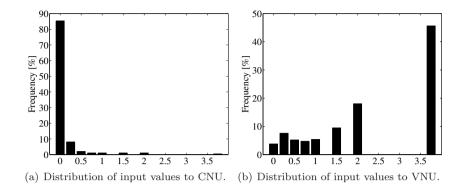

throughput. An architecture implementing the algorithm is proposed, and simulation and synthesis results are included. In Chapter 5, a minor contribution in the data representation of a sum-product LDPC decoder is explained. It is shown how redundancy in the data representation can be used to reduce the required memory used for storage of messages between iterations. Finally, in Chapter 6, conclusions are given and future work is discussed.

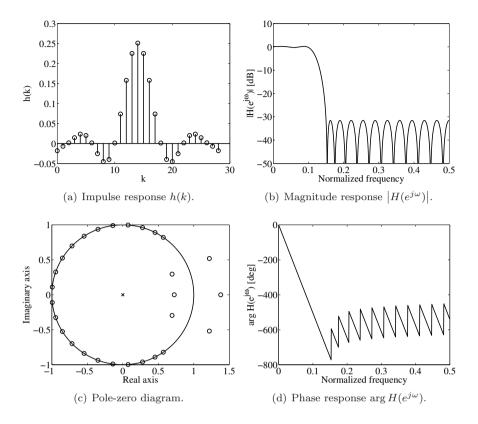

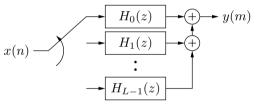

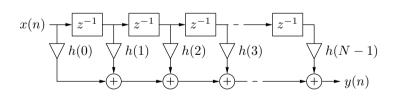

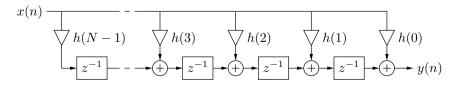

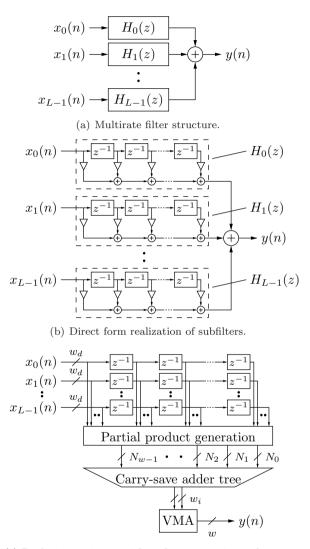

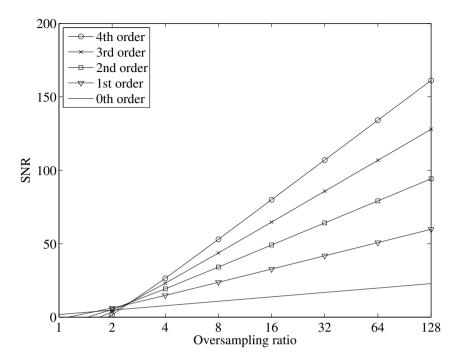

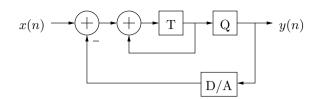

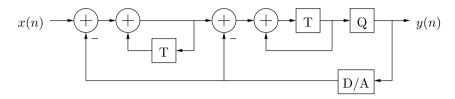

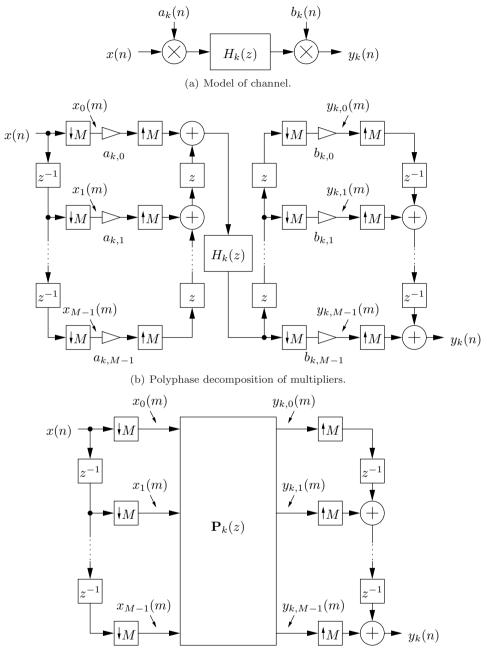

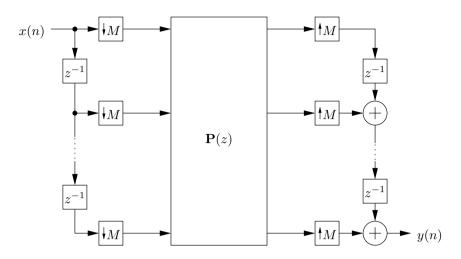

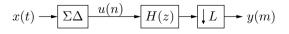

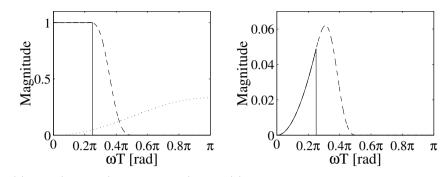

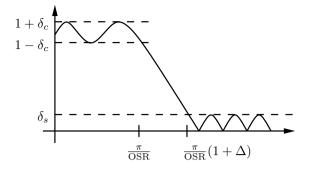

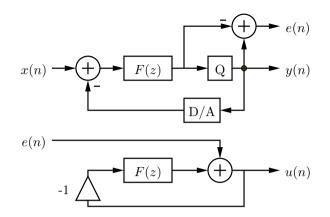

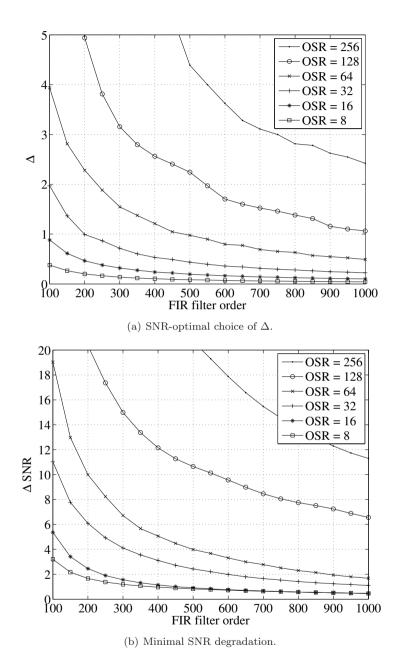

The outline of Part II is as follows. In Chapter 7, an introduction to highspeed data conversion is given, and the scientific contributions of the second part of the thesis are described. In Chapter 8, a short introduction to finite impulse response (FIR) filters, multirate theory and FIR filter architectures is given. In Chapter 9, the basics of ADCs using  $\Sigma\Delta$ -modulators are discussed, and some highspeed structures using parallel  $\Sigma\Delta$ -ADCs are shown. In Chapter 10, a general model for the analysis of matching requirements in parallel  $\Sigma\Delta$ -ADCs is proposed. It is shown that some parallel systems may become alias-free with limited matching between subsets of the channels, whereas others may require matching between all channels. In Chapter 11, a short analysis of the relations between oversampling factors,  $\Sigma\Delta$ -modulator orders, required signal-to-noise ratio (SNR) and decimation filter complexity is contributed. In Chapter 12, an integer linear programming approach to the design of high-speed decimation filters for  $\Sigma\Delta$ -ADCs is proposed. Several architectures are discussed and their complexities compared. Finally, in Chapter 13, conclusions are given and future work is discussed.

### Publications

This thesis contains research done at Electronics Systems, department of Electrical Engineering at Linköping University, Sweden. The work has been done between March 2005 and June 2011, and has resulted in the following publications [7–17]:

- 1. A. Blad, O. Gustafsson, and L. Wanhammar, "An LDPC decoding algorithm utilizing early decisions," in *Proc. National Conf. Radio Science*, Jun. 2005.

- A. Blad, O. Gustafsson, and L. Wanhammar, "An early decision decoding algorithm for LDPC codes using dynamic thresholds," in *Proc. European Conf. Circuit Theory Design*, Aug. 2005, pp. 285–288.

- A. Blad, O. Gustafsson, and L. Wanhammar, "A hybrid early decisionprobability propagation decoding algorithm for low-density parity-check codes," in *Proc. Asilomar Conf. Signals, Syst., Comp.*, Oct. 2005.

- A. Blad, O. Gustafsson, and L. Wanhammar, "Implementation aspects of an early decision decoder for LDPC codes," in *Proc. Nordic Event ASIC Design*, Nov. 2005.

- A. Blad and O. Gustafsson, "Energy-efficient data representation in LDPC decoders," *IET Electron. Lett.*, vol. 42, no. 18, pp. 1051–1052, Aug. 2006.

- A. Blad, P. Löwenborg, and H. Johansson, "Design trade-offs for linear-phase FIR decimation filters and sigma-delta modulators," in *Proc. XIV European* Signal Process. Conf., Sep. 2006.

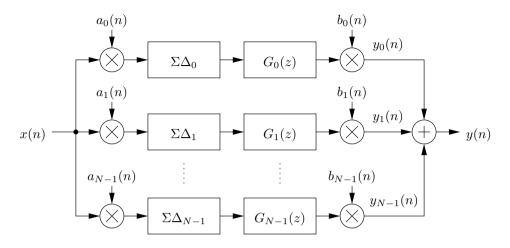

- A. Blad, H. Johansson, and P. Löwenborg, "Multirate formulation for mismatch sensitivity analysis of analog-to-digital converters that utilize parallel sigma-delta modulators," *Eurasip J. Advances Signal Process.*, vol. 2008, 2008, article ID 289184, 11 pages.

- A. Blad and O. Gustafsson, "Integer linear programming-based bit-level optimization for high-speed FIR decimation filter architectures," Springer Circuits, Syst. Signal Process. - Special Issue on Low Power Digital Filter Design Techniques and Their Applications, vol. 29, no. 1, pp. 81–101, Feb. 2010.

- A. Blad and O. Gustafsson, "Redundancy reduction for high-speed FIR filter architectures based on carry-save adder trees," in *Proc. Int. Symp. Circuits*, *Syst.*, May 2010.

- A. Blad, O. Gustafsson, M. Zheng, and Z. Fei, "Integer linear programming based optimization of puncturing sequences for quasi-cyclic low-density parity-check codes," in *Proc. Int. Symp. Turbo-Codes, Related Topics*, Sep. 2010.

- A. Blad and O. Gustafsson, "FPGA implementation of rate-compatible QC-LDPC code decoder," in *Proc. European Conf. Circuit Theory Design*, Aug. 2011.

During the period, the following papers were also published, but are either outside the scope of this thesis or overlapping with the publications above:

- A. Blad, C. Svensson, H. Johansson, and S. Andersson, "An RF sampling radio frontend based on sigma-delta conversion," in *Proc. Nordic Event ASIC Design*, Nov. 2006.

- A. Blad, H. Johansson, and P. Löwenborg, "A general formulation of analogto-digital converters using parallel sigma-delta modulators and modulation sequences," in *Proc. Asia-Pacific Conf. Circuits Syst.*, Dec. 2006, pp. 438– 441.

- A. Blad and O. Gustafsson, "Bit-level optimized high-speed architectures for decimation filter applications," in *Proc. Int. Symp. Circuits, Syst.*, May 2008.

- M. Zheng, Z. Fei, X. Chen, J. Kuang, and A. Blad, "Power efficient partial repeated cooperation scheme with regular LDPC code," in *Proc. Vehicular Tech. Conf.*, May 2010.

- O. Gustafsson, K. Amiri, D. Andersson, A. Blad, C. Bonnet, J. R. Cavallaro, J. Declerckz, A. Dejonghe, P. Eliardsson, M. Glasse, A. Hayar, L. Hollevoet,

C. Hunter, M. Joshi, F. Kaltenberger, R. Knopp, K. Le, Z. Miljanic, P. Murphy, F. Naessens, N. Nikaein, D. Nussbaum, R. Pacalet, P. Raghavan, A. Sabharwal, O. Sarode, P. Spasojevic, Y. Sun, H. M. Tullberg, T. Vander Aa, L. Van der Perre, M. Wetterwald and M. Wu, "Architecture for cognitive radio testbeds and demonstrators - An overview," in *Proc. Int. Conf. Cognitive Radio Oriented Wireless Networks Comm.*, Jun. 2010.

- A. Blad, O. Gustafsson, M. Zheng, and Z. Fei, "Rate-compatible LDPC code decoder using check-node merging," in *Proc. Asilomar Conf. Signals, Syst.*, *Comp.*, Nov. 2010.

- M. Abbas, O. Gustafsson, and A. Blad, "Low-complexity parallel evaluation of powers exploiting bit-level redundancy," in *Proc. Asilomar Conf. Signals*, *Syst.*, Comp., Nov. 2010.

# Contents

| Ι | De                      | codin   | g of low-density parity-check codes | 1             |  |  |  |

|---|-------------------------|---------|-------------------------------------|---------------|--|--|--|

| 1 |                         |         |                                     |               |  |  |  |

|   | 1.1                     |         |                                     | $\frac{3}{5}$ |  |  |  |

|   | 1.2                     |         | ations                              | -             |  |  |  |

|   | 1.3                     | Scienti | ific contributions                  | 5             |  |  |  |

| 2 | Error correction coding |         |                                     |               |  |  |  |

|   | 2.1                     | Digita  | l communications                    | 8             |  |  |  |

|   |                         | 2.1.1   | Channel models                      | 8             |  |  |  |

|   |                         | 2.1.2   | Modulation methods                  | 10            |  |  |  |

|   |                         | 2.1.3   | Uncoded communication               | 10            |  |  |  |

|   | 2.2                     | Coding  | g theory                            | 12            |  |  |  |

|   |                         | 2.2.1   | Shannon bound                       |               |  |  |  |

|   |                         | 2.2.2   | Block codes                         | 14            |  |  |  |

|   | 2.3                     | LDPC    | codes                               | 18            |  |  |  |

|   |                         | 2.3.1   | Tanner graphs                       | 18            |  |  |  |

|   |                         | 2.3.2   | Quasi-cyclic LDPC codes             | 19            |  |  |  |

|   |                         | 2.3.3   | Randomized quasi-cyclic codes       |               |  |  |  |

|   | 2.4                     | LDPC    | decoding algorithms                 |               |  |  |  |

|   |                         | 2.4.1   | Sum-product algorithm               |               |  |  |  |

|   |                         |         |                                     |               |  |  |  |

|   |     | 2.4.2  | Min-sum approximation                 | 24 |

|---|-----|--------|---------------------------------------|----|

|   | 2.5 | Rate-c | compatible LDPC codes                 | 24 |

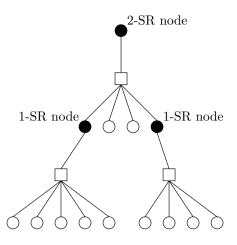

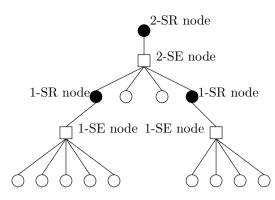

|   |     | 2.5.1  | SR-nodes                              | 25 |

|   |     | 2.5.2  | Decoding of rate-compatible codes     | 26 |

|   | 2.6 | LDPC   | decoder architectures                 | 26 |

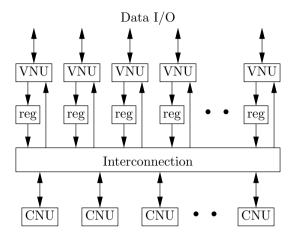

|   |     | 2.6.1  | Parallel architecture                 | 27 |

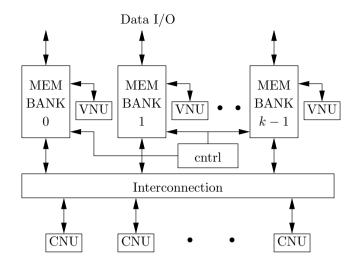

|   |     | 2.6.2  | Serial architecture                   | 28 |

|   |     | 2.6.3  | Partly parallel architecture          | 29 |

|   |     | 2.6.4  | Finite wordlength considerations      | 29 |

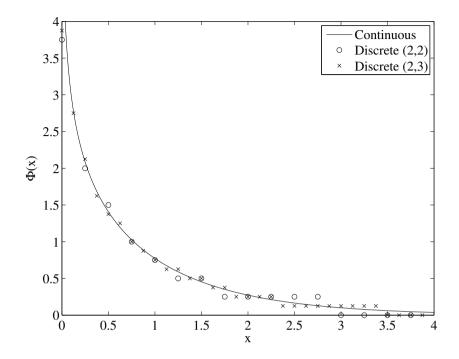

|   |     | 2.6.5  | Scaling of $\Phi(x)$                  | 30 |

|   | 2.7 | Sum-p  | roduct reference decoder architecture | 31 |

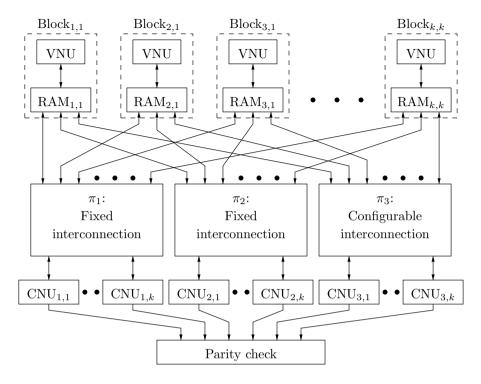

|   |     | 2.7.1  | Architecture overview                 | 32 |

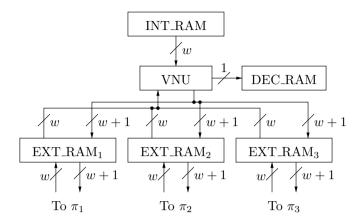

|   |     | 2.7.2  | Memory block                          | 32 |

|   |     | 2.7.3  | Variable node processing unit         | 33 |

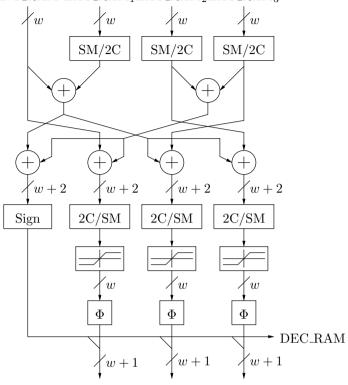

|   |     | 2.7.4  | Check node processing unit            | 34 |

|   |     | 2.7.5  | Interconnection networks              | 35 |

|   |     | 2.7.6  | Memory address generation             | 36 |

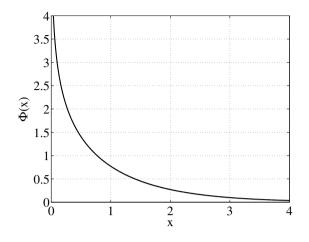

|   |     | 2.7.7  | $\Phi$ function                       | 37 |

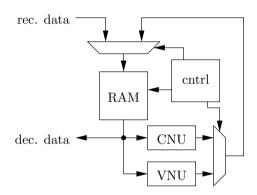

|   | 2.8 | Check  | -serial min-sum decoder architecture  | 37 |

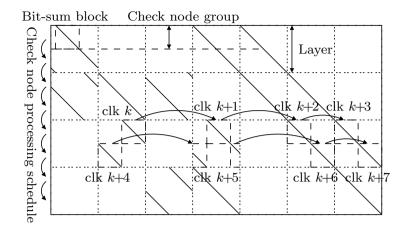

|   |     | 2.8.1  | Decoder schedule                      | 37 |

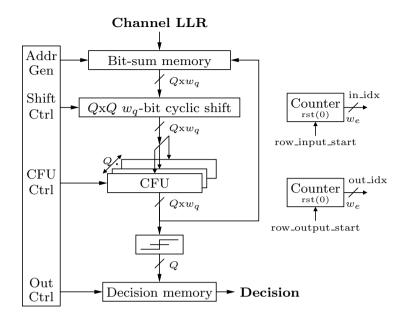

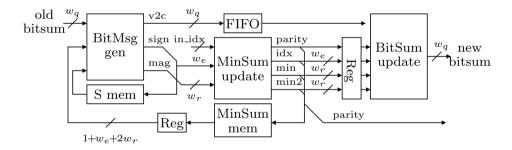

|   |     | 2.8.2  | Architecture overview                 | 38 |

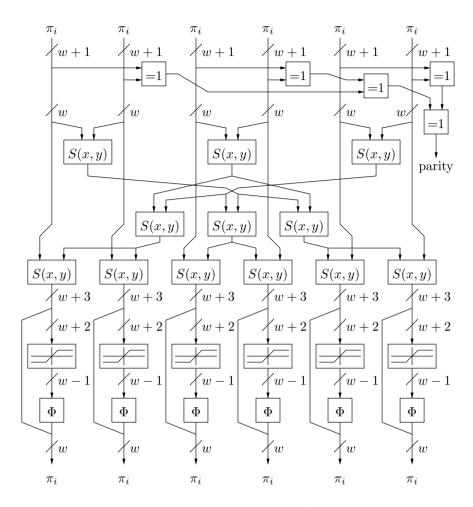

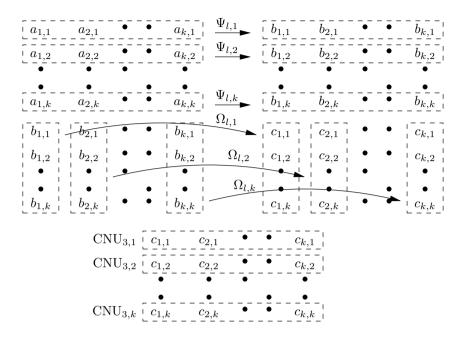

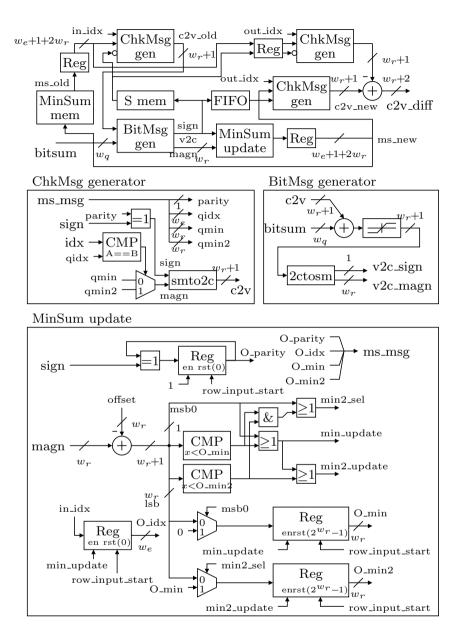

|   |     | 2.8.3  | Check node function unit              | 39 |

|   | -   |        |                                       |    |

| 3 |     |        | XISION DECODING                       | 41 |

|   | 3.1 |        | decision algorithm                    | 42 |

|   |     | 3.1.1  | Choice of threshold                   | 43 |

|   |     | 3.1.2  | Handling of decided bits              | 43 |

|   |     | 3.1.3  | Bound on error correction capability  | 44 |

|   |     | 3.1.4  | Enforcing check constraints           | 44 |

|   |     | 3.1.5  | Enforcing check approximations        | 46 |

|   | 3.2 |        | decoding                              | 47 |

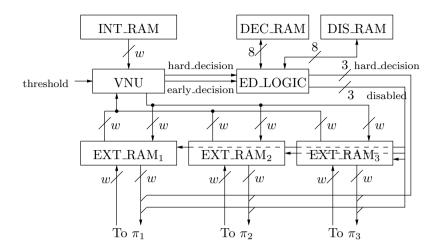

|   | 3.3 | v      | decision decoder architecture         | 47 |

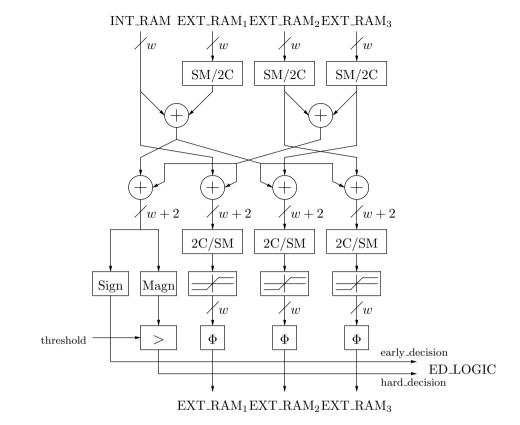

|   |     | 3.3.1  | Memory block                          | 47 |

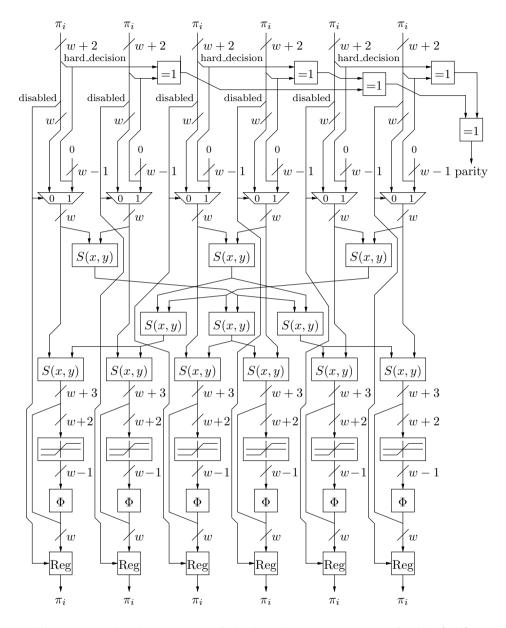

|   |     | 3.3.2  | Node processing units                 |    |

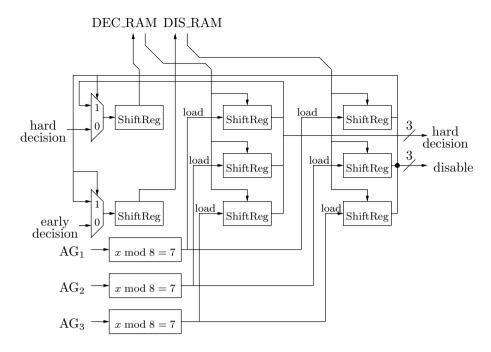

|   |     | 3.3.3  | Early decision logic                  |    |

|   |     | 3.3.4  | Enforcing check constraints           | -  |

|   | 3.4 |        | d decoder                             | 52 |

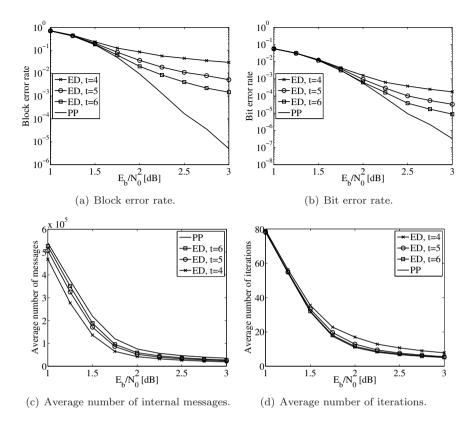

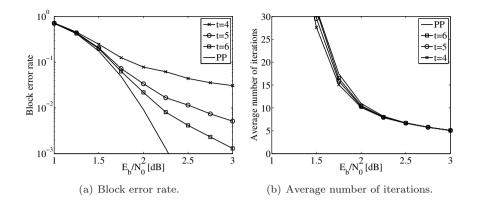

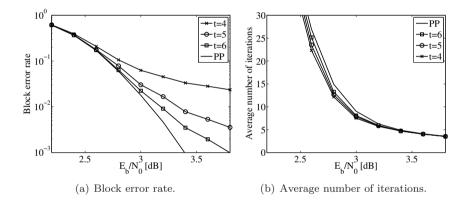

|   | 3.5 |        | ation results                         | 52 |

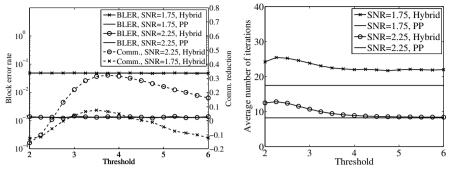

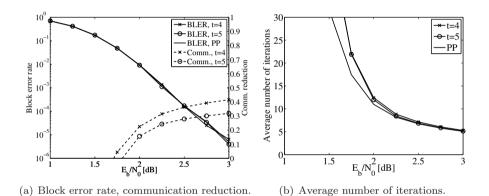

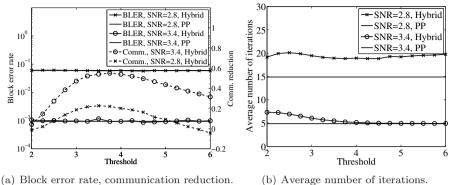

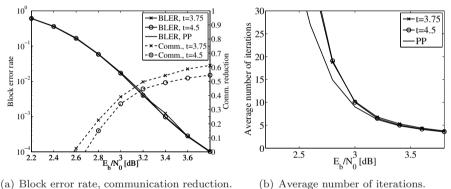

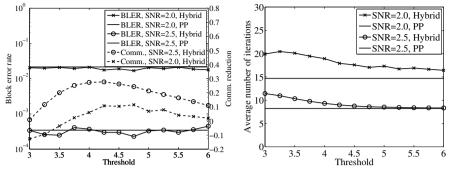

|   |     | 3.5.1  | Choice of threshold                   | 52 |

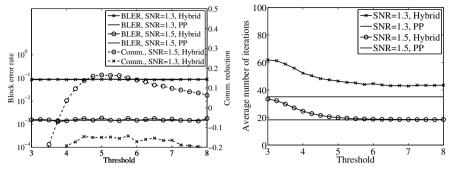

|   |     | 3.5.2  | Enforcing check constraints           | 55 |

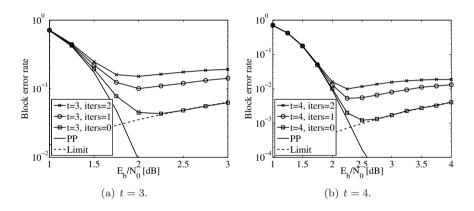

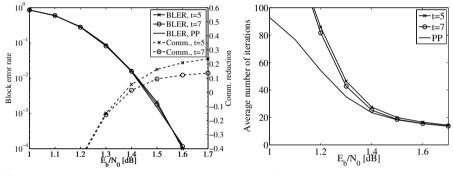

|   |     | 3.5.3  | Hybrid decoding                       | 56 |

|   |     | 3.5.4  | Fixed-point simulations               | 58 |

|   | 3.6 | Synthe | esis results                          | 61 |

| 4 | Rat                     | e-compatible LDPC codes                                      | 63        |  |  |  |  |  |

|---|-------------------------|--------------------------------------------------------------|-----------|--|--|--|--|--|

|   | 4.1                     | Design of puncturing patterns                                | 64        |  |  |  |  |  |

|   |                         | 4.1.1 Preliminaries                                          | 64        |  |  |  |  |  |

|   |                         | 4.1.2 Optimization problem                                   | 65        |  |  |  |  |  |

|   |                         | 4.1.3 Puncturing pattern design                              | 67        |  |  |  |  |  |

|   | 4.2                     |                                                              | 68        |  |  |  |  |  |

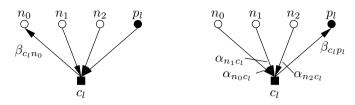

|   |                         |                                                              | 68        |  |  |  |  |  |

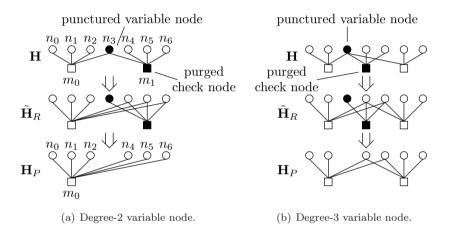

|   |                         | 4.2.2 Algorithmic properties of decoding with $\mathbf{H}_P$ | 70        |  |  |  |  |  |

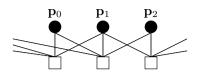

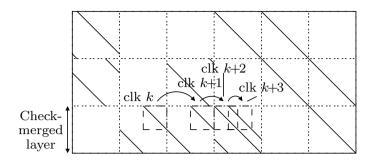

|   |                         | 4.2.3 Choosing the puncturing sequence $\mathbf{p}$          | 71        |  |  |  |  |  |

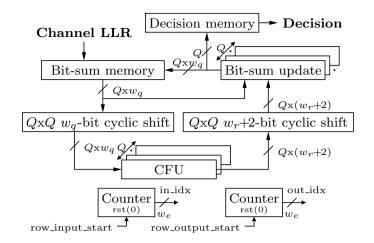

|   | 4.3                     | Rate-compatible QC-LDPC code decoder                         | 72        |  |  |  |  |  |

|   |                         |                                                              | 72        |  |  |  |  |  |

|   |                         |                                                              | 73        |  |  |  |  |  |

|   |                         | 4.3.3 Cyclic shifters                                        | 74        |  |  |  |  |  |

|   |                         |                                                              | 74        |  |  |  |  |  |

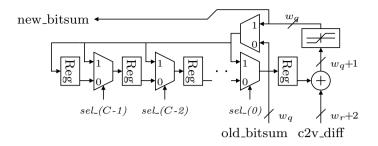

|   |                         | 4.3.5 Bit-sum update unit                                    | 76        |  |  |  |  |  |

|   |                         | 4.3.6 Memories                                               | 76        |  |  |  |  |  |

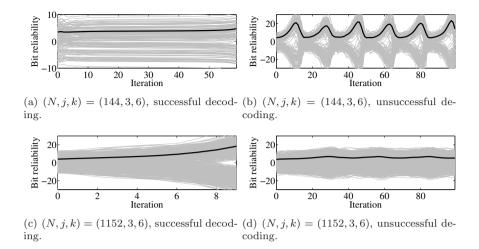

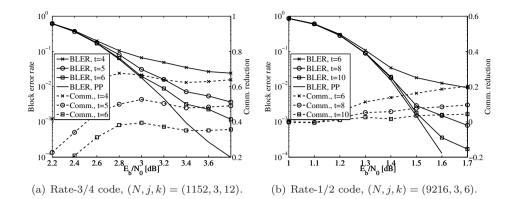

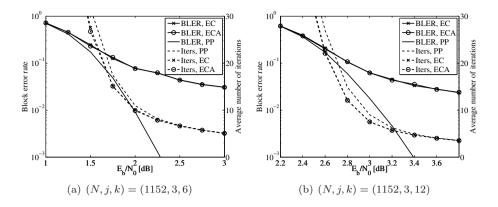

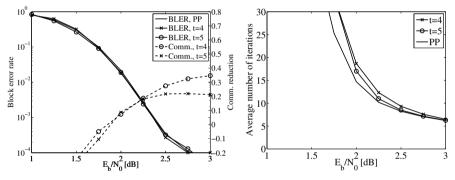

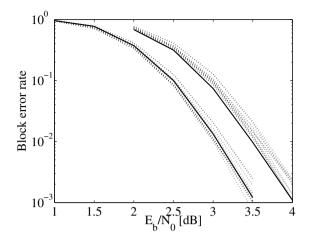

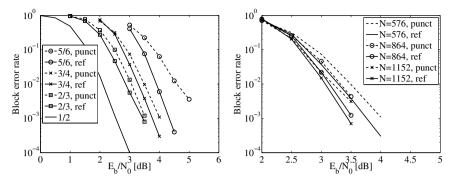

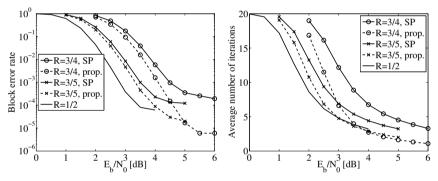

|   | 4.4                     | Simulation results                                           | 77        |  |  |  |  |  |

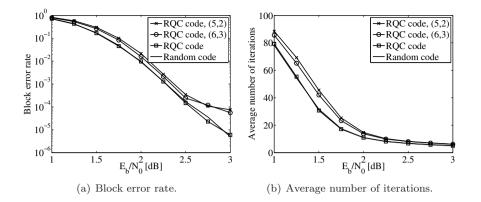

|   |                         | 4.4.1 Design of puncturing sequences                         | 77        |  |  |  |  |  |

|   |                         | 4.4.2 Check-merging decoding algorithm                       | 78        |  |  |  |  |  |

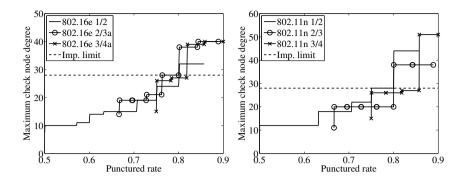

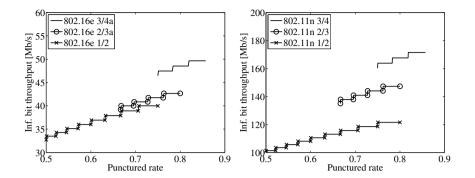

|   | 4.5                     | Synthesis results of check-merging decoder                   | 79        |  |  |  |  |  |

|   |                         | 4.5.1 Maximum check node degrees                             | 80        |  |  |  |  |  |

|   |                         |                                                              | 80        |  |  |  |  |  |

|   |                         | 4.5.3 FPGA synthesis                                         | 80        |  |  |  |  |  |

| 5 | DATA REPRESENTATIONS 83 |                                                              |           |  |  |  |  |  |

|   | 5.1                     |                                                              | 83        |  |  |  |  |  |

|   | 5.2                     |                                                              | 83        |  |  |  |  |  |

|   | 5.3                     | *                                                            | 85        |  |  |  |  |  |

| C | Car                     |                                                              | 07        |  |  |  |  |  |

| 6 |                         |                                                              | 87<br>87  |  |  |  |  |  |

|   | 6.1                     |                                                              | 87        |  |  |  |  |  |

|   | 6.2                     | Future work                                                  | 88        |  |  |  |  |  |

| п | н                       | igh-speed analog-to-digital conversion                       | <b>39</b> |  |  |  |  |  |

|   |                         |                                                              |           |  |  |  |  |  |

| 7 |                         |                                                              | 91        |  |  |  |  |  |

|   | 7.1                     | 0                                                            | 91        |  |  |  |  |  |

|   | 7.2                     | 11                                                           | 92        |  |  |  |  |  |

|   | 7.3                     | Scientific contributions                                     | 93        |  |  |  |  |  |

| 8 | FIR                     |                                                              | 95        |  |  |  |  |  |

|   | 8.1                     |                                                              | 95        |  |  |  |  |  |

|   |                         | 8.1.1 FIR filter definition                                  | 96        |  |  |  |  |  |

|   |                         |                                                              | 96        |  |  |  |  |  |

|   |                         | 8.1.3 Linear phase filters                                   | 97        |  |  |  |  |  |

|    | 8.2  | FIR fil | lter design $\ldots \ldots $                                                  |

|----|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 8.3  | Multir  | ate signal processing                                                                                                                                             |

|    |      | 8.3.1   | Sampling rate conversion                                                                                                                                          |

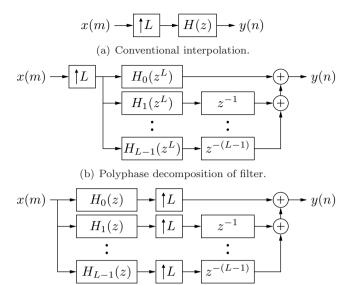

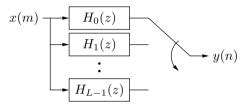

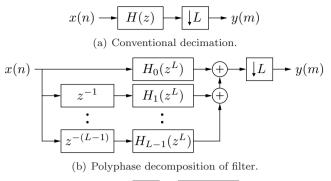

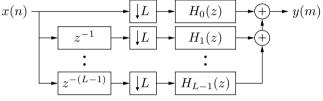

|    |      | 8.3.2   | Polyphase decomposition                                                                                                                                           |

|    |      | 8.3.3   | Multirate sampling rate conversion                                                                                                                                |

|    | 8.4  | FIR fil | ter architectures                                                                                                                                                 |

|    |      | 8.4.1   | Conventional FIR filter architectures                                                                                                                             |

|    |      | 8.4.2   | High-speed FIR filter architecture                                                                                                                                |

| 9  | SIGM | IA-DEL  | TA DATA CONVERTERS 105                                                                                                                                            |

|    | 9.1  | Sigma   | -delta data conversion                                                                                                                                            |

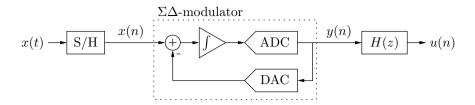

|    |      | 9.1.1   | Sigma-delta ADC overview                                                                                                                                          |

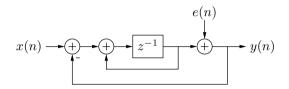

|    |      | 9.1.2   | Sigma-delta modulators                                                                                                                                            |

|    |      | 9.1.3   | Quantization noise power                                                                                                                                          |

|    |      | 9.1.4   | SNR estimation                                                                                                                                                    |

|    | 9.2  | Modul   | ator structures                                                                                                                                                   |

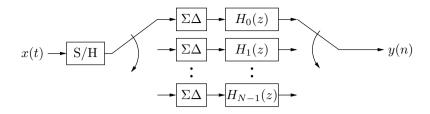

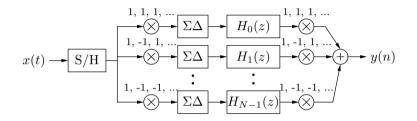

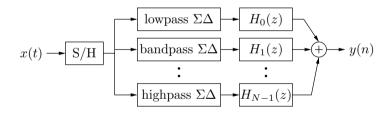

|    | 9.3  | Modul   | ated parallel sigma-delta ADCs                                                                                                                                    |

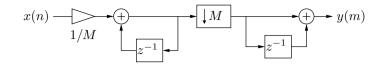

|    | 9.4  |         | $ate decimation \dots \dots$                                |

| 10 | Par  | ALLEL   | SIGMA-DELTA ADCs 115                                                                                                                                              |

|    |      |         | system model                                                                                                                                                      |

|    | -    |         | Signal transfer function                                                                                                                                          |

|    |      |         | Alias-free system                                                                                                                                                 |

|    |      |         | <i>L</i> -decimated alias-free system                                                                                                                             |

|    | 10.2 |         | wity to channel mismatches $\ldots \ldots \ldots$ |

|    | -    |         | Modulator nonidealities                                                                                                                                           |

|    |      |         | Modulation sequence errors                                                                                                                                        |

|    |      |         | Modulation sequence offset errors                                                                                                                                 |

|    |      |         | Channel offset errors                                                                                                                                             |

|    | 10.3 |         | tion results $\ldots \ldots \ldots$               |

|    |      | 10.3.1  | Time-interleaved ADC                                                                                                                                              |

|    |      |         | Hadamard-modulated ADC                                                                                                                                            |

|    |      |         | Frequency-band decomposed ADC                                                                                                                                     |

|    |      |         | Generation of new scheme                                                                                                                                          |

|    | 10.4 |         | model of system                                                                                                                                                   |

| 11 | SIGN | /A-DEL  | TA ADC DECIMATION FILTERS 135                                                                                                                                     |

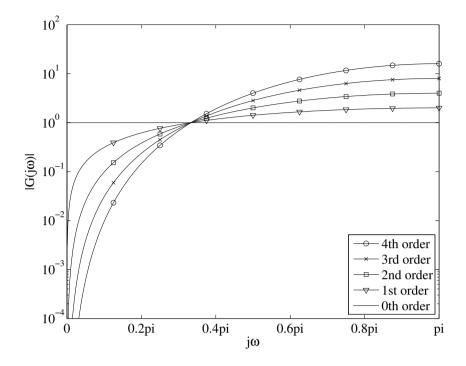

|    |      |         | $135$ considerations $\dots \dots \dots$                          |

|    |      | 0       | FIR decimation filters                                                                                                                                            |

|    |      |         | Decimation filter specification                                                                                                                                   |

|    |      |         | Signal-to-noise-ratio                                                                                                                                             |

|    | 11.2 |         | ation results                                                                                                                                                     |

| 12 |      | High-speed digital filtering |                                |     |  |  |

|----|------|------------------------------|--------------------------------|-----|--|--|

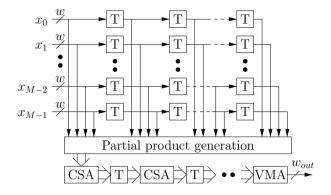

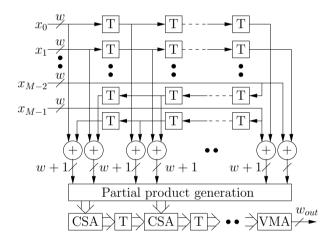

|    | 12.1 | FIR fil                      | ter realizations               | 146 |  |  |

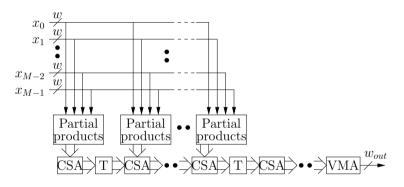

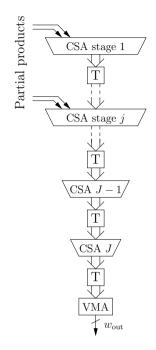

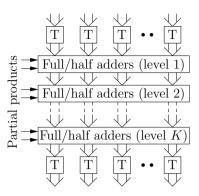

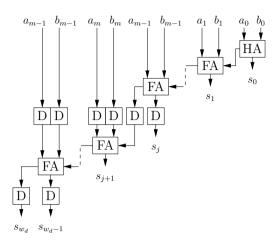

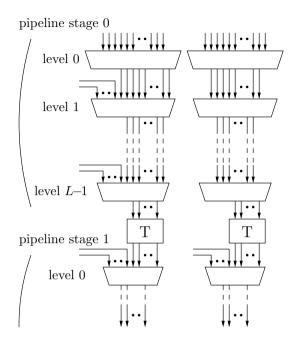

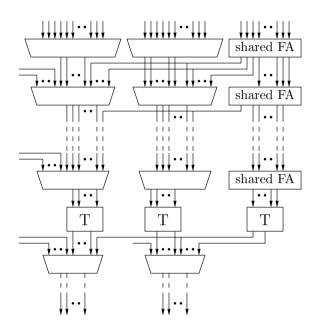

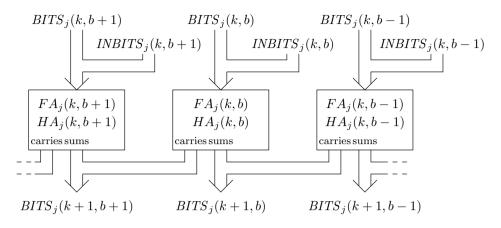

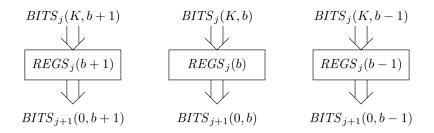

|    |      | 12.1.1                       | Architectures                  | 146 |  |  |

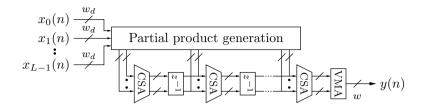

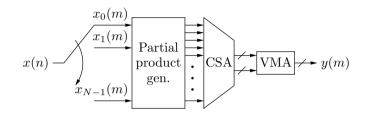

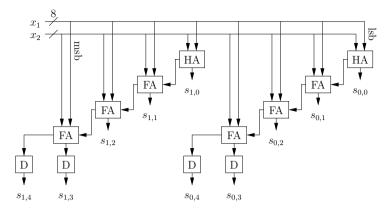

|    |      | 12.1.2                       | Partial product generation     | 150 |  |  |

|    | 12.2 | Impler                       | nentation complexity           | 152 |  |  |

|    |      |                              | Adder complexity               |     |  |  |

|    |      |                              | Register complexity            |     |  |  |

|    | 12.3 |                              | l product redundancy reduction |     |  |  |

|    |      |                              | Proposed algorithm             |     |  |  |

|    | 12.4 |                              | otimization                    |     |  |  |

|    |      |                              | ILP problem formulation        |     |  |  |

|    |      |                              | DF1 architecture               |     |  |  |

|    |      |                              | DF2 architecture               |     |  |  |

|    |      | 12.4.4                       | DF3 architecture               | 160 |  |  |

|    |      | 12.4.5                       | TF architecture                | 161 |  |  |

|    |      | 12.4.6                       | Constant term placement        | 161 |  |  |

|    | 12.5 |                              | ۔<br>S                         |     |  |  |

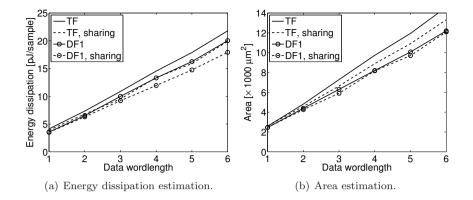

|    |      |                              | Architecture comparison        |     |  |  |

|    |      |                              | Coefficient representation     |     |  |  |

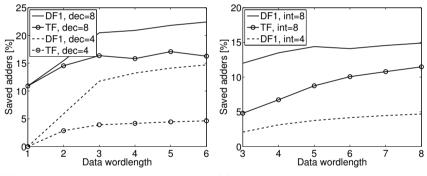

|    |      |                              | Subexpression sharing          |     |  |  |

| 13 | CON  | CUUSIO                       | NS AND FUTURE WORK             | 169 |  |  |

| 10 |      |                              | Isions                         |     |  |  |

|    |      |                              |                                |     |  |  |

|    | 10.2 | ruture                       | e work                         | T10 |  |  |

# Part I

# Decoding of low-density parity-check codes

## INTRODUCTION

### 1.1 Background

Digital communication is used ubiquitously for transferring data between electronic equipment. Examples include cable and satellite TV, mobile phone voice and data transmissions, wired and wireless LAN, GPS, computer peripheral connections through USB and IEEE1394 and many more. The basic principles of a digital communications system are known, and one of the main advantages of digital communications systems over analog is the ability to use error correction coding (ECC) for the data transmission.

ECC is used in almost all digital communications systems to improve link performance and reduce transmitter power requirements [3]. By adding redundant data to the transmitted data stream, the system allows a limited amount of transmission errors to be corrected, resulting in a reduction of the number of errors in the transmitted information. However, for the digital data symbols that are received correctly, the received information is identical to that which is sent. This can be contrasted to analog communications systems, where transmission noise will irrevocably degrade the signal quality, and the only way to ensure a predefined signal quality at the receiver is to use enough transmitter power. Thus, the metrics used to measure the transmission quality are intrinsically different for digital and analog communications, with bit error rate (BER) or block error rate (BLER) for

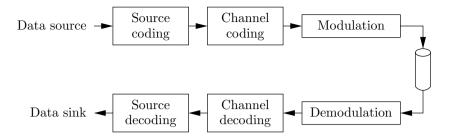

Figure 1.1 Simple communications system model

digital systems, and signal-to-noise ratio (SNR) for analog systems. Whereas analog error correction is not principally impossible, analog communications systems are different enough on a system level to make practically feasible implementations hard to envisage.

As the quality metrics of digital and analog communications systems are different, the performance of an analog and a digital system cannot easily be objectively compared with each other. However, it is often the case that a digital system with a quality subjectively comparable to that of an analog system requires significantly less power and/or bandwidth. One example is the switch from analog to digital TV, where image coding and ECC allow four standard definition channels of comparable quality in the same bandwidth as one channel in the analog TV.

A simple model of a digital communications system is shown in Fig. 1.1. The modeled system encompasses wireless and wired communications, as well as data storage, for example on optical disks and hard drives. However, the properties of the blocks are dependent on data rate, acceptable error probability, channel conditions, the nature of the data, and so on. In the communications system, data is usually first source coded (or compressed) to reduce the amount of data that needs to be transmitted, and then channel coded to add redundancy to protect against transmission errors. The modulator then converts the digital data stream into an analog waveform suitable for transmission. During transmission, the analog waveform is affected by channel noise, and thus the received signal differs to the sent. The result is that when the signal is demodulated, the digital data will contain errors. It is the purpose of the channel coder. Finally, the data stream is unpacked by the source decoder, recreating data suitable to be used by the application.

The work in this part of the thesis considers the hardware implementation of the channel decoder for low-density parity-check (LDPC) codes. The decoding of LDPC codes is complex, and is often a major part of the baseband processing of a receiver. For example, the flexible decoder in [79] supports the LDPC codes in IEEE 802.11n and IEEE 802.16e, as well as the Turbo codes in 3GPP-LTE, but at a maximum power dissipation of 675 mW. The need for low-power components is obviously high in battery-driven applications like hand helds and mobile phones, but becomes increasingly important also in stationary equipment like computers,

5

computer peripherals and TV receivers, due to the need of removing the waste heat produced. Thus the focus of this work is on reducing the power dissipation of LDPC decoders, without sacrificing the error-correction performance.

LDPC codes were discovered originally in 1962 by Robert Gallager [39]. He showed that the class of codes has excellent theoretical properties and he also provided a decoding algorithm. However, as the hardware of the time was not powerful enough to run the decoding algorithm efficiently, LDPC codes were not practically usable and were forgotten. They were rediscovered in 1995 [74,101], and have been shown to have a very good performance close to the theoretical Shannon limit [73,75]. Since the rediscovery, LDPC codes have been successfully used in a number of applications, and are suggested for use in a number of important future communications standards.

### **1.2** Applications

Today, LDPC codes are used or are proposed to be used in a number of applications with widely different characteristics and requirements. In 2003, a type of LDPC codes was accepted to be used for the DVB-S2 standard for satellite TV [113]. The same type of code was then adopted for both the DVB-T2 [114] and DVB-C2 [115] standards for terrestial and cable-based TV, respectively. A similar type has also been accepted for the DTTB standard for digital TV in China [122]. The system-level requirements of these systems are relatively low, with relaxed latency requirements as the communication is unidirectional, and relatively small constraints on power dissipation, as the user equipment is typically not battery-driven. Thus, the adopted code is complex with a resulting complex decoder implementation.

Opposite requirements apply for the WLAN IEEE 802.11n [118] and WiMax IEEE 802.16e [120] standards, for which LDPC codes have been chosen as optional ECC schemes. In these applications, communication is typically bi-directional, necessitating low latency. Also, the user equipment is typically battery-driven, making low power dissipation critical. For these applications, the code length is restricted directly by the latency requirements. However, it is preferable to reduce the decoder complexity as much as possible to save power dissipation.

Whereas these types of applications are seen as the primary motivation for the work in this part of the thesis, LDPC codes are also used or suggested in several other standards and applications. Among them are the IEEE 802.3an [121] standard for 10Gbit/s Ethernet, the IEEE 802.15.3c [119] mm-wave WPAN standard, and the gsfc-std-9100 [116] standard for deep-space communications.

### **1.3** Scientific contributions

There are two main scientific contribution in the first part of the thesis. The first is a modification to the sum-product decoding algorithm for LDPC codes, called the early-decision algorithm, and is described in Chapter 3. The aim of the early-decision modification is to dynamically reduce the number of possible states of the decoder during decoding, and thereby reduce the amount of internal communication of the hardware. However, this algorithm modification impacts the error correction performance of the code, and it is therefore also investigated how the modified decoding algorithm can be efficiently combined with the original algorithm to yield a resulting hybrid decoder which retains the performance of the original algorithm while still offering a reduction of internal communication.

The second main contribution is an improved algorithm for decoding of ratecompatible LDPC codes, and is described in Chapter 4. Using rate-compatible LDPC codes obtained through puncturing, the higher-rate codes can trivially be decoded by the low-rate mother code. However, by defining a specific code by merging relevant check nodes for each of the punctured rates, the code complexity can be reduced at the same time as the propagation speed of the extrinsic information is increased. The result is a significant reduction in the convergence time of the decoding algorithm for the higher-rate codes.

A minor contribution is the observation of redundancy in the internal data format in a fixed-width implementation of the decoding algorithm. It is shown that a simple data encoding can further reduce the amount of internal communication.

The performance of the proposed algorithms have been evaluated in software. For the early-decision algorithm, it is verified that the modifications have an insignificant impact on the error correction performance, and the change in the internal communication is estimated. For the check-merging decoding algorithm, the modifications can be shown to even improve the error correction performance. However, these improvements are mostly due to the reduced convergence time, allowing the algorithm to converge for codewords which the original algorithm does not have sufficient time for.

The early-decision and check-merging algorithms have been implemented in a Xilinx Virtex 5 FPGA and an Altera Cyclone II FPGA, respectively. As similar implementations have not been published before, they have mainly been compared with implementations of the original reference decoders. For the early-decision decoder, the required overhead has been determined, and the power dissipation of both the original and proposed architecture have been simulated and compared using regular quasi-cyclic LDPC codes with an additional scrambling layer. For the check-merging decoder, the required overhead has been determined, and the increased throughput obtainable with the modification has been quantized for two different implementations geared for the IEEE 802.16e and IEEE 802.11n standards, respectively.

## ERROR CORRECTION CODING

In this chapter, the basics of digital communications systems and error correction coding are explained. In Sec. 2.1, a model of a system using digital communications is shown, and the channel model and different modulation methods are explained. In Sec. 2.2, coding theory is introduced as a way of reducing the required transmission power with a retained bit error probability, and block codes are defined. In Sec. 2.3, LDPC codes are defined as a special case of general block codes, and Tanner graphs are introduced as a way of visualizing the structure of an LDPC code. The sum-product decoding algorithm and the min-sum approximation are discussed in Sec. 2.4, and in Sec. 2.5, rate-compatible LDPC codes are introduced as a way of obtaining practical usable codes with a wide range of rates. Also, the implications of rate-compatibility on the decoding algorithm are discussed. In Sec. 2.6, several general decoder architectures with different parallelism degrees are discussed, including a serial architecture, a parallel architecture, and a partly parallel architecture. In Sec. 2.7, a partly parallel architecture for a specific class of regular LDPC codes is described, and is also used as a reference for the early decision algorithm proposed in Chapter 3. In Sec. 2.8, a partly parallel architecture using the min-sum decoding algorithm for general quasi-cyclic LDPC codes is described, and is used as a reference for the check merging decoding algorithm proposed in Chapter 4.

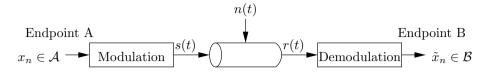

Figure 2.1 Digital communications system model.

### 2.1 Digital communications

Consider a two-user digital communications system, such as the one shown in Fig. 2.1, where an endpoint A transmits information to an endpoint B. Whereas multi-user communications systems with multiple transmitting and receiving endpoints can be defined, only systems with one transmitter and receiver will be considered in this thesis. The system is digital, meaning that the information is represented by a sequence of symbols  $x_n$  from a finite discrete alphabet  $\mathcal{A}$ . The sequence is mapped onto an analog signal s(t) which is transmitted to the receiver through the air, through a cable, or using any other medium. During transmission, the signal is distorted by noise n(t), and thus the received signal r(t) is not equal to the transmitted signal. By the demodulator, the received signal r(t) is mapped to symbols  $\tilde{x}_n$  from an alphabet  $\mathcal{B}$ , which may or may not be the same as alphabet  $\mathcal{A}$ , and may be either discrete or continuous. Typically, if the output data stream is used directly by the receiving application,  $\mathcal{B} = \mathcal{A}$ . However, commonly some form of error coding is employed, which can benefit from including symbol reliability information in the receiving alphabet  $\mathcal{B}$ .

#### 2.1.1 Channel models

In analyzing the performance of a digital communications system, the chain in Fig. 2.1 is modeled as a probabilistic mapping  $P(\tilde{X} = b \mid X = a), \forall a \in \mathcal{A}, b \in \mathcal{B}$ , from the transmission alphabet  $\mathcal{A}$  to the reception alphabet  $\mathcal{B}$ . The system modeled by the probabilistic mapping is formally called a channel, and X and  $\tilde{X}$  are stochastic variables denoting the input and output of the channel, respectively. For the channel, the following requirement must be satisfied for discrete reception alphabets

$$\sum_{b \in \mathcal{B}} P(\tilde{X} = b \mid X = a) = 1, \forall a \in \mathcal{A},$$

(2.1)

or analogously for continuous reception alphabets

$$\int_{b\in\mathcal{B}} P(\tilde{X}=b \mid X=a) = 1, \forall a \in \mathcal{A}.$$

(2.2)

Depending on the characteristics of the modulator, demodulator, transmission medium, and the accuracy requirement of the model, different channel models are suitable. Some common channel models include • the binary symmetric channel (BSC), a discrete channel defined by the alphabets  $\mathcal{A} = \mathcal{B} = \{0, 1\}$ , and the mapping

$$P(\tilde{X} = 0 \mid X = 0) = P(\tilde{X} = 1 \mid X = 1) = 1 - p$$

$$P(\tilde{X} = 1 \mid X = 0) = P(\tilde{X} = 0 \mid X = 1) = p,$$

where p is the cross-over probability that the sent binary symbol will be received in error. The BSC is an adequate channel model in many cases when a hard-decision demodulator is used, as well as in early stages of a system design to compute the approximate performance of a digital communications system.

• the binary erasure channel (BEC), a discrete channel defined by the alphabets  $\mathcal{A} = \{0, 1\}, \mathcal{B} = \{0, 1, e\}$ , and the mapping

$$P(\tilde{X} = 0 \mid X = 0) = P(\tilde{X} = 1 \mid X = 1) = 1 - p$$

$$P(\tilde{X} = e \mid X = 0) = P(\tilde{X} = e \mid X = 1) = p$$

$$P(\tilde{X} = 1 \mid X = 0) = P(\tilde{X} = 0 \mid X = 1) = 0,$$

where p is the erasure probability, i.e., the received symbols are either known by the receiver, or known that they are unknown. The binary erasure channel is commonly used in theoretical estimations of the performance of a digital communications system due to its simplicity, but can also be adequately used in low-noise system modeling.

• the additive white Gaussian noise (AWGN) channel with noise spectral density  $N_0$ , a continuous channel defined by a discrete alphabet  $\mathcal{A}$  and a continuous alphabet  $\mathcal{B}$ , and the mapping

$$P(X = b \mid X = a) = f_{(a,\sigma)}(b),$$

(2.3)

where  $f_{(a,\sigma)}(b)$  is the probability density function for a normally distributed stochastic variable with mean *a* and standard deviation  $\sigma = \sqrt{N_0/2}$ . The size of the input alphabet is usually determined by the modulation method used, and is further explained in Sec. 2.1.2. The AWGN channel models real-world noise sources well, especially for cable-based communications systems.

• the Rayleigh and Rician fading channels. The Rayleigh channel is appropriate for modeling a wireless communications system when no line-of-sight is present between the transmitter and receiver, such as cellular phone networks and metropolitan area networks. The Rician channel is more appropriate when a dominating line-of-sight communications path is available, such as for wireless LANs and personal area networks.

The work in this thesis considers the AWGN channel with a binary input alphabet only.

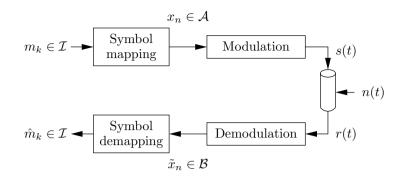

Figure 2.2 Model of uncoded digital communications system.

#### 2.1.2 Modulation methods

The size of the transmission alphabet  $\mathcal{A}$  for the AWGN channel is commonly determined by the modulation method used. Common modulation methods include

- the binary phase-shift keying (BPSK) modulation, using the transmission alphabet  $\mathcal{A} = \{-\sqrt{E}, +\sqrt{E}\}$  and reception alphabet  $\mathcal{B} = \mathbb{R}$ . *E* denotes the symbol energy.

- the quadrature phase-shift keying (QPSK) modulation, using the transmission alphabet  $\mathcal{A} = \sqrt{E/2}\{(-1-i), (-1+i), (+1-i), (+1+i)\}$  with complex symbols, and reception alphabet  $\mathcal{B} = \mathbb{C}$ . The binary source information is mapped in blocks of two bits onto the symbols of the transmission alphabet. As the alphabets are complex, the probability density function in (2.3) is the probability density function for the two-dimensional Gaussian distribution.

- the quadrature amplitude (QAM) modulation, which is a generalization of the QPSK modulation to higher orders, using equi-spaced symbols from the complex plane.

In this thesis, BPSK modulation has been assumed exclusively. However, the methods are not limited to BPSK modulation, but may straight-forwardly be applied to systems using other modulation methods as well.

#### 2.1.3 Uncoded communication

In order to use the channel for communication of data, some way of mapping the binary source information to the transmitted symbols is needed. In the system using uncoded communications depicted in Fig. 2.2, this is done by the symbol mapper, which maps the source bits  $m_k$  to the transmitted symbols  $x_n$ . The transmitted symbols may be produced at a different rate than the source bits are consumed.

On the receiver side, the end application is interested in the most likely symbols that were sent, and not the received symbols. However, the transmitted and received data are symbols from different alphabets, and thus a symbol demapper is used to infer the most likely transmitted symbols from the received ones, before mapping them back to the binary information stream  $\hat{m}_k$ . In the uncoded case, this is done on a per-symbol basis.

For the BSC, the source bits are mapped directly to the transmitted symbols such that  $x_n = m_k$ , where n = k, whereas the BEC is not used with uncoded communications and is thus not discussed. For the AWGN with BPSK modulation, the source bits are conventionally mapped so that the bit 0 is mapped to the symbol  $+\sqrt{E}$ , whereas the bit 1 is mapped to the symbol  $-\sqrt{E}$ . For higher-order modulation, several source bits are mapped to each symbol, and the source bits are typically mapped using gray mapping so that symbols that are close in the complex plane differ by one bit. The optimal decision rules for the symbol demapper can be formulated as follows for different channels.

For the BSC,

$$\hat{m}_k = \begin{cases} \tilde{x}_n & \text{if } p < 0.5\\ 1 - \tilde{x}_n & \text{if } p > 0.5, \end{cases}$$

(2.4)

where the case p > 0.5 is rather unlikely. For the AWGN channel using BPSK modulation,

$$\hat{m}_{k} = \begin{cases} 0 & \text{if } \tilde{x}_{n} > 0 \\ 1 & \text{if } \tilde{x}_{n} < 0. \end{cases}$$

(2.5)

Finally, if QPSK modulation with gray mapping of source bits to transmitted symbols is used,

$$\{\hat{m}_k, \hat{m}_{k+1}\} = \begin{cases} 00 & \text{if } \operatorname{Re} \tilde{x}_n > 0, \operatorname{Im} \tilde{x}_n > 0\\ 01 & \text{if } \operatorname{Re} \tilde{x}_n < 0, \operatorname{Im} \tilde{x}_n > 0\\ 11 & \text{if } \operatorname{Re} \tilde{x}_n < 0, \operatorname{Im} \tilde{x}_n < 0\\ 10 & \text{if } \operatorname{Re} \tilde{x}_n > 0, \operatorname{Im} \tilde{x}_n < 0. \end{cases}$$

(2.6)

In analyzing the performance of a communications system, the probability of erroneous transmissions is interesting. For BPSK communications with equal symbol probabilities, the bit error probability can be defined as

$$P_{B,BPSK} = P(\hat{m}_k \neq m_k) =$$

$$= P(\tilde{x}_n > 0 \mid x_n = 1)P(x_n = 1) + P(\tilde{x}_n < 0 \mid x_0 = 0)P(x_n = 0) =$$

$$= Q\left(\frac{\sqrt{E}}{\sigma}\right) = Q\left(\sqrt{\frac{2E}{N_0}}\right),$$

(2.7)

where Q(x) is the cumulative density function for normally distributed stochastic variables. However, it turns out that significantly lower error probabilities can be achieved by adding redundancy to the transmitted information, while keeping

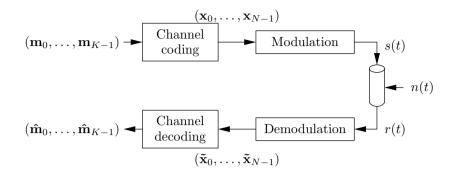

Figure 2.3 Error correction system overview

the total transmitter power unchanged. Thus, the individual symbol energies are reduced, and the saved energy is used to transmit redundant symbols computed from the information symbols according to some well-defined code.

### 2.2 Coding theory

Consider the error correction system in Fig. 2.3. As the codes in this thesis are block codes, the properties of the system are formulated assuming that a block code is used. Also, it is assumed that the symbols used for the messages are binary symbols. A message **m** with K bits is to be communicated over a noisy channel. The message is encoded to the codeword **x** with N bits, where N > K. The codeword is then modulated to the analog signal s(t) using BPSK modulation with an energy of E per bit. During transmission over the AWGN channel, the noise signal n(t) with a one-sided spectral density of  $N_0$  is added to the signal to produce the received signal r(t). The received signal is demodulated to produce the received vector  $\tilde{\mathbf{x}}$ , which may contain either bits or scalars. The channel decoder is then used to find the most likely sent codeword  $\hat{\mathbf{x}}$ , given the received vector  $\tilde{\mathbf{x}}$ . From  $\hat{\mathbf{x}}$ , the message bits  $\hat{\mathbf{m}}$  are then extracted.

For the system, a number of properties can be defined:

- The **information** transmitted is K bits.

- The **block size** of the code is N bits. Generally, in order to achieve better error correction performance, N must be increased. However, a larger block size requires a more complex encoder/decoder and increases the latency of the system, and there is therefore a trade-off between these factors in the design of the coding system.

- The code rate is R = K/N. Obviously, increasing the code rate increases the amount of information transmitted for a fixed block size N. However, it is also the case that a reduced code rate allows more information to be

Figure 2.4 Capacity for binary-input AWGN channel using different SNR.

transmitted for a constant transmitter power level (see Sec. 2.2.1), and the code rate is therefore also a trade-off between error correction performance and encoder/decoder complexity.

- The normalized SNR at the receiver is  $E_b/N_0 = ER/N_0$  and is used instead of the actual SNR  $E/N_0$  in order to allow a fair comparison between codes of different rates. The normalized SNR is denoted SNR in the rest of this thesis.

- The bit error rate (BER) is the fraction of differing bits in  $\mathbf{m}$  and  $\hat{\mathbf{m}}$ , averaged over several blocks.

- The **block error rate** (BLER) is the fraction of blocks where  $\mathbf{m}$  and  $\hat{\mathbf{m}}$  differs.

Coding systems are analyzed in depth in any introductionary book on coding theory, e.g. [3,102].

#### 2.2.1 Shannon bound

In 1948, Claude E. Shannon proved the noisy channel coding theorem [89], that can be phrased in the following way.

For each channel, as defined in Sec. 2.1.1, there is associated a quantity called the channel capacity. The channel capacity is the maximum amount of information, as measured by the shannon unit, that can be transferred per channel use, guaranteeing error-free transmission. Moreover, error-free transmission at information rates above the channel capacity is not possible.

Thus, transmitting information at a rate below the channel capacity allows an arbitrarily low error rate, i.e., there are arbitrarily good error-correcting codes. Additionally, the noisy channel coding theorem states that above the channel capacity, data transmission can not be done without errors, regardless of the code used.

The capacity for the AWGN channel using BPSK modulation and assuming equi-probable inputs is given here without derivation, but calculations are found e.g. in [3]. It is

$$C_{BIAWGN} = \int_{-\infty}^{\infty} f_{\sqrt{2E/N_0}}(y) \log_2\left(\frac{2f_{\sqrt{2E/N_0}}(y)}{f_{\sqrt{2E/N_0}}(y) + f_{-\sqrt{2E/N_0}}(y)}\right) \mathrm{d}y, \quad (2.8)$$

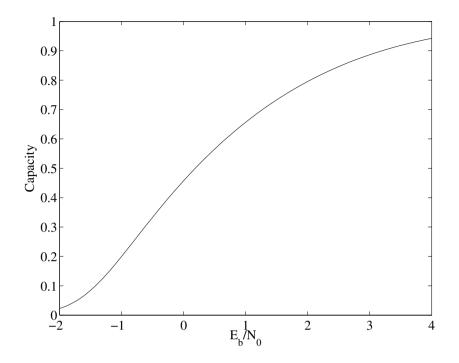

where  $f_{\pm\sqrt{2E/N_0}}(y)$  are the probability density functions for Gaussian stochastic variables with means  $\pm\sqrt{E}$  and standard deviation  $\sqrt{N_0/2}$ . In Fig. 2.4 the capacity of a binary-input AWGN channel is plotted as a function of the normalized SNR  $E_b/N_0 = ER/N_0$ , and it can be seen that reducing the code rate allows error-free communications using less energy even if more bits are sent for each information bit.

Shannon's theorem can be rephrased in the following way: for each information rate (or code rate) there is a limit on the channel conditions, above which communication can achieve an arbitrarily low error rate, and below which communication must introduce errors. This limit is commonly referred to as the Shannon limit, and is commonly plotted in code performance plots to show how far the code is from the theoretical limit. The Shannon limit can be found numerically for the binary input AWGN channel by iteratively solving (2.8) for the argument  $\sqrt{E/N_0}$  that yields the desired information rate.

#### 2.2.2 Block codes

There are two standard ways of defining block codes: through a generator matrix G or through a parity-check matrix H. For a message length of K bits and block length of N bits, G has dimensions of  $K \times N$ , and H has dimensions of  $M \times N$ , where M = N - K. Denoting the set of codewords by C, C can be defined in the

following two ways:

$$C = \left\{ \mathbf{x} = \mathbf{mG} \,|\, \mathbf{m} \in \{0, 1\}^K \right\}$$

(2.9)

$$C = \left\{ \mathbf{x} \in \{0, 1\}^N \, | \, \mathbf{H} \mathbf{x}^T = \mathbf{0} \right\}$$

(2.10)

The most important property of a code regarding performance is the minimum Hamming distance d, which is the minimum number of bits that two codewords may differ in. Moreover, as the set of codewords C is linear, it is also the weight of the lowest-weight codeword which is not the all-zero codeword. The minimum distance is important because all transmission errors with a weight strictly less than d/2 can be corrected. However, for practical codes d is often not known exactly, as it is often difficult to calculate theoretically, and exhaustive searches are not realistic with block sizes of thousands of bits. Also, depending on the type of decoder used, the actual error-correcting ability may be both above and below d/2. Thus the performance of modern codes is usually determined experimentally by simulations over a noisy channel and by measuring the actual bit- or block-error rate at the output of the decoder.

A simple example of a block code is the (N, K, d) = (7, 4, 3) Hamming code defined by the parity-check matrix

$$H = \begin{pmatrix} 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \end{pmatrix}.$$

(2.11)

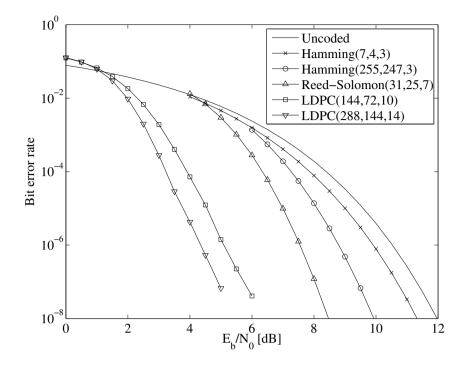

The code has a block length of N = 7 bits, and a message length of K = 4 bits. Thus the code rate is R = K/N = 4/7. It can easily be shown that the minimumweight codeword has a weight of d = 3, which is therefore the minimum distance of the code. The error correcting performance of this code over the AWGN channel is shown in Fig. 2.5. As can be seen, the code performance is just somewhat better than uncoded transmission. There exists a Hamming code with parameters  $(N, K, d) = (2^m - 1, 2^m - m - 1, 3)$  for every integer  $m \ge 2$ , and their paritycheck matrices are constructed by concatenating every nonzero *m*-bit vector. The advantage of these codes is that decoding is very simple, and they are used e.g. in memory chips.

To decode a received block using Hamming coding, consider for example the (7, 4, 3) Hamming code and a received vector  $\tilde{\mathbf{x}}$ . Then the syndrome of the received vector is  $\mathbf{H}\tilde{\mathbf{x}}^T$ , which is a three-bit vector. If the syndrome is zero, the received vector is a valid codeword, and decoding is finished. If the syndrome is non-zero, the received vector could become a codeword if the bit corresponding to the column in  $\mathbf{H}$  that matched the syndrome is flipped. It should thus be noted that the columns of  $\mathbf{H}$  contain every non-zero three-bit vector, and thus every received vector  $\tilde{\mathbf{x}}$  will be at a distance of at most one from a valid codeword. Thus decoding will consist of changing at most one bit, determined by the syndrome if it is non-zero.

To increase the error correcting performance, the code needs to be able to correct more than single bit errors, and then the above decoding technique does not work. While the method could be generalized to determine the bits to flip by

Figure 2.5 Error correcting performance of short codes. The Hamming and Reed-Solomon curves are estimations for hard-decision decoding, whereas the LDPC curves are obtained using simulations with soft-decision decoding.

finding the minimum set of columns whose sum is the syndrome, this is usually not efficient. Thus the syndrome is usually computed only to determine if a given vector is a codeword or not.

The performance of other short codes are also shown in Fig. 2.5. The Hamming and Reed-Solomon curves are estimations for hard-decision decoding obtained using the MATLAB<sup>TM</sup> function **bercoding**. The LDPC codes are randomly constructed (3, 6)-regular codes (as defined in Sec. 2.3). Ensembles of 100 codes were generated, and their minimum distances computed using integer linear programming optimization. Among the codes with the largest minimum distances, the codes with the best performance under the sum-product algorithm were selected.

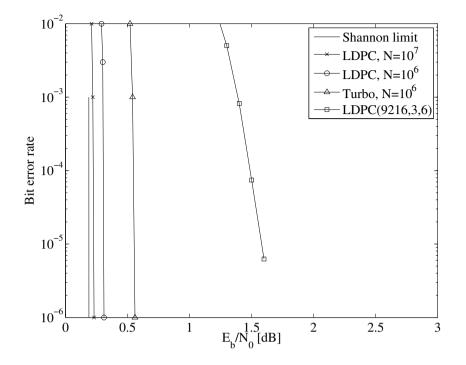

The performance of some long codes are shown in Fig. 2.6. The performance of the  $N = 10^7$  LDPC code is from [26], whereas the performance of the  $N = 10^6$ codes are from [86]. It is seen that at a block length of  $10^6$  bits, the LDPC code performs better than the Turbo code. The  $N = 10^7$  code is a highly optimized irregular LDPC code with variable node degrees up to 200, and performs within 0.04 dB of the Shannon limit at a bit error rate of  $10^{-6}$ . At shorter block lengths

Figure 2.6 Error correcting performance of long codes.

of 1000-10000 bits, the performance of Turbo codes and LDPC codes are generally comparable. The (9216, 3, 6) code is a randomly constructed regular code, also used in the simulations in Sec. 3.5.

For block codes, there are three general ways in which a decoding attempt may terminate:

- **Decoder successful:** The decoder has found a valid codeword, and the corresponding message  $\hat{\mathbf{m}}$  equals  $\mathbf{m}$ .

- **Decoder error:** The decoder has found a valid codeword, and the corresponding message  $\hat{\mathbf{m}}$  differs from  $\mathbf{m}$ .

- **Decoder failure:** The decoder was unable to find a valid codeword using the resources specified.

For both the error and the failure result, the decoder has been unable to find the correct sent message **m**. However, the key difference is that decoder failures are detectable, whereas decoder errors are not. Thus, if, for example, several decoder algorithms are available, the decoding could be retried with another algorithm when a decoder failure occurs.

Figure 2.7 Example of Tanner graph for the (7,4,3) Hamming code.

|             |       | Variable nodes |       |       |       |       |       |       |  |

|-------------|-------|----------------|-------|-------|-------|-------|-------|-------|--|

|             |       | $v_0$          | $v_1$ | $v_2$ | $v_3$ | $v_4$ | $v_5$ | $v_6$ |  |

|             | $c_0$ | 1              | 1     | 1     | 1     | 0     | 0     | 0     |  |

| Check nodes | $c_1$ | 1              | 1     | 0     | 0     | 1     | 1     | 0     |  |

|             | $c_2$ | 1              | 0     | 1     | 0     | 1     | 0     | 1     |  |

Figure 2.8 Parity-check matrix H for (7, 4, 3) Hamming code.

# 2.3 LDPC codes

A low-density parity-check (LDPC) code is a code defined by a parity-check matrix with low density, i.e., the parity-check matrix  $\mathbf{H}$  has a low number of 1s. It has been shown [39] that there exists classes of such codes that asymptotically reach the Shannon bound with a density tending to zero as the block length tends to infinity. Moreover, the theorem also states that such codes are generated with a probability approaching one if the parity-check matrix  $\mathbf{H}$  is just constructed randomly. However, the design of practical decoders is greatly simplified if some structure can be imposed upon the parity-check matrix. This seems to often negatively impact the error-correcting performance of the codes, leading to a trade-off between the performance of the code and the complexity of the encoder and decoder.

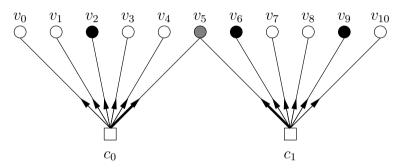

## 2.3.1 Tanner graphs

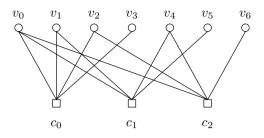

LDPC codes are commonly visualized using Tanner graphs [92]. Moreover, the iterative decoding algorithms are defined directly on the graph (see Sec. 2.4.1). The Tanner graph consists of nodes representing the columns and rows of the parity-check matrix, with an edge between two nodes if the element in the intersection of the corresponding row and column in the parity-check matrix is 1. Nodes corresponding to columns are called variable nodes, and nodes corresponding to rows are called check nodes. As there are no intersections between columns and between rows, the resulting graph is bipartite with all the edges between variable nodes and check nodes. An example of a Tanner graph is shown in Fig. 2.7, and its corresponding parity-check matrix is shown in Fig. 2.8. Comparing to (2.11), it is seen that the matrix is that of the (7, 4, 3) Hamming code.

Having defined the Tanner graph, there are some properties which are interesting for the decoding algorithms for LDPC codes.

- A **check node regular** code is a code for which all check nodes have the same degree.

- A variable node regular code is a code for which all variable nodes have the same degree.

- A (j, k)-regular code is a code which is variable node regular with variable node degree j and check node regular with check node degree k.

- The girth of a code is the length of the shortest cycle in its Tanner graph.

- The **diameter** of a code is the largest distance between two nodes in its Tanner graph.

Using a regular code can simplify the decoder architecture. However, it has also been conjectured [39] that regular codes can not be capacity-approaching under message-passing decoding. The conjecture will be proved if it can be showed that cycles in the code can not enhance the performance of the decoder on average. Furthermore, it has also been showed [25,27,72,87] that codes need to have a wide range of node degree distributions in order to be capacity-approaching. Therefore, assuming that the conjecture is true, there is a trade-off between code performance and decoder complexity regarding the regularity of the code.

The sum-product decoding algorithm for LDPC codes computes exact marginal bit probabilities when the code's Tanner graph is free of cycles [65]. However, it can also be shown that the graph must contain cycles for the code to have more than minimal error correcting performance [36]. Specifically, it is shown that for a cycle-free code C with parameters (N, K, d) and rate R = K/N, the following conditions apply. If  $R \ge 0.5$ , then  $d \le 2$ , and if R < 0.5, then C is obtained from a code with  $R \ge 0.5$  and  $d \le 2$  by repetition of certain symbols. Thus, as cycles are needed for the code to have good theoretical properties, but also inhibit the performance of the practical decoder, the concept of girth is important. Using a code with large girth and small diameter is generally expected to improve the performance, and codes are therefore usually designed so that the girth is at least six.

## 2.3.2 Quasi-cyclic LDPC codes

One common way of imposing structure on an LDPC code is to construct the parity-check matrix from equally sized sub-matrices which are either all zeros or cyclically shifted identity matrices. These types of LDPC codes are denoted quasicyclic (QC-LDPC) codes. Typically, QC-LDPC codes are defined from a base

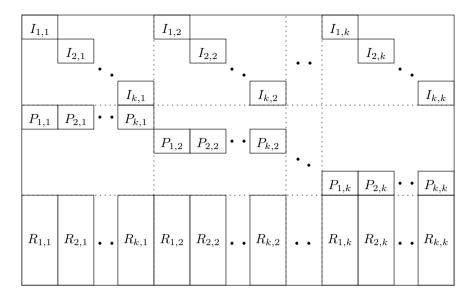

Figure 2.9 Parity-check matrix structure of randomized quasi-cyclic codes through joint code and decoder architecture design.

matrix  $\mathbf{H}_b$  of size  $M_b \times N_b$  with integer elements:

$$\mathbf{H}_{b} = \begin{pmatrix} \mathbf{H}_{b}(0,0) & \mathbf{H}_{b}(0,1) & \cdots & \mathbf{H}_{b}(0,N_{b}-1) \\ \mathbf{H}_{b}(1,0) & \mathbf{H}_{b}(1,1) & \cdots & \mathbf{H}_{b}(1,N_{b}-1) \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{H}_{b}(M_{b}-1,0) & \mathbf{H}_{b}(M_{b}-1,1) & \cdots & \mathbf{H}_{b}(M_{b}-1,N_{b}-1) \end{pmatrix}.$$

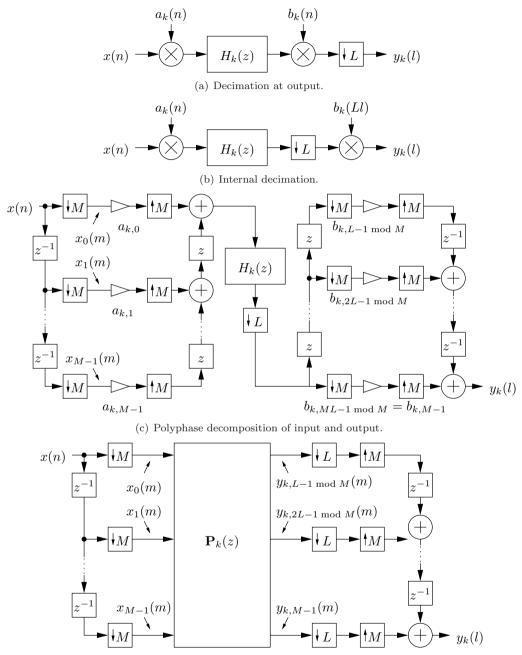

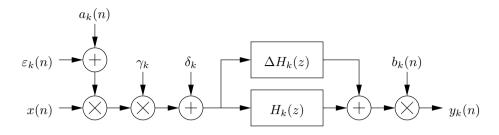

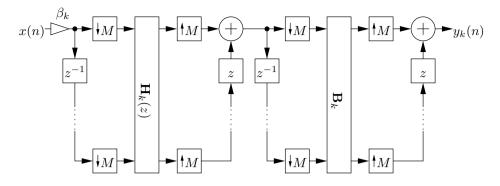

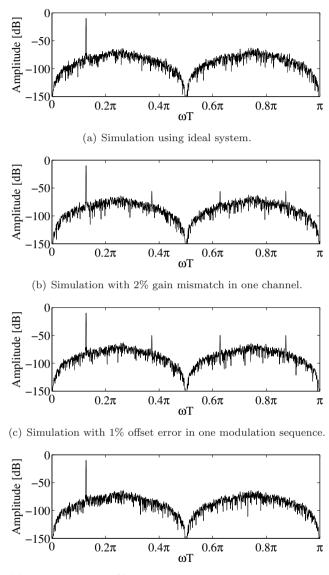

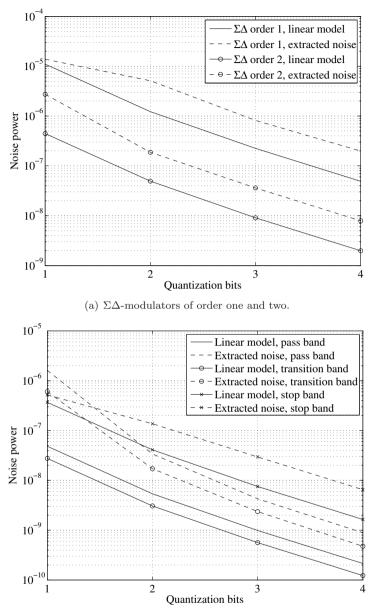

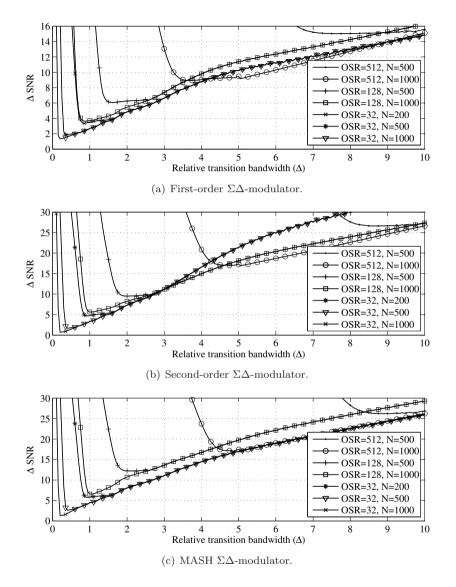

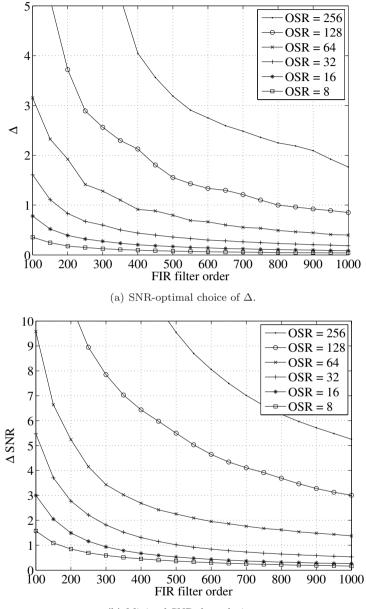

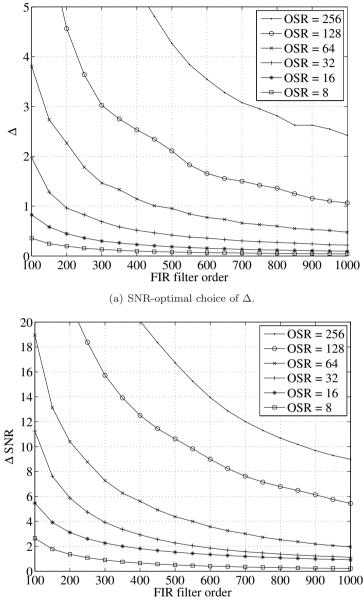

(2.12)