# 1 Patterning metal contacts on monolayer MoS<sub>2</sub> with vanishing Schottky

# 2 barriers using thermal nanolithography

- 3 Xiaorui Zheng<sup>1, 2†</sup>, Annalisa Calò<sup>1, 2†</sup>, Edoardo Albisetti<sup>1, 2, 3\*</sup>, Xiangyu Liu<sup>1, 2</sup>, Abdullah Sanad M.

- 4 Alharbi<sup>2</sup>, Ghidewon Arefe<sup>4</sup>, Xiaochi Liu<sup>5</sup>, Martin Spieser<sup>6</sup>, Won Jong Yoo<sup>5</sup>, Takashi Taniguchi<sup>7</sup>, Kenji

- Watanabe<sup>7</sup>, Carmela Aruta<sup>8</sup>, Alberto Ciarrocchi<sup>9</sup>, Andras Kis<sup>9</sup>, Brian S. Lee<sup>10</sup>, Michal Lipson<sup>10</sup>, James

- 6 Hone<sup>4</sup>, Davood Shahrjerdi<sup>2</sup>, Elisa Riedo<sup>1, 2\*</sup>

7

- 8 Advanced Science Research Center (ASRC), CUNY Graduate Center, New York NY 10031, USA

- <sup>2</sup> Tandon School of Engineering, New York University, New York NY 11201, USA

- <sup>3</sup> Dipartimento di Fisica, Politecnico di Milano, Milano 20133, Italy

- <sup>4</sup>Department of Mechanical Engineering, Columbia University, New York NY 10027, USA

- 12 <sup>5</sup> SKKU Advanced Institute of Nano-Technology (SAINT), Sungkyunkwan University, 2066, Seobu-ro, Jangan-gu, Suwon,

- **13** Gyeonggi 440-746, Korea

- 14 <sup>6</sup> SwissLitho AG Technoparkstrasse 1, Zurich CH-8005, Switzerland

- <sup>7</sup> National Institute of Materials Science, 1-1 Namiki Tsukuba, Ibaraki 305-0044, Japan

- 16 National Research Council (CNR-SPIN), Rome 00133, Italy

- 17 <sup>9</sup> Electrical Engineering Institute, and Institute of Materials Science and Engineering, École Polytechnique Fédérale de Lausanne

- 18 (EPFL), 1015, Lausanne, Switzerland

- 19 Department of Electrical Engineering, Columbia University, New York NY 10027, USA

20

- <sup>†</sup>These authors contributed equally to this work.

- \*e-mail: edoardo.albisetti@polimi.it, elisa.riedo@nyu.edu

23 **24**

25

26 27

28

29

30

31

32

33

34 35 Two-dimensional semiconductors, such as molybdenum disulfide (MoS<sub>2</sub>), exhibit a variety of properties that could be useful in the development of novel electronic devices. However, nanopatterning metal electrodes on such atomic layers, which is typically achieved using electron beam lithography, is currently problematic, leading to non-ohmic contacts and high Schottky barriers. Here, we show that thermal scanning probe lithography can be used to pattern metal electrodes with high reproducibility, sub-10 nm resolution, and high throughput (10<sup>5</sup> µm²/h per single probe). The approach, which offers simultaneous in situ imaging and patterning, does not require a vacuum, high energy, or charged beams, in contrast to electron beam lithography. Using this technique, we pattern metal electrodes in direct contact with monolayer MoS<sub>2</sub> for top-gate and back-gate field-effect transistors. These devices exhibit vanishing Schottky barrier heights (around 0 meV), on/off ratios of 10<sup>10</sup>, no hysteresis, and subthreshold swings as low as 64 mV/dec without using negative capacitors or hetero-stacks.

**36** 37

38

39

As conventional electronic devices reach their limits of performance, a search is underway in the microelectronics industry to find new materials<sup>1</sup>, fabrication methods<sup>2</sup>, and architectures<sup>3</sup>. Conventional lithographic techniques are, in particular, problematic in terms of resolution (optical lithography), operational costs (electron beam lithography, EBL), and their ability to pattern novel electronic materials and architectures. Among various novel materials being considered, two-dimensional molybdenum disulfide (MoS<sub>2</sub>) is of particular interest due to its large band gap, low dielectric constant, and heavy carrier effective mass<sup>3-6</sup>. Currently, a key issue in creating high performing field-effect transistors (FETs) based on MoS<sub>2</sub> and other transition metal dichalcogenides (TMDC) films is the poor quality of the metal contacts fabricated on these atomic layers, which gives rise to non-ohmic contacts, high Schottky barriers and large contact resistances<sup>1,7</sup>. Several approaches have been proposed to address these problems<sup>8</sup>, including trying different metallic alloys and doping<sup>9,10</sup>, using a metallic phase of MoS<sub>2</sub><sup>11</sup> or a h-BN layer as interface between the metal contact and the semiconducting MoS<sub>2</sub> layer<sup>12</sup>, and exploiting graphene as contact<sup>13-15</sup>. However, all these strategies are either non-scalable or have not yet been fully developed. They also all rely on conventional fabrication methods, typically EBL, for metal contact patterning.

EBL is currently the most widespread and reliable nanomanufacturing method for metal electrode patterning when nanoscale dimensions are required. The technique requires ultra-high vacuum (UHV) and does not allow in situ imaging. Its scalability is also limited by the costs and complexity of a multi-beam systems. Furthermore, primary and secondary electrons in EBL, as well as ultraviolet (UV) exposure in optical lithography, can damage 2D materials, from graphene to TMDC films<sup>16-20</sup>. Moreover, resist contamination on the surface of the 2D material is a major impediment for the fabrication of high performing electronic devices<sup>21-27</sup>. Among other nanopatterning methods, laser direct writing is a promising technique that offers far-field three-dimensional, maskless and cost-effective optical beam lithography with high throughput, even if the diffraction-limit is a barrier for achieving nanoscale resolution. Laser direct writing has, for example, been shown to be effective in patterning electrodes by direct laser sintering of metal nanoparticle inks deposited on a substrate<sup>25</sup>.

In this Article, we report a strategy to fabricate metal contacts on 2D materials with high reproducibility. Our approach is based on a double polymer stack chemical etching/lift off process combined with thermal scanning probe lithography (t-SPL). Using a commercial system based on t-SPL<sup>2,28-31</sup>, top-gated and back-gated monolayer (a single atomic layer, 1L) MoS<sub>2</sub> FETs are fabricated with different metals as direct contacts on the MoS<sub>2</sub>. The approach does not require vacuum, allows for in situ simultaneous patterning and imaging of a monolayer of MoS<sub>2</sub>, can achieve sub-10 nm resolution, gives rise to no resist contamination, and completely eliminates damage from either electrons or photons. As a result, the t-SPL fabricated FETs exhibit on/off ratios up to 10<sup>10</sup>, Schottky barrier heights (SBH) close to 0 mV, and sub threshold swings as low as 64 mV/dec without using negative capacitors or hetero-stacks, outperforming EBL results in the literature<sup>4,32-36</sup>. Applications to other TMDCs are also reported. The technique,

which currently runs with a single scanning probe, has a throughput similar to EBL and can readily be implemented in a cost-effective manner to multiple probes to increase throughput.

## MoS<sub>2</sub> FETs fabrication by t-SPL

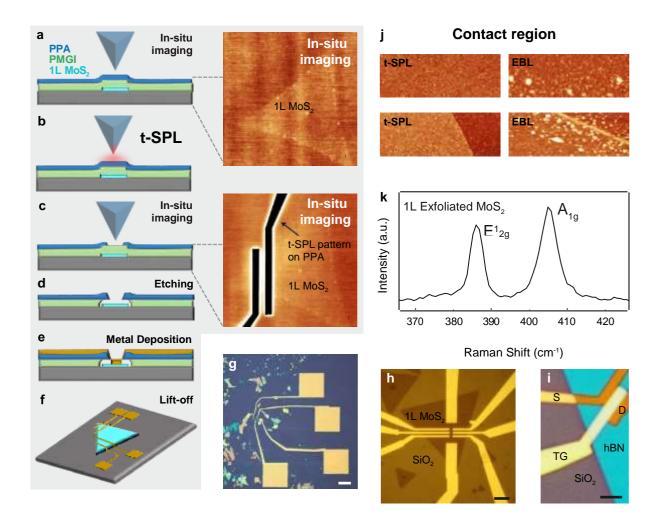

Our approach to patterning metal contacts uses a two-layer polymer stack (Fig. 1), uniformly spin coated on MoS<sub>2</sub> films. The top polymer layer is locally thermally decomposed/evaporated in less than 1 µs using a heated nano-probe<sup>28-31</sup> in t-SPL (see Supplementary Information, and Supplementary Figure 1, Supplementary Fig. 2, and Supplementary Video 1), while the removal and optimal undercut profile of the exposed bottom polymer layer is obtained by selective chemical etching and prebake conditions (see Methods). Polyphthalaldehyde (PPA)<sup>29</sup> serves as the top layer resist (20 nm thick) due to its remarkable thermal sensitivity, while polymethylglutarimide (PMGI) is used as the sacrificial bottom layer (210 nm thick) for the high yield and high resolution metal lift-off process. Before starting the electrode patterning, the 1L MoS<sub>2</sub> structure is imaged *in situ* underneath the polymer stack via thermal nanoimaging (see Fig. 1a, Supplementary Information, and Supplementary Fig. 1). Single-digit nanometer patterns in PPA, with lateral resolution of less than 10 nm and vertical resolution of 1 nm, can be reproducibly achieved<sup>2,37,38</sup> (see Supplementary Fig. 2). Moreover, the PPA thermally decomposed products evaporate immediately without re-deposition on the substrate or contaminating the nanoprobes, facilitating a complete residual-free and clean patterning process. The patterned PPA does not require any chemical development and can readily be used as an etching mask with high mechanical stability. After t-SPL patterning of PPA (Fig. 1b), the PMGI layer is locally exposed without PPA residuals, and the patterned area can be directly imaged for checking the correct alignment of the pattern (Fig. 1c) before initiating the PMGI chemical etching (Fig. 1d). After PMGI selective removal, the patterned MoS<sub>2</sub> contact region is exposed and ready for metal deposition. The final step consists in the evaporation of the metal electrodes (Fig. 1e) and lift-off (Fig. 1f) (see also Methods). Figures 1g-i show optical images of different examples of t-SPL fabricated FETs on 1L CVD and exfoliated MoS<sub>2</sub> flakes, illustrating that both large pads (Fig. 1g) and fine electrodes (Fig. 1h) can be fabricated by t-SPL.

Imaging by atomic force microscopy (AFM) (see Fig. 1j) indicates that the patterned MoS<sub>2</sub> contact region is completely free of any resist residue, whereas the contact region after the conventional EBL process shows considerable resist residues. Extensive AFM characterization of different locations on MoS<sub>2</sub> flakes after t-SPL and EBL fabrication shows in the case of the EBL process damage of the flakes' edges and presence of residuals (see the Supplementary Section 3 and Fig. S4-S6). Furthermore, X-Ray Photoemission spectroscopy (XPS) indicates that these residuals are indeed residues of the PMMA resist used during the EBL process (see Supplementary Section 4 and Supplementary Fig. 7). Figure 1k shows the Raman spectroscopy characterization of a typical exfoliated 1L MoS<sub>2</sub> flake used for FET fabrication, confirming that the E<sup>1</sup><sub>2g</sub> and A<sub>1g</sub> modes are separated by 19 cm<sup>-1</sup>, characteristic of monolayer flakes<sup>39-41</sup>. The exfoliated<sup>42</sup> and CVD MoS<sub>2</sub> flakes used in this work have been all characterized by Raman spectroscopy to confirm their monolayer nature (see Supplementary Section 6 and Fig. 10).

- Representative AFM images of monolayer exfoliated and CVD flakes used in this work are

- shown in Supplementary Fig. 11. The t-SPL fabricated 1L MoS<sub>2</sub> FETs channel region is also

- characterized by Raman spectroscopy after fabrication (see Supplementary Section 5 and

- Supplementary Fig. 9), confirming that the t-SPL process does not damage MoS<sub>2</sub>. We remark

- that, differently from t-SPL, it has been shown that, during EBL, electron beam irradiation can

- cause damage in 2D materials<sup>43,44</sup>.

- The bottom device layer, in this case monolayer  $MoS_2$ , is not heated (T <  $50^{\circ}$ C) during the t-SPL

- patterning process, as verified by thermal flow finite element simulations (see Supplementary

- Fig. 3). Moreover, after each writing line, the non-heated nano-probe reads the written line

- allowing for *in situ* correction, closed-loop patterning, and self-alignment. t-SPL also allows for

- imaging the surface before patterning using the same, non-heated probe used for t-SPL, for

- localizing the area where the patterns need to be fabricated and aligning features with nanometric

- precision, without the necessity of additional markers. The versatility of t-SPL allows the

- fabrication on a wide range of materials, as shown in Fig. 1i, where we display the optical image

- of an aligned top-gate (TG) fabricated by t-SPL on an exfoliated h-BN flake (see discussion of

- 139 Fig. 2), in the SI we also report on monolayer WSe<sub>2</sub> FETs. Finally, the t-SPL throughput can be

- scaled up by multiplexing the nanoprobe arrays<sup>30</sup> (see Supplementary Fig. 1e), in contrast to

- 141 EBL in which multiplexing is complex and costly.

- 142

143

# t-SPL 1L MoS<sub>2</sub> FETs electrical characterization

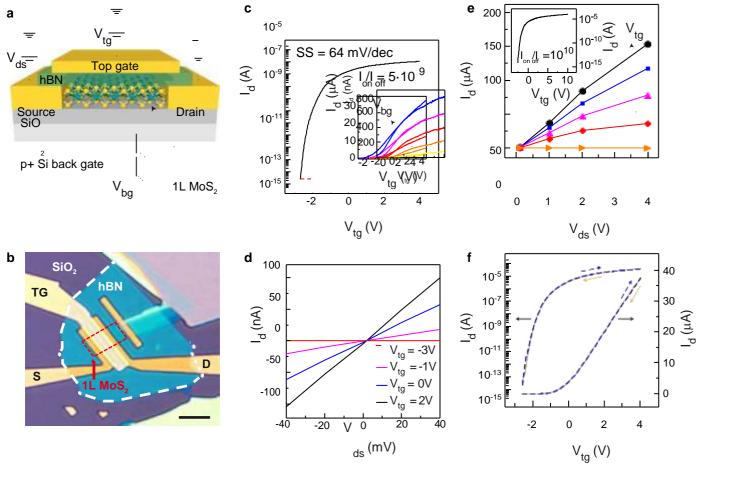

- In order to demonstrate the capabilities of t-SPL, we fabricate dual-gate 1L MoS<sub>2</sub> FETs with

- aligned patterned top-gate. First, Pd/Au source and drain contacts are fabricated as shown in Fig.

- 1. Then, a 15-20 nm insulating h-BN flake is aligned and transferred on the FET as gate

- dielectric. After the coating of the PMGI/PPA layers stack, the topography of the system was

- acquired in situ via thermal nanoimaging. This process allows to directly visualize with

- nanometric precision the source/drain contacts underneath the resist as well as the h-BN flake,

- and precisely align the top-gate with no need for additional markers (see Supplementary Fig. 12).

- Figure 2a shows a schematic of the cross section of a top-gate 1L MoS<sub>2</sub> FET, with the electrical

- 153 connections used in the measurements. In Fig. 2b, the optical image of the FET is shown. The

- regular geometry of the rectangular 1L MoS<sub>2</sub> flake (red dashed line in Fig. 2b, see

- Supplementary Fig. 13 for the optical image of the pristine flake) allows the precise

- measurement of the channel length  $L = 1.9 \mu m$  and width  $W = 3.5 \mu m$ . Figure 2c reports on the

- room temperature transfer curve of the FET for a drain voltage  $V_{\rm ds} = 2$  V, measured by recording

- the drain current  $I_d$  as a function of the top-gate voltage  $V_{tg}$ . It features a nearly-ideal 64 mV/dec

- subthreshold swing, combined with the highest on/off ratio reported in literature for a 1L MoS<sub>2</sub>

- FET of  $I_{\rm on}/I_{\rm off} = 5 \cdot 10^9$ . In the inset, the top-gate transfer curves are presented as a function of the

- back-gate voltage ranging from  $V_{bg} = -20 \text{ V}$  (yellow curve) to  $V_{bg} = +20 \text{ V}$  (blue curve),

- demonstrating the full functionality of the dual-gate t-SPL patterned FET. The high quality of the

t-SPL contacts is demonstrated also in Fig. 2d, where the output curves of the FET for small  $V_{\rm ds}$  are presented. The curves, acquired by recording the drain current  $I_{\rm d}$  as a function of the drain voltage  $V_{\rm ds}$ , are linear, demonstrating the ohmic character of the contacts.

For evaluating the performance of the device in terms of on-current  $I_{\rm on}$ , we performed additional measurements at higher  $V_{\rm ds}$  and  $V_{\rm tg}$  after keeping the device in vacuum for 1 week. In Fig. 2e, we report the  $I_{\rm d}$  as a function of the  $V_{\rm ds}$  up to 4 V, for different top-gate voltages ranging from  $V_{\rm tg}$  = -2.5 V (orange curve) up to  $V_{\rm tg}$  = 10 V (black curve). The device features an extremely high  $I_{\rm on}$ =154  $\mu$ A, which gives rise to the normalized value of  $I_{\rm on}$ -L/W= 84  $\mu$ A, which is among the highest values reported for monolayer MoS<sub>2</sub> FETs (see discussion of Fig. 5). We remark that the corresponding transfer curve, reported in the inset, features a very low off current  $I_{\rm off}$ , leading to the record-high  $I_{\rm on}/I_{\rm off}$  =  $2\cdot10^{10}$ . The equivalency of the source and drain currents, acquired throughout the whole measurements (see Supplementary Fig. 14), confirms the high quality of the h-BN gate dielectric and fabrication process. Fig. 2f reports the forward and reverse transfer curve at  $V_{\rm ds}$  = 2 V, plotted both in the logarithmic and linear scale. Importantly, it demonstrates a hysteresis-free transfer curve across the whole range of  $V_{\rm tg}$ , due to the absence of defects and trapped charges at the dielectric interface. This provides an additional compelling demonstration that t-SPL enables a residue-free and defect-free fabrication process, which in turn preserves an extremely high quality of the materials and interfaces.

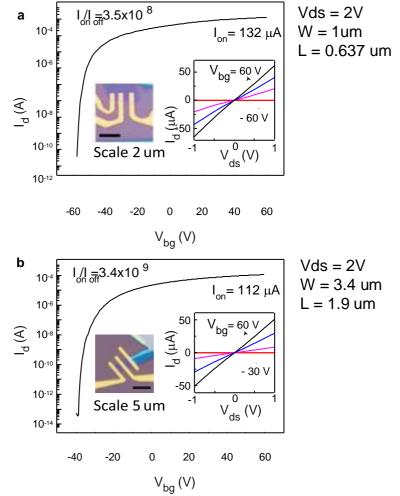

The electrical characterization of two back-gate exfoliated 1L MoS<sub>2</sub> FETs with Pd/Au contacts fabricated by t-SPL is shown in Fig. 3. The corresponding optical images of the devices are shown in the insets. The devices feature a channel length and width of  $L=0.6~\mu m$ ,  $W=1~\mu m$  (Fig. 3a) and  $L=1.9~\mu m$ ,  $W=3.5~\mu m$  (Fig. 3b). Room temperature transfer characteristics (drain current  $I_d$  as a function of the back-gate voltage  $V_{bg}$ ) are measured by sweeping  $V_{bg}$  up to +60 V with drain voltage  $V_{ds}=2~V$ . Both FETs show a considerably large on-current of 132  $\mu A$  and 112  $\mu A$ , which leads to normalized on-current values  $I_{on} \cdot L/W$  of 84  $\mu A$  and 62  $\mu A$  respectively, combined with extremely high  $I_{on}/I_{off}$  of  $3.5\cdot10^8$  and  $3.4\cdot10^9$ , respectively. The subthreshold swing is 500 mV/dec and 400 mV/dec respectively, which is remarkably low for a thick global SiO<sub>2</sub> back-gate<sup>45</sup>. The insets show the corresponding room temperature output curves, featuring a linear  $I_d$  ( $V_{ds}$ ) behavior at all  $V_{bg}$ , from -60 V to +60 V, and even at low temperatures (see inset of Fig. 4a), indicating an ohmic contact between the t-SPL patterned electrodes and MoS<sub>2</sub>. We remark that, as reported in the detailed comparison with literature of Fig. 5, these back-gate devices feature state-of-the-art on-current combined with record-high  $I_{on}/I_{off}$ .

In a direct metal-MoS<sub>2</sub> contact there are two main components contributing to the contact resistance, the tunneling barrier between the metal and MoS<sub>2</sub> due to the Van der Waals gap and the Schottky barrier between the contact and the channel region. Schottky Barrier Height values vary from 370-38 meV<sup>33-36</sup> for metals in direct contact with 1L MoS<sub>2</sub>, to 16 meV when using h-BN/MoS<sub>2</sub> stacks<sup>36</sup>. Values obtained between multilayer MoS<sub>2</sub> and contact metals vary between

50 meV with Ti and 30 meV with  $Sc^{46}$ , larger SBH have been found for monolayer  $MoS_2$  with Ti, precisely 350 meV, in part because of its smaller electron affinity  $(4.2 \text{ eV})^{42}$ . The SBH is related to many factors and it is a complex phenomenon<sup>1</sup> which accounts for the work function difference between metal and  $MoS_2$ , diffusion and doping of the metal atoms in the  $MoS_2$  layer<sup>42,47</sup>, presence of defects<sup>48</sup>, and presence of adsorbates of various origin including resist residuals<sup>1,49</sup>. To evaluate the SBH of the t-SPL patterned electrodes, temperature dependent transfer characteristics are collected on exfoliated  $1L MoS_2$  FETs with different metal contacts.

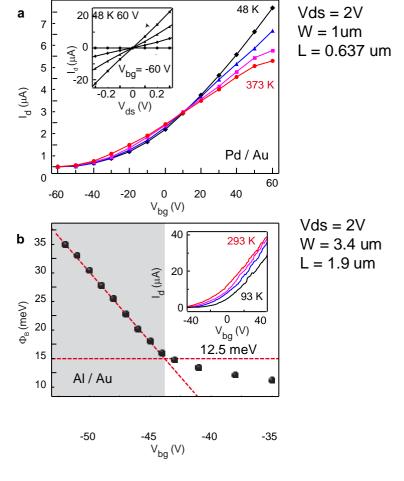

First, the transfer curves of the t-SPL patterned FETs with Pd/Au electrodes (as reported in Fig. 3) are obtained at different temperatures at  $V_{\rm ds} = 0.1$  V, as shown in Fig. 4a. For positive gate voltages, the drain current decreases with increasing temperature, indicating a metallic behavior, whereas for negative biases this temperature dependence is reversed, giving rise to insulating characteristics. This transition manifests as a crossing-over at  $V_{\rm bg} \sim 10$  V in Fig. 4a, and it is known as metal-insulator transition (MIT)<sup>50-52</sup>. The corresponding output curves at 48 K are plotted in the inset of Fig. 4a, showing a linear behavior even at low temperatures. Together, the metallic temperature dependence shown in Fig. 4a, and the linearity of the I-V curves at all temperatures (see Fig. 3 and inset of Fig. 4a) indicate a vanishing SBH (also confirmed by the Arrhenius plots as a function of  $V_{\rm bg}$  as described below here) and an ohmic behavior of the t-SPL patterned FET with Pd/Au electrodes.

Moreover, Al/Au contacts are patterned by t-SPL on 1L exfoliated MoS<sub>2</sub> flake. The temperature dependent transfer curves obtained at  $V_{\rm ds} = 2$  V are shown in the inset of Fig. 4b. To evaluate the SBH, the variations of the current through the device as a function of  $V_{\rm bg}$  under different temperatures are used to generate the Arrhenius plots reported in the Supplementary Fig. 15. It is well known that in a FET the current mainly depends on the thermionic emission and the thermally assisted tunneling, and when  $V_{\rm bg}$  is below the flat-band voltage,  $I_{\rm d}$  can be written as  $^{1,9,12,34}$ :

$$I_{d} = A^{*} T^{3/2} exp \left(-\frac{q \triangleleft P}{4}\right) \left[1 - exp \left(-\frac{q \vee ds}{4}\right)\right]$$

(1)

$$^{2d} k_{B}T k_{B}T$$

where  $A^{*d}$  is the 2D equivalent Richardson constant,  $\mathcal{O}_B$  is the SBH, T is the absolute temperature,  $k_B$  is the Boltzmann constant, and q is the electronic charge. Since we are considering  $q \cdot V_{ds} >> k_B T$ , Eq. (1) can be simplified to obtain a linear relationship between  $\ln(I_d/T^{3/2})$  and 1/T. In particular, the SBH is determined from the slope of the Arrhenius plots and plotted as a function of  $V_{bg}$  in Fig. 4b. It can be clearly seen that the thermionic emission current dominates when  $V_{bg}$  is lower than the flat-band voltage, which corresponds to the voltage at which the activation energy stops to depend linearly on  $V_{bg}$ . Therefore, the flat-band Schottky barrier height for t-SPL patterned Al/Au contacts can be readily determined from Fig. 4b to be merely 12.5 meV.

To the best of our knowledge, 12.5 meV and the vanishingly small barrier observed in Pd/Au devices are the smallest SBH ever demonstrated in any EBL patterned direct metal contact on MoS<sub>2</sub> back-gated FETs<sup>1,33-35,42,53,54</sup>. The best value reported for 1L exfoliated MoS<sub>2</sub> direct contacts is 38 meV<sup>36</sup> and for multi-layer MoS<sub>2</sub> is 30 meV<sup>46</sup>. We notice that Al/Au contacts give larger SBH than Pd/Au in our t-SPL patterned FETs. The factors that could potentially influence the contact resistance and the SBH in a given metal contact include 42,47 48 33,55 variations in surface contamination, defect and surface states concentration in the material, field emission, metal/semiconductor wave function overlap (predicted for metals on graphene to result in an effective lowering of the metal work function that may also apply to MoS<sub>2</sub>), metal-induced gap states (MIGS), defect dominated Schottky barrier height, interface dipole formation, metal-semiconductor interaction induced gap states. Also, complex mechanisms which are metal specifics, have been highlighted as important factors in studying the metal/MoS<sub>2</sub> monolayer interface, for example s-electron metals such as Ag, Al, and Au have fully occupied d-orbitals and interact with MoS<sub>2</sub> weakly, whereas the d-electron metals such as Pd interact with MoS<sub>2</sub> strongly. We argue that the observed absence of damage at the edges and the residual-free surfaces observed for the t-SPL process as opposed to EBL (see Supplementary Fig. 4-7) may be the underlying reason for the observed vanishingly small SBH in the t-SPL 1L-MoS<sub>2</sub>-FETs. It is indeed possible that by freeing the metal-MoS<sub>2</sub> interface from polymer residuals, we may change the nature itself of the interface, e.g. by increasing the metal/MoS2 interaction and the metal-induced-gap-states. Further experiments are required to understand the microscopic origin of the different contact behavior for different metals and for the t-SPL and EBL processes.

## Comparison of t-SPL FETs with literature results

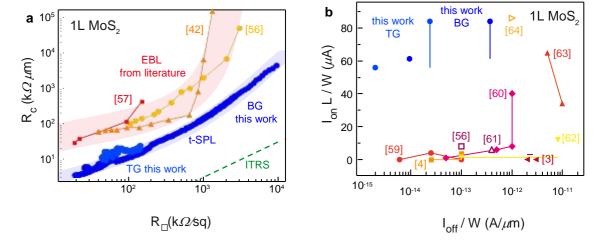

To quantitatively characterize the quality of the t-SPL electrodes and compare them with state-of-the-art electrodes patterned with conventional methods, we have derived the contact resistance ( $R_c$ ) of the different t-SPL fabricated contacts on 1L MoS<sub>2</sub>. Since the contact resistance depends mainly on the quality of the contact interface and on the resistivity of the MoS<sub>2</sub> film itself, a reliable comparison should involve MoS<sub>2</sub> films having similar sheet resistance to separate the effect of the contact from the effect of the material properties<sup>1</sup>. Accordingly, in Fig. 5a we plot the contact resistance of t-SPL fabricated electrodes as a function of the sheet resistance ( $R_{\Box}$ ) for both top-gate and back-gate devices shown in Fig. 2, Fig. 3 (see also Supplementary Fig. 16a and Fig. 17), Fig. 4 and Supplementary Fig. 19 (blue lines and symbols), and compare these values with the EBL results reported in literature<sup>42,56,57</sup> (red-yellow lines and symbols). We remark that the sheet resistance of a MoS<sub>2</sub> film can be modulated by changing the gate voltage in the corresponding FET.

In general, the contact resistance is expected to decrease with the sheet resistance. For example, the international technology roadmap for semiconductors (ITRS) 22-nm-node requirement for low-standby-power silicon-on-insulator FETs<sup>1</sup>, plotted in Fig. 5a (green dashed line), shows that the goal in terms of contacts formation is to reduce the intercept of the linear  $R_c$  vs.  $R_{\Box}$  curves,

i.e. to obtain contacts with lower contact resistance for samples having the same sheet resistance.

When analyzing the data related to EBL electrodes on MoS<sub>2</sub>, we notice that the  $R_c$  vs.  $R_{\square}$  data points for 1L exfoliated flakes follow the same curve, suggesting comparable contact quality (see the shaded stripe in red, as guide to eyes).

> Here, by using t-SPL to fabricate the electrodes, we show that we are able to dramatically lower the  $R_c$  vs.  $R_{\square}$  curves for direct metal contacts on 1L MoS<sub>2</sub> in both top-gate and back-gate configuration. This is clearly demonstrated from the blue symbols reported in Fig. 5a. Data are extracted from transport measurements on transfer length measurement (TLM) structures fabricated on chemical vapor deposited (CVD) 1L MoS<sub>2</sub> (see Supplementary Section 11 and Supplementary Fig. 19 and 20), and using the Y-function method to analyze the data from the electrical measurements on top-gate and back-gate exfoliated 1L MoS<sub>2</sub> FETs as reported in Fig. 2, Fig. 3 and Fig. 4 (for the Y-function method, see the Supplementary Section 12 and Supplementary Fig. 21). It is evident that the t-SPL patterned contacts show one order of magnitude smaller contact resistance compared to EBL patterned electrodes for MoS<sub>2</sub> samples having the same sheet resistance. The lowest contact resistance obtained for a t-SPL FET with CVD 1L MoS<sub>2</sub> is ~ 20 k $\Omega$ · $\mu$ m<sup>56</sup> while, as expected, the t-SPL FETs with exfoliated flakes show much smaller sheet resistance than CVD MoS<sub>2</sub> with a minimum contact resistance of only 3  $k\Omega \cdot \mu m$  at  $V_{ds} = 2$  V, for the device in Fig. 3a. This is one of the lowest values ever reported for direct metal MoS<sub>2</sub> monolayer contact<sup>1,33,42,56,58</sup> at this  $V_{\rm ds}$ . For example, Liu et. al. demonstrated a contact resistance of 3 k $\Omega$ ·µm at  $V_{ds} = 2$  V<sup>42</sup>. We notice that the dependence of the contact resistance on the sheet resistance of the exfoliated MoS2 t-SPL FETs follows the same line as for CVD MoS<sub>2</sub> t-SPL FETs, indicating that the improvement in contact quality is independent of material source or quality. While these curves represent the present benchmark of the t-SPL patterned electrodes, they can certainly be further improved by using additional strategies recently proposed in literature for improving contacts, such as the use of a dielectric tunneling layer<sup>36</sup>, 1T phase engineering<sup>11</sup>, and the use of graphene for the contacts<sup>15</sup>.

Figure 5b shows the detailed comparison of the on-current  $I_{\text{on}} \cdot L/W$  and off-current  $I_{\text{off}}/W$  of the t-SPL 1L MoS<sub>2</sub> FETs, with the best values found in literature. In order to compare effectively the contact quality in FETs with different geometries, the normalization to the channel width and length is crucial. In Fig. 5b red-yellow symbols and lines report the data for EBL 1L MoS<sub>2</sub> FETs<sup>3,4,56,59-64</sup>, while blue lines and symbols represent t-SPL 1L MoS<sub>2</sub> FETs presented in this work. Noteworthy, the great majority of the EBL FETs are characterized by relatively low normalized  $I_{\text{on}}$  below 10  $\mu$ A, and the FETs characterized by higher on-current feature a correspondingly larger off-current, leading to a significant reduction of the  $I_{\text{on}}/I_{\text{off}}$ . Remarkably, t-SPL FETs feature a normalized  $I_{\text{on}}$  current which is the among the best reported, combined with an extremely low  $I_{\text{off}}$  current leading to record-high  $I_{\text{on}}/I_{\text{off}}$  between 10<sup>9</sup>-10<sup>10</sup> for 1L MoS<sub>2</sub> FETs in both the top-gate and back-gate configuration.

In Figure 5c we report the comparison of the performance of t-SPL devices with the best results in literature concerning on-off ratio  $I_{\text{on}}/I_{\text{off}}$ , subthreshold swing SS and normalized on-current

$I_{\text{on}}^{4,58,60,62,64,65}$ . We remark that, here, the comparison is extended to multilayer MoS<sub>2</sub> FETs, 323 which are usually characterized by higher on-currents, and to different strategies for improving 324 the FETs performances, such as the use of negative capacitor gate dielectrics. Moreover, the 325 comparison between FETs fabricated by t-SPL and the best EBL results in literature 4,33-36,42,58,64 326 327 for only direct metal contacts on monolayer MoS<sub>2</sub> is summarized, as shown in Table 1. Finally, as an additional test, the back-gate t-SPL devices based on exfoliated 1L MoS<sub>2</sub> is compared with 328 equivalent EBL devices fabricated in our laboratory, with the same contact metals and device 329 geometry. The obtained results confirm the superior performance of the t-SPL devices and are 330 shown in Section 9 (Supplementary Fig. 16-18) and Supplementary Table 1 of the 331 Supplementary Information. Noteworthy, the results of this work, obtained by simple metal 332 patterning via t-SPL, show remarkably better performances in terms of combination of 10<sup>9</sup>-10<sup>10</sup> 333 on-off ratio, nearly ideal subthreshold swing of 64 mV, high normalized  $I_{\rm on}$  and zero hysteresis. 334 We anticipate that by combining the t-SPL metal patterning approach with the aforementioned 335 methods, even higher performance MoS<sub>2</sub> FETs can be envisioned.

337

338

339

340

341

342

343

344

345 346

336

To demonstrate the generality of the approach also for other 2D semiconductors, back-gated FETs are fabricated via t-SPL on monolayer WSe<sub>2</sub> exfoliated on Si/SiO<sub>2</sub> substrates. The results are reported in the SI, in Supplementary Fig. 24. Along with these results we also include Table S3 where we compare the performances of a back gated monolayer WSe<sub>2</sub> FET fabricated by t-SPL with data from literature on FETs based on the same type of material. In particular, for a meaningful comparison, we compare the previously published transfer characteristics performances of n-FET WSe<sub>2</sub> with our data, by reporting both maximum on current and on/off ratio for monolayer and few-layer (< 5) n-FET WSe<sub>2</sub>. As clear from this Table, t-SPL can produce FETs with transfer characteristics having the highest on/off ratio and on current among n-type monolayer or few-layer WSe<sub>2</sub> FETs.

348

349

350

351

352

353

354

355

356

357 358

359

360

361

362

363

347

### **Conclusions**

We have shown that thermal scanning probe lithography can be used to fabricate high-quality metal contacts on 2D materials with high reproducibility. Electron beam lithography is typically used for metal nanopatterning when high resolution is needed, but the need for ultra-high vacuum and high-energy electrons limits its wider application. Compared to EBL, our approach offers advantages in terms of device performance and capabilities, including not requiring a vacuum, even for 14 nm-length channels, and simultaneous in situ imaging and patterning with an overlay accuracy better than 5 nm. We have used our t-SPL-based scheme to fabricate topgated and back-gated FETs on 1L MoS2 and 1L WSe2. By eliminating resist contamination, and damage from either electrons or photons, our MoS<sub>2</sub> FETs show linear I-V curves even at low temperatures, record low Schottky barrier heights (~0 mV), record high on/off ratios (10<sup>9</sup>-10<sup>10</sup>), and exceptionally low SS (64 mV/dec). t-SPL is compatible with standard etching procedures and could potentially be pushed to single-digit-nm spatial resolution, and, by multiplexing with thermal nanoprobe arrays<sup>30,66</sup>, to higher throughput. The approach could thus lead to low-cost, no-vacuum, one-step industrial metal nanomanufacturing.

365

#### **METHODS**

#### 366 **Materials**

- We use monolayer exfoliated MoS<sub>2</sub> flakes (from bulk MoS<sub>2</sub>, SPI) and monolayer 367

- monocrystalline CVD MoS<sub>2</sub> triangular structures (from 2Dlayer) on highly doped Silicon 368

- substrate covered with 285 nm of thermally grown Silicon Oxide. Exfoliated MoS<sub>2</sub> samples are 369

- dipped for 2 h in Acetone to remove tape residuals, and then rinsed with Isopropyl alcohol 370

- (IPrOH) before starting the fabrication. For the top-gated FETs, we use as top-gate dielectric h-371

- BN flakes mechanically exfoliated on SiO<sub>2</sub>/Si, which are annealed (300°C, 2h), and then 372

- transferred onto the target 1L MoS<sub>2</sub> FET (back-gated) with a dry stamp-assisted pick-and-place 373

- 374 process. The thickness of the h-BN flake for the FET shown in Fig. 2 is 15 nm, as measured by

- 375 AFM. The t-SPL patterning scheme is then used to image and pattern in situ the top-gate without

- 376 markers.

377

403

# Device fabrication by t-SPL

- All MoS<sub>2</sub> samples are kept in contact with HMDS vapors for 90 s to promote polymer adhesion. 378

- First, a solution of pure PMGI (Polymethylglutarimide, Sigma) is spin-coated on the samples 379

- surface (2000 rpm, 35 s) followed by a quick baking. For device fabrication this step is repeated 380

- three times; then, a PPA (Polyphthalaldehyde, Sigma) solution (1.3 wt % in Anisole) is spin-381

- coated on PMGI (conditions: 2000 rpm at 500 rpm/s for 4 s and then 3000 rpm at 500 rpm/s for 382

- 383 35 s) followed by a quick baking. With these conditions, a 20 nm thick PPA film on top of a 210

- nm thick PMGI film is deposited on the samples surface. Patterning of PPA is performed using a 384

- commercial NanoFrazor t-SPL tool (SwissLitho AG), which uses hot probes to locally heat a 385 resist<sup>37</sup> with nanoscopic resolution (more details are reported in the SI). During the lithographic 386

- writing the tip is heated to reach about 200°C at the PPA surface. Finite element simulations of 387

- the heat flow from the hot tip through PMGI, after all PPA is evaporated, have been performed 388

- with the FEniCS platform to evaluate the heat temperature underneath PMGI on the MoS<sub>2</sub> layer, 389

- as reported in the Supplementary Section 2 and Supplementary Fig. S3. Patterns are performed 390

- with a pixel time in the range of 30-70 µs. For patterning large pads (size: 100 x 100 µm<sup>2</sup>) the 391

- overlay and stitching routine is used<sup>66</sup>. For the chemical etching of PMGI after patterning, 392

- samples are immersed in a solution of TMAH in deionized water (Tetramethylammonium 393

- hydroxide AZ726 MIF, MicroChemicals) (0.17 mol/L) for 400 s, then rinsed with deionized 394

- water (30 s), IPrOH (30 s) and finally dried with N<sub>2</sub>. Metal deposition is performed using an AJA 395

- Orion 8E e-beam evaporator (Pressure ~10<sup>-8</sup> torr, evaporation rate: 1 Å/s). Finally, metal/resist 396

- lift-off is performed by dipping samples in Remover PG (MicroChem) for a few hours, then 397

- rinsing (IPrOH) and drying (N<sub>2</sub>). The back-gate t-SPL FETs presented in this paper have been 398

- fabricated using different metals: Pd/Au (10 nm/10 nm), Pd/Au (10 nm/20 nm), Al/Au (10 nm/10 399

- nm), and Pt/Au (10 nm/10 nm) for exfoliated MoS<sub>2</sub> (see Fig. 3, 4, Supplementary Fig. 15, 16, 17,

- 400 401 18, 21 and Supplementary Table 1), and Cr/Au for CVD MoS<sub>2</sub> (10 nm/20 nm) (see

- 402 Supplementary Fig. 19 and 20). Cr/Au (10 nm/20 nm) is used as metal for the top-gate.

#### **Electrical measurements**

404 Electrical characterization of CVD monolayer MoS<sub>2</sub> is carried out using a parameter analyzer and a home built shielded probe station working in vacuum (10<sup>-4</sup> Torr) with micro-manipulated 405 probes. A 7651 Agilent DC source, a Keithley KE2400 source-meter and a 34401A Agilent 406 Multimeter are used respectively for applying the gate voltage, the source-drain voltage and to 407 read the drain current. Electrical measurements on exfoliated flakes are carried out following the 408 standard routines for FETs by either using an Agilent 4155C semiconductor parameter analyzer 409 in a vacuum probe station at a pressure of 10<sup>-3</sup> Torr, or a Keithley 4200-scs semiconductor 410 characterization system in a Lakeshore probe station at a pressure of 10<sup>-5</sup> Torr. To avoid the 411 capacitive coupling between the back and top-gates during the measurements of the top-gate 412 devices, the back-gate is either grounded or biased. 413

# Samples characterization

414

- Tapping mode AFM images are collected in different areas of CVD monolayer MoS<sub>2</sub> flakes after

- 416 EBL and t-SPL fabrication and resist removal, in order to systematically investigate the

- cleanliness of the samples and the presence of residuals from fabrication. The results are shown

- in the Supplementary Section 3 and in the Supplementary Fig. 4-6. Tapping mode AFM images

- are also collected to verify the monolayer nature of the CVD and exfoliated MoS<sub>2</sub> samples used

- in this work (see Supplementary Fig. 11), and before and after electrodes deposition in t-SPL

- fabrication to assess the resolution of the t-SPL technique (see Supplementary Fig. 2). Images are

- 422 collected using a Multimode 8 AFM (Bruker) and PPP-NCH tips (Nanosensors).

- Raman spectroscopy is used to establish the monolayer nature of all the exfoliated and CVD

- 424 MoS<sub>2</sub> flakes used for t-SPL fabrication (see the Supplementary Section 6 and Fig. 110) and to

- investigate the contact and channel region for the t-SPL and EBL fabrication (see Supplementary

- 426 Fig. 8 and 9). Raman spectra are collected using a Horiba LabRAM HR800 system coupled with

- an Olympus BX41 inverted optical microscope, and using a laser source with excitation

- wavelength of 532 nm. Laser power is adjusted to avoid sample damage, or any sample

- modification, as observed by optical microscopy. Spectra are acquired between 100-900 cm<sup>-1</sup>

- with 1s exposure time and as an average of 10 different measurements. The peak at 520.7 cm<sup>-1</sup>

- from the Silicon substrate is used as a reference for the position of the MoS<sub>2</sub> peaks. Reported

- spectra in Fig. S8, S9 and S10 are normalized with respect to the MoS<sub>2</sub> A<sub>1g</sub> peak.

- 433 XPS spectroscopy is used to investigate the residuals from EBL fabrication, as reported in

- Supplementary Section 4 and Fig. S7. XPS measurements are performed with a Physical

- Electronics VersaProbe II system (UHV pressure < 10<sup>-6</sup> Pa) and using Al Kα radiation (1486.6

- eV). The sample is mounted on a steel sample holder and grounded. The following conditions

- are used: analyzer acceptance angle =  $20^{\circ}$ ; take-off angle =  $45^{\circ}$ ; beam size =  $200 \mu m$ ; pass

- energy = 11.75 eV (C1s); integration time = 200 ms/step; step size = 0.05 eV/step.

#### DATA AVAILABILITY STATEMENT

- The data that support the plots within this paper and other findings of this study are available

- from the corresponding author upon reasonable request

439

#### **REFERENCES**

444 445

- 1 Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. *Nat Mater* **14**, 1195-1205 (2015).

- 448 2 Garcia, R., Knoll, A. W. & Riedo, E. Advanced scanning probe lithography. *Nat Nanotechnol* **9**, 577-587 (2014).

- Desai, S. B. *et al.* MoS<sub>2</sub> transistors with 1-nanometer gate lengths. *Science* **354**, 99-102 (2016).

- 452 4 Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS<sub>2</sub>

453 transistors. *Nat Nanotechnol* **6**, 147-150 (2011).

- 5 Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors Nat Rev Mater 1, 1-15 (2016).

- Lembke, D., Bertolazzi, S. & Kis, A. Single-layer MoS<sub>2</sub> electronics. *Acc Chem Res* **48**, 100-110 (2015).

- 458 7 Xu, Y. *et al.* Contacts between two- and three-dimensional materials: ohmic, schottky, and p-n heterojunctions. *ACS Nano* **10**, 4895-4919 (2016).

- 8 Zhao, Y. *et al.* Doping, contact and interface engineering of two-dimensional layered transition metal dichalcogenides transistors. *Adv Funct Mater* **27**, 1603484 (2017).

- Wang, W. *et al.* Controllable Schottky barriers between MoS<sub>2</sub> and permalloy. *Sci Rep* **4**, 6928 (2014).

- 464 10 Yang, L. *et al.* Chloride molecular doping technique on 2D materials: WS<sub>2</sub> and MoS<sub>2</sub>.

465 *Nano Lett* **14**, 6275-6280 (2014).

- 466 11 Kappera, R. *et al.* Phase-engineered low-resistance contacts for ultrathin MoS<sub>2</sub> transistors. *Nat Mater* **13**, 1128-1134 (2014).

- Farmanbar, M. & Brocks, G. Controlling the Schottky barrier at MoS<sub>2</sub>/metal contacts by inserting a BN monolayer. *Phys Rev B* **91**, 161304 (2015).

- Cui, X. *et al.* Multi-terminal transport measurements of MoS<sub>2</sub> using a van der Waals heterostructure device platform. *Nat Nanotechnol* **10**, 534-540 (2015).

- Guimarães, M. H. *et al.* Atomically thin ohmic edge contacts between two-dimensional materials. *ACS Nano* **10**, 6392-6399 (2016).

- Leong *et al.* Low resistance metal contacts to MoS<sub>2</sub> devices with Nickel etched graphene electrodes. *ACS Nano* **9**, 869-877 (2015).

- 476 16 Zan, R. *et al.* Control of radiation damage in MoS<sub>2</sub> by Graphene encapsulation. *ACS Nano* **7**, 10167-10174 (2013).

- Meyer, J. C. *et al.* Accurate measurement of electron beam induced displacement cross sections for single-layer graphene. *Phys Rev Lett* **108**, 196102 (2012).

- Lehnert, T., Lehtinen, O., Algara–Siller, G. & Kaiser, U. Electron radiation damage mechanisms in 2D MoSe<sub>2</sub>. *Appl Phys Lett* **110**, 033106 (2017).

- Imamura, G. & Saiki, K. Modification of graphene/SiO<sub>2</sub> interface by UV-irradiation: effect on electrical characteristics. *ACS Appl Mater Interfaces* **7**, 2439-2443 (2015).

- Zhang, R., Chen, T., Bunting, A. & Cheung, R. Optical lithography technique for the fabrication of devices from mechanically exfoliated two-dimensional materials. *Microelectron Eng* **154**, 62-68 (2016).

- 487 21 M. Ishigami, J. H. Chen, W. G. Cullen, M. S. Fuhrer & Williams, E. D. Atomic Structure of Graphene on SiO<sub>2</sub>. *Nano Lett* **7**, 1643–1648 (2007).

- Robinson, J. A. et al. Contacting graphene. Appl Phys Lett 98, 053103 (2011).

- 490 23 Macintyre, D. S., Ignatova, O., Thoms, S. & Thayne, I. G. Resist residues and transistor gate fabrication. *J Vac Sci Technol B* **27**, 2597-2601 (2009).

- 492 24 Kang, S., Movva, H. C. P., Sanne, A., Rai, A. & Banerjee, S. K. Influence of electron-493 beam lithography exposure current level on the transport characteristics of graphene field 494 effect transistors. *J Appl Phys* **119**, 124502 (2016).

- 495 25 Lin, Y. C. *et al.* Graphene annealing: how clean can it be? *Nano Lett* **12**, 414-419 (2012).

- Van Ngoc, H., Qian, Y., Han, S. K. & Kang, D. J. PMMA-etching-free transfer of waferscale chemical vapor deposition two-dimensional atomic crystal by a water soluble polyvinyl alcohol polymer method. *Sci Rep* **6**, 33096 (2016).

- 499 27 Lin, Z. *et al.* Controllable growth of large-size crystalline MoS<sub>2</sub> and resist-free transfer assisted with a Cu thin film. *Sci Rep* **5**, 18596 (2015).

- Albisetti, E. *et al.* Nanopatterning reconfigurable magnetic landscapes via thermally assisted scanning probe lithography. *Nat Nanotechnol* **11**, 545-551 (2016).

- Pires, D. *et al.* Nanoscale three-dimensional patterning of molecular resists by scanning probes. *Science* **328**, 732-735 (2010).

- 505 30 Carroll K. M. *et al.* Parallelization of thermochemical nanolithography. *Nanoscale* **6**, 1299-1304 (2014).

- 507 31 Szoszkiewicz, R. *et al.* High-speed, sub-15 nm feature size thermochemical nanolithography. *Nano Lett* **7**, 1064-1069 (2007).

- Wu, W. *et al.* High mobility and high on/off ratio field-effect transistors based on chemical vapor deposited single-crystal MoS<sub>2</sub> grains. *Appl Phys Lett* **102**, 142106 (2013).

- 511 33 Kim, C. *et al.* Fermi level pinning at electrical metal contacts of monolayer molybdenum dichalcogenides. *ACS Nano* **11**, 1588-1596 (2017).

- 513 34 Chen, J. R. *et al.* Control of Schottky barriers in single layer MoS<sub>2</sub> transistors with ferromagnetic contacts. *Nano Lett* **13**, 3106-3110 (2013).

- 515 35 Kwon, J. *et al.* Thickness-dependent Schottky barrier height of MoS<sub>2</sub> field-effect transistors. *Nanoscale* **9**, 6151-6157 (2017).

- 517 36 Cui, X. *et al.* Low-temperature ohmic contact to monolayer MoS<sub>2</sub> by van der Waals 518 bonded Co/h-BN electrodes. *Nano Lett* **17**, 4781-4786 (2017).

- Ryu Cho, Y. K. *et al.* Sub-10 nanometer feature size in silicon using thermal scanning probe lithography. *ACS Nano* **11**, 11890-11897 (2017).

- 521 38 Gottlieb, S. *et al.* Thermal scanning probe lithography for the directed self-assembly of block copolymers. *Nanotechnology* **28**, 175301 (2017).

- 523 39 Lee, C. *et al.* Anomalous lattice vibrations of single and few-layer MoS<sub>2</sub> *ACS Nano* **4**, 524 2695-2700 (2010).

- 525 40 Castellanos-Gomez, A. *et al.* Laser-thinning of MoS<sub>2</sub>: on demand generation of a single-layer semiconductor. *Nano Lett* **12**, 3187-3192 (2012).

- 527 41 Li, H. *et al.* From bulk to monolayer MoS<sub>2</sub>: evolution of Raman scattering. *Adv Funct Mater* **22**, 1385-1390 (2012).

- Liu, W., Sarkar, D., Kang, J., Cao, W. & Banerjee, K. Impact of contact on the operation and performance of back-gated monolayer MoS<sub>2</sub> field-effect-transistors. *ACS Nano* **9**, 7904-7912 (2015).

- 532 43 Childres, I. *et al.* Effect of electron-beam irradiation on graphene field effect devices.

533 *Appl Phys Lett* **97**, 173109 (2010).

- Parkin, W. M. *et al.* Raman shifts in electron-irradiated monolayer MoS<sub>2</sub>. *ACS Nano* **10**, 4134-4142 (2016).

- Ji, H. *et al.* Thickness-dependent carrier mobility of ambipolar MoTe<sub>2</sub>: Interplay between interface trap and Coulomb scattering. *App Phys Lett* **110**, 183501 (2017).

- Das, S., Chen, H. Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett* **13**, 100-105 (2013).

- Popov, I., Seifert, G. & Tomanek, D. Designing electrical contacts to MoS<sub>2</sub> monolayers: a computational study. *Phys Rev Lett* **108**, 156802 (2012).

- Su, J., Feng, L., Zhang, Y. & Liu, Z. Defect induced gap states in monolayer MoS<sub>2</sub> control the Schottky barriers of Pt-mMoS<sub>2</sub> interfaces. *Appl Phys Lett* **110**, 161604 (2017).

- Liu, Y., Stradins, P. & Wei, S.-H. Van der Waals metal-semiconductor junction: weak Fermi level pinning enables effective tuning of Schottky barrier. *Sci Adv* **2**, 1-6 (2016).

- 546 50 Mott, N. F. Metal-insulator transition. *Rev Mod Phys* **40**, 677-683 (1968).

- 547 51 Radisavljevic, B. & Kis, A. Mobility engineering and a metal-insulator transition in monolayer MoS<sub>2</sub>. *Nat Mater* **12**, 815-820 (2013).

- 549 52 Schmidt, H. *et al.* Transport properties of monolayer MoS<sub>2</sub> grown by chemical vapor deposition. *Nano Lett* **14**, 1909-1913 (2014).

- Wang, J. *et al.* High mobility MoS<sub>2</sub> transistor with low Schottky barrier contact by using atomic thick h-BN as a tunneling layer. *Adv Mater* **28**, 8302-8308 (2016).

- 553 54 Li, S.-L. *et al.* Thickness scaling effect on interfacial barrier and electrical contact to two-554 dimensional MoS<sub>2</sub> layers. *ACS Nano* **8**, 12836-12842 (2014).

- Tung, R. T. The physics and chemistry of the Schottky barrier height. *Appl Phys Rev* **1**, 011304 (2014).

- Liu, H. *et al.* Switching mechanism in single-layer molybdenum disulfide transistors: an insight into current flow across Schottky barriers. *ACS Nano* **8**, 1031-1038 (2014).

- Baugher, B. W., Churchill, H. O., Yang, Y. & Jarillo-Herrero, P. Intrinsic electronic transport properties of high-quality monolayer and bilayer MoS<sub>2</sub>. *Nano Lett* **13**, 4212-4216 (2013).

- 562 58 English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS<sub>2</sub> transistors by ultra-high vacuum metal deposition. *Nano Lett* **16**, 3824-3830 (2016).

- 565 59 Dai, Z., Wang, Z., He, X., Zhang, X.-X. & Alshareef, H. N. Large-area chemical vapor 566 deposited MoS<sub>2</sub> with transparent conducting oxide contacts toward fully transparent 2D 567 electronics. *Adv Funct Mater* **27**, 1703119 (2017).

- 568 60 Si, M. *et al.* Steep-slope hysteresis-free negative capacitance MoS<sub>2</sub> transistors. *Nat Nanotechnol* **13**, 24-28 (2018).

- Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS<sub>2</sub>. *ACS Nano* **5**, 9934–9938 (2011).

- Zhu, Y. *et al.* Monolayer molybdenum disulfide transistors with single-atom-thick gates.

*Nano Lett* 18, 3807-3813 (2018).

- 574 63 Xie, L. *et al.* Graphene-contacted ultrashort channel monolayer MoS<sub>2</sub> transistors. *Adv* 575 *Mater* **29**, 1702522 (2017).

- 576 64 Lembke, D. & Kis, A. Breakdown of high-performance monolayer MoS<sub>2</sub> transistors. *ACS* Nano **6**, 10070–10075 (2012).

- Kang, K. *et al.* High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* **520**, 656-660 (2015).

- Rawlings, C., Duerig, U., Hedrick, J., Coady, D. & Knoll, A. Nanometer control of the markerless overlay process using thermal scanning probe lithography. *IEEE/ASME*

582 International Conference on Advanced Intelligent Mechatronics (AIM) 1670–1675 (2014).583 584 585 ACKNOWLEDGEMENTS The authors acknowledge support from the U.S. Army Research Office (proposal # 69180-CH), 586 the Office of Basic Energy Sciences of the US Department of Energy and the National Science 587 Foundation. This project has received funding from the European Union's Horizon 2020 research 588 and innovation programme under the Marie Skłodowska-Curie grant agreement No 705326. A.S.M.A. and D.S. acknowledge the financial support of NSF-ECCS (grant # 1638598). AUTHOR CONTRIBUTION STATEMENT 589 590 X.Z., A.C., E.A., and X.L. patterned the metal electrodes by t-SPL. A.S.M.A. performed the electronic measurements on the t-SPL FETs. X.Z., E.A., X.L., A.S.M.A., D.S. and E.R. designed 591 the electronic experiments and analysed the data on the t-SPL FETs. G.A., and X.L. fabricated 592 and measured the EBL FETs. X.Z., M.S., and E.R. developed the two-polymer stack t-SPL 593 594 method. W.J.Y. and J.H. designed and analysed the EBL data. T.T. and K.W. provided the h-BN samples. C.A. analysed the XPS data. A.C. and A.K. provided the WSe<sub>2</sub> samples and contributed 595 to corresponding data analysis. B.S.L. and M.L. deposited Pd electrodes on t-SPL FETs. E.R. 596 597 conceived and analysed all the experiments on t-SPL FETs. X.Z., A.C., E.A., G.A., J.H., D.S. and E.R. contributed to write the article. 598 599 600 FINANCIAL AND NON-FINANCIAL COMPETING INTEREST STATEMENT The authors declare no competing financial interests. 601 ADDITIONAL INFORMATION 602 Supplementary information is available for this paper at https:// 603 604

607

608 609 610

611

612

613

614 615

616 617

618

619 620 Figure 1. The t-SPL fabrication process. a. In situ thermal nanoimaging of the sample topography (see also Supplementary Section 1). Image of a monolayer MoS<sub>2</sub> flake underneath the PMGI/PPA polymer stack (230 nm). Scale bar: 4 µm. b. The PPA polymer film is locally evaporated by scanning a heated scanning probe on its surface at a throughput of  $10^5 \, \mu m^2/h$ . c. In situ thermal nanoimaging of the t-SPL pattern on PPA. Scale bar: 4 um. d. Chemical etching of the now exposed PMGI polymer film, which uncovers selected areas of the MoS<sub>2</sub> surface. e. Metal contacts are deposited via evaporation. f. The PMGI and PPA films are removed via a lift- off process. g, h. Optical images of final devices fabricated on exfoliated and CVD monolayer MoS<sub>2</sub>, respectively. Scale bars: 50 µm (g) and 5 µm (h). i. Optical image of a top-gate contact fabricated on exfoliated h-BN flakes. Scale bar: 4 µm. j. Comparison between the exposed contact region after the chemical etching step and before metal deposition in t-SPL (left panels) and EBL (right panels) fabricated FETs on monolayer CVD MoS<sub>2</sub>, acquired inside (top panels) and at the boundaries (bottom panels) of monolayer CVD MoS<sub>2</sub>. Scale bars: 500 nm. k. Typical Raman spectra of monolayer exfoliated MoS<sub>2</sub> used for the fabrication of FETs via t-SPL.

Figure 2. Aligned top-gate FETs on exfoliated 1L MoS<sub>2</sub> flakes patterned by t-SPL. a.

Schematic cross-section and electrical connections of a top-gate FET. Both the source-drain contacts and the aligned top-gate are patterned via t-SPL. The structure comprises the degenerately

doped Si substrate as global back-gate, a 285 nm thermal SiO<sub>2</sub> as back-gate dielectric, and a 15 nm h-BN layer as top-gate dielectric. **b.** Optical image of the 1L MoS<sub>2</sub> FET, showing the source-

drain Pd/Au electrodes (S-D) fabricated on the 1L MoS<sub>2</sub> (red dashed line) and the aligned top-gate

= 1.9  $\mu$ m, channel width  $W = 3.5 \mu$ m. Scale bar: 5  $\mu$ m. c. Room temperature transfer curve of the

behavior of the contacts. e.  $I_d$  as a function of  $V_{ds}$  up to 4 V, at different top-gate voltages ranging

Cr/Au contact (TG) fabricated on the h-BN dielectric. Channel length L

621 622

623

624

625

626

627

628 629

630

631

632 633

top-gate FET measured at  $V_{\rm ds} = 2$  V. Subthreshold swing = 64 mV/dec,  $I_{\rm on}/I_{\rm off} = 5 \cdot 10^9$ . In the inset, transfer curves at different back-gate voltages ranging from  $V_{\rm bg} = -20 \text{ V}$  (yellow curve) to  $V_{\rm bg} = 20 \text{ V}$ 634 V (blue curve). **d.** Small voltage  $I_d$  ( $V_{ds}$ ) curves at different top-gate voltages showing ohmic 635

636 637

from  $V_{\rm tg} = -2.5$  V (orange curve) up to  $V_{\rm tg} = 10$  V (black curve), showing a maximum  $I_{\rm on}$ 638 639

= 154  $\mu$ A. In the inset, transfer curve at  $V_{\rm ds} = 4$  V, features an  $I_{\rm on}/I_{\rm off} = 2 \cdot 10^{10}$ . **f.** Forward (blue dashed line) and reverse (orange line) transfer curves in logarithmic and linear scales. The curves 640 are hysteresis-free in the whole top-gate voltage range.

641

642

Figure 3. Back-gate FETs fabricated via t-SPL on exfoliated 1L MoS<sub>2</sub> flakes. a-b. Room 648 temperature transfer curves at  $V_{\rm ds} = 2$  V of FETs with Pd/Au electrodes, fabricated on exfoliated 649 1L MoS<sub>2</sub>. The Si/SiO<sub>2</sub> 285 nm substrate was used as global back-gate and gate dielectric, 650 respectively. The devices feature  $I_{\rm on}$  up to 132 μA (a) and  $I_{\rm on}/I_{\rm off} > 3 \cdot 10^9$  (b). Scale bars: 2 μm 651 (panel a), 5 μm (panel b). Insets: corresponding room temperature output curves at different 652 back-gate voltages  $V_{\rm bg}$ .

653

654

655 **Figure 4.** Schottky barrier height (SBH) characterization of t-SPL FETs on exfoliated 1L 656 **MoS<sub>2</sub>. a.** Temperature dependent transfer curves of the t-SPL FET with Pd/Au electrodes 657 reported in Fig. 3a ( $V_{\rm ds} = 0.1 \text{ V}$ ). Inset: corresponding output curves of the same FET at 48 K. **b.** 658 Gate voltage dependence of the barrier height for a t-SPL patterned FET on 1L exfoliated MoS<sub>2</sub> 659 with Al/Au electrodes, at  $V_{\rm ds} = 2 \text{ V}$ . The deviation from the linear response at low  $V_{\rm bg}$  (dashed 660 red line) defines the flat band voltage and the SBH. Inset: corresponding temperature dependent 661 transfer curves at  $V_{\rm ds} = 2 \text{ V}$ .

662

663

664

665

666 Figure 5. Comparison of t-SPL MoS<sub>2</sub> FET performances with literature. a. Contact 667 resistance  $R_c$  of the electrodes as a function of the sheet resistance  $R_{\Upsilon}$  of 1L MoS<sub>2</sub> FETs. The red, 668 orange and yellow lines and symbols represent values extracted from literature for FETs 669 fabricated by EBL. The blue lines and symbols show the results of t-SPL fabricated FETs which 670 are extracted (right to left) from three back-gated FETs fabricated on 1L CVD (see 671 Supplementary Fig. 19), 1L exfoliated MoS<sub>2</sub> flakes (as shown in Fig. 3 and Fig. 4), and a top-FET fabricated on 1L exfoliated MoS<sub>2</sub> flake (as shown in Fig. 2). The shaded stripes show 673 the range of data corresponding to EBL data from literature (red) and t-SPL data from this work 674 (blue). The green dashed line represents the ITRS 22-nm-node requirement for low-standby- 675 power silicon-oninsulator FETs with the contact resistance down to 20% of the total resistance. 676 b. On-current normalized to the channel width W and length ( $I_{on}$ ·L/W), as a function of the  $I_{off}/W$ , 677 for 1L MoS<sub>2</sub> FETs. The red-yellow symbols and lines represent EBL data extracted from 678 literature. The blue symbols and lines show the t-SPL results presented in this work for 1L MoS<sub>2</sub> 679 FETs in the back-gate (Fig. 3) and top-gate (Fig. 2) configurations. c. In-depth comparison of the 680 performances of the best MoS<sub>2</sub> FETs presented in literature with the t-SPL results presented in 681 this work.

682

683

| 685 |  |

|-----|--|

| 686 |  |

|                         | SBH                                                       | Rc                                                 | Ion / Ioff           | ss                                                  | Requires<br>UHV | Simultaneous<br>imaging/<br>patterning | Throughput            | Resolution |

|-------------------------|-----------------------------------------------------------|----------------------------------------------------|----------------------|-----------------------------------------------------|-----------------|----------------------------------------|-----------------------|------------|

| t-SPL                   | ~ 0 meV                                                   | 3-6 kW mm<br>(Back gate)<br>10 kW mm<br>(Top gate) | 10 <sup>10</sup>     | 64 mV/dec                                           | NO              | YES                                    | 10 <sup>5</sup> μm²/h | ~ 10 nm    |

| EBL<br>in<br>literature | 38 meV [36]<br>55 meV [35]<br>60 meV [34]<br>110 meV [33] | 3 kW mm<br>(UHV) [58]<br>7 kW mm [33]              | 10 <sup>7</sup> [33] | 74 mV/dec [4]<br>178 mV/dec [64]<br>410 mV/dec [42] | YES             | NO                                     | 5 2<br>10 μm/h        | ~ 10 nm    |

**Table 1.** Comparison of FETs based on monolayer  $MoS_2$  with metal electrodes in direct contact with  $MoS_2$  (no graphene contacts, h-BN tunneling layers or NC dielectrics).

| С | Layers     | Configuration                                   | I <sub>on</sub> /I <sub>off</sub> , S (mV/dec) | I·L/W (μA) | Ref.      |

|---|------------|-------------------------------------------------|------------------------------------------------|------------|-----------|

|   | Multilayer | Bottom Gate<br>Negative Capacitor               | 10 <sup>6</sup> - 10 <sup>7</sup> , < 60       | 50         | [60]      |

|   | Multilayer | Bottom Gate (SiO <sub>2</sub> )<br>UHV Contacts | N.A.                                           | 45         | [58]      |

|   | 1L         | Top Gate                                        | 10 <sup>6</sup> , 500                          | 11         | [65]      |

|   | 1L         | Aligned Bottom Gate (Graphene contact)          | 10 <sup>7</sup> , 64                           | 1.5        | [62]      |

|   | 1L         | Top Gate                                        | 10 <sup>8</sup> , 74                           | 3.75       | [4]       |

|   | 1L         | Top Gate                                        | 10 <sup>8</sup> , 178                          | 86         | [64]      |

|   |            |                                                 |                                                |            |           |

|   | 1L         | Top Gate                                        | 10 <sup>9</sup> - 10 <sup>10</sup> , 64        | 84         | This work |

|   | 1L         | Bottom Gate (SiO <sub>2</sub> )                 | 10 <sup>9</sup> , 400                          | 62 - 84    | This work |