## **Durham Research Online**

## Deposited in DRO:

24 October 2012

## Version of attached file:

Published Version

## Peer-review status of attached file:

Peer-reviewed

## Citation for published item:

Yun, Y.J. and Pearson, C. and Petty, M.C. (2009) 'Pentacene thin film transistors with a poly(methyl methacrylate) gate dielectric : optimization of device performance.', Journal of applied physics., 105 (3). 034508.

## Further information on publisher's website:

http://dx.doi.org/10.1063/1.3075616

### Publisher's copyright statement:

Copyright 2009 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and the American Institute of Physics. The following article appeared in Yun, Y.J. and Pearson, C. and Petty, M.C. (2009) 'Pentacene thin film transistors with a poly(methyl methacrylate) gate dielectric : optimization of device performance.', Journal of applied physics., 105 (3). 034508 and may be found at http://dx.doi.org/10.1063/1.3075616

#### Use policy

$The full-text\ may\ be\ used\ and/or\ reproduced,\ and\ given\ to\ third\ parties\ in\ any\ format\ or\ medium,\ without\ prior\ permission\ or\ charge,\ for\ personal\ research\ or\ study,\ educational,\ or\ not-for-profit\ purposes\ provided\ that:$

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in DRO

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full DRO policy for further details.

# Pentacene thin film transistors with a poly(methyl methacrylate) gate dielectric: Optimization of device performance

Youngjun Yun, Christopher Pearson, and Michael C. Petty<sup>a)</sup>

School of Engineering and Centre for Molecular and Nanoscale Electronics, Durham University, Durham DH1 3LE, United Kingdom

(Received 3 October 2008; accepted 18 December 2008; published online 10 February 2009)

The electrical characteristics of pentacene-based organic thin film transistors (OTFTs) using poly(methyl methacrylate) (PMMA) as the gate dielectric are reported. Uniform pinhole-free and crack-free films of PMMA could be obtained by spin coating, with a lower limit of thickness of about 150 nm. The effects of the insulator thickness and channel dimensions on the performance of the devices have been investigated. Leakage currents, which are present in many polymeric gate dielectrics, were reduced by patterning the pentacene active layer. The resulting devices exhibited minimal hysteresis in their output and transfer characteristics. Optimized OTFT structures possessed a field-effect mobility of 0.33 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a threshold voltage of -4 V, a subthreshold slope of 1.5 V/decade, and an on/off current ratio of  $1.2 \times 10^6$ . © 2009 American Institute of Physics. [DOI: 10.1063/1.3075616]

#### **I. INTRODUCTION**

Organic thin film transistors (OTFTs) possess two key advantages over structures fabricated from inorganic semiconductors: mechanical flexibility and low-cost manufacture. Various organic semiconductor materials have been used as the active layer in OTFTs. These include molecular crystals such as pentacene, which can be deposited in thin film form by thermal evaporation, and conductive polymers, which can be conveniently processed by solution-based methods, such as spin coating and inkjet printing.<sup>1</sup> The gate dielectric layer also plays a crucial role in determining the performance of organic transistors;<sup>2</sup> the benefits of OTFTs can easily be lost if inappropriate insulators are used. For example, the inorganic insulator SiO<sub>2</sub>, a common gate dielectric in OTFTs, will crack under stresses caused by the bending of plastic substrates. Certain organic gate insulators, such as benzocyclobutene, need a very high curing temperature, which precludes the use of many organic substrates.

A range of different organic materials has been investigated for the gate dielectric. These include poly(vinyl alcohol), poly(vinyl phenol), and poly(styrene).<sup>1</sup> Hybrid organic/ inorganic insulators have also been used.<sup>3</sup> The high resistivity (>2×10<sup>15</sup>  $\Omega$  cm) and low dielectric constant (approximately 3, similar to that of silicon dioxide) of poly-(methyl methacrylate) (PMMA) make it potential candidate as the dielectric layer in OTFTs.<sup>2,4</sup> Furthermore, this polymer contains hydrophobic methyl radical groups, which can play a role as moisture inhibitors, as well as encourage good ordering of the active organic overlayer as it is deposited on the surface.<sup>5</sup> To date, pentacene-based OTFT devices using PMMA as the gate dielectric have shown low field-effect mobilities (generally less than 0.1  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ ) due to the relatively thick film of PMMA used, low on/off current ratios (10<sup>3</sup>) resulting from large leakage currents, and high threshold voltages (-15 to -25 V).<sup>6–9</sup> However, one encouraging

result is that of Huang *et al.*,<sup>10</sup> who reported a mobility of 0.24 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> using a 300 nm thick PMMA layer.

In this work, spin coating has been used to produce high quality thin layers of PMMA. These have been incorporated into pentacene OTFTs and the electrical characteristics have been studied as a function of the insulator thickness. It is shown that leakage currents can be reduced significantly by pattering the active layer, leading to a good on/off current ratio. Finally, the influence of scaling of the channel length and width on the transistor characteristics is reported.

#### **II. EXPERIMENT**

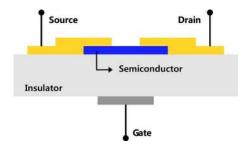

In this work, top-contact OTFTs were fabricated using the structure shown schematically in Fig. 1. The device fabrication was undertaken in a class 1000 clean room. Glass slides were used as the substrates and an aluminum gate (thickness: 30 nm) was defined by thermal evaporation through a shadow mask. An anisole (methoxybenzene; obtained from MicroChem) solution of PMMA ( $M_w$ =93 000, obtained from Sigma-Aldrich) was spin coated on top and cured for 1 h at 120 °C. The thickness of the PMMA film was varied from 100 to 2000 nm by changing the solution concentration and spin-coating speed. Following this, pentacene (Sigma-Aldrich and used without further purification) was thermally deposited at room temperature to a thickness

FIG. 1. (Color online) A schematic cross section of the pentacene-based OTFT with a PMMA gate dielectric.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: m.c.petty@durham.ac.uk.

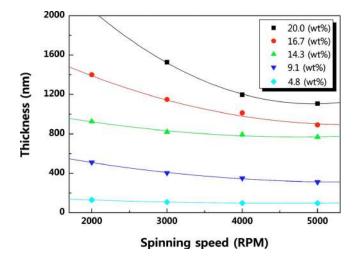

FIG. 2. (Color online) Thickness of spin-coated PMMA films as function of spinning speed and solution concentration.

of 30 nm. To explore the effects of patterning the active layer, the pentacene was deposited with and without the use of a shadow mask. The deposition rate was 0.05 nm s<sup>-1</sup> at a chamber pressure of approximately  $1 \times 10^{-6}$  mbar. A further shadow mask was used to define source and drain contacts, formed by the thermal evaporation of 30 nm of gold. The thicknesses and morphologies of the various layers were studied using a Digital Instruments Nanoscope IV atomic force microscope.

The OTFT current I versus voltage V characteristics were measured using a Keithley 485 picoammeter and 2400 source meter. The capacitance C versus voltage behavior was monitored with an HP4192A impedance analyzer.

#### **III. RESULTS AND DISCUSSION**

#### A. PMMA thickness

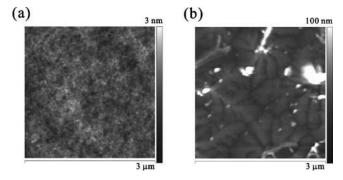

Figure 2 shows the thickness of PMMA as a function of spinning speed and solution concentration. Above 15 wt % polymer, the film thickness was inversely proportional to the spinning speed. For lower PMMA concentrations, the solution concentration was much more effective than spinning speed for controlling the thickness of the polymer. Uniform pinhole-free and crack-free films of PMMA could be obtained by spin coating, with a lower limit to the thickness of about 150 nm. Atomic force microscope images of the surfaces of a 150 nm PMMA film and of a 30 nm pentacene film, which was subsequently evaporated onto the PMMA, are shown in Fig. 3. A relatively smooth surface is evident for the PMMA [Fig. 3(a)]. The rms roughness was 0.30 nm; this can be contrasted with figures of 0.45-0.76 nm reported by Shin et al.<sup>11</sup> for a 140-160 nm thick PMMA layer. The grain size for the pentacene was greater than 1  $\mu$ m [Fig. 3(b)], with a rms roughness of 13 nm. These figures are similar to those reported by Huang et al.<sup>10</sup> for pentacene evaporated onto PMMA: grain size of  $1.0-1.5 \ \mu m$  and rms roughness of 11 nm.

A parallel plate capacitor structure (Al/insulator/Au) was fabricated to investigate the dielectric properties of the PMMA. The area of the top Au electrode was 2.25

FIG. 3. Atomic force microscope images of (a) 150 nm thick PMMA film spin coated onto a glass slide and (b) 30 nm thick pentacene film thermally evaporated on top of the PMMA.

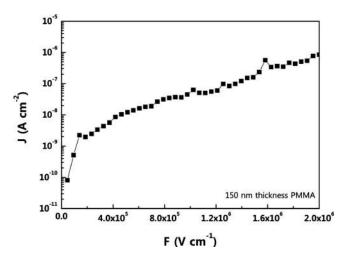

$\times 10^{-2}$  cm<sup>2</sup>. Figure 4 shows the current density *J* versus the electric field *F* for a 150 nm thick PMMA film. These data were similar for either polarity of voltage applied to the top electrode. The leakage current density is less than  $10^{-8}$  A cm<sup>-2</sup> for fields of up to 0.4 MV cm<sup>-1</sup> and this remained below  $10^{-6}$  A cm<sup>-2</sup> for fields of up to 2 MV cm<sup>-1</sup>. Such current densities are sufficiently small to allow the use of the 150 nm PMMA film as a gate dielectric in an OTFT.

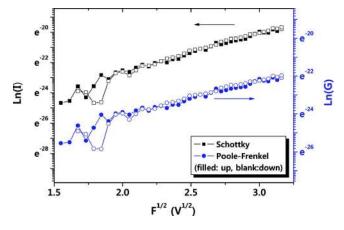

Physical processes that might account for the current versus voltage behavior in the presence of high electric fields are Schottky emission and the Poole–Frenkel effect.<sup>12,13</sup> The former process occurs at the interface between the electrode(s) and the dielectric and has an *I* versus *V* dependence of the form

$$I \propto T^2 \exp\left(\frac{\beta_{\rm Sc} V^{1/2} - \Phi_{\rm Sc}}{k_B T}\right),\tag{1}$$

where  $\Phi_{Sc}$  is the Schottky barrier height,  $\beta_{Sc}$  is the Schottky coefficient, *T* is the temperature, and  $k_B$  is the Boltzmann constant.

Poole–Frenkel conductivity is a similar process to Schottky emission, but it results from the lowering of the potential barriers around impurity centers in the bulk of the insulator. The I-V relationship is given by

FIG. 4. Current density vs applied electric field for an Al/PMMA/Au structure. The PMMA film thickness=150 nm.

FIG. 5. (Color online) Schottky  $[\ln(I) \text{ vs } F^{1/2}]$  and Poole–Frenkel  $[\ln(I/V) \text{ vs } F^{1/2}]$  plots for an Al/PMMA/Au structure. The PMMA film thickness = 150 nm.

$$I \propto V \exp\left(\frac{\beta_{\rm PF} V^{1/2} - \Phi_{\rm PF}}{k_B T}\right),\tag{2}$$

where  $\Phi_{\rm PF}$  is the potential barrier height and  $\beta_{\rm PF}$  is the Poole–Frenkel coefficient. Figure 5 shows the conductivity data obtained for the 150 nm PMMA film plotted in the form of the Schottky [ln(*I*) versus  $V^{1/2}$ ] and Poole–Frenkel [ln(*I*/*V*) versus  $V^{1/2}$ ] equations. Data are shown for both increasing and decreasing applied voltages. In each case, the fit to theory is very good. Either process (or both) might be responsible for the currents in the PMMA at high electric fields. Further work (e.g., variation in the insulator thickness and measurements at different temperatures) is clearly needed to distinguish between these electrical conduction processes.

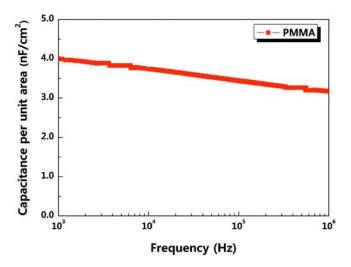

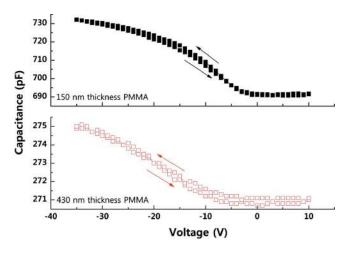

Figure 6 shows the measured capacitance per unit area as a function of frequency for an 810 nm thick PMMA layer sandwiched between the Au and Al electrodes. The dielectric constant of the PMMA decreases over the frequency range of the measurements and was calculated to be  $3.66 \pm 0.10$  at 1 kHz and  $2.89 \pm 0.10$  at 1 MHz. These values agree well with other literature reports.<sup>4,6,9,14</sup> The *C* versus *V* characteristics, measured at 1 MHz and a voltage scan rate of 1 V s<sup>-1</sup>, of

FIG. 6. (Color online) Capacitance vs frequency characteristics of a spincoated PMMA layer; thickness=810 nm.

FIG. 7. (Color online) Capacitance vs voltage characteristics, measured at 1 MHz and voltage scan rate of 1 V s<sup>-1</sup> for Al/PMMA/pentacene/Au structure for two different thicknesses of PMMA. Pentacene thickness=30 nm.

two Al/PMMA/pentacene/Au metal-insulator-semiconductor (MIS) structures are shown in Fig. 7. The *C-V* data for both samples (PMMA thicknesses of 150 and 430 nm) reveal the accumulation (large negative voltage applied to Al), depletion, and inversion behavior that is typical of MIS devices. Little hysteresis is evident on reversing the direction of the voltage scan. The anticlockwise direction of this may be related to the charging and discharging of interface traps located at, or close to, the PMMA/pentacene interface.<sup>15</sup> The accumulation capacitance values for the two MIS structures scale with the PMMA thickness and the calculated dielectric constant is consistent, within experimental errors, with the value calculated from the Au/PMMA/Al structure (Fig. 6).

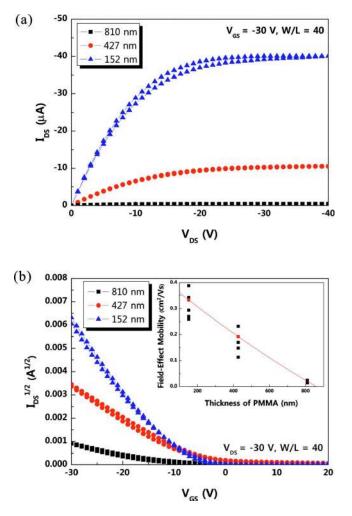

In this study, 14.3 wt % (810 nm), 9.1 wt % (427 nm), and 4.8 wt % (152 nm) solutions of PMMA, spin coated at 3000 rpm, were used to investigate the dependence of the electrical behavior of the transistors on the PMMA thickness. Figure 8 shows (a) the dependence of the drain-source current  $I_{\rm DS}$  on the drain-source voltage  $V_{\rm DS}$  (the OTFT output characteristics) and (b) the dependence of  $I_{\rm DS}$  on the gatesource voltage  $V_{\rm GS}$  (transfer characteristics) for the devices on the different thicknesses of PMMA; forward and reverse voltage scans are shown. The gate-source voltage was -30V for the output characteristics and the drain-source voltage was -30 V for the transfer characteristics. The channel width W to length L ratio was 40 (channel length=50  $\mu$ m; width=2000  $\mu$ m).

These data agree with simple thin film transistor theory.<sup>1</sup> For low  $V_{\rm DS}$  ( $V_{\rm DS} < V_{\rm G}$ ), the drain-source current is related to the drain-source voltage by

$$I_{\rm DS} = \frac{WC_i}{L} \mu \left[ V_{\rm GS} - V_T - \frac{V_{\rm DS}}{2} \right] V_{\rm DS},\tag{3}$$

where  $V_T$  is the threshold voltage,  $C_i$  is the insulator capacitance per unit area, and  $\mu$  is the field-effect mobility. The threshold voltage represents the value of the gate-source voltage beyond which a conductive channel forms at the pentacene surface (i.e., the transistor is turned on). This defines the linear region of device operation. As the gate insulator thickness is reduced,  $C_i$  will increase, accounting for the

FIG. 8. (Color online) (a) Output and (b) transfer characteristics with different thicknesses of PMMA. Inset: field-effect mobility as a function of the thickness of PMMA.

larger drain-source currents evident in Fig. 8.

For high  $V_{\text{DS}}$ , the drain-source current saturates as the conductive channel becomes "pinched off," and the saturated drain-source current  $I_{\text{DS(sat)}}$  is given by

$$I_{\rm DS(sat)} = \frac{WC_i}{2L} \mu (V_{\rm GS} - V_T)^2.$$

(4)

The value of  $\mu$  may therefore be evaluated from a plot of  $(I_{\text{DS(sat)}})^{1/2}$  versus  $V_{\text{GS}}$ . The intercept of this plot can be used to determine the device threshold voltage. The inset of Fig. 8(b) shows the variation in the field-effect mobility with insulator thickness for a number of different devices. A clear trend showing an increase in  $\mu$  with the decrease in the thickness of the gate insulator is evident. Averaged data reveal that  $\mu$  increased by about 13 times for a fivefold reduction in the PMMA thickness.

This effect has been reported previously for pentacene OTFTs (see, for example, Ref. 16), and there are now a number of different explanations for the dependence of carrier mobility on gate insulator thickness. For example, the phenomenon might be due to a variation in the gate dielectric constant of the film with the concentration of the PMMA solution.<sup>17</sup> Veres *et al.*<sup>2,18</sup> suggested that a higher dielectric

constant induces a broadening of the density of states (DOS) at the polymer/insulator interface. This results in a decrease in the DOS at the Fermi energy and subsequently causes a lower hopping probability, leading to a suppression of the carrier mobility. This effect can occur for OTFTs based on both polymers and low molecular weight materials such as pentacene. More recent work suggests that a mobility dependence for pentacene transistors can result from the viscoelastic properties of the organic dielectric.<sup>19</sup> It is certainly possible that our very thin PMMA spin-coated layers possess different surface chain dynamics. Alternatively, the morphological properties of the thermally evaporated pentacene, resulting in larger grains and higher carrier mobilities.

A theory described by Necliudov *et al.*<sup>20</sup> incorporates a gate-voltage dependent mobility. According to this model, in pentacene-based OTFTs operating above threshold, most of the charge induced by the gate-source voltage is trapped in numerous traps and only a fraction of the carriers participate in the current conduction. The effect of the charge trapping is accounted for by the gate-voltage dependent field-effect mobility given by<sup>20–22</sup>

$$\mu = \mu_0 \left( \frac{V_{\rm GS} - V_T}{V_{AA}} \right)^{\gamma},\tag{5}$$

where  $\gamma$  and  $V_{AA}$  are empirical parameters, which can be extracted from the transfer characteristics, and  $\mu_0$  is a constant. The number of accumulated carriers at the pentacene surface will depend on  $V_{GS}$ ; an increase in  $V_{GS}$  will result in an increase in the number of surface carriers. The same effect will be obtained if  $V_{GS}$  is held constant and the gate insulator thickness is reduced, due to an increase in the electric field in the insulator. Hence, for the same gate-source voltage, there will be more surface carriers available to fill the traps for a thinner insulator. Increasing the permittivity of the gate insulator will produce similar results.<sup>16</sup> The thinnest PMMA layers used in our work were 150 nm, limited by the quality of the spin-coated film. So far, we have been unable to use thinner gate dielectrics to explore if even higher mobility devices could be achieved.

We have also used the plot of  $(I_{DS(sat)})^{1/2}$  versus  $V_{GS}$  to determine the values of the threshold voltages for our OTFTs with different PMMA thicknesses. The trend was a decrease in  $V_T$  with a decrease in the thickness of the gate dielectric, from about -11 V for 810 nm gate insulators to approximately -4 V for the OTFTs with PMMA thicknesses of 152 nm. However, there was much variability between the samples (a full table showing all the parameters for our devices is shown later on, in Sec. III C) and these figures represent average values for a number of devices. The theoretical dependence of  $V_T$  on the thin film transistor parameters is quite complex. Assuming that there is no work function difference between the gate metal and the semiconductor, the magnitude of  $V_T$  can be approximated by<sup>23</sup>

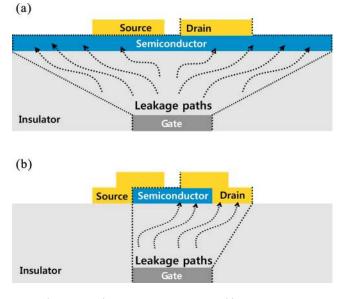

FIG. 9. (Color online) Possible leakage paths in (a) unpatterned pentacene OTFT and (b) patterned pentacene devices.

$$V_T = \left| \frac{Q_s}{C_i} \right|,\tag{6}$$

where  $Q_s$  is the effective total charge per unit area at the insulator/semiconductor interface at zero gate voltage. This charge (which may be positive or negative) will be made up from a number of contributions: mobile and fixed charges in the insulating layer and interface state charge. Our results reveal that the value of  $V_T$  decreases by a factor of approximately 3 for a fivefold decrease in the gate insulator thickness. This suggests that  $Q_s$  probably also varies with the thickness of the PMMA in our OTFTs.

#### B. Patterning the organic semiconductor

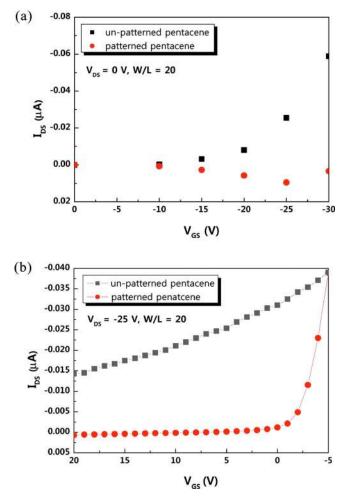

A further problem with OTFTs using PMMA as the gate dielectric has been a low on/off current ratio. This can be related to the drain offset current, which is defined as the drain current at different gate biases when the drain-source bias is zero. For an ideal device,  $I_{DS}=0$  A for  $V_{DS}=0$  V. The  $I_{\rm DS}$  offset is closely related to  $I_{\rm GS}$  and is a convenient indicator of gate induced leakage in OTFTs. Jia et al.<sup>24</sup> reviewed the possible origins of  $I_{DS}$  offset and concluded that the effect is related to the expansion of the source and drain electrodes by the semiconductor accumulation layer. The latter provides leakage paths and more current flows through the insulator as a result of these, as shown in Fig. 9(a). The leakage paths can be eliminated by patterning of the active layer [Fig. 9(b)]. This was confirmed by Jia et al.,<sup>24</sup> who reported a substantial reduction in the  $I_D$  offset following patterning of the organic semiconductor (poly-3hexylthiophene).

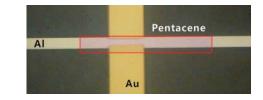

We have explored the effects of patterning the pentacene layer using shadow masks. Figure 10 shows a photograph of one of the patterned pentacene/PMMA devices. The pentacene is visible between the gold source and drain electrodes. The electrical behavior of the patterned OTFTs is shown in Fig. 11. Figure 11(a) depicts the drain current at different

FIG. 10. (Color online) Optical micrograph of a patterned pentacene-based OTFT with PMMA gate dielectric (channel length=50  $\mu$ m; channel width=500  $\mu$ m).

gate biases when the drain-source bias ( $V_{\text{DS}}$ ) was zero. For the unpatterned OTFT, it is evident that the offset in the drain current increased with increasing gate voltage. Patterning markedly decreases this effect. The gate leakage can be seen more clearly in the transfer characteristics [Fig. 11(b)], for which  $V_{\text{DS}}$ =-25 V. There is a large gate leakage in the unpatterned device, but again, this effect is much reduced in the OTFT in which the pentacene film is confined to the region between the source and drain electrodes.

#### C. Effect of channel dimensions

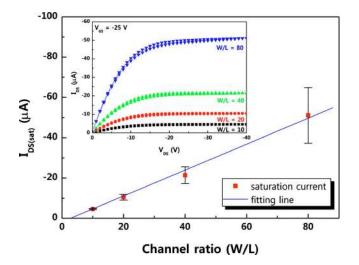

Figure 12 shows the relationship between  $I_{DS(sat)}$  and the ratio W/L for a number of our OTFTs with a fixed 50  $\mu$ m channel length and  $V_{GS}$ =-25 V; the PMMA thickness was

FIG. 11. (Color online) (a)  $I_{\rm DS}$  offset ( $V_{\rm DS}$ =0 V) and (b) leakage currents ( $V_{\rm DS}$ =-25 V) in patterned and unpatterned pentacene OTFTs.

FIG. 12. (Color online)  $I_{\text{DS(sat)}}$  vs channel width:length ratio (W/L) for pentacene OTFTs. The output characteristics are shown in the inset.  $V_{\text{DS}}$ = -25 V. PMMA thickness=152 nm.

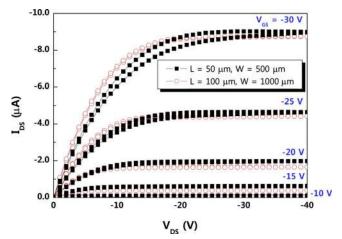

152 nm. The error bars reflect measurements on a number of different samples. The inset shows a typical set of output characteristics for these devices. Within experimental error, the saturated drain-source current varies linearly with W/L, as predicted by Eq. (2). The effects of keeping the same channel width to length ratio (W/L=10), but using different absolute values, are shown in Fig. 13: the results are for 50  $\mu$ m channel length and 100  $\mu$ m channel length structures. Both sets of data show similar output characteristics. However, the device with the longer channel shows improved saturation at lower values of  $V_{\rm DS}$  and less hysteresis (evident as the gate-source voltage is increased). We attribute these effects to the ability to align the patterned pentacene during the OTFT manufacture.

Table I provides a summary of the electrical characteristics of all of the devices that were fabricated in this study. The output and transfer characteristics for an optimized

J. Appl. Phys. 105, 034508 (2009)

FIG. 13. (Color online) Output characteristics for OTFTs with the same channel width:length ratio but different channel lengths and widths. PMMA thickness=152 nm.

OTFT are shown in Fig. 14; PMMA thickness=152 nm, L =50  $\mu$ m, and W=2000  $\mu$ m. For the output characteristics [Fig. 14(a)], linear behavior at low  $V_{\rm DS}$  with good drainsource current saturation was observed. For gate voltages below -25 V, minimal hysteresis is evident when the direction of the drain voltage scan is reversed. This suggests a relatively "clean" (in an electronic sense) interface between the pentacene and the PMMA, which is also apparent from the minimal hysteresis in the C-V characteristics of the MIS structures (Fig. 7). Figure 14(b) shows the transfer characteristics of the device, measured at  $V_{DS} = -30$  V. Plots are given in the form of both  $\log(I_{\rm DS})$  versus  $V_{\rm GS}$  and  $(I_{\rm DS})^{1/2}$  versus  $V_{GS}$ . The on/off current ratio, field-effect mobility, threshold voltage, and subthreshold slope for this particular device were  $1.2 \times 10^6$ , 0.33 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, -4 V, and 1.5 V/decade. These values compare very favorably with published data for pentacene/PMMA OTFTs.<sup>7-9</sup> For example, Huang et al.<sup>10</sup> gave  $\mu = 0.24$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $V_T = -6.3$  V; Puigdollers et

TABLE I. Summary of pentacene/PMMA OTFT characteristics.

| Thickness<br>(nm) | Channel length<br>(µm) | Channel width (µm) | Mobility<br>( $cm^2 V^{-1} s^{-1}$ ) | Subthreshold slope<br>(V decade <sup>-1</sup> ) | $V_T$ (V) | $I_{\mathrm{On}}/I_{\mathrm{Off}}$ |

|-------------------|------------------------|--------------------|--------------------------------------|-------------------------------------------------|-----------|------------------------------------|

| 152               | 50                     | 500                | 0.270                                | 2.0                                             | -4        | $6.9 \times 10^{6}$                |

|                   | 50                     | 1000               | 0.343                                | 1.2                                             | -3        | $9.7 \times 10^{5}$                |

|                   | 50                     | 2000               | 0.333                                | 1.5                                             | -4        | $1.2 \times 10^{6}$                |

|                   | 50                     | 4000               | 0.388                                | 2.9                                             | -3        | $1.5 \times 10^{5}$                |

|                   | 100                    | 1000               | 0.294                                | 1.7                                             | -6        | $6.3 \times 10^{6}$                |

|                   | 200                    | 2000               | 0.259                                | 1.6                                             | -5        | $5.7 \times 10^{6}$                |

| 427               | 50                     | 500                | 0.151                                | 5.21                                            | -5        | $4.1 \times 10^4$                  |

|                   | 50                     | 1000               | 0.113                                | 7.4                                             | -3        | $2.1 \times 10^{4}$                |

|                   | 50                     | 2000               | 0.192                                | 5.4                                             | 5         | $3.5 \times 10^{3}$                |

|                   | 50                     | 4000               | 0.232                                | 9.9                                             | 3         | $5.7 \times 10^{3}$                |

|                   | 100                    | 1000               | 0.170                                | 11                                              | -7        | $3.5 \times 10^{3}$                |

|                   | 200                    | 2000               | 0.148                                | 3.7                                             | -8        | $1.6 \times 10^{6}$                |

| 810               | 50                     | 500                | 0.014                                | 4.5                                             | -14       | $2.1 \times 10^4$                  |

|                   | 50                     | 1000               | 0.019                                | 3.4                                             | -13       | $3.2 \times 10^{4}$                |

|                   | 50                     | 2000               | 0.020                                | 2.6                                             | -10       | $8.6 	imes 10^4$                   |

|                   | 50                     | 4000               | 0.017                                | 2.9                                             | -7        | $1.1 \times 10^{5}$                |

|                   | 100                    | 1000               | 0.024                                | 2.5                                             | -10       | $2.8 \times 10^4$                  |

|                   | 200                    | 2000               | 0.024                                | 2.4                                             | -10       | $5.6 \times 10^{4}$                |

Downloaded 24 Oct 2012 to 129.234.252.65. Redistribution subject to AIP license or copyright; see http://jap.aip.org/about/rights and permissions

FIG. 14. (Color online) (a) Output and (b) transfer characteristics of a pentacene-based OTFT using PMMA as the gate dielectric. Channel length= $50 \ \mu m$ ; channel width= $2000 \ \mu m$ .

al.<sup>9</sup> reported  $\mu$ =0.01 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $V_T \sim -15$ ; and Kang *et al.*<sup>7</sup> measured  $\mu$ =0.045 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $V_T$ =-27.5 V. It is interesting to note that these three investigations used gate insulator thicknesses that are greater than the 152 nm for our optimized device, for example, 700 nm in the case of Puig-dollers *et al.*<sup>9</sup> and 945 nm for Kang *et al.*<sup>7</sup> This is entirely consistent with the trend of the data shown in Table I, which reveal an improvement in the OTFT characteristics as the PMMA thickness is reduced. The 300 nm film thickness figure and the mobility value of 0.24 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> obtained by Huang *et al.*<sup>10</sup> fit well with the trend of the data shown in the inset of Fig. 8.

#### **IV. CONCLUSIONS**

We have shown that the thickness of the PMMA dielectric layer in pentacene OTFTs has a strong influence on the field-effect mobility. In particular, the measured mobility was found to increase as the gate dielectric thickness decreased. With the thickness of the PMMA optimized to 150 nm, the OTFTs possessed a field-effect mobility >0.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a threshold voltage of around -4 V, an on/off current ratio >10<sup>6</sup>, and a subthreshold slope of 1.5 V/decade. The effect of patterning the pentacene layer during device fabrication was also investigated. This resulted in a significant reduction in the leakage currents. Finally, the influence of scaling on the OTFT characteristics was investigated with respect to the channel length and width. The results agree with simple thin film transistor theory. Although further work remains, such as understanding fully the dependence of field-effect mobility on the gate insulator thickness, the results show that PMMA is a very promising candidate for use as a dielectric layer in organic electronic devices.

#### ACKNOWLEDGMENTS

One of us (Y.Y.) would like to thank the School of Engineering, Durham University, for the provision of a studentship.

- <sup>1</sup>Organic Field-Effect Transistors, edited by Z. Bao and J. Locklin (CRC, Boca Raton, 2007).

- <sup>2</sup>J. Veres, S. Ogier, and G. Lloyd, Chem. Mater. 16, 4543 (2004).

- <sup>3</sup>D. K. Hwang, C. S. Kim, J. M. Choi, K. Lee, J. H. Park, E. Kim, H. K. Baik, J. H. Kim, and S. Im, Adv. Mater. (Weinheim, Ger.) 18, 2299 (2006).

<sup>4</sup>G. Horowitz, F. Deloffre, F. Garnier, R. Hajlaoui, M. Hmyene, and A.

- Yassar, Synth. Met. 54, 435 (1993).

- <sup>5</sup>S. H. Jin, J. S. Yu, C. A. Lee, J. W. Kim, B. G. Park, and J. D. Lee, J. Korean Phys. Soc. **44**, 181 (2004).

- <sup>6</sup>J. Puigdollers, C. Voz, I. Martin, A. Orpella, M. Vetter, and R. Alcubilla, J. Non-Cryst. Solids **338–340**, 617 (2004).

- <sup>7</sup>G.-W. Kang, K.-M. Park, J.-H. Song, C. H. Lee, and D. H. Hwang, Curr. Appl. Phys. **5**, 297 (2005).

- <sup>8</sup>K.-K. Han, S. W. Lee, and H. H. Lee, Appl. Phys. Lett. 88, 233509 (2006).

- <sup>9</sup>J. Puigdollers, C. Voz, I. Martin, M. Vetter, A. Orpella, and R. Alcubilla, Synth. Met. **146**, 355 (2004).

- <sup>10</sup>T.-S. Huang, Y. K. Su, and P.-C. Wang, Appl. Phys. Lett. **91**, 092116 (2007).

- <sup>11</sup>K. Shin, C. Yang, S. Y. Yang, H. Jeon, and C. E. Park, Appl. Phys. Lett. **88**, 072109 (2006).

- <sup>12</sup>M. C. Petty, *Molecular Electronics* (Wiley, Chichester, 2007).

- <sup>13</sup>A. S. Jombert, K. S. Coleman, D. Wood, M. C. Petty, and D. A. Zeze, J. Appl. Phys. **104**, 094503 (2008).

- <sup>14</sup>R. Asmatulu, B. Geist, W. B. Spillman, Jr., and R. O. Claus, Smart Mater. Struct. 14, 1493 (2005).

- <sup>15</sup>M. F. Mabrook, C. Pearson, D. Kolb, D. A. Zeze, and M. C. Petty, Org. Electron. 9, 816 (2008).

- <sup>16</sup>C. D. Dimitrakopoulos and D. J. Mascaro, IBM J. Res. Dev. 45, 11 (2001).

- <sup>17</sup>A. F. Stassen, R. W. I. de Boer, N. N. Iosad, and A. F. Morpurgo, Appl. Phys. Lett. 85, 3899 (2004).

- <sup>18</sup>J. Veres, S. D. Ogier, S. W. Leeming, D. C. Cupertino, and S. M. Khaffaf, Adv. Funct. Mater. **13**, 199 (2003).

- <sup>19</sup>C. Kim, A. Facchetti, and T. Marks, Science **318**, 76 (2007).

- <sup>20</sup>P. V. Necliudov, M. S. Shur, D. J. Gundlach, and T. N. Jackson, J. Appl. Phys. 88, 6594 (2000).

- <sup>21</sup>K. Seshadri and C. D. Frisbie, Appl. Phys. Lett. 78, 993 (2001).

- <sup>22</sup>G. Horowitz, J. Mater. Chem. 9, 2021 (1999).

- <sup>23</sup>B. G. Streetman and S. Banerjee, *Solid State Electronic Devices*, 5th ed. (Prentice-Hall, Englewood Cliffs, NJ, 2000).

- <sup>24</sup>H. Jia, G. K. Pant, E. K. Gross, R. M. Wallace, and B. E. Gnade, Org. Electron. 7, 16 (2006).