Article

# Performance Analysis of an Optimized Asymmetric Multilevel Inverter on Grid Connected SPV System

Devineni Gireesh Kumar <sup>1</sup>, Aman Ganesh <sup>2</sup>, Nagineni Venkata Sireesha <sup>3</sup>, Sainadh Singh Kshatri <sup>1</sup>, Sachin Mishra <sup>4</sup>, Naveen Kumar Sharma <sup>5</sup>, Mohit Bajaj <sup>6</sup>, Hossam Kotb <sup>7</sup>, Ahmad H. Milyani <sup>8,9,\*</sup> and Abdullah Ahmed Azhari <sup>10</sup>

- Department of Electrical & Electronics Engineering, B V Raju Institute of Technology, Narsapur 502313, India

Department of Electrical Engineering, Muharishi Markon dashyar Engineering College

- <sup>2</sup> Department of Electrical Engineering, Maharishi Markandeshwar Engineering College, Maharishi Markandeshwar (Deemed to Be University), Mullana, Ambala 133203, India

- <sup>3</sup> Department of Information Technology, Institute of Aeronautical Engineering, Hyderabad 500043, India

- <sup>4</sup> School of Electronics and Electrical Engineering, Lovely Professional University, Phagwara 144411, India

- <sup>5</sup> Department of Electrical Engineering, I. K. Gujral Punjab Technical University, Jalandhar 144603, India

- <sup>6</sup> Department of Electrical Engineering, Graphic Era (Deemed to Be University), Dehradun 248002, India

- <sup>7</sup> Department of Electrical Power and Machines, Faculty of Engineering, Alexandria University, Alexandria 21544, Egypt

- <sup>8</sup> Department of Electrical and Computer Engineering, King Abdulaziz University, Jeddah 21589, Saudi Arabia

- <sup>9</sup> Center of Research Excellence in Renewable Energy and Power Systems, King Abdulaziz University, Jeddah 21589, Saudi Arabia

- <sup>10</sup> The Applied College, King Abdulaziz University, Jeddah 21589, Saudi Arabia

- Correspondence: ahmilyani@kau.edu.sa

Abstract: The purpose of this research is to develop an efficient single-phase grid-connected PV system using a better performing asymmetrical multilevel inverter (AMI). Circuit component reduction, harmonic reduction, and grid integration are critical criteria for better inverter efficiency. The proposed inverter's optimized topology requires seven unidirectional switches, three symmetric dc sources, and three diodes to produce an asymmetric fifteen level output; whereas, the same configuration will generate 7, 11, and 15-level output with an appropriate choice of dc source magnitudes. It is possible to reduce inverter losses and boost efficiency by decreasing the number of switches used. The integration of an asymmetric 15-level inverter with a grid-connected solar photovoltaic system is discussed in this article. A grid-connected solar photovoltaic (GCSPV) system is modelled and simulated using an asymmetric 15-level inverter. The dc sources of the 15-level inverter are replaced with PV sources. The results were analyzed with different operating temperatures and solar irradiance conditions. The GCSPV system is controlled by a closed-loop control system using Particle Swarm Optimization (PSO), Harris Hawk Optimization (HHO), and Hybrid Particle Swarm Optimization-Genetic Algorithm (PSOGA) based Proportional plus Integral (PI) controllers. Grid voltage, grid current, grid power, and total harmonic distortion (THD) of grid currents were analyzed. The performance of the 15-level asymmetric inverter was evaluated by comparing the THD of the grid current and the efficiency of the grid-connected photovoltaic system.

**Keywords:** asymmetric multilevel inverter; solar photovoltaic system; grid integration; optimized inverter; 15-level inverter; grid-connected SPV system

# 1. Introduction

Standalone inverters based on solar photovoltaic (SPV) systems have become increasingly popular in domestic and commercial applications. Solar photovoltaic (PV) systems are becoming more important to the world in the twenty-first century to meet the electricity demand. However, due to variations in temperature or irradiation, the output voltage of the SPV system has larger ripples and, as a result, the output power is often variable. The MPPT algorithm is implemented using an appropriate DC-DC converter to address these hassles.

Citation: Kumar, D.G.; Ganesh, A.; Sireesha, N.V.; Kshatri, S.S.; Mishra, S.; Sharma, N.K.; Bajaj, M.; Kotb, H.; Milyani, A.H.; Azhari, A.A. Performance Analysis of an Optimized Asymmetric Multilevel Inverter on Grid Connected SPV System. *Energies* **2022**, *15*, 7665. https://doi.org/10.3390/en15207665

Academic Editor: Emilio Lorenzani

Received: 14 September 2022 Accepted: 14 October 2022 Published: 17 October 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). The power electronic circuits produce the higher-order harmonics in conventional inverters. Multilevel inverters are investigated to address the harmonic problems [1]. Multilevel inverter (MLI) seeks to create high-quality output to reduce THD compared to traditional inverter. The biggest disadvantage of MLIs is the use of more components. In addition, the complexity of the control and protection circuit increases. Usually, the converter reliability depends on the converter switch count [2]. High reliability and efficiency are achieved for multilevel inverters with fewer switches. Topologies that make use of as few switches as possible are discussed in [3–5]. Both high and low-frequency switching techniques may bring on an MLI operation. Sinusoidal pulse width modulation (PWM) is of the high-frequency switching method, but it also causes significant power losses and harmonic distortions. One way to avoid this drawback is by using a low-frequency modulation strategy, such as the Selective Harmonic Elimination (SHE) method [6,7]. Harmonic elimination with a focus, the only way to reduce dominating lower order harmonics in an inverter's output is to use pulse width modulation (SHEPWM). By solving the nonlinear equations generated by the inverter output. Inverter power losses are caused by high-frequency switching [8]. The reduced switch topology that is given [9] eliminates harmonics by the use of phase-shifted and level-shifted modulations; however, it is not optimal for use in high power applications. A switched capacitor-based topology has been developed with a smaller number of dc sources, but these capacitors have voltage balancing issues. To overcome problems associated with the high frequency switching modulation, a fundamental switching frequency control (SHEPWM) is implemented [10]. A boost converter is proposed [11] however, it uses many switching devices in its design increases the control complexity. The modern MLI topologies are not commercially feasible for SPV systems with limited energy conversion potential (performance in commercial applications is less than 20%).

To reduce the volume, cost, and losses in the multilevel inverter and meet the load requirements, multilevel inverters with reduced power switches and fewer circuit elements are required to build. On the other hand, the symmetrical MLI can increase the voltage levels of the inverter while operating at a low switching frequency, making it a potential PV inverter with greater efficacy. With a reduced number of switches, the inverter will operate relatively at a low switching frequency, which improves the inverter's performance and reduces the filter requirements for stand-alone or grid-connected PV applications.

Presently, multilevel inverters with reduced switch count have become a new research era for power electronic converters. This research focused on identifying and developing an asymmetric multilevel inverter with reduced switches to optimize the power and control circuits. The proposed multilevel inverter configuration is quite simple and easy to extend for higher levels, as well as its gating circuits are simplified due to the optimized number of switches. The primary factor influencing the inverter's performance is the harmonics of the multilevel output. Although, in the proposed topology of the inverter, the number of switches is reduced for the operation with different switching angles, which often causes harmonics in the output. The goal here is to optimize the switching angles to minimize the lower order harmonics of the proposed inverter.

Several optimization algorithms were reported to evaluate the optimal switching angles for the inverters; thereby, reducing the harmonics content in the inverter output. However, these algorithms are designed to operate at higher switching frequencies, unsuitable for effectively eliminating the lower order harmonics. The study carried out by various researchers mainly develops symmetrical reduced switch inverters with optimization methods, which are not relevant for solar PV applications since the solar PV system's output is variable with the variation of solar irradiance and temperature. The inverters must accept variable input from solar PV to produce a constant output voltage suitable for stand-alone or grid operation.

The optimization techniques [12] were proposed to solve the nonlinear equations formulated by selective harmonic elimination. A real-time implementation of SHEPWM is presented [13] for grid integration of SPV systems. However, feedback controls have

increased complexity. Even though two-level inverters may be utilized for PV systems that link to the grid, they result in higher dv/dt on switches and power losses [14,15]. A robust optimization method proposed in [16] to solve the non-linear constrain based functions for optimal power flow control. Also, a stochastic optimization method suggested in [17] for analyzing the virtual bidding in electricity markets. In consideration of the above, the asymmetric multilevel inverter can overcome problems for multilevel inverters, control methods, standard of grid requirements [18,19].

The above motivation leads this research to implement an asymmetric multilevel inverter with optimal switches and dc sources. The proposed topology is implemented for a 15-level inverter with seven power switches, three diodes, and three dc sources. This paper aims to develop a unique switched diode-based 15-level asymmetric inverter that achieves the necessary voltage levels. Furthermore, a hybrid PSO-GA algorithm is used to evaluate the nonlinear SHE equations for optimizing the switching angles. Section 2 describes the generalized model of the proposed structure of the asymmetric inverter, Section 3 presented a two-stage grid connected PV system and Implementation of grid connected PV system with the proposed inverter, Section 4 describes the control methodology of proposed GCSPV system, Section 5 presented the Results and Discussion and Section 6 presents the conclusion.

## 2. Proposed Asymmetric Multilevel Inverter

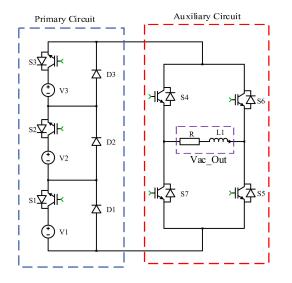

The proposed 15-level MLI consists of seven controlled semiconductor switches (IG-BTs), three diodes and three dc sources. These elements are organized in a methodical manner to achieve the desired output levels. Figure 1 shows the proposed 15-level asymmetric MLI topology. It consists of a dc supply coupled in conjunction with a main switch and a bypass diode. When the switch 'S' is switched on, the source voltage 'V' arrives at the load; when the switch 'S' is off, the source voltage is separated from the load; hence, Vdc-out = '0'. The suggested inverter operates in both symmetrical and asymmetrical modes, based on input Power source.

Figure 1. Proposed 15-level asymmetric multilevel inverter.

The circuit's dc voltage sources determine the output voltage. The proposed converter performs as an asymmetric inverter with different categories of dc sources. Table 1 shows the dc sources that can be used in the proposed inverter.

| Approach          | DC Voltages                                  | O/p<br>Steps | O/p<br>Levels | Max. O/p<br>Voltage |

|-------------------|----------------------------------------------|--------------|---------------|---------------------|

| Identical Voltage | $V_1 = V_2 = V_3 = V_{dc}$                   | 4            | 7             | 3V <sub>dc</sub>    |

| Unequal Magnitude | $V_1 = V_{dc}, V_2 = V_3 = 2V_{dc}$          | 6            | 11            | 5V <sub>dc</sub>    |

| Binary Approach   | $V_1 = V_{dc}, V_2 = 2V_{dc}, V_3 = 4V_{dc}$ | 8            | 15            | 7V <sub>dc</sub>    |

Table 1. Choice of DC voltages for the proposed MLI topology.

A similar magnitude approach produces symmetric dc sources of the same magnitude and can produce seven voltage output levels. Due to the symmetric nature of dc sources, they are not ideal for PV applications, where PV sources have variable output due to environmental changes/partial shading conditions. The second approach identifies unequal magnitude sources and produces eleven levels of output, but it is not a completely asymmetric design since V<sub>2</sub> and V<sub>3</sub> appear symmetrical in nature. The third method of selecting dc sources is the binary method, in which the input dc sources vary from one another and is ideal for PV applications. Multilevel inverters operate well with minimal switching and conduction losses at higher voltage levels; hence, the binary method was chosen for this study. As a result, the following voltages have been selected for 15-level output.

$$V_1 = V_{dc}, V_2 = 2V_{dc}, V_3 = 4V_{dc}$$

Multilevel inverters may function in an asymmetrical manner using this approach, which is suited for fluctuating solar irradiation. For the numerous levels of output step voltages, as shown in Table 2, the switching sequence is described for each voltage level from  $+7V_{dc}$  to  $-7V_{dc}$ , along with the '0' voltage level. During the auxiliary circuit's +ve half cycle of output voltage, the switches S<sub>4</sub> and S<sub>5</sub> operate consistently, while the switches S<sub>6</sub> and S<sub>7</sub> operate during the -ve half cycle. The load gets short-circuited with switches S<sub>4</sub> and S<sub>6</sub> turned ON or with switches S<sub>5</sub> and S<sub>7</sub> turned ON, then the output level becomes to 0 V. By switching the main and auxiliary circuits according to Table 2, the inverter provides 15 output voltage levels.

Table 2. ON switches, power flow paths, and corresponding output levels of proposed 15-level inverter.

| Switching Operation                                                                | Power Flow                                                                                                                                                     | Output Voltage    |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> & S <sub>5</sub> | $V_1{}^+ \rightarrow S_1 \rightarrow V_2 \rightarrow S_2 \rightarrow V_3 \rightarrow S_3 \rightarrow S_4 \rightarrow Load \rightarrow S_5 \rightarrow V_1{}^-$ | +7V <sub>dc</sub> |

| S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> & S <sub>5</sub>                  | $V_2{}^+ \rightarrow S_2 \rightarrow V_3 \rightarrow S_3 \rightarrow S_4 \rightarrow Load \rightarrow S_5 \rightarrow D_1 \rightarrow V_2{}^-$                 | +6V <sub>dc</sub> |

| S <sub>1</sub> , S <sub>3</sub> , S <sub>4</sub> & S <sub>5</sub>                  | $V_1{}^+ \rightarrow S_1 \rightarrow D_2 \rightarrow V_3 \rightarrow S_3 \rightarrow S_4 \rightarrow Load \rightarrow S_5 \rightarrow V_1{}^-$                 | +5V <sub>dc</sub> |

| S <sub>3</sub> , S <sub>4</sub> & S <sub>5</sub>                                   | $V_3{}^+ \rightarrow S_3 \rightarrow S_4 \rightarrow Load \rightarrow S_5 \rightarrow D_1 \rightarrow D_2 \rightarrow V_3{}^-$                                 | +4V <sub>dc</sub> |

| S <sub>1</sub> , S <sub>2</sub> , S <sub>4</sub> & S <sub>5</sub>                  | $V_1{}^+ \rightarrow S_1 \rightarrow V_2 \rightarrow S_2 \rightarrow D_3 \rightarrow S_4 \rightarrow Load \rightarrow S_5 \rightarrow V_1{}^-$                 | +3V <sub>dc</sub> |

| S <sub>2</sub> , S <sub>4</sub> & S <sub>5</sub>                                   | $V_2{}^+ \rightarrow S_2 \rightarrow D_3 \rightarrow S_4 \rightarrow \text{Load} \rightarrow S_5 \rightarrow D_1 \rightarrow V_2{}^-$                          | +2V <sub>dc</sub> |

| S <sub>1</sub> , S <sub>4</sub> & S <sub>5</sub>                                   | $V_1{}^+ \rightarrow S_1 \rightarrow D_2 \rightarrow D_3 \rightarrow S_4 \rightarrow Load \rightarrow S_5 \rightarrow V_1{}^-$                                 | +V <sub>dc</sub>  |

| S <sub>4</sub> & S <sub>6 (or)</sub> S <sub>5</sub> & S <sub>7</sub>               | $S_4 \rightarrow \text{Load} \rightarrow S_6 \rightarrow S_4 \text{ (or) } S_5 \rightarrow \text{Load} \rightarrow S_7 \rightarrow S_5$                        | 0                 |

| S <sub>1</sub> , S <sub>6</sub> & S <sub>7</sub>                                   | $V_1{}^+ \rightarrow S_1 \rightarrow D_2 \rightarrow D_3 \rightarrow S_6 \rightarrow \text{Load} \rightarrow S_7 \rightarrow V_1{}^-$                          | -V <sub>dc</sub>  |

| S <sub>2</sub> , S <sub>6</sub> & S <sub>7</sub>                                   | $V_2{}^+ \rightarrow S_2 \rightarrow D_3 \rightarrow S_6 \rightarrow \text{Load} \rightarrow S_7 \rightarrow D_1 \rightarrow V_2{}^-$                          | $-2V_{dc}$        |

| S <sub>1</sub> , S <sub>2</sub> , S <sub>6</sub> & S <sub>7</sub>                  | $V_1{}^+ \rightarrow S_1 \rightarrow V_2 \rightarrow S_2 \rightarrow D_3 \rightarrow S_6 \rightarrow Load \rightarrow S_7 \rightarrow V_1{}^-$                 | -3V <sub>dc</sub> |

| S <sub>3</sub> , S <sub>6</sub> & S <sub>7</sub>                                   | $V_3{}^+ \rightarrow S_3 \rightarrow S_6 \rightarrow Load \rightarrow S_7 \rightarrow D_1 \rightarrow D_2 \rightarrow V_3{}^-$                                 | $-4V_{dc}$        |

| S <sub>1</sub> , S <sub>3</sub> , S <sub>6</sub> & S <sub>7</sub>                  | $V_1{}^+ \rightarrow S_1 \rightarrow D_2 \rightarrow V_3 \rightarrow S_3 \rightarrow S_6 \rightarrow Load \rightarrow S_7 \rightarrow V_1{}^-$                 | $-5V_{dc}$        |

| S <sub>2</sub> , S <sub>3</sub> , S <sub>6</sub> & S <sub>7</sub>                  | $V_2{}^+ \rightarrow S_2 \rightarrow V_3 \rightarrow S_3 \rightarrow S_6 \rightarrow Load \rightarrow S_7 \rightarrow D_1 \rightarrow V_2{}^-$                 | -6V <sub>dc</sub> |

| S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> , S <sub>6</sub> & S <sub>7</sub> | $V_1{}^+ \rightarrow S_1 \rightarrow V_2 \rightarrow S_2 \rightarrow V_3 \rightarrow S_3 \rightarrow S_6 \rightarrow Load \rightarrow S_7 \rightarrow V_1{}^-$ | -7V <sub>dc</sub> |

# 3. Grid Integration Methodology of Solar PV System

# 3.1. Two-Stage Grid-Connected SPV System

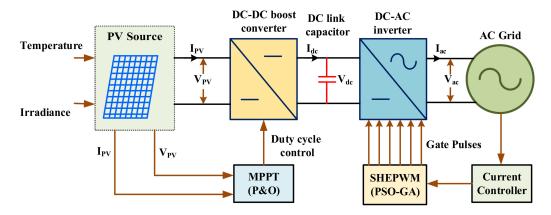

Figure 2 illustrates the suggested grid-connected solar photovoltaic system. In this system, the photovoltaic energy is integrated into the single-phase grid. The design model comprises a photovoltaic (PV) source, a boost converter, and an asymmetric inverter, among other components. PV cells are typically constructed of semiconductor materials and are capable of producing voltages ranging from 0.5 to 0.8 volts, which are quite low for real-time applications. To boost the voltage rating of a PV module, numerous PV cells (36 to 72) are coupled together in series to build a PV module. Connecting these PV modules in series and parallel to construct a larger array subsequently results in the formation of a photovoltaic (PV) panel. When PV modules are connected in series, the voltage rating of the PV module is increased; when PV modules are connected in parallel, the current rating of the PV module is increased.

Figure 2. Proposed two-stage grid-connected SPV system.

The PV panel is responsible for supplying power to the boost converter. The boost converter, using the P & O MPPT algorithm, takes the highest power possible from the PV panel, which is then delivered to the inverter input using a dc-link capacitor. The dc-link capacitor helps to stabilize the dc-link voltage of a grid-connected system, which results in an increase in the voltage injected into the power grid. When it comes to the grid system, the inverter is a critical component, and it is linked to it at the point of common coupling (PCC) [20]. The grid is interfaced with the proposed 15-level inverter, which can supply maximum power throughout the day. This can be achieved by optimal converter, inverter and control circuit to enhance the overall system efficiency.

#### 3.2. Implementation of Proposed Grid-Connected SPV System

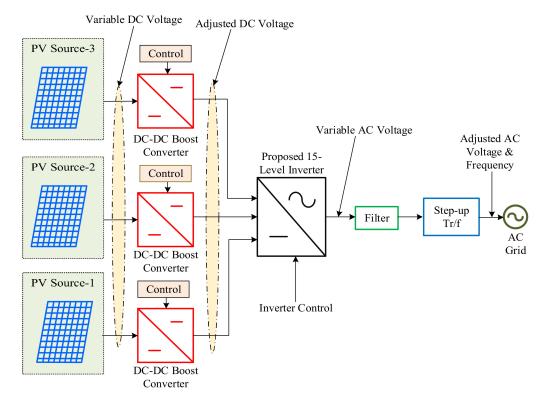

Figure 3 depicts the proposed grid-connected photovoltaic system's functioning block diagram. PV panels (or arrays), power converters, and the ac grid are the three essential components of the SPV system. Because PV arrays produce dc power, power electronic equipment must convert dc power into ac power. The grid-connected SPV system utilizes three PV sources for the three inputs of the proposed 15-level inverter. The dc power generated from three PV sources is fed to three separate boost converters controlled by the P & O MPPT algorithm to meet the input voltage requirements of the 15-level inverter. The inverter converts direct solar power into ac power and is crucial to operating an SPV system, although it is housed in sophisticated circuitry. The essential inverter features are the ability to work across a wide range of currents and voltages, output frequency, voltage regulation, and supply ac power with excellent power quality. The key innovation is the grid integration of a reduced switch 15-level inverter with solar photovoltaic systems. The inverter is controlled by the SHEPWM using a hybrid PSO-GA optimization algorithm, considering the grid voltage and grid currents are the reference parameters. In several locations worldwide, standalone power generating systems have been built without any

grid connection. The grid-connected system is thus a practical compromise for high power requirements and the erratic quality of renewable energy [21].

Figure 3. Schematic diagram of proposed grid-connected SPV system.

The passive LCL filter then incorporates the suggested topology with the grid-connected system to further minimize the THD and improve waveform quality as per the grid requirements. The process of the proposed method is tested, and the selective test findings are presented in this chapter under standard test conditions.

## 3.2.1. Modelling of SPV Sources

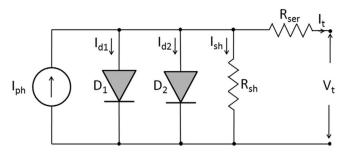

A PV module is a power generation unit of the SPV system. The amount of power that may be generated by photovoltaic modules has nonlinear features for both their I-V and P-V curves and is mostly dependent on the temperature and the level of irradiation. As a result, it is necessary to build a PV module in order to investigate its specific design, function, and the factors that contribute to the decrease in PV production. There are two major PV system design categories: single diode type and two diode type. Single diode type design is quite simple, but it does not consider the recombination of losses (constant ideality factor '1') in the depletion layer. The two-diode type is efficient and frequently used to match an actual curve, with the second diode's denominator of the exponential term's argument comprising an ideality factor of '2'. Although one diode modelling is highly prevalent for PV modelling, it has the following downsides.

- Temperature variations have a significant impact on photovoltaic performance. It prevents diffusion loss in the depletion region of PV cells.

- The precision of the measurement was determined at low irradiance, in fact, at an open circuit. (V<sub>oc</sub>)

The two-diode model improves PV system accuracy, curve fitting, and eliminates one-diode model annoyance. Figure 4 shows the two-diode model's equivalent circuit. It has an  $I_{PV}$  and two diodes. In actuality, there are two extra series ( $R_{ser}$ ) and parallel resistances ( $R_{sh}$ ). Solar cells aren't ideal conductors; hence, they have series resistance. Any change in Rser affects PV cell output.

Figure 4. A two-diode model of photovoltaic cell.

The design equations of PV cell are represented as follows;

$$I = I_{Ph} - \mu_1 - \mu_2 - (V_S + 1 * R_{ser}) / R_{sh}$$

(1)

where,

$$\mu_1 = I_{d1} * \left( e^{\frac{V_S + 1 * R_{Ser}}{\varepsilon_1 * V_I}} - 1 \right)$$

(2)

$$\mu_2 = I_{d2} * \left( e^{\frac{V_S + 1 * R_{Ser}}{\epsilon_2 * V_t}} - 1 \right)$$

(3)

Here,

$\mu_1$  = Current through diode D<sub>1</sub>,  $\mu_2$  = Current through diode D<sub>2</sub>,  $I_{d1}$  = Saturation current of diode D<sub>1</sub>,  $I_{d2}$  = Saturation current of diode D<sub>2</sub>,  $\varepsilon_1$  = Emission coefficient of diode D<sub>1</sub>,  $\varepsilon_2$  = Emission coefficient of diode D<sub>2</sub>,  $V_s$  = PV cell voltage,  $V_t$  = Terminal voltage of PV cell,  $I_{ph}$  = Current produced in a photovoltaic cell.

Therefore, the current produced by the PV cell is represented in Equation (4).

$$I_{ph} = I_{\sigma} * (I_{so} / I_{\sigma 0}) \tag{4}$$

where,

$I_{so}$  = Solar current,  $I_{\sigma}$  &  $I_{\sigma 0}$  = Irradiance currents.

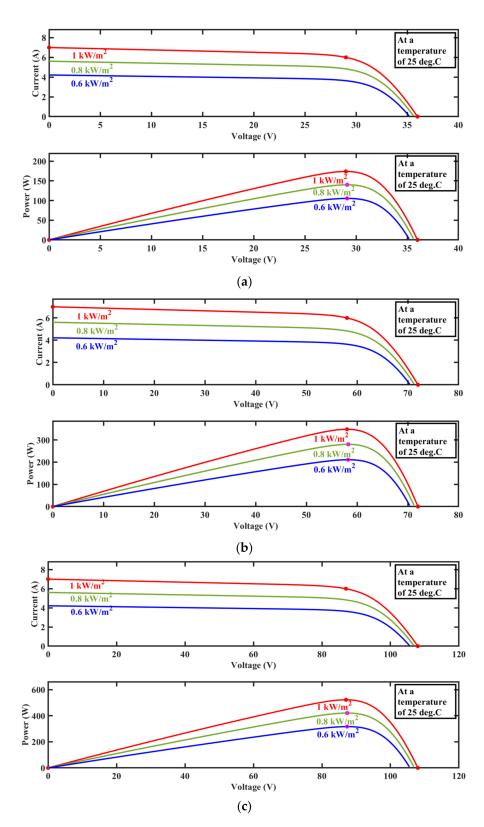

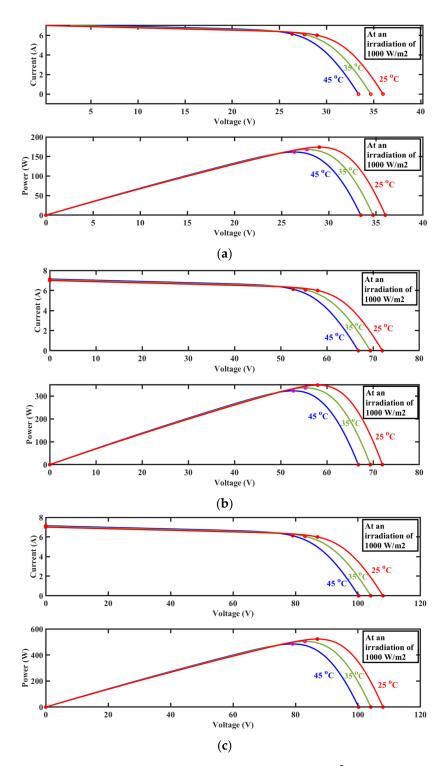

A solar panel is made up of 24 photovoltaic (PV) cells. Each photovoltaic cell has an open-circuit voltage of 0.5 V. At 1000 W/m<sup>2</sup> and 25 °C, these solar PV cells are connected in series to generate 12 V. The choice PV sources for the proposed grid-connected system are PV<sub>1</sub> = 48 V, PV<sub>2</sub> = 96 V, and PV<sub>3</sub> = 192 V to get a peak value of 336 V. Therefore, four 12 V modules are connected in series to generate a voltage of 48 V at the solar PV system's output. Similarly, the 96 V output can be obtained by series connection eight 12 V modules, and series connection sixteen 12 V modules get 192 V output. The characteristics I-V and P-V of the PV<sub>1</sub>, PV<sub>2</sub> and PV<sub>3</sub> are presented in Figure 5 at a constant temperature of 25 °C for variable irradiance. The characteristics I-V and P-V of photovoltaic cell is illustrated in Figure 6 at constant (1000 W/m<sup>2</sup>) irradiance with varying temperature.

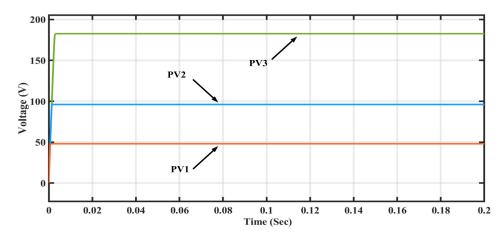

The three input sources required for the 15-level inverter are illustrated in Figure 7. These sources are dissimilar and asymmetric in nature with  $P_{V1} = 48$  V,  $P_{V2} = 96$  V, and  $P_{V3} = 192$  V.

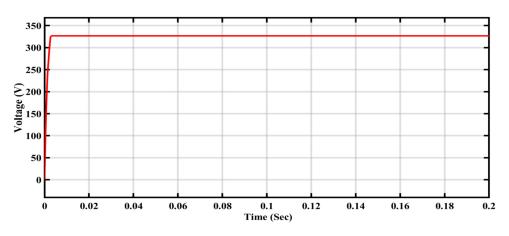

The total value of the dc-link voltages combing the three PV sources is illustrated in Figure 8. The simulated results give a peak value of 336 V.

**Figure 5.** I-V & P-V curves at a constant temperature of 25 °C with variable irradiances of 1000 W/m<sup>2</sup>, 800 W/m<sup>2</sup> and 600 W/m<sup>2</sup> (a)  $PV_1$ , (b)  $PV_2$  and (c)  $PV_3$ .

**Figure 6.** I-V & P-V curves at constant irradiation (1000 W/m<sup>2</sup>) with variable temperatures of 25 °C, 35 °C and 45 °C (**a**)  $PV_1$ , (**b**)  $PV_2$  and (**c**)  $PV_3$ .

Figure 7. Asymmetric PV sources for the input of proposed 15-level inverter.

Figure 8. Total dc-link voltage of the three PV sources.

# 3.2.2. Boost Converter Design for PV System

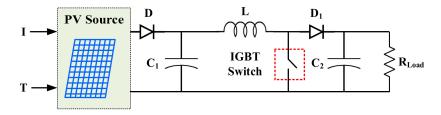

The dc-dc conversion is critical in photovoltaic systems since the voltage generated by the PV panels does not meet the load requirements. It is necessary to employ a boost converter in order to increase the voltage of the PV system. The boost converter gives maximum power to the proposed 15-level inverter throughout this operation. The typical design model of the boost converter (dc-dc) is illustrated in Figure 9. It includes the diode, IGBT switch, inductor, and capacitor. The purpose of the capacitor is to remove voltage disturbances in the output.

Figure 9. PV connected dc-dc boost converter.

The inductor and capacitor are two critical components of a dc-dc converter that must be modelled to obtain the required output voltage. The inductor and capacitor are designed using fundamental mathematics.

$$L = \frac{V_{in} * (V_{out} - V_{in})}{\Delta I_L * f_s * V_{out}}$$

(5)

$$C = \frac{I_{out} * \delta}{f_s * \Delta V_C} \tag{6}$$

where,

$\Delta I_L$  = Inductor ripple current  $\Delta V_C$  = Capacitor ripple voltage

$\delta$  = Duty cycle =  $\frac{V_0 - V_s}{V_0}$  $f_s$  = Switching frequency.

$J_s = 5$  when might nequency

The values of inductor ripple current and capacitor ripple voltages are calculated using Equations (7) and (8), respectively.

$$\Delta I_L = (2\% \ to \ 4\%) * I_{out(max)} * \frac{V_{out}}{V_{in}}$$

(7)

$$\Delta V_{C} = (2\% \ to \ 4\%) * V_{out(max)} * \frac{I_{out}}{I_{in}}$$

(8)

where,  $V_{out}$  is the maximum output voltage,  $V_{in}$  is the input voltage,  $I_{in}$  is the input current,  $I_{out(max)}$  is the maximum output current.

There are three separate boost converters used for the three independent PV sources to boost the PV voltage as per the requirement of inverter input. These boost converters are employed with individual P & O MPPT controllers for the control of the duty cycle.

3.2.3. Simulation of PV Sources at an Irradiance of  $600 \text{ W/m}^2$  at a Temperature of 35 °C

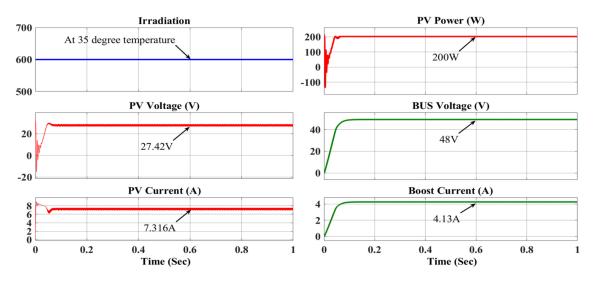

In this case, the PV sources operated at practical test conditions with the irradiance of  $600 \text{ W/m}^2$  and temperature of  $35 \degree$ C.

At this test condition,  $PV_1$  produces a power of 200 W with a voltage of 27.42 V and a current of 7.316 A. This voltage level is not sufficient for input-1 of the proposed inverter.  $PV_1$  voltage is increased from 27.42 V to 48 V with the help of a boost converter, and the corresponding output current is 4.13 A, as shown in Figure 10.

**Figure 10.** PV measurements, boost voltage, current, and PV output power at an irradiance of  $600 \text{ W/m}^2$  and temperature of 35 °C for PV<sub>1</sub>.

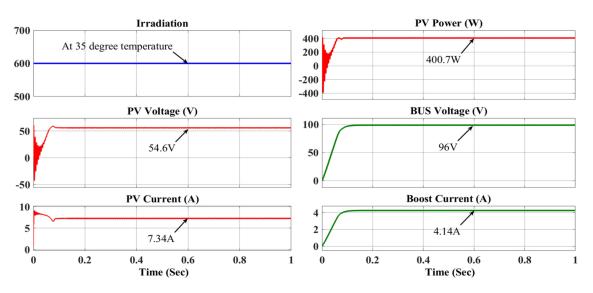

$PV_2$  produces a power of 400.7 W with a voltage of 54.6 V at 7.34 A of current. But the inverter input '2' is required 96 V. Hence, the  $PV_2$  voltage increased to 96 V from 54.6 V using a boost converter, giving an output current of 4.14 A, as shown in Figure 11.

**Figure 11.** PV measurements, boost voltage, current, and PV output power at an irradiance of  $600 \text{ W/m}^2$  and temperature of 35 °C for PV<sub>2</sub>.

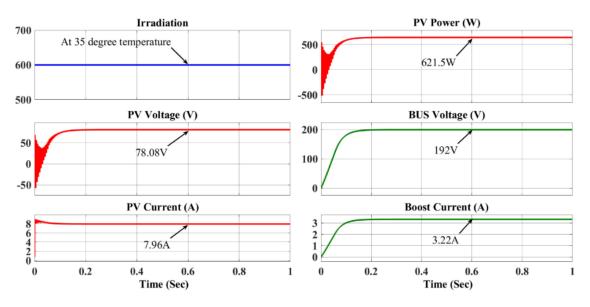

Similarly,  $PV_3$  produces a power of 621.5 W with a voltage of 78.08 V at 7.96 A of current. But the inverter input '3' is required 192 V. Hence, the  $PV_3$  voltage increased to 192 V from 78.08 V using a boost converter, giving an output current of 3.22 A, as shown in Figure 12.

**Figure 12.** PV measurements, boost voltage, current, and PV output Power at an irradiance of  $600 \text{ W/m}^2$  and temperature of  $35 \degree \text{C}$  for PV<sub>3</sub>.

Although, for analyzing the performance of the proposed inverter on practical operating test conditions of the PV system, an irradiance of  $600 \text{ W/m}^2$  and a temperature of 35 °C is considered. The control of grid parameters under these test conditions is described in the following sections.

# 3.2.4. Design of LCL Filter

In most cases, the filter is connected to both the inverter and the grid. The filter performs three essential functions: it reduces high-frequency noise, shields the transient, and converts the voltage to a current source. The L-type, LC-type, and LCL-type filters are the three primary filters used in grid-connected networks. The LCL filter is used to link the

inverter with the grid in this application. In addition, the inverter operation is based on triggering of power switches and since the switches need gating pulses. Due to switching of the devices, the output current may include large harmonic distortions that aim to degrade the power quality of the power system. To remove the switching harmonics in the output of the inverter, an LCL filter is designed in this study. The criteria for calculating the model parameters are listed below.

The inductor at the inverter side is modelled with the Equation (9).

$$L_i = \frac{V_{dc \ link}}{8 \ f_s \ \Delta I_L} \tag{9}$$

where,

$\Delta I_L$  = inductor ripple current

$f_s$  = Switching frequency = 1000 Hz

$V_{dc \ link} = DC \ link \ voltage = 336 \ V.$

Also, the inductor ripple current is evaluated using Equation (10)

$$\Delta I_L = 0.1 * \frac{\sqrt{2} P}{V_{ph \ (grid)}} \tag{10}$$

where,

P = Active power of the grid = 1250 W

$V_{ph}(grid)$  = Phase voltage of the grid = 240 V.

The grid side inductor can be calculated using Equation (11)

$$L_g = 0.6 * L_i \tag{11}$$

The capacitance value is determined, considering 5% of the base capacitance using the Equation (12).

$$C_f = 0.05 C_b$$

(12)

where,

$$C_b = \frac{P}{\omega_{grid} * V_{grid}^2} \tag{13}$$

$\omega_{grid}$  = Angular frequency =  $2\pi f$  = 314.2 rad/s.  $V_{grid}$  = Phase voltage of the grid = 240 V

# 4. Control Methodology of Proposed Grid-Connected PV System

Asymmetric PV sources feed the input dc supply of the proposed inverter. The current into the grid is injected by using an adaptive PI controller. For the power factor to be maintained at unity, the current injection must be sinusoidal and in phase with the grid voltage [22]. Keeping the dc voltages generated by the PV array steady throughout the day is essential for producing sinusoidal current.

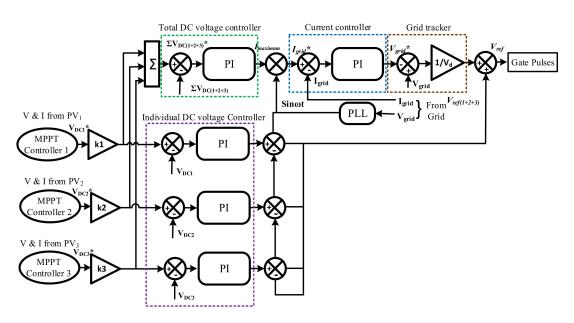

There are two different control strategies used for voltage control with PI controllers for injecting the current into the grid. One PI controller regulates the total dc voltage produced by the three PV sources and the other PI controller regulates the voltage of individual PV sources. Because asymmetrical PV inputs are supplied to the inverter through dc links, separate dc-dc boost converters with MPPT controllers are constructed for each PV source in the proposed configuration. Under various operating situations, these independent MPPT controllers keep the dc-link voltages in the 1:2:4 ratio. To produce the reference PV voltages such as  $V_{dc1}^*$ ,  $V_{dc2}^*$  and  $V_{dc3}^*$  a P & O based MPPT algorithm is used.

Figure 13 illustrates the suggested grid-connected inverter's control approach. It consists of a voltage controller, current controller, and a grid tracker. This controls the three separate dc sources and keeps their voltages in the proper ratio (1:2:4) to meet the grid codes.

**Figure 13.** Grid-connected controller for proposed 15-level inverter [23]. '\*' refrers to the reference/base values in the figure.

# 4.1. Total dc Voltage Control

Figure 13 depicts the closed-loop voltage controller used to produce the required voltage in the dc link, which is comparable to the appropriate reference voltage for the specified irradiation level. The reference voltages  $(V_{dc1}^* + V_{dc2}^* + V_{dc3}^*)$  are compared with the actual voltages  $(V_{dc1} + V_{dc2} + V_{dc3})$ , to regulate the total dc voltage of the PV system and the corresponding error is processed through the PI controller. The PI controller consists of two gains like Kpv1, Kpi1, which are tuned by a hybrid PSO-GA optimization control to get the maximum value of reference current of the grid (I<sub>max</sub>). A PLL generates the sinusoidal reference current (I<sup>\*</sup><sub>g</sub>) of the grid for the grid-connected system.

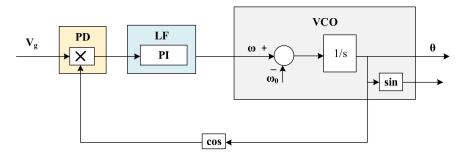

The PLL is usually employed for grid integration. The typical model of PLL is illustrated in Figure 14. The components of the PLL are a voltage-controlled oscillator, a low-pass filter controlled by a PI controller, and a phase detector. The phase detector block is responsible for detecting the phase difference between the input and feedback signals. The input of the phase detector block is provided by Equation (14).

$$V_{\rm G}(t) = \sqrt{2} \, V_{\rm grid \ (rms)} * \sin(\omega_{\rm g} t + \phi) \tag{14}$$

Figure 14. A typical model of single-phase PLL.

The output obtained from the phase detector block is represented in Equation (15).

$$V_{PD}(t) = \sqrt{2} V_{grid(rms)} \sin(\theta_g) \cos(\hat{\theta})$$

(15)

15 of 25

The Equation (15) further represented as,

$$V_{PD}(t) = \frac{\sqrt{2}}{2} V_{grid(rms)} \left( \sin \left[ \begin{pmatrix} (\omega_g - \hat{\omega})t + \\ (\varphi_g - \hat{\varphi}) \end{pmatrix} + \sin \left[ \begin{pmatrix} (\omega_g + \hat{\omega})t + \\ (\varphi_g + \hat{\varphi}) \end{pmatrix} \right] \right)$$

(16)

There are two components in Equation (16) (high frequency and low frequency). When the phase detector's output is transmitted through the PI-based LF block, the low-pass filter removes the high-frequency component, and the frequency component is retrieved at the LF block's output.

$$V_{LF}(t) = \frac{\sqrt{2}}{2} V_{grid(rms)} \left( \sin\left[ \left( \omega_g - \hat{\omega} \right) t + \left( \varphi_g - \hat{\varphi} \right) \right] \right)$$

(17)

The PI controller will provide appropriate frequency. As  $\omega_g = \hat{\omega}_g$  and  $\varphi_g = \hat{\varphi}$ , the output signal from the LF block indicated in Equation (17) tends to zero under the steady condition. By using the grid voltage as an input, the output phase signal is locked.

#### 4.2. Grid Voltage and Grid Current Control

To produce the reference current needed by the grid, a PLL (phased lock loop) is used. The measured value (I<sub>grid</sub>) is compared to the reference grid current I<sub>grid</sub>\*, and the error acquired is sent into the PI current controller. The grid current is maximized by changing the gains (K<sub>p</sub>, K<sub>i</sub>) of the PI controller. The current controller provides a reference signal  $V_{k^*}$  during stable operating conditions, and the reference inverter voltage is obtained by subtracting the grid voltage signal from the reference inverter voltage. As a result, the inverter reference voltage changes in line with the grid voltage. When the grid voltage drops, the difference  $V_{grid} - V_{k^*}$  drops as well, and the reference voltage of the inverter drops as well with the grid tracker. The grid tracker's output can be scaled to create a part of the inverter's reference voltage.

#### 4.3. Individual dc Voltage Control

For a 15-level asymmetric inverter, three unequal dc sources  $V_{dc1}$ ,  $V_{dc2}$ ,  $V_{dc3}$ , are used under various atmospheric conditions. In addition to the total dc voltage control, there exist two other voltage controllers, which are required to maintain the  $V_{dc2}$ ,  $V_{dc3}$  voltages at their reference voltages  $V_{dc2}^*$  and  $V_{dc3}^*$ . Grid frequency is generated by adding the sine component of the grid frequency (obtained via PLL) to both the total voltage controller and individual voltage controller outputs to form the reference signal for the inverter, which is then used to generate the PWM signals.

#### 4.4. SHEPWM Control for Grid-Connected PV System

The selective harmonic elimination technique is used to establish the switching pulses to the inverter and to provide a waveform that is free of harmonics. Lower order harmonics are reduced by using the SHEPWM method, resulting in a smaller filter size for the system [24]. This method uses quarter-wave symmetry to cut down on computations. Hence the switching angles are computed between  $0^{\circ}$  and  $90^{\circ}$  ( $0^{\circ} \le \alpha \le 90^{\circ}$ ). The even-order harmonics in the Fourier expansion are '0' because of the odd symmetry of the quarter-wave.

According to the following formula, the Fourier series is generated from the output of the inverter,

$$V_0 = a_0 + \sum_{n=1}^{\infty} A_n \cos(n\omega t) + \sum_{n=1}^{\infty} B_n \sin(n\omega t)$$

(18)

The even harmonics become zero in the output of the inverter because the analysis is considered the quarter-wave symmetry. Therefore, the Equation (18) can be written as,

$$V_0 = \sum_{n=1}^{\infty} B_n \sin(n\omega t)$$

(19)

where,

$$B_n = \frac{1}{\pi} \int_{0}^{2\pi} V_{PV} \sin(n\omega t) d\omega t$$

(20)

Generally, the output of the multilevel inverter is the stepped wave; hence the Equation (20) is represented as,

$$B_n = \frac{2}{\pi} \int_0^{\pi} V_{PV} \sin(n\omega t) d\omega t$$

(21)

On integrating the Equation (21), the resultant  $B_n$  can be written as

$$B_n = \frac{4V_{PV}}{k\pi} \sum_{i}^{z} \cos(k\alpha_i)$$

(22)

Here, k represents the harmonic order, z represents the number of switching angles for the quarter-wave,  $\alpha_i$  Represents the i<sup>th</sup> switching angle, and V<sub>PV</sub> represents the voltage from the PV array. The number of triggering angles for an N-level output is represented in Equation (23).

$$Z = \frac{N-1}{2} \tag{23}$$

where N represents output voltage levels of the inverter, therefore, from Equation (23), the switching angles needed to produce the 15 voltage levels is '7'. Hence, there are six nonlinear equations (excluding fundamental) to be solved for obtaining the seven switching angles of the 15-level inverter. These must fulfil the below constrain for the quarter-wave approximation.

$$\alpha_1 < \alpha_2 < \alpha_3 < \alpha_4 < \alpha_5 < \alpha_6 < \alpha_7 < \frac{\pi}{2} \tag{24}$$

The fundamental voltage component always is set to modulation index  $(M_i)$ , defined in Equation (25)

$$M_i = \frac{V}{V_{PV}} \tag{25}$$

where *V* is the magnitude of the fundamental component,  $V_{PV}$  represents the DC voltages fed from the SPV system. Therefore, the nonlinear equations generated from Equation (22) is solved using Particle Swarm Optimization (PSO), Harris Hawk Optimization (HHO) and a hybrid PSOGA algorithm, and the corresponding switching angles are stored in memory lookup tables for several modulation indexes. These switching angles are retrieved from the lookup tables for a given modulation index set by the dc-link voltage. Further, these switching angles trigger the seven switches in the proposed inverter to produce the corresponding voltage and currents.

#### 5. Results and Discussion

#### 5.1. Implementation of PSO-PI Controller for GCSPV System

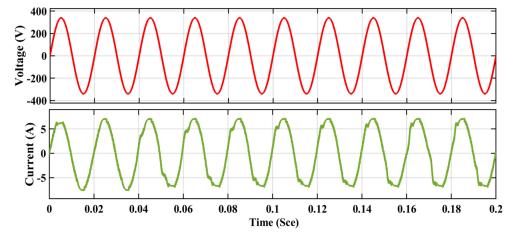

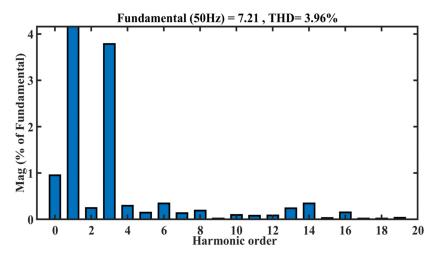

The PSO variables necessary to configure the PI controllers of the total dc voltage control block and the current control block are shown in Table 3. The integral time absolute error is selected as the fitness function, and the PSO algorithm gives the gains of the two PI controllers while minimizing the fitness function. After 114 iterations, the best gain parameters for voltage gains of PI ( $K_{Vp}$ ,  $K_{Vi}$ ) and current gains of PI ( $K_{Cp}$ ,  $K_{Ci}$ ) controllers are achieved. The PSO tuned PI gains of the voltage and current controllers are given as  $K_{Vp} = 0.51$ ,  $K_{Vi} = 0.209$ ,  $K_{Cp} = 0.87$ ,  $K_{Ci} = 0.341$ , respectively. A peak voltage of 336.8V and a peak current of 6.89A are shown in Figure 15, which is in phase with the grid voltage when utilizing PSO-PI control. Figure 16 shows the PSO-PI controller's FFT analysis of the grid current waveform, which represents the overall harmonic distortion (3.96%).

| Values |                              |

|--------|------------------------------|

| 50     |                              |

| 0.5    |                              |

| 1.25   |                              |

| 1      |                              |

| 10     |                              |

| 200    |                              |

|        | 50<br>0.5<br>1.25<br>1<br>10 |

Table 3. Parameters & specifications of PSO.

\_

Figure 15. Grid voltage and grid current waveforms with PSO-PI controller.

Figure 16. THD analysis of grid current waveform with PSO-PI controller.

## 5.2. Implementation of HHO-PI Controller for GCSPV System

For the proposed control system's total voltage controller block and current controller block, the HHO technique allows use of the integral time absolute error as the fitness function to determine the parameters of the PI controller, which is implemented as a PI controller. Equations (26) and (27) represents integral time absolute errors used as the fitness functions of HHO for tuning the gain values of total voltage control and current control blocks, respectively. The parameters and specifications involved in tuning the PI controller using the HHO algorithm are represented in Table 4.

$$ITAE = \int t * |e(t)| dt = \int_{0}^{t} |V_{DCref} - V_{DCact}(t)| * t . dt$$

(26)

$$ITAE = \int t * |e(t)| dt = \int_{0}^{t} \left| I_{GRIDref} - I_{GRIDact}(t) \right| * t . dt$$

(27)

Table 4. Specifications and parameters of HHO.

| Parameters                        | Values                                                    |

|-----------------------------------|-----------------------------------------------------------|

| Number of Hawks' N'               | 30                                                        |

| Random generations r1, r2, r3, r4 | In the range of [0, 1]                                    |

| Number of search agents           | 7                                                         |

| Initial energy (E <sub>0</sub> )  | [–1, 1], [–1, 0] loosing energy,<br>[0, 1] raising energy |

| Convergence probability 'r'       | 0.5                                                       |

| Number of iterations              | 200                                                       |

HHO uses 75 iterations to get the most acceptable voltage and current control gains of the PI controller. The optimum values of gain parameters are  $K_{Vp} = 0.81$ ,  $K_{Vi} = 0.11$ ,  $K_{Cp} = 0.91$ ,  $K_{Ci} = 0.089$  using HHO-PI controller for GCSPV system.

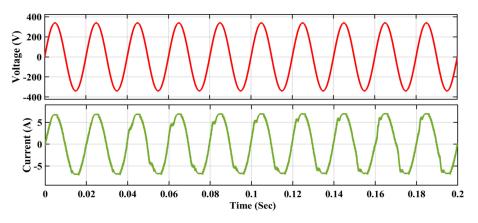

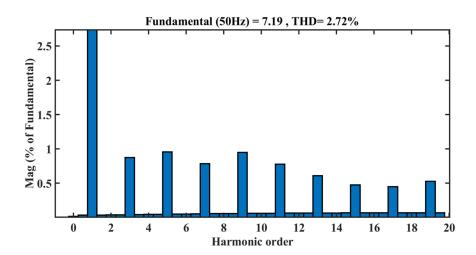

Figure 17 shows the grid voltage waveform and grid current waveform with a peak voltage of 336.7 V and peak current of 6.91 A, using HHO-PI control. The FFT analysis of grid current waveform, representing the total harmonic distortion (2.72%), is shown in Figure 18 using the HHO-PI controller.

Figure 17. Grid voltage and grid current waveforms with HHO-PI controller.

Figure 18. THD analysis of grid current waveform with HHO-PI controller.

# 5.3. Implementation of a Hybrid PSOGA-PI Controller for GCSPV System

To overcome the problems of local minima and to improve the search accuracy hybrid PSOGA is implemented. The hybrid algorithm consists of the following stages.

Stage A: PSO parameters initialization.

Stage B: GA parameters initialization.

**Stage C:** At each case determine the GA optimal solution by arranging the PSO parameters.

Stage D: Execute the GA crossovers and mutation at GA optimal solution.

**Stage E:** Search for the best solution for both GA and PSO until the termination criteria. **Stage F:** If the termination criteria not reached go to Stage C.

**Stage G:** If the generations are segregated according to the iterative items N, then the selection of P individuals should be based on their objective from the various sub-systems. When utilizing this strategy, the vector is improved by particle swarm optimization (PSO), and the decision vectors are updated through the application of genetic operators using the genetic algorithm (GA). With the introduction of genetic operators, such as crossover and mutation, into the PSO algorithm, it has been possible to further improve the balance between exploration and exploitation capability. In this case, the integral time absolute error is selected as the fitness function. In order to compute the gains of the two PI controllers while keeping the fitness function as small as possible, the PSO algorithm is utilized. The fitness function for the voltage controller of PI is represented by Equation (26) and the fitness function for the current controller of PI is represented by Equation (27), respectively. The optimum values of gain parameters are  $K_{Vp} = 0.96$ ,  $K_{Vi} = 0.089$ ,  $K_{Cp} = 0.94$ ,  $K_{Ci} = 0.096$  using PSOGA-PI controller for GCSPV system. The specifications and parameters used in hybrid PSOGA based PI tuning is presented in Table 5.

Table 5. Specifications and parameters of hybrid PSOGA.

| Parameters           | Values         |

|----------------------|----------------|

| Population size from | 50             |

| Crossover fraction   | 0.8 as default |

| Number of iterations | 200            |

| Mutation rate        | 0.006          |

| Cognitive factor, C1 | 0.5            |

| Social factor, C2    | 1.25           |

| Inertia Weight, W    | 1              |

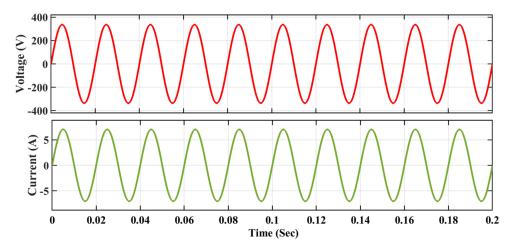

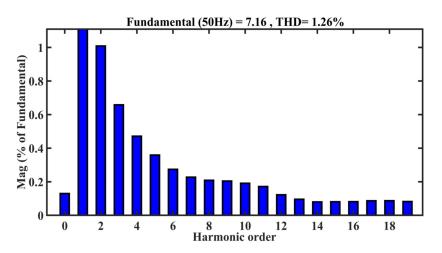

Figure 19 depicts the grid voltage and grid current waveforms, with a peak voltage of 336.7 V and a peak current of 6.96 A, respectively, when the PSOGA-PI control is used to regulate the grid voltage and grid current. Figure 20 depicts the results of an FFT analysis of the grid current waveform, which represents the overall harmonic distortion (1.26%) and was performed using the PSOGA-PI controller.

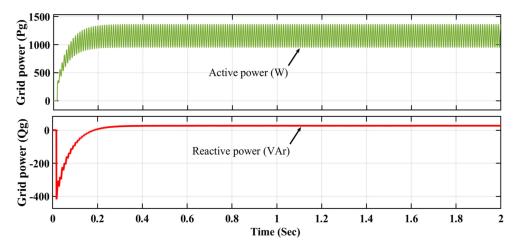

During the grid's steady-state operation, the inverter is responsible for supplying active electricity to the grid. The suggested inverter injects current into the grid at a rate that is in phase with the grid voltage in order to preserve unity power factor. When the grid is operating in steady state, the active and reactive power are measured, and the associated waveforms of the system are shown in Figure 21. According to the measurements, the active and reactive powers are 1171 W and 26.09 VAr, respectively.

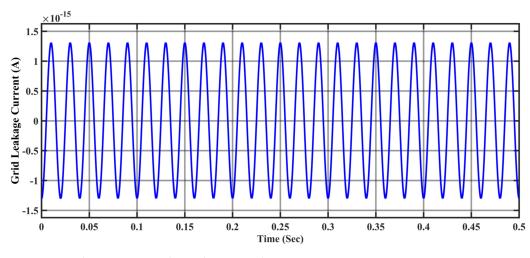

Figure 22 depicts the leakage current measured in the grid, which is in the order of  $1.25 \times 10^{-15}$  A (very low). The leakage current in the grid is very low and insignificant. Thus, this research concludes that the grid's performance is good with the suggested inverter and control method. The leakage current is affected by the driver circuit's design, grid voltage, and frequency of pulse width modulation, grid impedance, and filter interference. A comparison of various gain parameters and corresponding THDs of different grid-connected controllers with the proposed controller is presented in Table 6.

Figure 19. Grid voltage and grid current waveforms with PSOGA-PI controller.

Figure 20. THD analysis of grid current waveform with PSOGA-PI controller.

Figure 21. Active and reactive power delivered to the grid.

Figure 22. Leakage current in the grid-connected PV system.

| Controller | Voltage (       | Controller      | Current (       | Controller      | % THD |

|------------|-----------------|-----------------|-----------------|-----------------|-------|

| _          | K <sub>Vp</sub> | K <sub>Vi</sub> | К <sub>Ср</sub> | K <sub>Ci</sub> | _     |

| PSO-PI     | 0.51            | 0.209           | 0.87            | 0.341           | 3.96% |

| HHO-PI     | 0.81            | 0.11            | 0.91            | 0.089           | 2.72% |

| PSOGA-PI   | 0.96            | 0.089           | 0.94            | 0.096           | 1.26% |

The performance of grid-connected PV systems with different grid controllers is described in terms of efficiency, as shown in Table 7. The grid power in terms of RMS values is  $\frac{1}{2} V_g * I_g$ . Where,  $V_g$  is the peak value of grid voltage, and  $I_g$  is the peak value of grid current. The dc power of the PV system can be obtained using Equation (28).

$$P_{DC} = (V_{pv1} * I_{pv1}) + (V_{pv2} * I_{pv2}) + (V_{pv3} * I_{pv3})$$

(28)

$$P_{DC} = (27.42 \times 7.31) + (54.6 \times 7.34) + (78.08 \times 7.96) = 1222.72 \text{ W}$$

Table 7. Efficiency of the proposed GCSPV system with different controllers.

| Controller | Power from<br>PV System<br>(W) | Grid Voltage $V_g$ (V) | Grid Current<br>I <sub>g</sub> (A) | Grid Power $\frac{1}{2} V_g * I_g$ (W) | % Efficiency |

|------------|--------------------------------|------------------------|------------------------------------|----------------------------------------|--------------|

| PSO-PI     | _                              | 336.8                  | 6.89                               | 1160.28                                | 94.89%       |

| HHO-PI     | P <sub>DC</sub> = 1222.72      | 336.7                  | 6.91                               | 1163.33                                | 95.14%       |

| PSOGA-PI   |                                | 336.7                  | 6.96                               | 1171.72                                | 95.82%       |

Also, the comparative analysis of different controllers with other topologies presented in the literature is presented in Table 8. This comparative analysis shows that the proposed PSOGA-based PI controller performs satisfactorily with a low THD of 1.26% at 95.82% efficiency.

| Authors                              | Controller | Level of the<br>Inverter | %<br>THD | % Efficiency |

|--------------------------------------|------------|--------------------------|----------|--------------|

|                                      | EANFIS     | 27                       | 0.78%    | -            |

| Bihari and Sadhu et al. [21]         | PI         | 27                       | 18.19%   | -            |

|                                      | PID        | 27                       | 16.11%   | -            |

| Makhamreh et al. [22]                | MPC        | 7                        | 3.45%    | -            |

| Satti and Hasan et al. [25]          | DMPC       | 7                        | 2.7%     | 95.3%        |

| I akahmi and Hamamalini at al. [26]  | PI         | 3                        | 3.32%    | -            |

| Lakshmi and Hemamalini et al. [26]   | FO-PI      | 3                        | 2.62%    | -            |

| Dishore Shanmugam Vanaja et al. [24] | HHO-PI     | 31                       | 1.49%    | 94%          |

|                                      | PSO-PI     | 15                       | 3.96%    | 94.89%       |

| Proposed                             | HHO-PI     | 15                       | 2.72%    | 95.14%       |

|                                      | PSOGA-PI   | 15                       | 1.26%    | 95.82%       |

Table 8. Comparative analysis with other techniques proposed in the literature.

Due to continuous variations in solar irradiation and temperature, the power out of the PV Panel is affected. However, the maximum power output can be obtained from the PV panel using the maximum power point tracking technique. The proposed system employs the P & O MPPT algorithm to track the maximum power point of the PV system under varying environmental conditions and is tabulated in Table 9. From Table 9, it is observed that as the irradiance is decreased and affecting the grid voltage to decrease. However, the proposed controller allows the grid voltage variations  $\pm 6\%$  to the nominal RMS voltage of 240 V.

Table 9. Impact of solar irradiance and temperature on grid connected PV systems.

| PV Source<br>& Irradiance                                                        | Temperature<br>in (deg.C) | V <sub>PV</sub> | - (V) | I <sub>PV</sub> | (A)  | P <sub>PV</sub> | (W)   | V <sub>Boo</sub> | <sub>st</sub> (V) | I <sub>Boos</sub> | <sub>t</sub> (A) | Grid<br>Voltage<br>(V) | Grid<br>Current<br>(A) |

|----------------------------------------------------------------------------------|---------------------------|-----------------|-------|-----------------|------|-----------------|-------|------------------|-------------------|-------------------|------------------|------------------------|------------------------|

| & muunite                                                                        |                           | Mean            | RMS   | Mean            | RMS  | Mean            | RMS   | Mean             | RMS               | Mean              | RMS              | RMS                    | RMS                    |

| $\begin{array}{c} PV \text{ Source-1} \\ \cong \\ 600 \text{ W/m}^2 \end{array}$ |                           | 31.7            | 32.1  | 7.08            | 7.09 | 223.8           | 226.2 | 45.4             | 45.9              | 4.54              | 4.59             |                        |                        |

| $\frac{PV \text{ Source-2}}{\underset{800}{\cong} \text{W/m}^2}$                 | 35 °C                     | 30.04           | 30.7  | 9.12            | 9.14 | 275.9           | 278.1 | 50.2             | 50.7              | 5.02              | 5.07             | 237.8                  | 5.74                   |

| $\begin{array}{c} \text{PV Source 3} \\ \cong \\ 1000 \text{ W/m}^2 \end{array}$ | -                         | 28.7            | 28.9  | 11.1            | 11.2 | 319             | 321   | 53.8             | 54.2              | 5.38              | 5.43             | _                      |                        |

| PV Source 1<br>$\cong$ 500 W/m <sup>2</sup>                                      |                           | 34              | 34.5  | 6.01            | 6.02 | 203.4           | 206   | 43.3             | 43.8              | 4.33              | 4.38             |                        |                        |

| $\begin{array}{c} \text{PV Source 2} \\ \cong \\ 600 \text{ W/m}^2 \end{array}$  | 25 °C                     | 33.8            | 34.2  | 6.94            | 6.95 | 233.5           | 236.1 | 46.4             | 46.9              | 4.61              | 4.69             | 241.2                  | 5.61                   |

| $\begin{array}{c} \text{PV Source 3} \\ \cong \\ 800 \text{ W/m}^2 \end{array}$  | -                         | 32.1            | 32.3  | 9.15            | 9.20 | 291.7           | 294.2 | 51.7             | 52.2              | 5.17              | 5.22             | _                      |                        |

## 6. Conclusions

The application of the proposed 15-level asymmetric inverter on grid integration of an SPV system was explored in this chapter. On the Simulink platform, a 1.25 kW grid-connected SPV system is modelled and tested. The proposed grid-connected solar photovoltaic system is put through its tests using a variety of solar irradiance and temperature conditions. When designing the proposed system to inject sinusoidal current into the grid, two voltage controllers are taken into consideration. The total dc voltage of the proposed inverter is controlled by one controller, while the dc voltage of the corresponding dc sources provided by the PV array is controlled by the other. A PI controller is used to control the grid voltage and current under changing irradiance and variable temperature circumstances, which adjusts the needed gain to maintain constant grid voltage in all weather conditions. The THDs obtained from PSO-PI, HHO-PI, and PSOGA-PI controllers are 3.96%, 2.72% and 1.26%, respectively. These comparisons conclude that the hybrid PSOGA based PI controller gives a good response with less THD of 1.26% than other controllers. Also, the GCSPV system with the proposed inverter works flawlessly, with an efficiency of 95.82% using a hybrid PSOGA based PI controller. Further to extend the research work presented in this article, future work can be considered in the following possibilities:

- The investigations can be extended to operate the inverter, considering an array of renewable energy resources such as fuel cells, PV cells, wind energy, etc.

- By extending the concepts and procedures deduced in the thesis, the fault-tolerant capability of the MLI can be carried out.

- The performance assessment can be carried out by injecting reactive power into the grid. This further improves the efficiency of the inverter, but investigations are required into the lifetime of the inverter since the inverter's performance will degrade with the injection of reactive power.

- The real-time analysis can be carried out to validate the analytical results of the proposed work.

- The investigations can be extended to optimize dc-link voltage of designed multilevel inverter with input energy storage system under varying operating conditions.

- The proposed multilevel inverter topology can be applied for various stand-alone medium and high-voltage applications, such as induction motor drive, FACTS devices, and HVDC applications.

- The suggested method can be extended to the three-phase systems.

Author Contributions: Conceptualization, D.G.K.; Data curation, A.G. and S.S.K.; Formal analysis, S.M.; Funding acquisition, A.H.M. and A.A.A.; Investigation, A.G., N.K.S., M.B., H.K. and A.H.M.; Methodology, N.V.S. and S.M.; Software, N.V.S. and A.A.A.; Validation, N.K.S. and M.B.; Writing—original draft, S.S.K.; Writing—review & editing, H.K. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: The data sources employed for analysis are presented in the text.

Conflicts of Interest: The authors declare no conflict of interest.

# Abbreviations

| SPV             | Solar photovoltaic system                             |

|-----------------|-------------------------------------------------------|

| GCSPV           | Grid connected photovoltaic system                    |

| Р&О             | Perturb and observe                                   |

| MPPT            | Maximum power point tracking                          |

| MLI             | Multilevel inverter                                   |

| SHEPWM          | Selective harmonic elimination pulse width modulation |

| PDPWM           | Phase disposition pulse width modulation              |

| SVPWM           | Space vector pulse width modulation                   |

| MV              | Medium voltage                                        |

| HV              | High voltage                                          |

| THD             | Total harmonic distortion                             |

| V <sub>dc</sub> | DC input voltage                                      |

| FSFC            | Fundamental switching frequency control               |

| α                  | Switching angle                                    |

|--------------------|----------------------------------------------------|

| V <sub>1max</sub>  | Peak fundamental voltage                           |

| $V_1$              | Actual fundamental voltage                         |

| k                  | Degree of freedom                                  |

| Ν                  | No of output voltage levels                        |

| OF                 | Objective function                                 |

| GA                 | Genetic algorithm                                  |

| PSO                | Particle swarm optimization                        |

| HHO                | Harris hawk Optimization                           |

| PSOGA              | Particle Swarm Optimization with Genetic Algorithm |

| Vgrid              | Grid voltage                                       |

| V <sub>PV</sub>    | PV cell voltage                                    |

| $I_{PV}$           | PV cell current                                    |

| P <sub>PV</sub>    | PV cell power                                      |

| V <sub>Boost</sub> | Output voltage of dc-dc boost converter            |

| I <sub>Boost</sub> | Output current of dc-dc boost converter            |

| K <sub>Vp</sub>    | Proportional gain value of voltage controller      |

| K <sub>Vi</sub>    | Integral gain value of voltage controller          |

| K <sub>Cp</sub>    | Proportional gain value of current controller      |

| K <sub>Ci</sub>    | Integral gain value of current controller          |

| PI                 | Proportional plus integral                         |

# References

- Arun, N.; Noel, M. Crisscross switched multilevel inverter using cascaded semi-half-bridge cells. *IET Power Electron.* 2018, 11, 23–32. [CrossRef]

- Alishah, R.; Hosseini, S.; Babaei, E.; Sabahi, M. A new general multilevel converter topology based on cascaded connection of sub multilevel units with reduced switching components, DC sources, and blocked voltage by switches. *IEEE Trans. Ind. Electron.* 2016, 63, 7157–7164. [CrossRef]

- Samadaei, E.; Sheikholeslami, A.; Gholamian, S.; Adabi, J. A square T-type (ST-type) module for asymmetrical multilevel inverters. IEEE Trans. Power Electron. 2018, 33, 987–996. [CrossRef]

- 4. Saeedian, M.; Adabi, J.; Hosseini, S. Cascaded multilevel inverter based on symmetric–asymmetric DC sources with reduced number of components. *IET Power Electron.* 2017, *10*, 1468–1478. [CrossRef]

- Alishah, R.; Hosseini, S.; Babaei, E.; Sabahi, M. Optimal Design of new Cascaded Switch-Ladder Multilevel Inverter Structure. IEEE Trans. Ind. Electron. 2017, 64, 2072–2080. [CrossRef]

- 6. Agrawal, R.; Jain, S. Multilevel inverter for interfacing renewable energy sources with low/medium- and high-voltage grids. *IET Renew. Power Gener.* 2017, *11*, 1822–1831. [CrossRef]

- Lee, S. Single-stage switched-capacitor module (S3CM) topology for cascaded multilevel inverter. *IEEE Trans. Power Electron.* 2018, 33, 8204–8207. [CrossRef]

- Gautam, S.; Kumar, L.; Gupta, S. Single-phase multilevel inverter topologies with self-voltage balancing capabilities. *IET Power Electron.* 2018, 11, 844–855. [CrossRef]

- 9. Tariq, M.; Meraj, M.; Azeem, A.; Maswood, A.; Iqbal, A.; Chokkalingam, B. Evaluation of level-shifted and phase-shifted PWM schemes for seven level single-phase packed U cell inverter. *CPSS Trans. Power Electron. Appl.* **2018**, *3*, 232–242. [CrossRef]

- Barzegarkhoo, R.; Kojabadi, H.; Zamiry, E.; Vosoughi, N.; Chang, L. Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple DC link producer with reduced number of switches. *IEEE Trans. Power Electron.* 2016, 31, 5604–5617. [CrossRef]

- 11. Sharifzadeh, M.; Vahedi, H.; Al-Haddad, K. New constraint in SHE-PWM for single-phase inverter applications. *IEEE Trans. Ind. Appl.* **2018**, *54*, 4554–4562. [CrossRef]

- 12. Lee, S. A single-phase single-source 7-level inverter with triple voltage boosting gain. IEEE Access 2018, 6, 30005–30011. [CrossRef]

- Valderrama, G.; Guzman, G.; Pool-Mazun, E.; Martinez-Rodriguez, P.; Lopez-Sanchez, M.; Zuniga, J.A. Single-phase asymmetrical T-type five-level Transformerless PV inverter. *IEEE J. Emerg. Sel. Top. Power Electron.* 2018, *6*, 140–150. [CrossRef]

- 14. Rai, N.; Chakravorty, S. Generalized formulations and solving techniques for selective harmonic elimination PWM strategy: A review. J. Inst. Eng. India Ser. B 2019, 100, 649–664. [CrossRef]

- Kumar, D.G.; Ganesh, A.; Naga Malleswara Rao, D.S. Design and Analysis of a Novel Cascaded 15-Level Asymmetric Inverter Using PSO and Whale Algorithms. In Proceedings of the 2021 International Conference on Sustainable Energy and Future Electric Transportation (SEFET), Hyderabad, India, 21–23 January 2021; pp. 1–6. [CrossRef]

- 16. Fang, X.; Du, E.; Zheng, K.; Yang, J.; Chen, Q. Locational pricing of uncertainty based on robust optimization. *CSEE J. Power Energy Syst.* **2021**, *7*, 1345–1356.

- 17. Xiao, D.; Qiao, W. Hybrid scenario generation method for stochastic virtual bidding in electricity market. *CSEE J. Power Energy Syst.* **2021**, *7*, 1312–1321.

- Kumar, D.G.; Ganesh, A.; Bhoopal, N. Power loss analysis in 15 level asymmetric reduced switch inverter using PLECS thermal models. J. Eng. Sci. Technol. Rev. 2021, 14, 10–17. [CrossRef]

- 19. Heidari, A.A.; Mirjalili, S.; Faris, H.; Aljarah, I.; Mafarja, M.; Chen, H. Harris hawks optimization: Algorithm and applications. *Futur. Gener. Comput. Syst.* **2019**, *97*, 849–872. [CrossRef]

- Ahmed, M.; Sheir, A.; Orabi, M. Real-time solution and implementation of selective harmonic elimination of seven-level multilevel inverter. *IEEE J. Emerg. Sel. Top. Power Electron.* 2017, *5*, 1700–1709. [CrossRef]

- 21. Bihari, S.; Sadhu, P. Design analysis of high level inverter with EANFIS controller for grid connected PV system. *Analog. Integr. Circuits Signal Process* **2020**, *103*, 411–424. [CrossRef]

- Makhamreh, H.; Trabelsi, M.; Kukrer, O.; Abu-Rub, H. An effective sliding mode control design for a grid-connected PUC7 multilevel inverter. *IEEE Trans. Ind. Electron.* 2021, 67, 3717–3725. [CrossRef]

- 23. Shunmugham Vanaja, D.; Stonier, A.A. Grid integration of modular multilevel inverter with improved performance parameters. *Int. Trans. Electr. Energy Syst.* 2021, 31, e12667. [CrossRef]

- 24. Shunmugham Vanaja, D.; Stonier, A. A novel PV fed asymmetric multilevel inverter with reduced THD for a grid-connected system. *Int. Trans. Electr. Energy Syst.* 2020, 30, e12267. [CrossRef]

- Satti, M.; Hasan, A. Direct model predictive control of novel H-bridge multilevel inverter based grid-connected photovoltaic system. *IEEE Access* 2019, 7, 62750–62758. [CrossRef]

- Lakshmi, M.; Hemamalini, S. Decoupled control of grid connected photovoltaic system using fractional order controller. *Ain Shams Eng. J.* 2018, 9, 927–937. [CrossRef]