# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 11 Issue: V Month of publication: May 2023

DOI: https://doi.org/10.22214/ijraset.2023.51561

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 11 Issue V May 2023- Available at www.ijraset.com

### Performance Analysis of Deep Sub Micron Two Quadrant Analog Divider Circuits

#### Minikumari G

Abstract: Current mode Analog Dividers are widely used in various circuits such as fuzzy logic controllers, neural networks, adaptive filters and variable gain amplifiers. When these current analog divider circuits implemented in DSM technology, many of the second order effects starts deteriorating its performance. Most of the available literatures on analog dividers are reporting performance of these circuits implemented using long channel MOSFETs. Hence it is a peak time to compare the performance variation between various proposed analog circuits implemented in lower technological nodes. This is for identifying most reliable circuit which safely works in this node. In this work a comparative performance analysis of two quadrant CMOS analog divider against two quadrant CMOS approximation divider using 45nm technological node has been carried out. The obtained result indicates that Approximation Divider is reliable than two quadrant CMOS analog divider. The entire work is carried out using Tanner software.

Keywords: DSM Technology, Short channel effects, Analog Divider circuits, Two quadrant CMOS analog divider. Two quadrant CMOS approximation divider.

#### I. INTRODUCTION

Analog signal processing find applications in portable equipments, wireless nano sensors or medical implantation devices because of their compact implemented structure due to low power consumption and speed [2]. Analog Dividers are widely used in current mode analog circuits such as fuzzy logic controllers, neural networks, adaptive filters and variable gain amplifiers [3]. Most of the available analog divider circuits implemented using long channel MOSFETs [4-6]. When current divider circuits uses DSM technology, many of the second order effects deteriorating performance. The reduction of the channel length of the transistor is the most common features of the modern CMOS technology. With the introduction of DSM CMOS technologies (minimal channel length below 100nm) designers of analog circuits are facing new challenges at different stages of the design [1]. The common second order effects are body effect, channel length modulation and subthreshold conduction [7]. This work aim to fill that literature gap. In this work a comparative analysis of two quadrant CMOS analog divider [4] against two quadrant CMOS approximation divider [6] has been carried out. This is for identifying most reliable circuit which safely works in DSM node. This work aim to explore the functionality and performance variations of settling time and resolution.

Section II compares basic working difference of two analog divider circuits such as two quadrant CMOS analog divider against two quadrant CMOS approximation divider and it also gives an overview of various second order effects arises in DSM circuits.. , Statement of problem and solution methodology are discussed in section III. Section IV consolidates the various results obtained and the conclusion remarks and future scope of this work is narrated in Section V.

#### II. REVIEW OF LITERATURE

This work mainly focuses on two types of analog dividers. The first circuit under study is a two quadrant CMOS analog divider, where , the numerator and denominator input data are provided to the circuit as equivalent currents where as the output quotient is a voltage. In this circuit which some transistors operate in the triode region. The second structure two quadrant CMOS approximation divider the numerator and denominator data are currents and output also derived in current This circuit developed by using two variable second-order Taylor series approximation. The main three second order effects which play prominent role in DSM circuits are body happens if the bulk effect, channel length modulation and subthreshold conduction. Body effect voltage of an NFET drops below the source voltage ie  $V_b < 0$  more holes attracted to the substrate connection leaving a large negative charge behind. It results in the widening of depletion region.

As a function of that threshold voltage increases. As in the case of channel-length modulation, actual length of the inverted channel gradually decreases as the potential difference between the gate and drain increases. This is the channel-length modulation. Even for gate source voltage less than threshold voltage the drain current is finite, but it exhibits an exponential dependence on gate source voltage called subthreshold voltage.

Volume 11 Issue V May 2023- Available at www.ijraset.com

#### III. PROBLEM STATEMENT AND SYSTEM METHODOLGY

Most of the literatures on analog dividers are discussing there performance when they are implemented in long channel MOSFETs. Hence there is lack of information about the performance and reliability of these circuits when they are implemented using lower technological node such as 45nm. This work aim to fill that literature gap. A comparative performance analysis of two prominent analog divider circuits are carried out in work. The aim of this work is to simulate and study the comparative performance variation of two quadrant Analog dividers in 45nm technological node. Spice tool from TANNER is used for this purpose.

#### IV. RESULT ANALYSIS

#### A. Two Quadrant Analog Divider Circuit

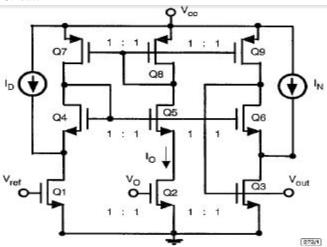

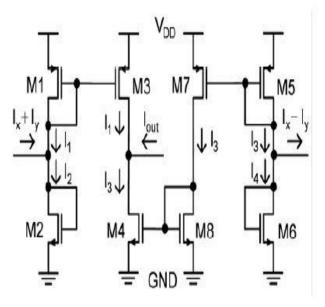

Fig.1 Two Quadrant CMOS Analog divider

In the simplified schematic drawing of the divider shown in Fig 1, the numerator and denominator are two currents called  $I_N$  and  $I_D$  respectively. The output is derived from the gate voltage of transistor Q3. The circuit comprises three layers of transistors. The lowest one performs the actual division operation. All transistors are connected in common source mode. Transistors  $Q_1$ -  $Q_{\#}$  have the same size and are operates in the triode region. The middle layer consists of two source followers  $Q_5$  and  $Q_6$  controlled by the diode connected transistor  $Q_4$ , which replicates the drain voltage  $V_{ds}$  of  $Q_1$  at the drains of  $Q_2$  and  $Q_3$ . Finally, the upper layer is a current mirror mirroring the drain current of the centre transistor  $Q_5$  into the drains of  $Q_5$  and  $Q_5$ . The principle of the divider is , considering transistors  $Q_5$  and  $Q_5$  first. The drain current of  $Q_5$  will be equal to the sum of  $Q_5$  and the mirrored drain current of  $Q_5$ , we have

$$I_D + I_o = \beta \Big( (V_{ref} - V_T) V_{ds} - \frac{n}{2} V_{ds}^2 \Big)$$

(1)

where

$$I_o = \beta \left( (V_o - V_T)V_{ds} - \frac{n}{2}V_{ds}^2 \right) \tag{2}$$

Hence

$$I_D = \beta (V_{ref} - V_o) V_{ds} \tag{3}$$

Now consider the transistor Q3 its drain current is equal to the sum of  $I_N$  and Io its gate voltage Vout must adjust itself to satisfy the expression

$$I_N + I_o = \beta \Big( (V_{out} - V_T) V_{ds} - \frac{n}{2} V_{ds}^2 \Big)$$

(4)

Hence, similarly to eqn. 3,

$$I_N = \beta (V_{out} - V_o) V_{ds} \tag{5}$$

and thus

$$V_{out} - V_o = (V_{ref} - V_o) \frac{I_N}{I_D}$$

(6)

Volume 11 Issue V May 2023- Available at www.ijraset.com

Thus if  $V_{out}$  is referred to Vo a two quadrant divider is obtained. The transistor Q3 is being connected to high impedance node, the loop gain controlling the output voltage can be very large while the output impedance is very large

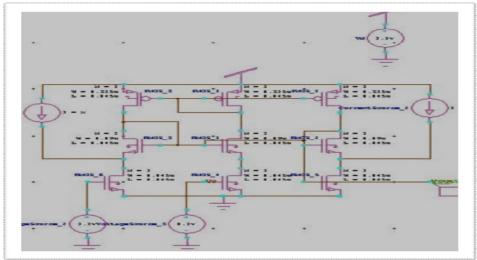

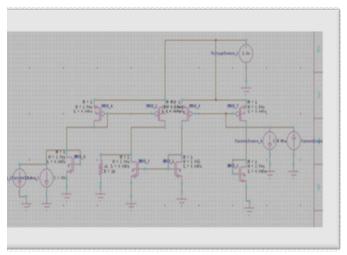

Fig.2 Current-input/Voltage-output Two quadrant divider (simulation set-up)

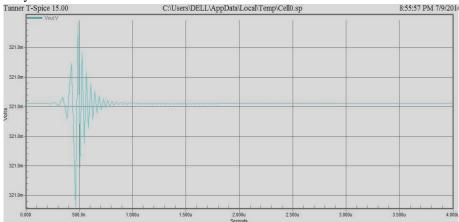

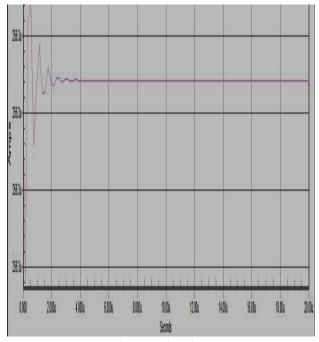

#### 1) Settling time

It is the time required for the output to reach and stay within a tolerance band. In this circuit upto 2.85uS the output shows ringing and after it goes on to steady

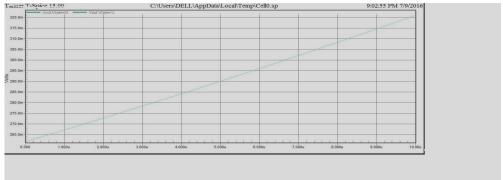

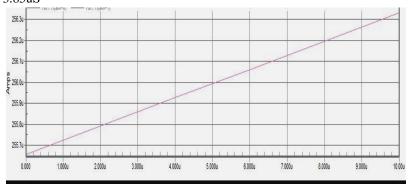

#### 2) DC response of the circuit

Fig.4 shows the measured dc response of two quadrant the analog divider it shows a relative error which is more than approximation divider.

Fig. 4 DC Response of the Divider (Vout against  $I_{\mathbb{D}}$  from 0-10uA in 1uA steps with  $I_{\mathbb{N}}$  10uA)

Volume 11 Issue V May 2023- Available at www.ijraset.com

#### 3) Resolution

It is the minimum input to produce a perceptible output. This minimum necessary increment is called resolution.

#### B. Two-Quadrant CMOS approximation Divider

Fig.5 Two Quadrant CMOS Approximation Divider

In Fig.5 the left cell constructed by M1, M2 and current input  $I_{x+}I_{y}$ , produces  $I_{2}$  and  $I_{1}$  where

$$I_{1} = KV_{0}^{2} \left( 1 - \frac{I_{x} + I_{y}}{4KV_{0}^{2}} \right)^{2}$$

The core cell constructed by M5, M6 and current input Ix-Iy ,produces  $I_3$  and  $I_4$  Where

$$I_3 = KV_0^2 \left(1 + \frac{I_x - I_y}{4KV_0^2}\right)^2$$

In these two = equations

$$V_{\text{o}} = (V_{\text{DD}} - \left| V_{\text{Tp}} \right| - V_{\text{Tn}})/2$$

$$K = K_n = \frac{1}{2} \mu_n C_{ox} W/L = K_p = \frac{1}{2} \mu_p C_{ox} W/L$$

The output current Iout =  $I_{3-}I_{1}$ Then

$$I_{out} = I_x - \frac{I_x I_y}{4KV_0^2}$$

Volume 11 Issue V May 2023- Available at www.ijraset.com

Fig.6 Two Quadrant CMOS Approximation Divider (simulation set-up)

Fig.7 Settling time

This circuit settled out after 3.85uS

Fig. 8 DC response of the divider (Iout against  $I_x$  from 0 to 10uA in 1uA steps with  $I_y$ , .10uA DC response is better than Analog divider in approximation divider

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 11 Issue V May 2023- Available at www.ijraset.com

#### V. CONCLUSION

| Parameter      | Analog divider- | Analog divider- |

|----------------|-----------------|-----------------|

|                | 1               | 2               |

| Settling time  | 2.85uS          | 3.85uS          |

| Resolution     | 0.2mV           | .02mV           |

| Relative error | more            | less            |

In this paper, the performance of two analog dividers namely CMOS analog divider and approximation divider are compared according to settling time, resolution and relative error and it is verified that the Analog divider is more reliable than Approximation divider. In this paper process variability is not considered so proposing Monte carlo analysis for reducing the process variations.

#### **REFERENCES**

- [1] Overview and comparison of methodologies for design of deep submicron cmos processes, aleksandar p radev, ieee xplore 08-sep-2022

- [2] Synthesis of computational structures for analog signal processing, cosmin radu popa, spinger sciences+business media

- [3] Cmos current-mode companding multiplier/divider and its nth-root kuo-jen lin,chih-jen cheng andjwu-e chen, department of microelectronics engineering chung hua universitytaiwan 300

- [4] Two quadrantemos analog divider c.dualibe, mverleysen and p jespers electronic letters 11th june 1998 vol.34 no.12

- [5] Liu,w, s.i liu and s.k wei cmos current mode divider and its applications, "ieee trans.circuit systems ii, express briefs,52,(3), pp 145-148,2005

- [6] Two-quadrant cmos approximation divider, kuo-jen lin department of microelectronics engineering chung hua university taiwan 300

- [7] B.Razavi, design of analog cmos integrated circuits. mcgraw hill, 2000

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)