## Research Article

# Performance Analysis of High Speed Hybrid CMOS Full Adder Circuits for Low Voltage VLSI Design

### Subodh Wairya,<sup>1</sup> Rajendra Kumar Nagaria,<sup>2</sup> and Sudarshan Tiwari<sup>2</sup>

<sup>1</sup> Department of Electronics Engineering, Institute of Engineering & Technology (IET), Lucknow 226021, India

<sup>2</sup> Department of Electronics and Communication Engineering, Motilal Nehru National Institute of Technology (MNNIT), Allahabad 211004, India

Correspondence should be addressed to Subodh Wairya, swairya@gmail.com

Received 28 June 2011; Revised 2 November 2011; Accepted 24 November 2011

Academic Editor: Jose Carlos Monteiro

Copyright © 2012 Subodh Wairya et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

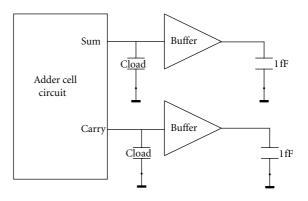

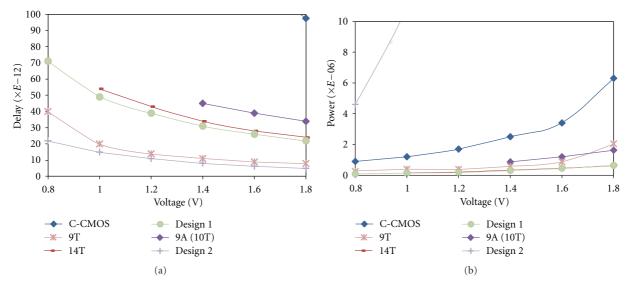

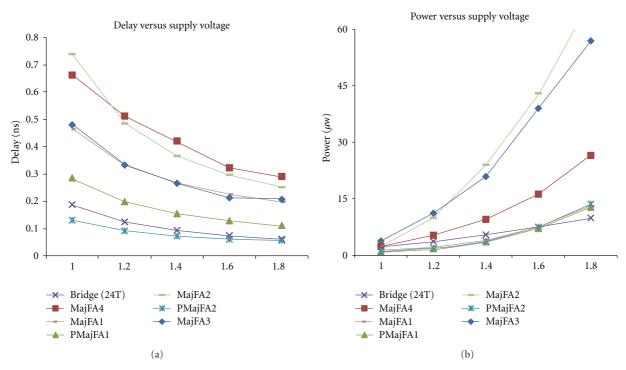

This paper presents a comparative study of high-speed and low-voltage full adder circuits. Our approach is based on hybrid design full adder circuits combined in a single unit. A high performance adder cell using an XOR-XNOR (3T) design style is discussed. This paper also discusses a high-speed conventional full adder design combined with MOSCAP Majority function circuit in one unit to implement a hybrid full adder circuit. Moreover, it presents low-power Majority-function-based 1-bit full addersthat use MOS capacitors (MOSCAP) in its structure. This technique helps in reducing power consumption, propagation delay, and area of digital circuits while maintaining low complexity of logic design. Simulation results illustrate the superiority of the designed adder circuits over the conventional CMOS, TG, and hybrid adder circuits in terms of power, delay, power delay product (PDP), and energy delay product (EDP). Postlayout simulation results illustrate the superiority of the newly designed majority adder circuits against the reported conventional adder circuits. The design is implemented on UMC 0.18  $\mu$ m process models in Cadence Virtuoso Schematic Composer at 1.8 V single-ended supply voltage, and simulations are carried out on Spectre S.

### 1. Introduction

It is time we explore the well-engineered deep submicron CMOS technologies to address the challenging criteria of these emerging low-power and high-speed communication digital signal processing chips. The performance of many applications as digital signal processing depends upon the performance of the arithmetic circuits to execute complex algorithms such as convolution, correlation, and digital filtering. Fast arithmetic computation cells including adders and multipliers are the most frequently and widely used circuits in very-large-scale integration (VLSI) systems. The semiconductor industry has witnessed an explosive growth of integration of sophisticated multimedia-based applications into mobile electronics gadgetry since the last decade. However, the critical concern in this arena is to reduce the increase in power consumption beyond a certain range of operating frequency. Moreover, with the explosive growth, the demand, and the popularity of portable electronic products, the designers are driven to strive for smaller silicon area,

higher speed, longer battery life, and enhanced reliability. The XOR-XNOR circuits are basic building blocks in various circuits especially arithmetic circuits (adders & multipliers), compressors, comparators, parity checkers, code converters, error-detecting or error-correcting codes and phase detector.

Adder is the core element of complex arithmetic circuits like addition, multiplication, division, exponentiation, and so forth. There are standard implementations with various logic styles that have been used in the past to design fulladder cells [1–4] and the same are used for comparison in this paper. Although they all have similar function, the way of producing the intermediate nodes and the transistor count is varied. Different logic styles tend to favor one performance aspect at the expense of the others. The logic style used in logic gates basically influences the speed, size, power dissipation, and the wiring complexity of a circuit. The circuit *delay* is determined by the number of inversion levels, the number of transistors in series, transistor sizes (i.e., channel widths), and the intracell wiring capacitances. Circuit *size* depends upon the number of transistors, their sizes and on the wiring complexity. Some of them use one logic style for the whole full adder while the other use more than one logic style for their implementation.

Power is one of the vital resources, hence the designers try to save it while designing a system. Power dissipation depends upon the switching activity, node capacitances (made up of gate, diffusion, and wire capacitances), and control circuit size. At the device level, reducing the supply voltage  $V_{\rm DD}$ and reducing the threshold voltage accordingly would reduce the power consumption. Scaling the supply voltage appears to be the well-known means to reduce power consumption. However, lower-supply voltage increases circuit delay and degrades the drivability of the cells designed with a certain logic style. One of the most significant obstacle in decreasing the supply voltage is the large transistor count and  $V_{\rm th}$  loss problem. By selecting proper (*W/L*) ratio we can minimize the power dissipation without decreasing the supply voltage.

To summarize, some of the performance criteria are considered in the design and evaluation of adder cells and some are utilized for the ease of design, robustness, silicon area, delay, and power consumption. The paper is organized section wise. Section 2 describes the review of full adder circuit topologies. Section 3 illustrates the concept of SUM function-based hybrid full adders topologies and highlights some 1-bit adder cells, which is based on XOR-XNOR (3T) circuits. A review of Majority function, MOS capacitor characteristics, and three-input and five-input Majority function (MOSCAPs) based full adder topologies has been discussed in Section 4. In Section 5, implementations of Hybrid XOR-XNOR (3T) and Majority-function-based full adder methodologies are discussed. The simulation results are analyzed and compared in Section 6. Finally, Section 7 concludes the paper.

### 2. Review of Full Adder Topologies

In recent years, several variants of different logic styles have been proposed to implement 1-bit adder cells [5-28]. There are two types of full adders in case of logic structure. One is static and the other is dynamic style. Static full adders are commonly more reliable, simpler and are lower power consuming than dynamic ones. Dynamic is an alternative logic style to design a logic function. It has some advantages over the static mode such as faster switching speeds, no static power consumption, nonratioed logic, full swing voltage levels, and lesser number of transistors. An N input logic function requires N+2 transistors versus 2N transistors in the standard CMOS logic. The area advantage comes from the fact that the pMOS network of a dynamic CMOS gate consists of only one transistor. This also results in a reduction in the capacitive load at the output node, which is the basis for the delay advantage. There are various issues related to the full adder like power consumption, performance, area, noise immunity, regularity and good driving ability. Many researchers have combined these two structures and have proposed hybrid dynamic-static full adders. They have investigated different approaches realizing adders using CMOS technology each having its own pros and cons.

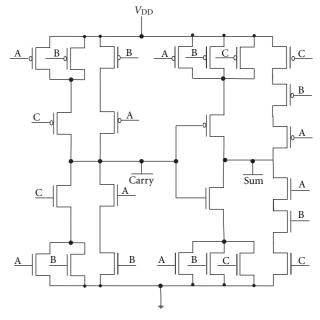

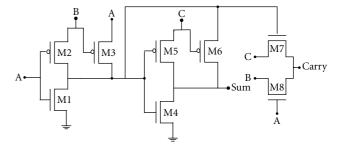

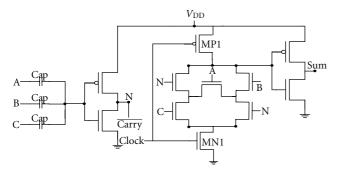

FIGURE 1: C-CMOS adder cell.

Full adder circuits can be divided into two groups on the basis of output. The first group of full adders have full swing output. C-CMOS, CPL, TGA, TFA, Hybrid, 14T, and 16T belong to the first group [5–20, 29–31]. The second group comprises of full adders (10T, 9T and 8T) without full swing outputs [21–28]. These full adders usually have low number of transistors- (3T-) based XOR-XNOR circuit, less power consumption, and less area occupation. The nonfull swing full adders are useful in building up larger circuits as multiple bit input adder and multipliers. One such application is the Manchester Carry-Look Ahead chain. The full adders of first group have good driving ability, high number of transistors, large area, and usually higher power consumption in comparison to the second group.

There are standard implementations for the full-adder cells which are used as the basis of comparison in this paper. Some of the standard implementations are as follows.

CMOS logic styles have been used to implement the lowpower 1-bit adder cells. In general, they can be broadly divided into two major categories: the Complementary CMOS and the Pass-Transistor logic circuits. The complementary CMOS (C-CMOS) full adder (Figure 1) is based on the regular CMOS structure [3, 4, 29]. The advantage of complementary CMOS style is its robustness against voltage scaling and transistor sizing, which are essential to provide reliable operation at low voltage with arbitrary transistor sizes.

The pass-transistor logic (PTL) is a better way to implement circuits designed for low power applications. The low power pass-transistor logic and its design analysis procedures were reported in [12, 13]. Its advantage is that one passtransistor network (either pMOS or nMOS) is sufficient to implement the logic function, which results in lower number of transistors and smaller input load. Moreover, direct  $V_{DD}$ to-ground paths, which may lead to short-circuit energy dissipation, are eliminated.

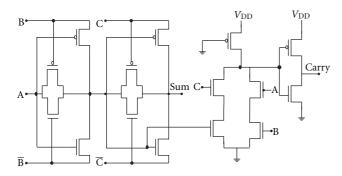

FIGURE 2: TG-Pseudo adder cell.

Pseudo nMOS full adder cell operates on pseudo logic, which is referred to as ratioed style. This full adder cell uses 14 transistors to realize the negative addition function. The advantage of pseudo nMOS adder cell is its higher speed (compared to conventional full adder) and less transistor count. The disadvantage of pseudo nMOS cell is the static power consumption of the pull-up transistor as well as the reduced output voltage swing, which makes this adder cell more susceptible to noise. To increase the output swing, CMOS inverter is added to this circuit.

Newly designed full adder [20] is a combination of low power transmission gates and pseudo nMOS gates as depicted in Figure 2. Transmission gate consists of a pMOS transistor and an nMOS transistor that are connected in parallel, which is a particular type of pass-transistor logic circuit. There is no voltage drop at output node, but it requires twice the number of transistors to design similar function.

Another full adder is the Complementary Pass Transistor Logic (CPL) with swing restoration, which uses 32 transistors [5, 6, 30, 31]. CPL adder produces many intermediate nodes and their complement to give the outputs. The most important features of CPL include the small stack height and low output voltage swing at the internal node which contribute to reduction in power consumption. The CPL suffers from static power consumption due to the low swing at the gates of the output inverters. *Double pass-transistor logic* (DPL) [8] and *swing restored pass-transistor logic* (SRPL) [9, 10] are related to CPL.

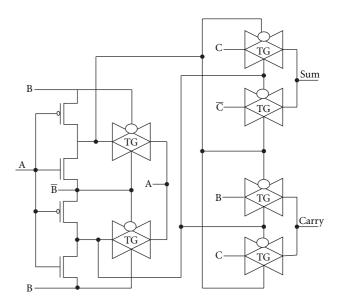

Some designs of the full adder circuit based on transmission gates are shown in Figure 3. Transmission gate logic circuit is a special kind of pass-transistor logic circuit [4, 5, 25]. The main disadvantage of transmission gate logic is that it requires twice the number of transistors than pass-transistor logic or more to implement the same circuit. TG gate full adder cell has 20 transistors. Similarly, transmission function full adder (TFA) cell has 16 transistors [4, 29]. It exhibits better speed and less power dissipation than the conventional CMOS adder due to the small transistor stack height.

### 3. Sum Function-Based Hybrid Full Adder Topologies

More than one logic style is used for implementation of the hybrid full adders. The hybrid adder cells may be classified

FIGURE 3: TG adder cell.

into various categories depending upon their structure and logical expression of the Sum and Carry output signals. All hybrid designs use the best available modules implemented using different logic styles or enhance the available modules in an attempt to build a low power consuming full-adder cell [17–19]. Most full adder topologies are based on two XOR circuits: one to generate H (XOR) with  $\overline{H}$  (XNOR), and the other to generate the Sum output. The carry signal is obtained by using one MUX (multiplexer):

Sum =

$$A \oplus B \oplus C$$

, Carry =  $AB + C(A \oplus B)$ ,

$H = A \oplus B$ , Sum =  $H \oplus C$ , (1)

Carry =  $A \cdot \overline{H} + C \cdot H$ .

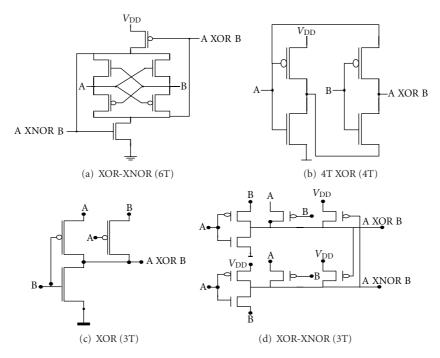

3.1. XOR-XNOR Topologies. In [28, 32–35], the XOR-XNOR circuit designed with static CMOS logic with complementary pull-up pMOS and pull-down nMOS networks is the conventional one, but it requires more number of CMOS transistors. This circuit may operate with full output voltage swing. Different XOR/XNOR topologies are illustrated in Figure 4. A PTL based 6-transitor XOR-XNOR circuit presented in [34] has full output voltage swing and better driving capability.

A new set of low power four transistor (4T) XOR and XNOR circuits called powerless P-XOR and Groundless G-XNOR, respectively, is proposed in [25–28, 32]. The P-XOR and G-XNOR circuits consume less power than other designs because they have no direct supply voltage ( $V_{DD}$ ) or ground connection. The performance of the complex logic circuits is affected by the individual performance of the XOR-XNOR circuits that are included in them. An XOR and XNOR function with low circuit complexity can be achieved with only three transistors (3T) in PTL. Despite the saving in transistor count, the output voltage level is degraded at certain input signal combinations.

FIGURE 4: Basic designs of XOR-XNOR gate found in literature.

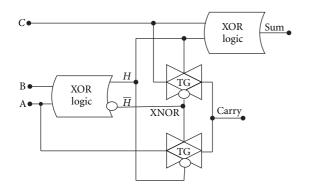

FIGURE 6: Centralized XOR-XNOR based-adder.

FIGURE 5: Cascaded XOR-XNOR based-adder.

Generally, the main aim is to reduce the number of transistors in the adder cell and consequently to reduce the number of power dissipating nodes. This is achieved by utilizing intrinsically low power consuming logic styles like TFA, TGA or simply passing transistors. There are three main components to design a hybrid full adder circuit [19]. These are XOR or XNOR, Carry generator and Sum generator. Hybrid adders may be classified into two groups which are as follows.

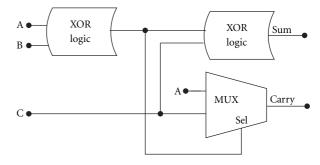

*3.2. Cascaded Output Based Adders (Group 1).* In this category, signal Sum is generated using, either two cascaded XOR or two cascaded XNOR modules. Figure 5 shows the basic blocks of this category. Almost all the circuits in this category suffer from high delay in generating Sum and Carry signals. The Static Energy Recovery full adder (SERF) falls under this category [23].

3.3. Centralized Output Based Adders (Group 2). In this category, Sum and Carry are generated using intermediate signals XOR and XNOR. In this group, output Sum and Carry are generated faster than the outputs in cascaded output full adders. The key point here is to produce intermediate signals simultaneously. Otherwise, there may be glitches, unnecessary power consumption, and longer delay. Figure 6 shows the basic blocks of this category. TGA and TFA are in this category. Some of the hybrid full adders do not belong to any of these two groups, such as Complementary and Level Restoring Carry Logic (CLRCL) full adder [26] and Multiplexer based (MBF 12T) full adder [18].

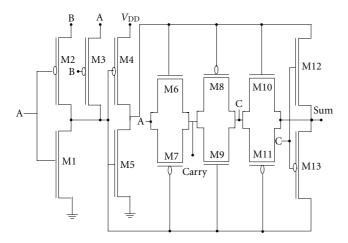

*3.4. 10T Full Adder.* In [24] different components have been combined to make 41 new 10T full adder full adders. Some 10T full adders can be designed by interchanging the inputs of the module having lowest propagation delay amongst all the 10T full adder circuits. The design of the 10T adder cell is based on an optimized design for the XOR function

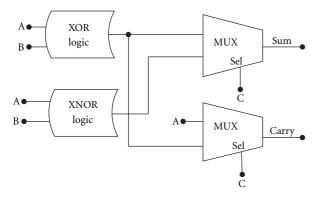

FIGURE 7: XOR-XNOR- (3T-) based 10T full adder.

and pass transistor logic to implement the addition logic function. Two XOR operations are required to calculate the Sum function. Each XOR operation requires four transistors (4T). 2X1 MUX is used for Carry function implemented using two transistors.

Another 10T full adder based on centralized structure is shown in Figure 7. Intermediate XOR and XNOR are generated using three transistor (3T) XOR and XNOR gate. Sum and Carry are generated using two double transistors multiplexers. 3T XOR and XNOR consume high energy due to short circuit current in ratio logic. They all have double threshold losses in full adder output terminals. This problem usually prevents the full adder design from operating at low supply voltage or cascading directly without extra buffering. The lowest possible power supply is limited to  $2V_{\rm tn} + V_{\rm tp}$ where  $V_{\rm tn}$  and  $V_{\rm tp}$  are the threshold voltages of nMOS and pMOS respectively. The basic advantages of 10T transistor full adders are: less area compared to higher gate count full adders, lower power consumption and lower operating voltage. It becomes very difficult and even obsolete to keep full voltage swing operation as the designs with fewer transistor count and lower power consumption are pursued.

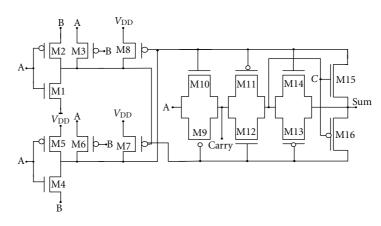

3.5. 9T Full Adder. In nine transistor (9T) full adder circuit, we have only one 3T XOR gate as is shown in the Figure 8 [36]. The design of 3T (M1–M3) XOR circuit is based on a modified version of a CMOS inverter and a pMOS pass transistor. When A = 1 and B = 0, voltage degradation due to threshold drop occurs across transistor M3 and consequently the output (M3) is degraded with respect to the input. The voltage degradation due to threshold drop can be minimized by increasing the *W/L* ratio of transistor M3. An equation relating threshold voltage of a MOS transistor to the channel length and width is given as

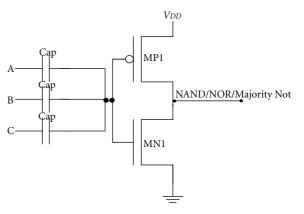

$$V_T = V_{T0} + \gamma \left( \sqrt{V_{SB} + \phi_0} - \sqrt{\phi_0} \right) - \alpha_l \frac{t_{ox}}{L} (V_{SB} + \phi_0)$$

$$- \alpha_v \frac{t_{ox}}{L} (V_{DS}) + \alpha_W \frac{t_{ox}}{L} (V_{SB} + \phi_0),$$

(2)

where

$V_{T0}$  is the zero bias threshold voltage,

$\gamma$  is bulk threshold coefficient,

$\phi_0$  is  $2\phi_F$ , where  $\phi_F$  is the Fermi potential,

FIGURE 8: 9T full adder.

FIGURE 9: 8T full adder.

$\alpha_l, \alpha_v$ , and  $\alpha_w$  are the process dependent parameters.

The above equation shows that by increasing channel width (W) it is possible to decrease the threshold voltage  $(V_{th})$ . So it is possible to minimize the voltage degradation due to threshold voltage by increasing the width of M3 transistor & keeping the length constant. In 9T full adder circuit pass transistor M4, M5 and M6, M7 are used for Carry and Sum function respectively.

*3.6. 8T Full Adder*. The design of an eight transistor (8T) full adder using 3T XOR gates is shown in Figure 9 [37]. The Boolean equations for the design of the eight transistor full adder are as follows:

Sum =

$$A \oplus B \oplus C$$

,

Carry =  $BC + CA + AB = C(A \oplus B) + AB$ . (3)

The Sum output function is obtained by a cascade of 3T XOR gates. Carry can be realized using a wired OR logic in accordance with the above equation.

Another 8T full adder using centralizer output condition contains three modules—two 3T XOR gates and one multiplexer (2T). It can work at high speed with low power dissipation due to minimum number of transistors and small transistor delay.

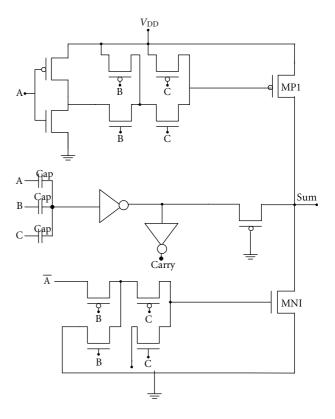

FIGURE 10: Implementation of Majority functions (MOSCAP).

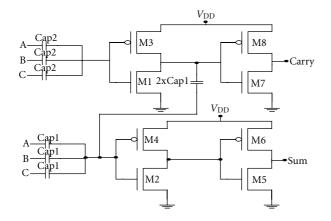

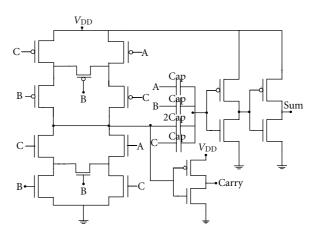

### 4. Carry (Majority) Function-Based Hybrid Full Adder Topologies

The Majority function is a logic circuit that functions as a majority vote to determine the output of the circuits [38]. This function has only odd number of inputs. Its output is equal to "1" when the number of input logic "1" is more than logic "0". Comparing to the XOR implementations of full adder cells, Majority-based full adders are more reliable and robust [38]. Moreover, the bridge style full adder circuits [39] by sharing transistors can operate faster and are smaller than the conventional CMOS full adder circuits.

4.1. Literature Review of Majority Functions. Boolean algebra with three variables is used to facilitate the conversion of a sum-of-products expression to minimize majority logic as shown in Table 1 [38]. Three binary variables can only produce eight unique minterms. Any three-variable Boolean function can be represented by the combinations of up to eight of these minterms. The three-variable Boolean function of 5–7 minterms can be represented using the complement form of 3–1 minterms. Based on DeMorgan's theorem, a Boolean function, expressed as the sum of several minterms, can also be expressed as the complement of the sum of the remaining minterms. The simplified majority expressions for 13 standard functions are given in Table 1.

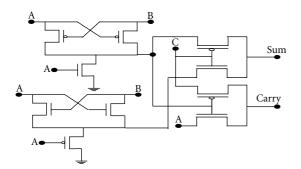

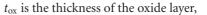

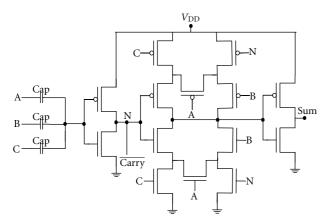

4.2. Circuit-Interpretation-of-MOS Capacitor- (MOSCAP-) Based Majority Not Function. The majority structure is implemented by three input capacitors. These three input capacitors prepare an input voltage that is applied for driving static CMOS buffer. The majority gates may be designed with more inputs by this method by increasing the number of input capacitors. The capacitor network is used to provide voltage division for implementing majority logic as explained below.

Total current *I* at node  $V = I_1 + I_2 + I_3$ ,

$$(V)c_{x}s = (V_{1} - V)c_{1}s + (V_{2} - V)c_{1}s + (V_{3} - V)c_{1}s$$

$$= (c_{X} + 3c_{1})V = (V_{1} + V_{2} + V_{3})c_{1},$$

$$(4)$$

$$V = (V_{1} + V_{2} + V_{3})\left(\frac{c_{1}}{3c_{1} + c_{X}}\right).$$

The input capacitors shown in Figure 10 are used to prepare an input voltage that is applied for driving static

FIGURE 11: Majority function- (MOSCAP-) based logic gates.

inverter. When the majority of inputs are "0", the output of capacitor network is considered as logic "0" by the CMOS buffer and consequently the output of buffer is 0 V. When the majority of inputs are logic "1", the output of capacitor network is considered logic "1" by the CMOS buffer and consequently the output of buffer is  $V_{DD}$ . The input capacitance of the CMOS buffer is negligible and has no effect on operation of the circuit. Three capacitors perform voltage summation to implement scaled-linear sum. Through superposition of input capacitors, increased input voltage is scaled at point V as shown in Figure 10 and given in Table 2 [40].

4.3. MOS Capacitor (MOSCAP) Structure. In this section hardware implementation and construction of MOSCAP are discussed. Tying the drain and source of a MOSFET together results in a MOSCAP. Many realizable alternatives such as Poly-Insulator-Poly capacitors (PIPCAP), Metal-Insulator-Metal capacitors (MIMCAP), or Metal-Oxide-Semiconductor capacitors (MOSCAP) can be utilized for realizing the capacitor network. However, MOSCAP has an advantage of more capacitance; less chip area. The nMOSCAP usually has lesser capacitance in comparison to pMOSCAP for the same area, so pMOSCAP is used for implementing the capacitor network. Table 3 shows that the variation of MOS capacitor with respect to channel width of MOS transistor.

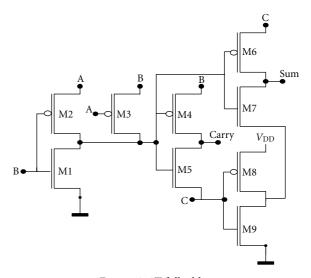

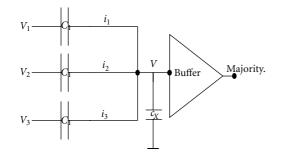

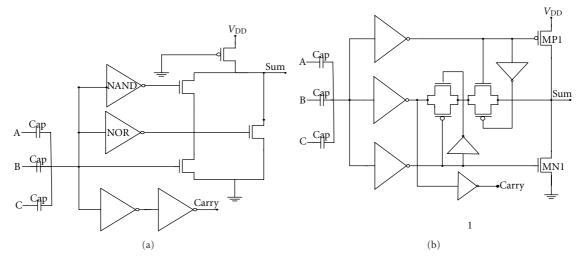

4.4. Implementation of (NAND, NOR and Majority Not) Gates Using MOSCAP Majority Function. Figure 11 shows the circuit used to implement Majority Not function with inverter utilizing high- $V_{th}$  for both nMOS and pMOS. This circuit can be used to implement NAND gate using high- $V_{th}$  nMOS and low- $V_{th}$  pMOS, and NOR gate using low- $V_{th}$  nMOS and high- $V_{th}$  pMOS. The Majority gates may be designed with more inputs by this method by increasing the number of input capacitors. The capacitor network is used to provide voltage division for implementing majority logic.

There are two methods to design the NAND and NOR logic circuits. First method is the transistor sizing that shifts the voltage transfer curve (VTC) to the left and right by changing the ratio of (W/L)n to (W/L)p. Raising this ratio moves VTC to the left; therefore, this circuit will operate as

### VLSI Design

| Standard Boolean function                                                    | Majority expression                                                        | Function implementation diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F = A                                                                        | M(A, 0, 1)                                                                 | $\begin{array}{c} A \\ 1 \\ 0 \end{array} \qquad M \\ 0 \end{array} \qquad \bullet F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $F = A \cdot B$                                                              | M(A, B, 0)                                                                 | $\begin{array}{c} A \\ 0 \\ B \end{array} \qquad M \\ B \end{array} \qquad \qquad$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $F = A \cdot B \cdot C$                                                      | M(M(A,B,0),C,0)                                                            | $\begin{array}{c} A \\ 0 \\ B \end{array} \qquad M \\ C \end{array} \qquad M \\ F \\ \bullet \\ C \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $F = A \cdot B \cdot C + \overline{A} \cdot \overline{B} \cdot \overline{C}$ | $M\{M(M(A,0,B),C,0), M(M(\overline{A},\overline{B},0),\overline{C},0),1\}$ | $\begin{array}{c} A \\ 0 \\ B \\ 0 \\ C \\ 0 \\ M \\ \hline \\ 0 \\ \hline \\ 0 \\ \hline \\ M \\ \hline \\ 0 \\ \hline \\ \\ \hline \\ \\ 0 \\ \hline \\ \\ \hline \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $F = A \cdot B + \overline{A} \cdot \overline{B} \cdot C$                    | $M\{M(A, 0, B), M(M(\overline{A}, \overline{B}, 0), C, 0), 1\}$            | $\begin{array}{c} A \\ 0 \\ B \\ \end{array} \\ M \\ H \\ C \\ 0 \\ M \\ \overline{A} \\ \overline{B} \\ \overline{B} \\ M \\ \overline{B} \\ \overline{B}$ |

| $F = A \cdot B + \overline{B} \cdot C$                                       | $M\{M(A,0,B),M(\overline{B},0,C),1\}$                                      | $\begin{array}{c} A \\ 0 \\ B \\ \end{array} \\ \hline \\ B \\ 0 \\ C \\ \end{array} \\ M \\ M \\ \end{array} \\ \begin{array}{c} F \\ \bullet \\ \\ M \\ C \\ \end{array} \\ \begin{array}{c} M \\ \bullet \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $F = A \cdot B + \overline{A} \cdot \overline{B}$                            | $M\{M(A, 0, B), M(\overline{A}, 0, \overline{B}), 1\}$                     | $\begin{array}{c} A \\ 0 \\ B \\ \hline \\ A \\ \hline \\ 0 \\ \hline \\ B \\ \hline \\ M \\ \hline \\ B \\ \hline \\ M \\ \hline \\ \\ B \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $F = A \cdot B + B \cdot C$                                                  | M(B, M(A, 1, C), 0)                                                        | $\begin{array}{c} A \\ 1 \\ C \end{array} \\ M \\ B \\ B \\ \end{array} \\ M \\ F \\ \bullet \\ B \\ \bullet \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

TABLE 1: Majority expression of standard logic functions.

|                                                                                                                                                       | TABLE 1: Continued.                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

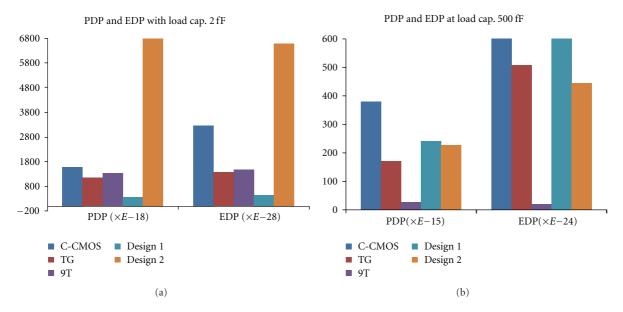

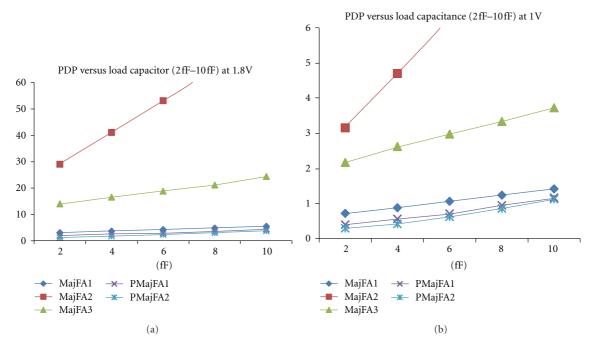

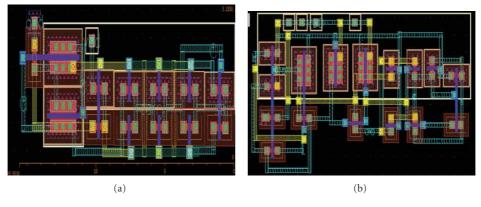

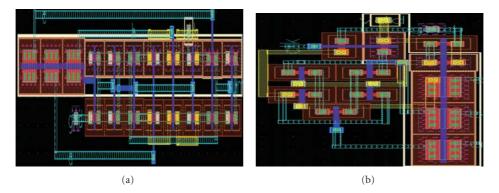

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|