## 0115-0

DOE/ET/20356-9 (DE84010378)

#### PHOTOVOLTAIC POWER CONDITIONING SUBSYSTEM: STATE OF THE ART AND DEVELOPMENT OPPORTUNITIES

By S. Krauthamer K. Bahrami R. Das T. Macie W. Rippel

January 15, 1984

Work Performed Under Contract No. AI01-76ET20356

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

Energy

S O L A R

> Technical Information Center Office of Scientific and Technical Information United States Department of Energy

#### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

### DISCLAIMER

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

#### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

This report has been reproduced directly from the best available copy.

Available from the National Technical Information Service, U. S. Department of Commerce, Springfield, Virginia 22161.

Price: Printed Copy A09 Microfiche A01

Codes are used for pricing all publications. The code is determined by the number of pages in the publication. Information pertaining to the pricing codes can be found in the current issues of the following publications, which are generally available in most libraries: *Energy Research Abstracts* (*ERA*); Government Reports Announcements and Index (*GRA* and I); Scientific and Technical Abstract Reports (STAR); and publication NTIS-PR-360 available from NTIS at the above address.

#### 5220-21

Photovoltaics Program Project Analysis and Integration Center DOE/ET/20356-9 (DE84010378) Distribution Category UC-63

# Photovoltaic Power Conditioning Subsystem: State of the Art and Development Opportunities

- S. Krauthamer

- K. Bahrami

- R. Das

- T. Macie

- W. Rippel

January 15, 1984

Prepared for

U.S. Department of Energy

Through an Agreement with National Aeronautics and Space Administration

by

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

JPL Publication 83-81

# THIS PAGE WAS INTENTIONALLY LEFT BLANK

#### ABSTRACT

Photovoltaic systems, the state of the art of power conditioning subsystem components, and the design and operational interaction between photovoltaic systems and host utilities are detailed in this document. Major technical issues relating to the design and development of power conditioning systems for photovoltaic application are also considered, including: (1) standards, guidelines, and specifications; (2) cost-effective hardware design; (3) impact of advanced components on power conditioning development; (4) protection and safety; (5) quality of power; (6) system efficiency; and (7) system integration with the host utility. In addition, theories of harmonic distortion and reactive power flow are discussed, and information about power conditioner hardware and manufacturers is provided. Power conditioning development has been a significant component of the Photovoltaics (PV) Program of the U.S. Department of Energy (DOE). This document establishes a perspective for that effort. Because alternative renewable energy sources are expected to become competitive with more conventional utility energy generation sources, realization of the full potential of the alternative energy will ultimately require interconnections with the utility grid. Power conditioners must therefore be grid compatible. The DOE has long recognized the need to resolve interconnection issues to ensure a smooth integration of Dispersed Storage and Generations (DSG) systems into the utility grid. The Electric Energy Systems Division (DOE/EES) has been given the generic responsibility for ensuring the integration of DSG systems with the utility grids without undue difficulties. The Photovoltaics Energy Technology Division has the responsibility for developing photovoltaics as a renewable alternative energy source.

In concert will the generic EES programs and in the context of making photovoltaics viable as an alternative energy source, the DOE/PV program has a continuing interest in facilitating the integration of photovoltaics with the utility grid. More specifically, the DOE/PV program complements the DOE/EES program by addressing the interconnection issues from a point of view unique to the PV program. To that end, the JPL Photovoltaics Technology Development and Applications Lead Center published "Distributed Photovoltaic Systems: Utility Interface Issues and Their Present Status" (JPL Publication 81-89) in September 1981. The study addressed the outstanding utility interconnection issues from a photovoltaics point of view and identified relevant unresolved technical issues. This led in turn to the preparation in November 1981 by the JPL Lead Center, in conjunction with the Electric Power Research Institute, of a draft entitled "Interim Working Guidelines and Discussion Concerning the Interface of Small Dispersed Photovoltaic (PV) Power Producers with Electric Utility Systems." These guidelines were ultimately published by EPRI as "Interconnecting D.C. Energy Systems: Responses to Technical Issues" (EPRI Publication AP/EM-3124) in June 1983. These documents provide a source of technical input in support of the national consensus standards process sponsored by the IEEE and others.

The aforementioned activities in the Photovoltaics Program to resolve utility interface issues have made the critical role of PV power conditioning systems increasingly evident. The objective of this current publication is to complement those earlier efforts by bringing together in one report the essentials of the photovoltaics power conditioning discipline needed for a complete understanding of photovoltaics interconnection issues.

> Robert V. Powell Manager Systems Research and Technology Photovoltaics Program TD&A Lead Center Jet Propulsion Laboratory

#### FOREWORD

#### ACKNOWLEDGMENTS

The authors wish to express appreciation to A. Bulawka, manager, Photovoltaic Power Conditioning Program, U.S. Department of Energy; and to E.S. Davis, technical manager, Jet Propulsion Laboratory (JPL), for their valuable contributions to the report. Appreciation is also expressed for the support and assistance of J. Klein and J. Graf, technical group supervisors, JPL; R.V. Powell, manager, JPL Photovoltaic Project Analysis and Integration Center; and C. Edwards, editor.

# THIS PAGE WAS INTENTIONALLY

# LEFT BLANK

#### CONTENTS

| PART | ONE :  | EXECUTIVE SUMMARY                                                                        | • | ••  | 1   |

|------|--------|------------------------------------------------------------------------------------------|---|-----|-----|

| PART |        | PHOTOVOLTAIC POWER CONDITIONING SUBSYSTEM: STATE OF THE<br>AND DEVELOPMENT OPPORTUNITIES |   |     | 1-1 |

| 1.   | PURPOS | SE AND APPROACH                                                                          | • | ••  | 1-3 |

| 2.   | INTROD | DUCTION                                                                                  | • | ••  | 2-1 |

| 3.   | HISTOR | RICAL PERSPECTIVE                                                                        | • | ••  | 3-1 |

|      | 3.1    | INTRODUCTION                                                                             | • | ••  | 3-1 |

|      | 3.2    | ROTARY CONVERTERS                                                                        | • | ••  | 3-1 |

|      | 3.3    | SOLID-STATE (STATIC) CONVERTERS                                                          | • | • • | 3-2 |

|      | 3.4    | ROTARY vs. SOLID-STATE CONVERSION                                                        | • | • • | 3-4 |

|      | 3.5    | THE FUTURE                                                                               | • | ••  | 3-5 |

| 4.   | SYSTEM | 1 CONFIGURATION, REQUIREMENTS, AND OPERATION                                             | • | • • | 4-1 |

|      | 4.1    | SYSTEM DESCRIPTION                                                                       | • | ••  | 4-1 |

|      | 4.2    | SUBSYSTEM DESCRIPTION                                                                    | • | • • | 4-2 |

|      |        | 4.2.1 Array Subsystem                                                                    | • |     | 4-2 |

|      |        | 4.2.2 Power Conditioning Subsystem                                                       | • | • • | 4-4 |

|      |        | 4.2.3 Control Subsystem                                                                  | • | • • | 4-5 |

|      |        | 4.2.4 Utility Interconnection Subsystem                                                  |   |     | 4-6 |

|      | 4.3    | SUBSYSTEM REQUIREMENTS                                                                   |   |     | 4-6 |

|      | · ·    | 4.3.1 Array Subsystem Requirements                                                       |   |     | 4-6 |

|      |        | 4.3.2 PCS Requirements                                                                   |   |     | 4-7 |

|      |        | 4.3.3 Control Subsystem Requirements                                                     |   |     | 4-9 |

|      | ·      | 4.3.4 Utility Interconnection Subsystem Requirements .                                   |   |     |     |

| 4.4   | SYSTEM REQUIREMENTS                            | 4-10             |

|-------|------------------------------------------------|------------------|

|       | 4.4.1 System Performance Requirements          | 4-10             |

|       | 4.4.2 System Protection Requirements           | 4-13             |

|       | 4.4.3 System Stability                         | 4-16             |

| 4.5   | SYSTEM OPERATION                               | 4-18             |

|       | 4.5.1 Constant Voltage Operation               | 4-19             |

|       | 4.5.2 Maximum Power Operation                  | 4-19             |

| 4.6   | GENERAL DESIGN PRACTICES                       | 4-26             |

| 4.7   | SYSTEM CONFIGURATIONS                          | 4-26             |

| 4.8   | SELECTION AND SIZING OF PCS                    | 4-27             |

|       | 4.8.1 PCS Circuit Design Issues                | 4-27             |

|       | 4.8.2 PCS Operational Design Issues            | 4-31             |

|       | 4.8.3 General Procedure for Selection of a PCS | 4-35             |

| 4.9   | REFERENCES                                     | 4-37             |

| POWER | CONDITIONING COMPONENTS                        | 5-1              |

| 5.1   | INTRODUCTION                                   | 5-1              |

| 5.2   | SWITCHES (ELECTROMECHANICAL)                   | 5-1              |

| 5.3   | MAGNETIC COMPONENTS                            | 5 <del>-</del> 1 |

| 5.4   | CAPACITORS                                     | 5-2              |

| 5.5   | POWER COMPONENTS                               | 5-3              |

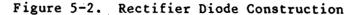

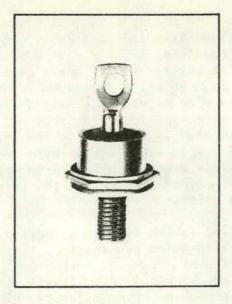

|       | 5.5.1 Rectifier Diode                          | 5-3              |

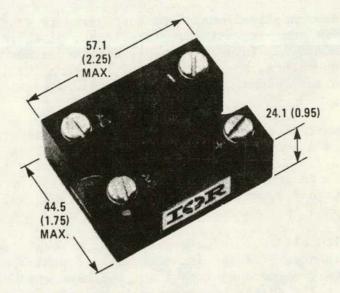

|       | 5.5.2 Bipolar Transistors                      | 5-7              |

|       | 5.5.3 Transistor Fabrication and Packaging     | 5-12             |

|       | 5.5.4 Field-Effect Transistor                  | 5-13             |

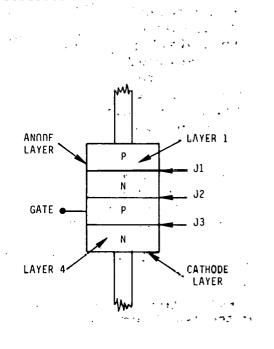

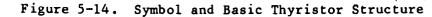

|       | 5.5.5 Thyristor                                | 5-17             |

|       | 5.5.6 Gate Turn-off Thyristor (GTO)            | 5-22             |

. 5.

|    |        | 5.5.7 Advanced Semiconductor Devices                              |

|----|--------|-------------------------------------------------------------------|

|    | 5.6    | REFERENCES                                                        |

| 6. | FUNDAM | ENTALS OF INVERTERS                                               |

|    | 6.1    | INTRODUCTION                                                      |

|    | 6.2    | INVERTER APPLICATIONS                                             |

|    | 2      | 6.2.1 Utility Interactive Inverters 6-1                           |

|    |        | 6.2.2 Stand-Alone Inverter                                        |

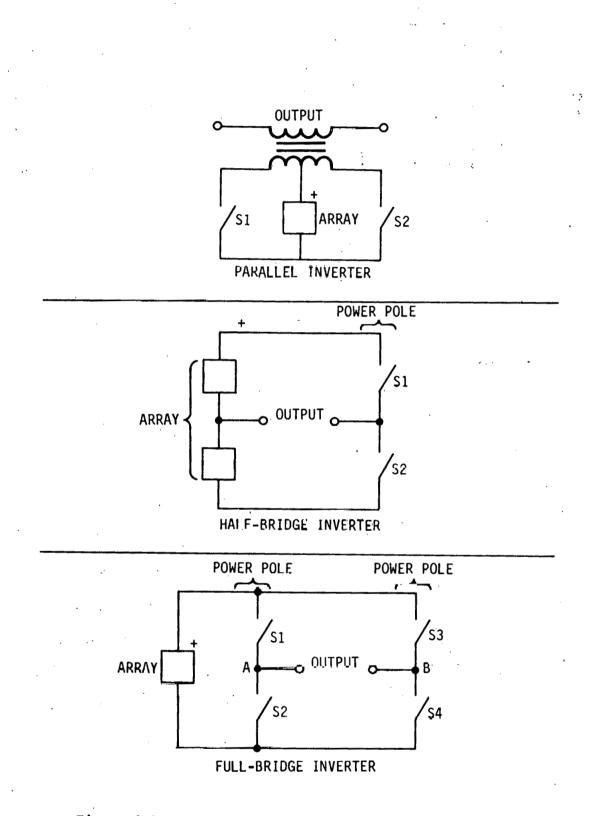

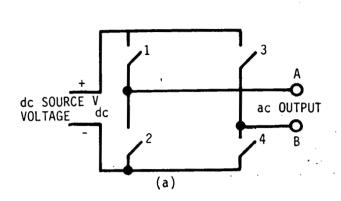

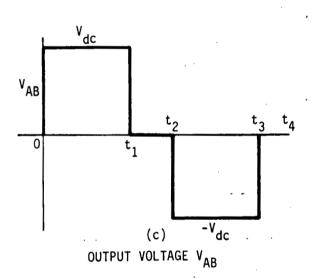

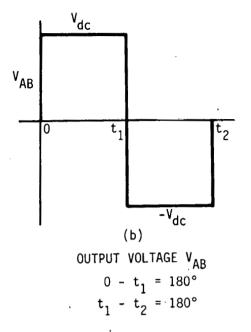

|    | 6.3    | INVERSION METHODOLOGY                                             |

|    |        | 6.3.1 Basic Inverter                                              |

|    |        | 6.3.2 Current-Fed Inverter                                        |

|    |        | 6.3.3 Voltage-Fed Inverter                                        |

|    |        | 6.3.4 Line-Commutated Inverter                                    |

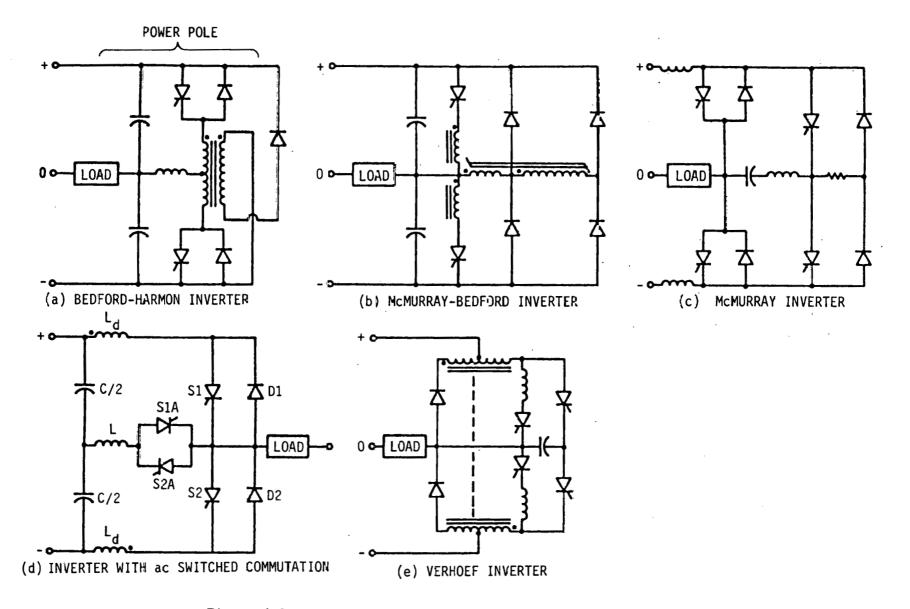

|    |        | 6.3.5 Self-Commutated/Force-Commutated Inverters 6-11             |

|    |        | 6.3.6 Forced Commutation                                          |

|    | 6.4    | WAVESHAPING AND VOLTAGE REGULATION                                |

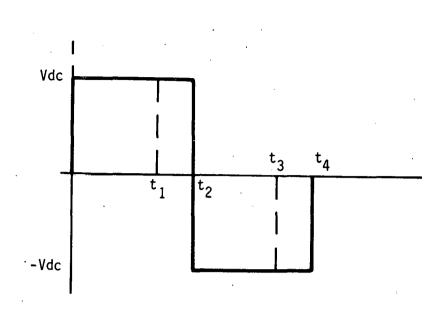

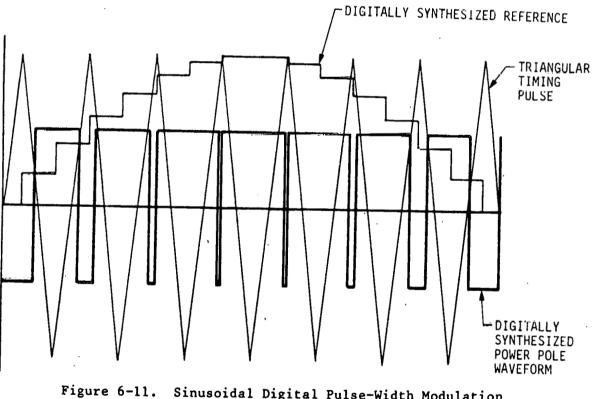

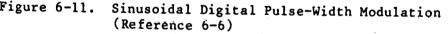

|    |        | 6.4.1 Sinusoidal Pulse-Width Modulation (PWM) 6-15                |

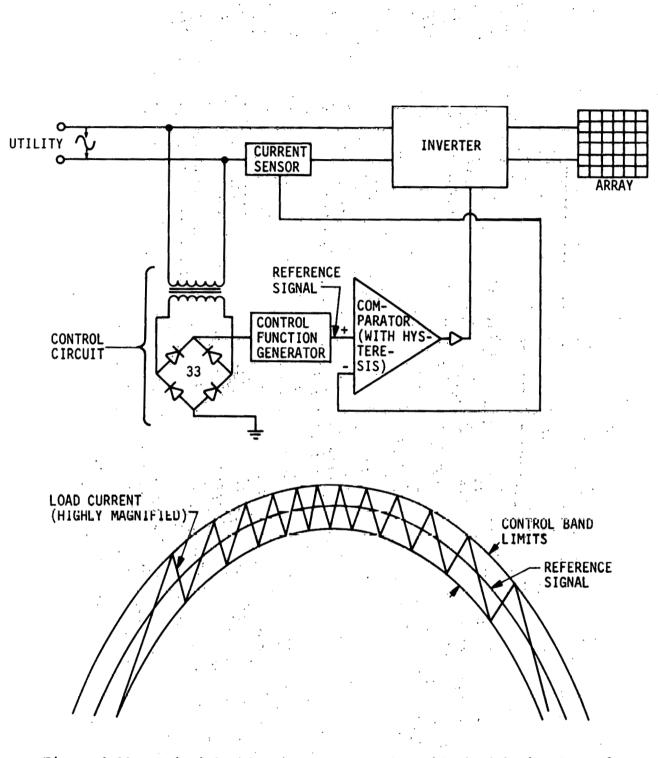

|    |        | 6.4.2 Synthesized-Waveform Inverters 6-19                         |

|    | 6.5    | REFERENCES                                                        |

| 7. |        | TERISTICS OF STATE-OF-THE-ART AND ADVANCED POWER<br>ER TOPOLOGIES |

|    | 7.1    | SMALL INVERTERS (1 to 15 kW)                                      |

|    |        | 7.1.1 Transistorized Single-Bridge Inverter                       |

|    |        | 7.1.2 Transistorized Dual-Bridge Inverter                         |

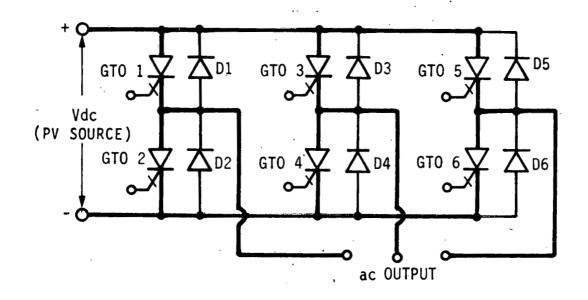

|    |        | 7.1.3 Gate Turn-off, Half-Bridge Inverter                         |

|    |        | 7.1.4 High-Frequency Link Utility Interactive Inverter 7-7        |

|    |        | 7.1.5 Thyristor Bridge, Line-Commutated Inverter                  |

|    |        | 7.1.6 dc/dc Converter Controlled Transistor<br>Bridge Inverter    |

ix

|    | 7.2          | INTERMEDIATE SIZE INVERTERS (15 to 1000 kW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |              | 7.2.1 Thyristor-Powered Inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|    |              | 7.2.2 Transistorized Inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |              | 7.2.3 Inverters Using Gate Turn-off Thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

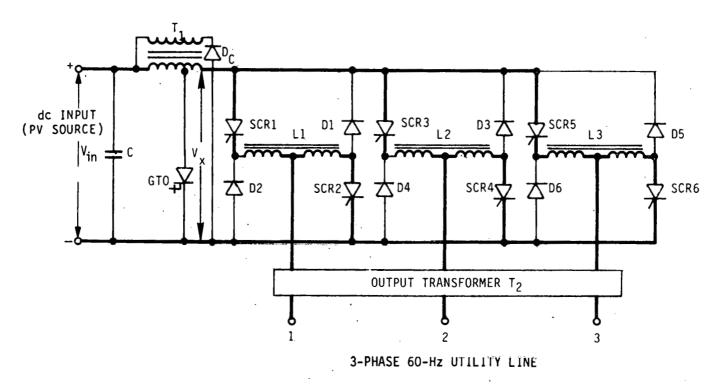

|    |              | 7.2.4 Hybrid Inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 7.3          | LARGE INVERTERS (ABOVE 1 MW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 1            | 7.3.1 Six-Pulse, Line-Commutated 1-MW Inverter 7-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    |              | 7.3.2 Twelve-Pulse, Line-Commutated Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |              | 7.3.3 Twelve-Pulse, Self-Commutated, 500-kW and<br>750-kW Thyristor Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |              | 7.3.4 4.8-MW, Self-Commutated, Eighteen-Pulse Inverter 7-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    |              | 7.3.5 5-MW, Chopper-Controlled, Line-Commutated,<br>Twolvo-Pulse Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | 7.4          | REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8. |              | D RESEARCH AND OPPORTUNITIES FOR DEVELOPING IMPROVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8. | POWER        | CONDITIONING SUBSYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8. |              | CONDITIONING SUBSYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8. | POWER<br>8.1 | CONDITIONING SUBSYSTEMS8-1STANDARDS, GUIDELINES, AND SPECIFICATIONS8-1OPPORTUNITIES TO REDUCE COST AND INCREASE EFFICIENCY<br>OF POWER CONDITIONERS8-38.2.1Power Conditioning Subsystems8-38.2.2Development of Cost- and Performance-Effective,<br>Intermediate Power Conditioning Systems8-48.2.3Development of Cost- and Performance-Effective,<br>Large Power Conditioning Systems8-48.2.4Impacts of Advanced Semiconductor Devices on<br>Power Conditioner Design8-58.2.5Impacts of Advanced Magnetic Materials on<br>Power Conditioner Design8-5 |

| 8. | POWER<br>8.1 | CONDITIONING SUBSYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.3        | SAFETY          | ISSUES                                                                                                           |   |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------|---|

|            |                 | Effect of Array Grounding on Ground-Fault<br>Indicators                                                          |   |

| :          |                 | Effect of Array Grounding on PCS Logic<br>Circuits and Protective Circuit Operation 8-7                          |   |

| 8.4        | PCS AR          | RAY/INTERCONNECTION DESIGN FACTORS 8-8                                                                           |   |

| · · · · ·  | 8.4.1           | Effects of Inverter Ripple on Array<br>Energy Delivery                                                           |   |

| :          | 8.4.2           | Power Extraction Control Methods 8-8                                                                             |   |

|            | 8.4.3           | Power Conditioner to Array Size Ratio 8-9                                                                        |   |

| 8.5.       | FACTOR          | S RELATING TO UTILITY INTEGRATION 8-9                                                                            |   |

|            | 8.5.1           | Utility System Voltage Range and Voltage<br>Unbalance Effect on PV Power Conditioner<br>Design and Cost          |   |

|            | 8.5.2           | Voltage Regulation and Reactive Compensation 8-10                                                                |   |

| ۰.         | 8.5.3           | Stability                                                                                                        | 2 |

|            | 8.5.4           | Harmonics                                                                                                        | 2 |

| 8.6        | REFERE          |                                                                                                                  | 5 |

| APPENDIXES |                 |                                                                                                                  |   |

| Α.         | REACTI          | VE POWER FLOW                                                                                                    |   |

| в.         |                 | OF HARMONIC DISTORTION                                                                                           |   |

| С.         | POWER<br>Applic | CONDITIONERS AVAILABLE FOR PHOTOVOLTAIC<br>CATIONS                                                               |   |

|            |                 | and the second |   |

| · .        |                 |                                                                                                                  |   |

|            |                 |                                                                                                                  |   |

|            | ۰.              |                                                                                                                  |   |

|            |                 |                                                                                                                  |   |

|            |                 |                                                                                                                  |   |

xi

#### PART ONE

### EXECUTIVE SUMMARY

#### 1.0 BACKGROUND

As the cost of conventional fuels has increased and their availability has decreased, other methods of generating electricity have attracted a great deal of attention, particularly those methods that do not use scarce resources. Solar- and wind-based generations are examples. One of the solarbased generation technologies is photovoltaics (PV), a process that uses solidstate devices to generate electricity from sunlight. Direct current is produced and is subsequently converted to ac power. The power output range of these systems could be from a few kilowatts to greater than 10 megawatts. Photovoltaic power generation has various applications. It may be used in residential, intermediate, and central station systems and has the potential of economically displacing significant amounts of centrally generated electricity.

There are several factors that affect the design and development of a PV system. The major factors include safety and economics. The objective would be to design and build the system to maximize the return or the invested capital within the safety and operational requirements. In this process of optimization, the selection, design, and development of various parts of the PV system play important roles. The power conditioning subsystem (PCS) is one such element whose selection, design, and development affect the economic and technical viability of the PV system.

#### 2.0 PURPOSE, APPROACH, AND SELECTION

The purpose of this document is to provide an overview of power conditioning design elements, concerns, and issues for large, intermediate, and small (residential) photovoltaic systems. Specific objectives include:

- (1) Defining important issues and tradeoffs relating to the design and development of power conditioning subsystems for photovoltaic application.

- (2) Providing an integrated and generic discussion of photovoltaic systems, state of the art of power conditioning components and design, and the operational interaction between the photovoltaic (PV) systems and the host utilities.

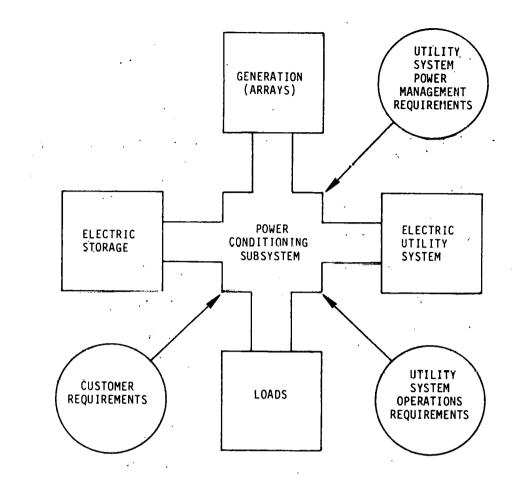

The approach to this document is based on the philosophy that the power conditioning subsystem cannot be considered by itself but must be considered as one element of an integrated photovoltaic system. The consideration must include the challenging problems of working with a highly variable dc source (variable insolation and variable characteristics of PV cells due to ambient temperature and cell-age dependence), having to meet demanding requirements from the host utility (relating to operational safety, quality of power, and reliability), and providing acceptable performance at reasonable costs.

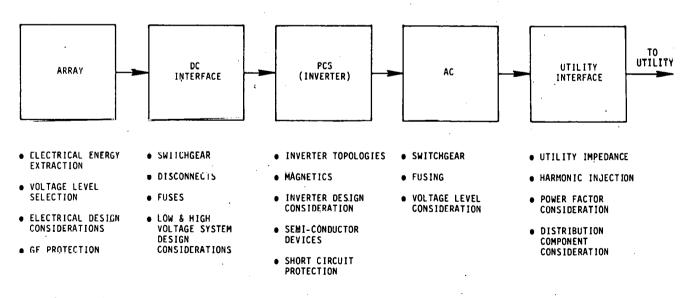

There are many external requirements being placed on the power conditioning subsystem (such as harmonics and power factor) that may preclude the use of a less complex power conversion method. The electrical characteristics

of the array and its output need to be studied to provide insight into optimal energy extraction methods and its impact on PCS sizing, cost, and rating. The PV array interface is unique in its demand on PCS design and must be clearly understood to design power conditioning equipment and to apply power conditioning technology intelligently. The utility interface impacts the PCS design cost and performance. The implication of these impacts must be understood. As the penetration of PV systems into the utility increases and more stringent utility requirements relating to power quality (harmonics), reactive power, etc., are imposed, the need for understanding the issues involved in power conditioner design and development assume an even greater importance. The current industrial power conditioning experience may not be sufficient to provide power conditioning subsystems that meet stringent cost and projected performance requirements for PV systems but will have to be augmented by the pursuit of new development opportunities.

This document begins with a historical perspective of power conversion technology in an attempt to lay the foundation for subsequent discussions. Advantages and disadvantages of rotary and solid-state power conversion technologies are provided. Generic discussions of large, intermediate, and small PV systems follow. The configuration of the PV systems, the characteristics of their elements, as well as their interactions with each other and with the host utility, are discussed. The complex nature of power conditioning designs is demonstrated and assessed by reviewing the requirements of complete PV systems in various operating modes. Fundamentals of inverters are discussed in some detail. Then specific design approaches to power conditioning for both current and advanced topologies are explored.

The aforementioned criteria establish the groundwork for defining the important issues and tradeoffs that are brought about in the development of power conditioning technologies and their applications suitable for PV application. These issues and tradeoffs are explored in depth in this document.

3.0 PHOTOVOLTAIC SYSTEM CONFIGURATON, REQUIREMENTS, AND OPERATION

#### 3.1 SYSTEM CONFIGURATION

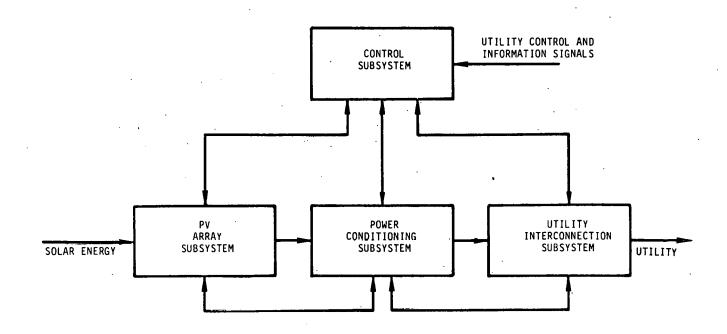

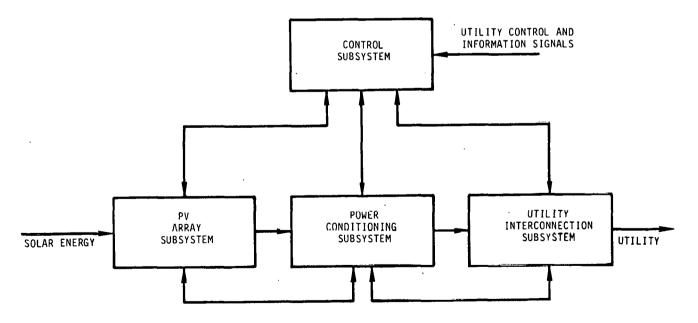

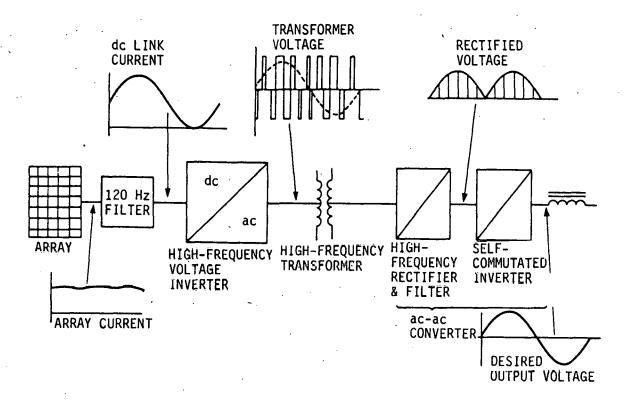

A block schematic diagram of a utility interactive photovoltaic system is shown in Figure 1. The system consists of a PV array subsystem, power conditioning subsystem, utility interconnection subsystem, and control subsystem.

The PV array subsystem converts solar energy into electrical power. It collects dc power and provides protection for PV arrays. The subsystem consists of PV cells assembled into modules, dc cabling and certain protection equipment. The cells and modules are electrically connected in series and in parallel to obtain the desired operating voltage and current levels. Means of protection for the array and means of isolating the array from the PCS are provided to facilitate the maintenance of the array. The array subsystem includes any field fuses, switches, and disconnects that may be necessary. It may include a distribution panel for array wiring and may also include experimental instrumentation.

Figure 1. Block Diagram of a Utility Interactive Photovoltaic System

PCS converts dc-power to ac-power and also does the following: regulates the amount of power extracted from the PV array at any given insolation and environmental condition, causes the desired voltage and frequency levels to be achieved at the output (ac side) of the PV system, and provides the necessary protection for the components within the PCS as well as a certain amount of protection for equipment outside the PCS. It also provides the necessary control action within the PCS.

The utility interconnection subsystem provides means for synchronization with the connection to the utility. Also, it provides the means for the isolation of the PV system from the utility when necessary. It protects the utility system from malfunctions within the PV system. Similarly, it protects the PV system from utility abnormal conditions. The subsystem may include appropriate meters and instrumentation equipment as specified within the utility interface requirements.

The control subsystem oversees the operation of the PV system and performs the following functions: provides overall coordination of system protection, communicates status information to the utility dispatch center, and if so desired, provides signals for tracking the PV array. In the case of larger PV systems it can also receive operational commands from the utility dispatch center.

#### **3.2** SYSTEM PERFORMANCE REQUIREMENTS

The system performance requirements may include requirements on efficiency, voltage regulation, voltage flicker, dc injection into the utility system, output reactive power, harmonics, and voltage unbalance.

#### 3.3 SYSTEM PROTECTION REQUIREMENTS

The PV system and the utility systems should be protected against abnormal operating conditions such as under/overvoltage, overcurrent, over or under frequency. Some of these abnormal conditions may originate either in the PV system or the utility system. If the utility bus is de-energized, the PV system should be isolated and should remain isolated until conditions permit resynchronization. Protection systems should be mutually time-coordinated to disconnect the PV system from the utility under these abnormal conditions.

#### 3.4 SYSTEM OPERATION

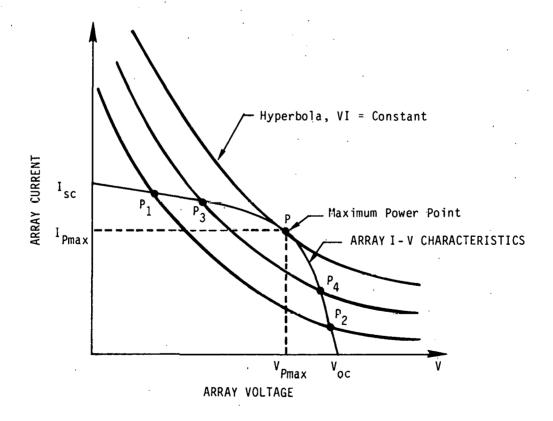

There are three possible conditions of PV system operation: constant current operation, constant voltage operation, and maximum power operation. Independent of the operational mode, the primary objective is to be able to extract maximum energy from the array. Therefore, an understanding of the array characteristics for a specific site is essential in designing an efficient PV system. In this section, PV system operation will be examined. Although these discussions will refer to flat-plate arrays, tracking arrays exhibit similar electrical behavior in a particular mode of operation.

Constant Current Operation. Because the PCS consists of solidstate components that are limited by current ratings, the PV array may be operated in a constant current mode. As a result, a fluctuation in array output power will cause PCS input voltage to change. If the dc voltage is within specified limits, constant current operation will continue; otherwise, the PCS will be shut off.

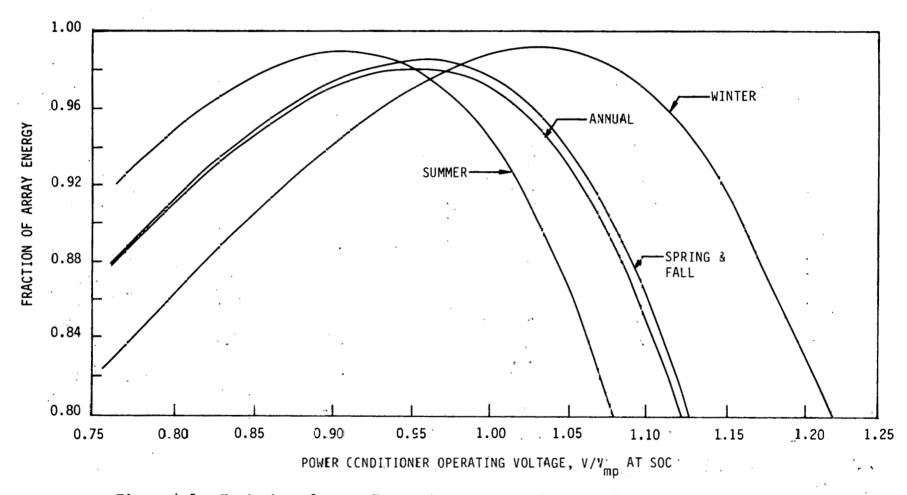

Constant Voltage Operation. Here the dc array voltage is compared with a reference value and the difference is kept to a minimum. In general, however, fixed-voltage operation does not guarantee maximum power output. Adjusting reference voltage may improve efficiency, but it requires adjustment seasonally.

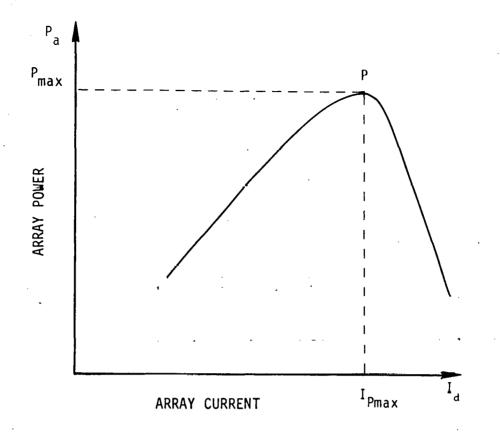

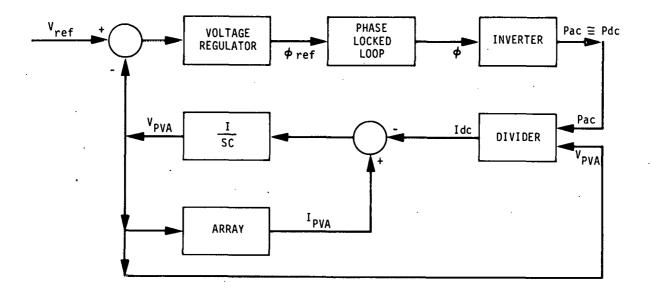

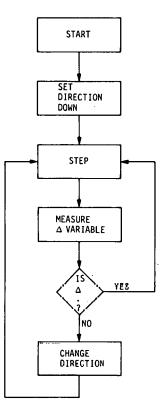

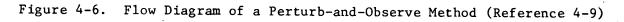

Maximum Power Operation. In this mode of operation a closed-loop feedback control system is used, PCS output power is sensed, and operation at maximum power is achieved by continuously shifting the operating point on the array characteristics. There are many schemes of maximum power tracking.

One scheme of maximum power tracking is the perturb-and-observe scheme. In this scheme, the operating point of the array/inverter combination is shifted slightly by a change in the inverter controls. The power before and after the change is compared. If the power is found to have increased, then the previous operating point was not the point of maximum power. A further change in the same direction is made. If the power is found to have decreased, the direction of the perturbation is changed, and the process repeated. When the temperature and insolation are constant, this maximum power tracker will operate in a limit cycle around the point of maximum power.

There is another interesting peak power tracking approach. In this approach, ripple power is sensed and, when ripple power is equal to zero, the maximum power point is reached.

#### 3.5 SELECTION AND SIZING OF PCS

In the selection and sizing of a PCS for a given PV array, the primary objective is to be able to capture maximum solar energy at the least possible cost. That is, the levelized energy cost or the bus bar energy cost associated with the selected PCS and the given array must be minimum. The selection of a PCS in terms of voltage, current, and power ratings must be based on the cost per unit of energy output. Therefore, the sensitivity of these ratings to the energy cost must be examined.

Voltage Rating. Selection of voltage rating of a PCS may be dictated by the application. However, presently available power conditioners have only discrete voltage ratings. As a result, there may be two ways to match the load voltage to the PCS output (ac) voltage: (1) Select a PCS with output voltage rating equal to the load voltage; and (2) Select a PCS with output voltage rating not equal to the required load voltage and use a transformer to match the load voltage. For small and intermediate size systems, power conditioning subsystems presently available have discrete dc/ac voltage ratings. For large PV systems, they are not available and have to be designed specially. Input (dc) voltage rating is provided by the manufacturer of the selected PCS or will depend on the inverter topology for a PCS if it is to be designed for special applications.

<u>Current Rating</u>. Once power and voltage ratings are determined, current ratings for ac and dc sides can be specified.

Energy Conversion Performance Factor. The energy conversion performance factor (ECPF) is a measure of the ability of the PCS to convert available array energy into usable ac output. If is defined in terms of array energy utilization capability, weighted average conversion efficiency, and miscellaneous looses.

PCS Voltage Limits. Any time the PCS is not loaded, the array open-circuit voltage will rise. Therefore, allowable dc input voltage limits for the PCS must be examined in selecting a PCS.

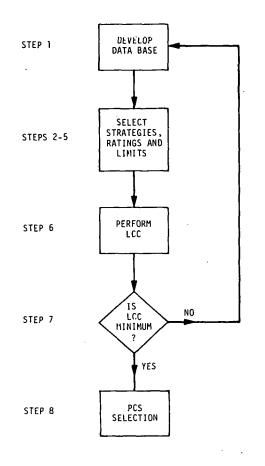

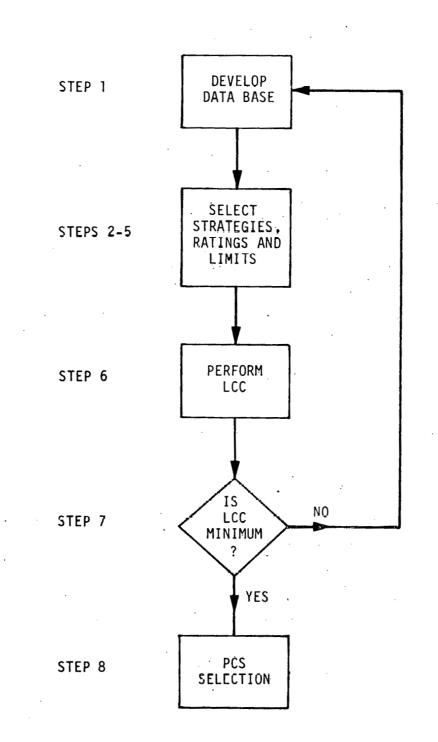

PCS Sizing and Selection. Given an array, the selection of a PCS for a small and intermediate-size, utility-interactive PV system involves the following steps:

• 5

Step 1: Develop a data base consisting of:

- (a) Weather data for the site.

- (b) Available PCS cost and performance data.

- (c) Utility operational requirements, if any.

- (d) Utility interface requirements.

- Step 2: Select shutdown, partial, or total rejection strategies for overlimit conditions.

- Step 3: Select constant voltage or maximum power operation strategy.

- Step 4: Determine power, voltage, and current ratings for the PCS.

- Step 5: Determine power, voltage, and current limits for overlimit PCS conditions.

- Step 6: Performance life-cycle cost (LCC) analysis subject to one set of variables in Steps 1 through 5.

- Step 7: Repeat Steps 1 through 6 with other sets of variables until LCC is minimum.

- Step 8: Select PCS corresponding to minimum LCC. PCS parameters and operating strategies in Steps 1 through 5 will correspond to minimum LCC.

For large PV systems, PCS cost and performance data is limited. LCC analysis in this case may be performed with respect to various PCS topologies and other variables of Steps 1 through 5. The PCS selected will ensure minimum LCC. Figure 2 is a flow chart illustrating the above procedure for selecting a PCS.

#### 4.0 INVERTER TECHNOLOGY

#### 4.1 HISTORY

In the early 1900s, the conversion of electrical energy from dc to ac was accomplished by dc motor motor/alternator rotating machines. In the late 1920s, static power converters were developed using thyratron-type (mercury arc) valves.

In the 1950s, with the development of the power transistor and the silicon controlled rectifier (SCR) and the discovery of a means of feeding reactive loads without power factor correction, a significant change occurred in the dc-to-ac inversion methodology. The need for high-efficiency and highreliability inverters for both military and space needs sparked a resurgence in the development of static inversion technology. The technologies used during the 1950s were also used for synthetic textile fiber manufacturing applications.

In the late 1950s, two developments were commercialized that resulted in the first solid-state, dc-to-ac inverter. These developments were the power transistor and the thyristor. With the early power transistors, collector voltages were typically limited to less than about 60 V. Thus, these devices were limited to low-power linear applications such as audio amplifiers. Because of their low-switching speeds, inverter applications were limited to 400 Hz and less. In contrast to power transistors, thyristors quickly developed into high-power devices capable of switching hundreds of amps at over 1000 V. By the end of the 1960s, devices rated at over 1000 A and 1500 V were in production.

During the past 20 years, semiconductor switching speeds have been improved and their costs have reduced. Self turn-off devices have been introduced. Two major thrusts have occurred:

- (1) Transistor systems are continuing to displace thyristor systems to increasingly higher power levels.

- (2) Totally new inverter and converter applications and techniques are being developed.

Bipolar transistors and thyristors have been widely used in inverter design. Gate turn-off thyristors (GTOs) are currently available for use in advanced inverter design.

Many new high-power semiconductor devices are in development. When these devices become available, new opportunities will be presented for new inverter topology development, affording potentially low-cost and highperformance power conditioner subsystems. Some devices are available in prototype or initial production phase quantities and others are in the research phase. Several of these devices are:

- (1) Gallium Arsenide Field-Effect Transistor (GaAsFET).

- (2) Insulated Gate Transistor (IGR).

- (3) Static Induction Transistor (SIT).

- (4) Field-Controlled Thyristor (FCT).

- (5) Reverse-Conduction Thyristor (RCT).

- (6) Asymmetrical Thyristor (ASCR).

Table 1 is a comparison of operating characteristics for gate turn-off devices. These include bipolar, GTO, MOSFET, SIT, FCT, GaAsFET devices. These devices have applications in both low-, medium-, and highpower applications. It should be noted that the technology distribution is toward high-frequency operation (2 MHz) and high junction temperature (200°C).

#### 4.2 FUNDAMENTALS OF INVERTERS

Various topologies of inverters are available for application in PV systems. The topologies reviewed in this report were selected out of a pool of the commercially available, breadboard-proven or only conceptually conceived inverter circuits.

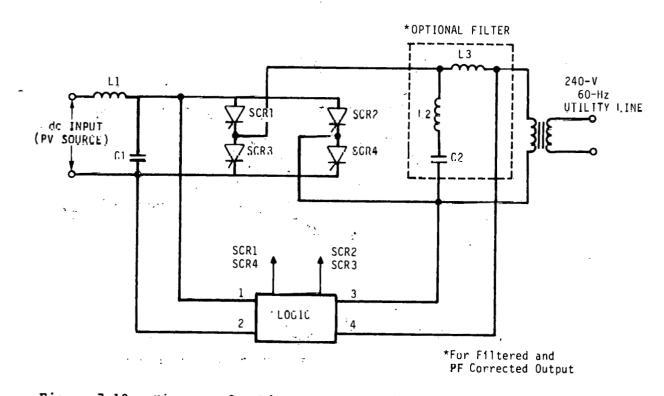

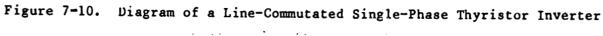

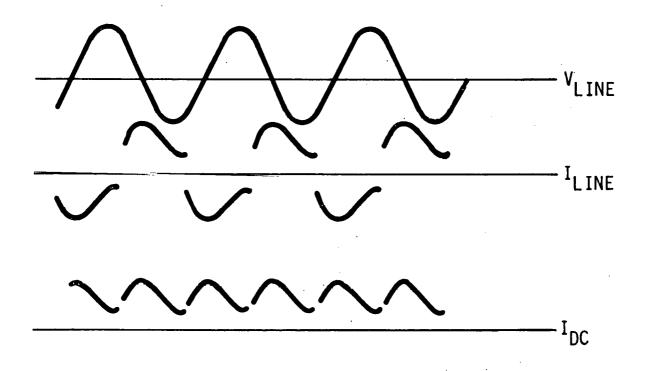

Two fundamental types of inverters are being used in utility interactive photovoltaic power conditioners: line-commutated and self-commutated. Line-commutated systems without output filters inject high levels of harmonic currents into a utility system. Line-commutated inverters with comparable performance to self-commutated inverters require output filters that approximate a large percentage of the kVA rating of the power conditioner. The effect of these large filter elements and harmonics on a utility system under large PV penetration is presently unknown.

Utility interactive inverters are divided into three categories: small, intermediate, and large inverters. These inverters are discussed as follows.

| Table 1. | Comparison d | of Operating | Characteristics | for | Gate | Turn-off De | vices |

|----------|--------------|--------------|-----------------|-----|------|-------------|-------|

|----------|--------------|--------------|-----------------|-----|------|-------------|-------|

| Device<br>Characteristic                                       | Bipolar<br>Tran-<br>sistor                                                                          | Gate Turn-<br>Off Thy-<br>ristor                              | MOSFET                                                                       | JFET and<br>Static<br>Induction<br>Transistor | Field-<br>Controlled<br>Thyristor<br>(FCT) | GaAs<br>FET  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------|--------------|

| Normally On/Off                                                | Off                                                                                                 | Off                                                           | Off                                                                          | On                                            | On                                         | On/Off       |

| Reverse Block-<br>ing Capability,<br>V                         | ≈ 50                                                                                                | 500 to<br>2500                                                | 0                                                                            | 0                                             | 500 to<br>2500                             | 0            |

| Breakdown Volt-<br>age Range                                   | 50 to<br>500                                                                                        | 500 to<br>2500                                                | 50 to<br>500                                                                 | 50 to<br>500                                  | 500 to<br>2500                             | 50 to<br>500 |

| Forward Conduc-<br>tion Current<br>Density,* A/cm <sup>2</sup> | 40                                                                                                  | 100                                                           | 10                                                                           | 10                                            | 100                                        | 100          |

| Surge-Current-<br>Handling<br>Capability                       | Poor                                                                                                | Good                                                          | Poor                                                                         | Poor                                          | Good                                       | Poor         |

| Maximum Switch-<br>ing Speed<br>(approximate)                  | 200 kHz                                                                                             | 20 kHz                                                        | 2 MHz                                                                        | 2 MHz                                         | 20 kHz                                     | 2 MHz        |

| Gate-Drive<br>Power                                            | High<br>(large<br>base-drive<br>current<br>required<br>during on-<br>state and<br>for turn-<br>off) | Medium<br>(large<br>turn-off<br>gate<br>currents<br>required) | Low<br>(only<br>small<br>capaci-<br>tive<br>charging<br>currents<br>required | Low                                           | Medium                                     | Low          |

| Operating<br>Temperature,<br><sup>o</sup> C                    | 150                                                                                                 | ≈125                                                          | 200                                                                          | 200                                           | 200                                        | 200          |

"The forward current densities are compared here for 500-V devices operating at a forward voltage drop of 1.5 V.

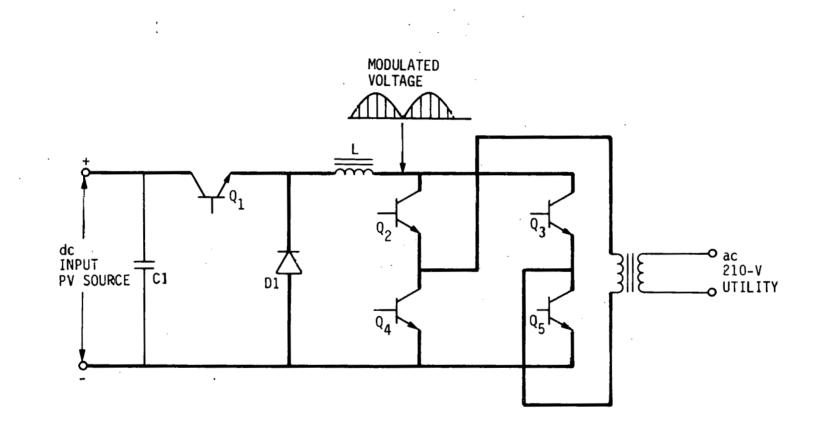

<u>Small Inverters (1 to 15 kW)</u>. Small inverters are residentialsize units intended to link the photovoltaic source with the utility for the parallel system operation. Rating of the units does not exceed 15 kW. Inversion is single-phase, with ac output of 240 V.

There is a strong trend toward the use of transistors instead of thyristors for power switching; however, some thyristor inverters are still being produced and installed. In addition, the emergence of the GTO thyristor has created new opportunities that are beginning to be exploited. Selected configurations that are reviewed are as follows:

#### Single-Phase Small Inverters

| Inverter Type                     | Power Semiconductor Usage |

|-----------------------------------|---------------------------|

| Transistor, single-bridge         | Transistor                |

| Transistor, dual-bridge           | Transistor                |

| Gate turn-off, half-bridge        | Gate turn-off thyristor   |

| High-frequency link               | Transistor                |

| Line-commutated                   | Thyristor                 |

| dc/dc converter controlled bridge | Transistor                |

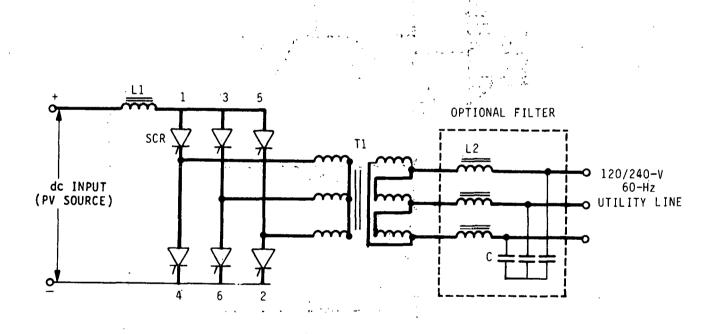

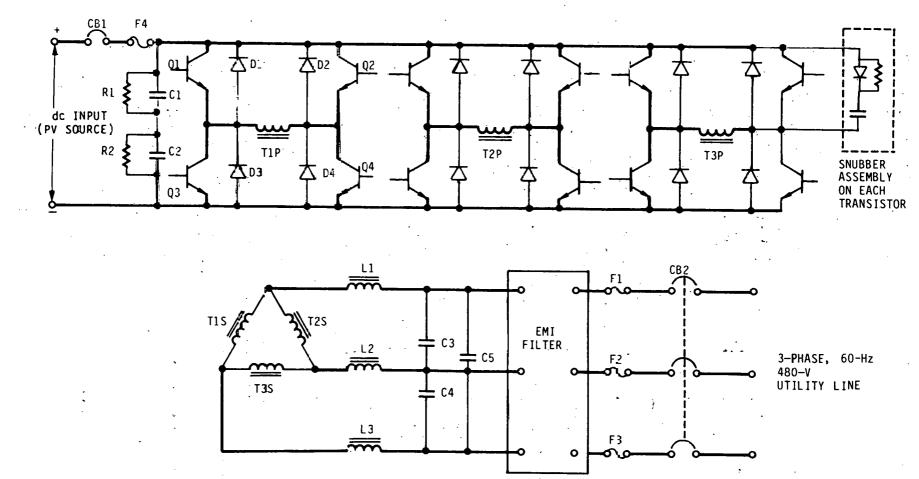

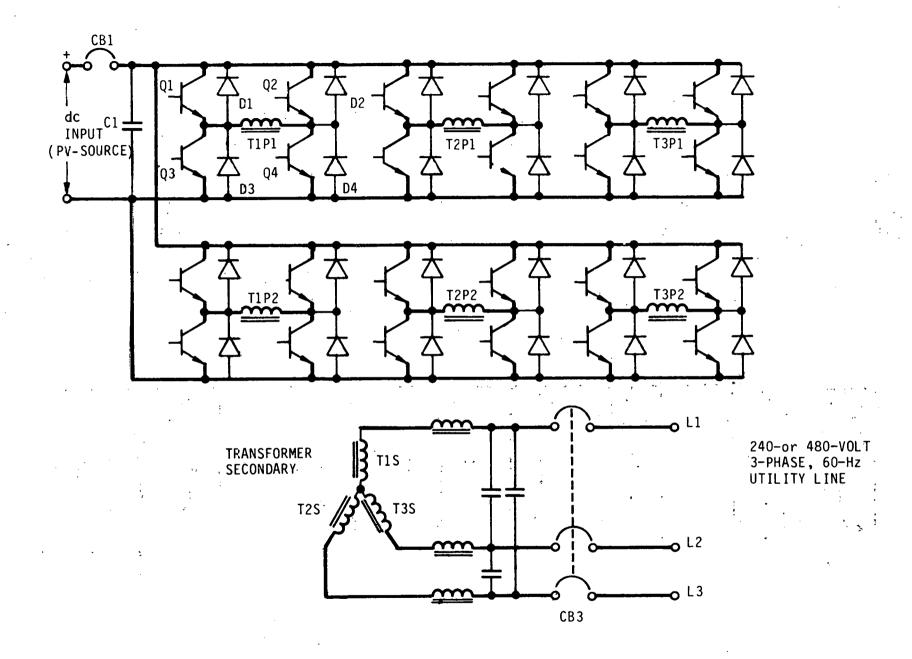

Intermediate Inverters (15 to 1000 kW). Inverters in the intermediate-size range are intended to provide power conversion for photovoltaic systems for various industrial, commercial, and agricultural customers. They will be operating in parallel with the utility. The inverter output power will be delivered at 208 V or 480 V, 3-phase, 60 Hz. Certain applications require a utility interface at 3 kV or above.

The majority of the commercially available inverters use thyristors for power switching. Some advanced configurations, which include GTOs and power transistors, are presently being evaluated for efficiency, reliability, and cost. Selected configurations that are reviewed are as follows:

#### Three-Phase Intermediate Inverters

| Inverter Type                   | Power Semiconductor Usage |

|---------------------------------|---------------------------|

| Six-pulse, line-commutated      | Thyristor                 |

| Twelve-pulse, line-commutated   | Thyristor                 |

| Transistorized bridge           | Transistor                |

| Pulse-width modulated six-pulse | Transistor                |

| Twelve-pulse inverter           | Transistor                |

| Gate turn-off, six-puloc        | Gate turn=off thyristor   |

| Hybrid                          | GTOs and thyristor        |

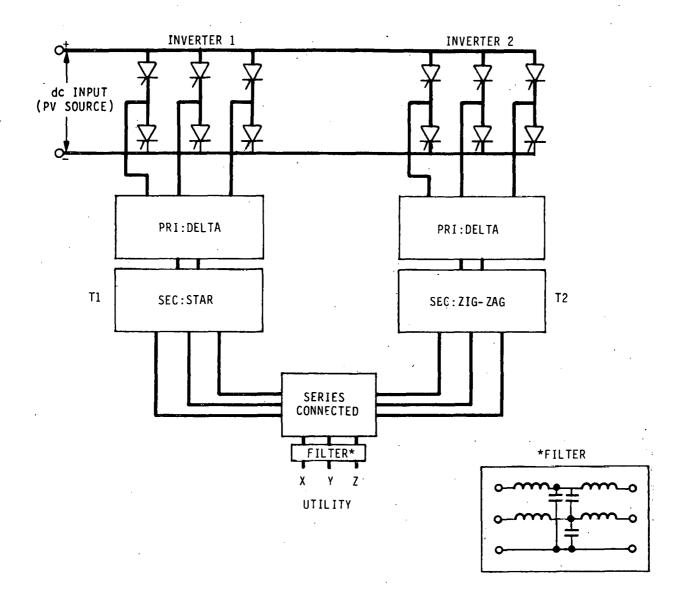

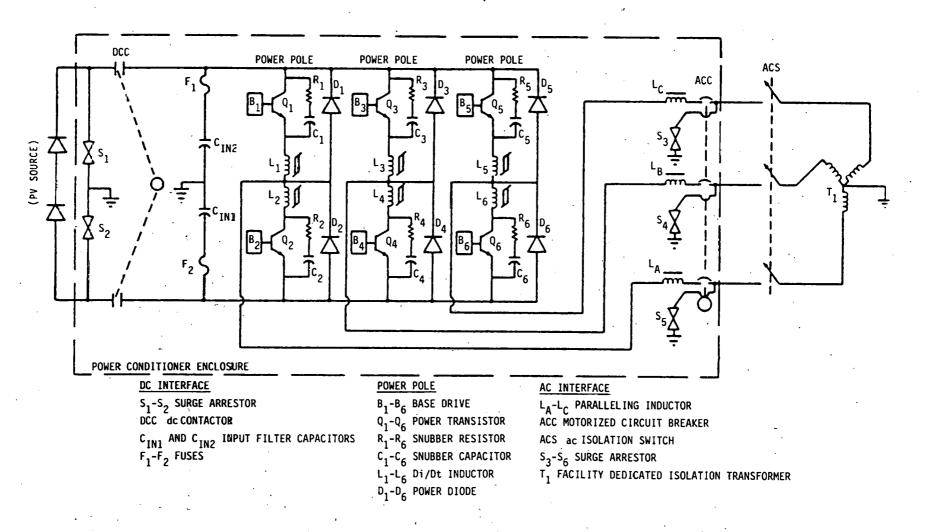

Large Inverters (Above 1 MW). Large inverters are used to provide the power conversion for photovoltaic systems for small generating stations that will partially supply power to small communities or become part of the dispersed power generation system of the future.

The power inverter consists of one or more high-power bridges of a three-phase variety. Thyristors for high-power applications are paralleled to increase the inverter power handling capability. Paralleling of the individual power conditioner units is used if increased power is required. Selected configurations that are reviewed are as follows:

#### Three-Phase Large Inverters

| Inverter Type                                              | Power Semiconductor Usage |

|------------------------------------------------------------|---------------------------|

| Six-pulse, line-commutated, 1-MW                           | Thyristors                |

| Twelve-pulse, line-commutated                              | Thyristors                |

| Twelve-pulse, self-commutated, 500-kW, 750-kW              | Thyristors                |

| Eighteen-pulse, self-commutated,<br>4.8 MW                 | Thyristors                |

| Chopper-controller, line-commutated,<br>twelve-pulse, 5-MW | GTOs and thyristors       |

5.0

NEEDED RESEARCH AND OPPORTUNITIES FOR DEVELOPING IMPROVED POWER CONDITIONING SUBSYSTEMS

Power conditioning subsystem technology has advanced rapidly in cecent years. As experience has been acquired, various requirements for PCS cost, performance, safety, and utility integration have surfaced. The current understanding of these requirements and their implications for PCS design are detailed in the document. Many of these power conditioner subsystems use microprocessor control and have what may be constituted a "brain." They do not require the usual synchronizing and protective relaying that are essential for conventional cogeneration and dispersed energy systems connected to the utility line. These units were developed to provide this intelligence by internal electronic means to reduce PCS costs because conventional synchronizing and protective relaying would have increased PV system costs excessively. Experience has shown that acceptable integrated operation can be expected with proper PCS design; however, there are still unknowns in the design of a utility interactive power conditioner subsystem.

With the development of advanced circuit topologies, losses and costs associated with filters in line- and self-commutated inverters can be materially reduced. In addition, costs and power losses associated with commutation circuitry in self-commutated systems can be substantially reduced. These cost- and power-loss reductions can provide for power conditioner subsystems of substantially improved cost, efficiency, and performance.

It is apparent that static and dynamic voltage and frequency changes on the utility system can seriously affect PCS design. Audible noise is also a concern because most small photovoltaic power conditioners may be installed inside a residence or in a critical work area. To meet adequate cost and electrical performance requirements, there are serious concerns in meeting various safety codes to guarantee the safety of users as well as PCS maintenance and utility personnel. A detailed description is provided of the current open issues and concerns that remain for the power conditioner subsystem designer to consider.

#### STANDARDS, GUIDELINES, AND SPECIFICATIONS

5.1

Standards, guidelines, and specifications are needed to inform manufacturers, utilities, and consumers about the specifics of adequate performance, characteristics, and safety concerns related to the design, manufacture, and installation of power conditioning subsystems.

Insolation characteristics over an operational day will vary in different parts of the United States. Power conditioning efficiencies at full or part loads do not necessarily reflect energy efficiency of the power conditioner with specified insolation profile. Thus, the energy efficiency for power conditioners will vary in different parts of the United States.

Different types of arrays such as flat plates, concentrator arrays, and tracking flat-plate arrays will have power output characteristics that will differ from each other even though operating in the same environment. Yower conditioning efficiencies, either at full load or part loads, are predicted upon power conditioning design. Thus, one power conditioner may have a high efficiency at full load and only a modest efficiency at one-quarter load. Another power conditioner may be designed for high efficiency at a three-quarter load and a somewhat lower efficiency at full load. The net effect is that power efficiency may in fact not reflect the important significant function of a power conditioner, which is to process the maximum amount of energy available. It is suggested that a figure of merit be determined for each power conditioner that will relate the available insolation characteristics (in a particular region where the PCS will be used) to the PCS energy efficiency. This will allow the system designer and/or the consumer to choose a power conditioner for a specific PV system by proper tradeoff of power conditioning cost and energy efficiency of the power conditioner.

Because of discrepancies in available documents, there is substantial confusion in determining design practice by system designers and power conditioning manufacturers in determining acceptable functional and safety requirements and performance parameters. Acceptable terms of design and integration for one region of the country may be unacceptable in another region. Currently, there are various national and international groups whose objectives include the development of standards, guidelines, and specifications. There are proposed modifications for the 1984 National Electrical Code (NEC) relating to photovoltaic integration that, if approved, will be in Section 690 of the Code. There are also various activities in the Institute of Electrical and Electronic Engineers (IEEE) Photovoltaics Power Conditioning Subcommittee, both in the area of power conditioning recommended practice and power conditioning testing recommended practice. The IEEE Photovoltaic System Subcommittee has promulgated a trial standard for integration of small and intermediate photovoltaic systems into a utility.

There are currently no acceptable standards or requirements for electromagnetic interference (EMI) and radio frequency interference (RFI) for power conditioning subsystems. Current field testing by the National Bureau of Standards reflects that most of the units tested interfered with AM-band radio operation, indicating the need for EMI filters for the PCS. Development of EMI and RFI standards and guidelines would assist power conditioning manufacturers to determine requirements for acceptable operation of power conditioning subsystems.

Currently, there are no definitive design guidelines for power conditioning subsystems. However, some of these activities have had substantial efforts to date.

#### 5.2

#### OPPORTUNITIES TO REDUCE COST AND INCREASE EFFICIENCY OF POWER CONDITIONERS

Acceptable photovoltaic power conditioning subsystem hardware can be defined as hardware that satisfies the performance and safety needs of a photovoltaic utility interactive installation. There are various concerns relating to the design and development of such power conditioning subsystem hardware that affect safety, performance, and cost. The optimum design configuration of a power conditioning subsystem would reflect low-cost and acceptable performance. Such factors as the dc array voltage, harmonics, power factor, and safety also affect cost and performance; therefore, they also have a direct impact on power conditioning design.

<u>Power Conditioning Subsystems</u>. Transformerless power conditioning subsystems have potential advantages over systems that contain isolation transformers. Transformers add substantially to the cost and size of the power conditioner as well as to a reduction of power conditioning subsystem efficiency. Transformerless systems can also reduce audible noise. The various concerns that must be answered for satisfactory transformerless systems relate to National Electric Codes, effects on distribution component ratings, ground-fault detector operation, dc-current injection, and effects on utility operation.

Development of Cost- and Performance-Effective, Intermediate Power Conditioning Systems. With advanced semiconductor components there is an opportunity to develop new circuit configurations that reduce PCS cost and improve performance. The new circuit configurations will allow for process-intensive designs instead of material-intensive designs (large magnetic and capacitor structures) for medium-size power conditioners.

<u>Development of Cost- and Performance-Effective, Large Power</u> <u>Conditioning Systems</u>. The cost and performance of large power conditioners is limited by the availability of new, advanced semiconductors with improved switching speeds. Thus, with newly developed semiconductors, large power conditioning subsystems that reflect process-intensive designs with low cost and high performance should be possible. Can commutation components be eliminated for self-commutated designs? What is an acceptable array dc voltage for minimum levelized energy cost? What new design opportunities exist for very large PV systems (above 50 MW)?

Impacts of Advanced Semiconductor Devices on Power Conditioner Design. The new, advanced, high-power semiconductor devices that are becoming available are high-voltage, high-current transistors; high-speed, high-voltage, gate turn-off control rectifiers; and induction-type thyristors (high-speed, high-voltage, high-current devices) will impact PCS design. Several of the major power conditioning research organizations under contract to the Department of Energy have indicated that advanced, megawatt-size power conditioner implementation PCS should be oriented toward the use of gate turn-off devices for next-generation PCS hardware. At present, there are no medium or highpowered inverters using GTOs available in this country in either the UPS, photovoltaics, or other dispersed-storage and generation markets.

#### Impacts of Advanced Magnetic Materials on Power Conditioner Design. New magnetic materials (amorphous steels, etc.) can be integrated in designs so that they can be manufactured in an economical and practical method to satisfy the needs of photovoltaic power conditioners.

Harmonic Current Effects on PV Filter Components. Research to determine the power spectrum and magnitude of harmonics on existing utility lines would be of significant value to designers of power conditioner filters. This would assist PCS designers to consider the effect of utility-line harmonics on filter component selection and sizing.

<u>Power Conditioner Self-Excitation</u>. If a power conditioner self excites and reapplication of utility voltage occurs out of phase of the self-excited generator voltage, large surges of current will flow. This large, out-of-phase current may damage components of the power conditioner. When there is a utility disconnect, the power conditioner must turn off immediately under all conditions of load and in the presence of other connected generators. In addition, self-excitation may provide unsafe conditions for maintenance personnel. Although this design requirement is understood, the best approach to meeting it has not been determined. Several manufacturers are doing development and testing of residential PCSs to meet this need. Sandia National Laboratories and various utilities are also conducting intensive testing with positive results reported.

#### 5.3 SAFETY ISSUES

It is important that PV systems connected to a utility system should not cause any safety hazard to either the PV source owners or to utility personnel. The safe installation of residential, commercial, and industrial electrical systems is guided by the National Electrical Code (NEC), which is published by the National Fire Protection Association (NFPA) every 3 years. The current code does not address photovoltaics. It is anticipated that revisions to the NEC (1984) will emphasize the unique aspects of photovoltaics and address those concerns that could result in an unsafe installation. Some issues of concern are grounding of PV arrays and the PCS, electrical isolation (through a transformer) of the PV system from the utility system, and disconnection of the PV array from the PCS and the PCS from the utility during times of maintenance. These and other issues directly related to safety must be thoroughly analyzed and included in any revision of the code.

Effect of Array Grounding on Ground Fault Indicators and PCS Logic Circuits and Protective Circuit Operation. Array grounding or equivalent is required by code. Code requirements relate to small and intermediate systems. Large utility systems do not necessarily follow national electrical code with regard to grounding. In large systems, major design concerns are protection of personnel, protection of equipment, and safety of maintenance personnel.

Arrays may be positive or negative-ground or center-tap ground. There is reason to believe that the National Electrical Code, when approved, will allow for equivalency of grounding with approved photovoltaics power conditioners. Currently, large systems use either center-tapped ground or high-resistance, center-tapped ground. Due to the various grounding methods, it is unknown whether available ground-fault detectors, protective circuits, interrupters, and conventionally designed power conditioning logic circuits will operate reliably.

#### 5.4 PCS ARRAY/INTERCONNECTION DESIGN FACTORS

Various factors affect the efficient extraction of energy from the array. Factors other than those that affect energy production (insolation levels, wind, temperature, and array degradation) are:

- (1) Inverter ripple.

- (2) Power extraction control methods.

- (3) The ratio of power conditioner rating to array rating.

*...* .

Effects of Inverter Ripple on Array Energy Delivery. Excessive array ac ripple due to the inverter can affect array energy extraction by reducing effective array energy output. There have been several curves published that quantify the loss in energy production to ripple level. The validity of these curves should be verified by testing.

Power Extraction Control Methods. Two methods of power extraction have been basically detailed for photovoltaic systems. One method tracks the maximum power point of the array I-V curve. The other method operates the array at fixed voltage.

Whether maximum power tracking is in fact an improvement over fixed-voltage operation will ultimately require empirical data on both cost, PCS sizing, efficiency, and reliability. Additional field engineering evaluation is required to determine the effectivity of the different maximum-power trackers and evaluating the differences of maximum-power tracker operation and fixed-voltage operation.

Power Conditioner to Array Size Ratio. Inverter design and requirements will be affected if it is required to process less than 100% of the energy developed by the array at nominal operating voltage. The ability

to process less than 100% of the array can be economically desirable. Design procedures are needed that will allow power conditioner size to be selected in a manner that minimizes the cost of power production.

#### 5.5 FACTORS RELATING TO UTILITY INTEGRATION

Utility System Voltage Range and Voltage Unbalance Effect on PV Power Conditioner Design and Cost. Excessive voltage unbalance can cause problems with power conditioning operation, component overheating, and nuisance tripping of power conditioning protective devices. Utility system voltage range will affect the power conditioning cost according to the range required by specification.

Better information on actual voltage ranges and the degree of voltage unbalance experienced could be of help in minimizing power losses and the cost of PCS components. Ultimately the cost to the utility for improving its voltage regulation needs to be traded off against the cost of PV system accommodating voltage deviation and unbalance. While ultimately important, this type of research is site specific.

Voltage Regulation and Reactive Compensation. Utilities must maintain the voltage at the customer's terminals with limits specific in tariff schedule offered to the customer.

When PV systems are connected to the utility distribution system, voltage regulation is affected and must be considered:

- (1) Improved models will need to be developed for the PV systems, voltage regulators, and the loads.

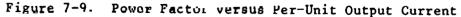

- (2) Line-commutated converters operate at lagging power factors. In other words, they draw reactive volt amperes (VARs) from the system. The utility system must be in a position to supply the additional VARs in addition to the VARs needed to satisfy the load requirements. A self-commutated inverter can be operated at a unity power-factor or possibly even a leading power factor. At this stage, however, it is not clear that a unity power factor converter is the answer because the ratio of volt amperes to watts at the substation would still be rather high.

Further research is required, particularly to determine the effects on voltage at the point of interconnection of the system to the utility.

<u>Stability</u>. Source or system stability is defined as the ability of an individual or multiple PV systems connected to the utility system to maintain operation without large fluctuations in voltage, power, etc.

Any such fluctuations in output parameters could cause nuisance tripping of the PV source following a disturbance. In some cases, it could also cause damage to the PV system. Any undesirable interaction between various PV

systems connected to the same distribution system could cause nuisance tripping at the lateral feeder or substation level, causing unnecessary outages to customers. It could also result in damage to customer equipment connected to the system.

Harmonics. The term "harmonics," as used in this document, is the maximum amount of voltage and/or current harmonics produced by a PV system (at its terminals) when connected to a utility power system. Harmonics (both current and voltage) have many undesirable effects associated with them. Excessive harmonics can cause problems with the utility power system with connected loads and with communication equipment.

The risk that any of the undesirable effects of harmonics will manifest themselves depends largely on the characteristic of the utility and its connected load. Power conditioner designers currently face a great deal of uncertainty concerning the level of harmonics that are tolerable in a given application.

Research is needed to finally establish standards that balance the risk of problems with the cost of limiting harmonics. The research would involve determining the maximum allowable harmonic limits at any point on the system and translation of this number into an allowable harmonic injection (voltage or current) at the terminals of the converter. This limit would depend on the characteristics of the distribution system, background harmonic level from other sources on the system and, most importantly, to the penetration level (both local and system-wide) of PV sources. System simulation and field measurements are a necessary part of this research.

#### PART TWO

#### PHOTOVOLTAIC POWER CONDITIONING SUBSYSTEM:

STATE OF THE ART AND DEVELOPMENT OPPORTUNITIES

# THIS PAGE WAS INTENTIONALLY

· · · ·

• • .

## LEFT BLANK

• • •

. .

. .

.

<u>ي</u> .

. :

· • • •

· ·

- 4.

•-

TBAL Jerti

•

•

. •

#### SECTION 1

#### PURPOSE AND APPROACH

#### 1.1 PURPOSE

The purpose of this document is to provide an overview of power conditioning design elements, concerns, and issues for large, intermediate, and small (residential) photovoltaic (PV) systems. Specific objectives include:

- (1) Defining important issues and tradeoffs relating to the design and development of power conditioning subsystems for photovoltaic application.

- (2) Providing an integrated and generic discussion of photovoltaic systems, state of the art of power conditioning components and design, and the operational interaction between the PV systems and the host utilities.

#### 1.2 APPROACH

The approach to this document is based on the philosophy that the power conditioning subsystem (PCS) cannot be considered by itself but must be considered as one element of an integrated photovoltaic system. The consideration must include the challenging problems of working with a highly variable dc source (variable insolation and variable characteristics of PV cells due to ambient temperature and cell-age dependence), having to meet demanding requirements from the host utility (relating to operational safety, quality of power, and reliability), and providing acceptable performance at reasonable costs.

There are many external requirements being placed on the power conditioning subsystem (such as harmonics and power factor) that may preclude the use of a less complex power conversion method. The electrical characteristics of the array and its output need to be studied to provide insight into optimal energy extraction methods and its impact on PCS sizing, cost, and The PV array interface is unique in its demand on PCS design and must rating. be clearly understood to design power conditioning equipment and to apply power conditioning technology intelligently. The utility interface impacts the PCS design cost and performance. The implication of these impacts must be understood. As the penetration of PV systems into the utility increases and more stringent utility requirements relating to power quality (harmonics), reactive power, etc., may be imposed, the need for understanding the issues involved in power conditioner design and development assume an even greater importance. The current industrial power conditioning experience may not be sufficient to provide power conditioning subsystems that meet stringent cost and projected performance requirements for PV systems but will have to be augmented by the pursuit of new development opportunities.

í

This document begins with a historical perspective of power conversion technology in an attempt to lay the foundation for subsequent discussions. Advantages and disadvantages of rotary and solid-state power conversion technologies are provided. Generic discussions of large, intermediate, and small PV systems follow. The configuration of the PV system, the characteristics of their elements, as well as their interactions with each other and with the host utility, are discussed. The complex nature of power conditioning designs is demonstrated and assessed by reviewing the requirements of complete PV systems in various operating modes. Fundamentals of inverters are discussed in some detail. Then specific design approaches to power conditioning for both current and advanced topologies are explored.

The aforementioned criteria establish the groundwork for defining the important issues and tradeoffs that are brought about in the development of power conditioning technologies and their applications suitable for PV application. These issues and tradeoffs are explored in depth in this document.

. .

#### SECTION 2

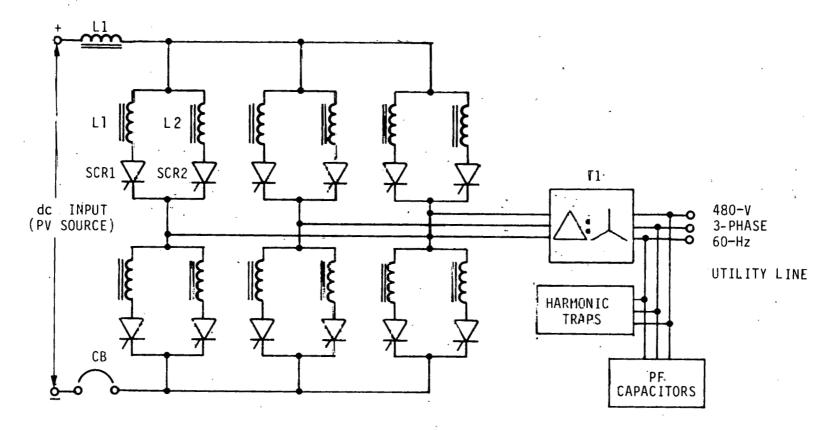

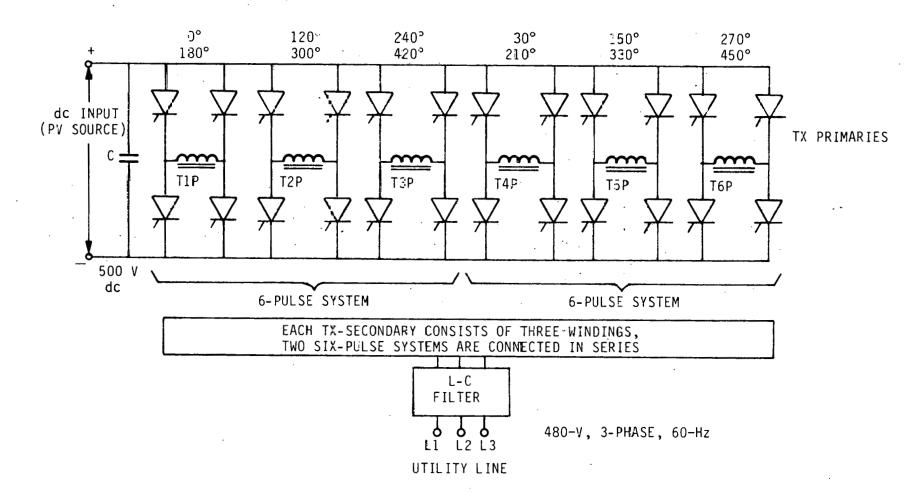

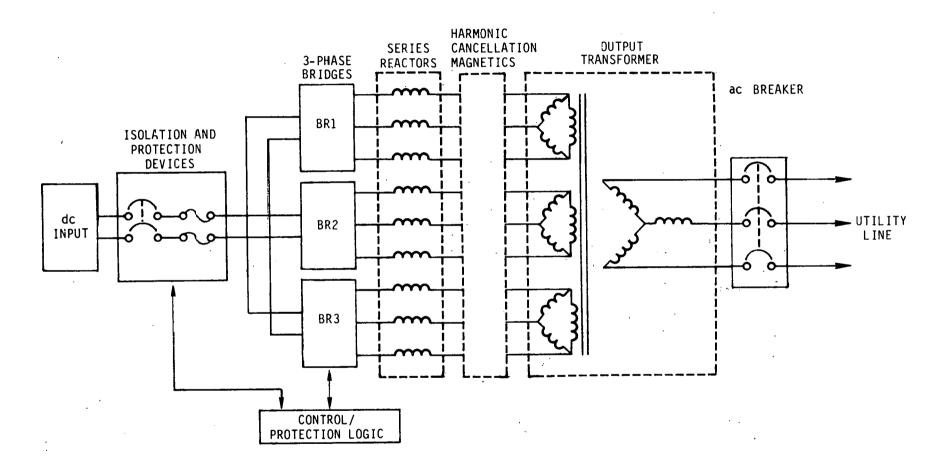

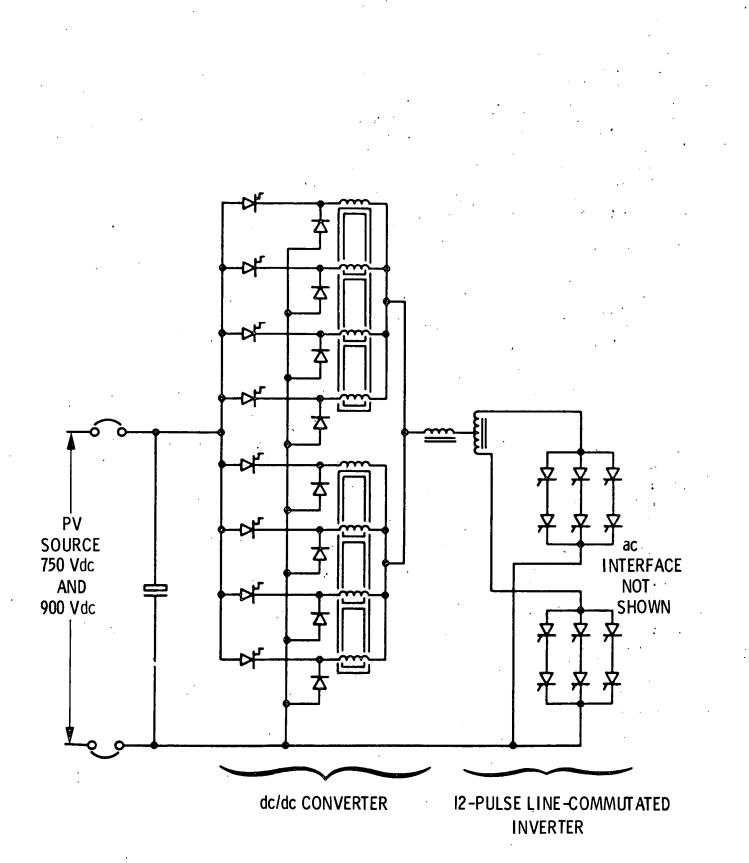

## INTRODUCTION