Nat.Lab. Unclassified Report 2003/00239

Date of issue: April 2003

# Physical Background of MOS Model 11 Level 1101

R. van Langevelde, A.J. Scholten and D.B.M. Klaassen

Unclassified Report <sup>©</sup>Koninklijke Philips Electronics N.V. 2003

Authors' address data: R. van Langevelde WAY41; Ronald.van.Langevelde@philips.com A.J. Scholten WAY41; Andries.Scholten@philips.com D.B.M. Klaassen WAY41; D.B.M.Klaassen@philips.com

> <sup>©</sup>Koninklijke Philips Electronics N.V. 2003 All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

| Unclassified Report: | 2003/00239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title:               | Physical Background of MOS Model 11<br>Level 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Author(s):           | R. van Langevelde, A.J. Scholten and D.B.M. Klaassen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Part of project:     | Compact modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Customer:            | Philips Semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Keywords:            | MOS Model 11, compact modelling, MOSFET, CMOS, circuit simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      | integrated circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Abstract:            | <ul> <li>A new compact model for MOS transistors has been developed, MOS Model 11 (MM11), the successor to MOS Model 9. MM11 not only gives an ac curate description of charges and currents and their first-order derivative (transconductance, conductance, capacitances), but also of their higher order derivatives. In other words, it gives an accurate description of MOS FET distortion behaviour, and as such MM11 is suitable for digital, analog as well as RF circuit design.</li> <li>MOS Model 11 is a symmetrical, surface-potential-based model. It in cludes an accurate description of all physical effects important for mod ern and future CMOS technologies, such as, e.g., gate tunnelling current gate-induced drain leakage, influence of pocket implants, poly-depletion quantum-mechanical effects and bias-dependent overlap capacitances. Including all of the above, MOS Model 11 achieves superior accuracy a compared to MOS Model 9 without an increase in the number of parameters and with only a slight increase in simulation time.</li> <li>The goal of this report is to present the complete physical background of MM11, Level 1101, including a description of steady-state currents charges and noise sources. This report gives a more in-depth description and derivation of the model equations as used in the report NL-UI</li> </ul> |

# List of Symbols

This list is not a complete list of the symbols used in this report, it excludes those symbols which are only used locally in a particular chapter. In the following, subscripts i and j denote one of the MOSFET terminals, i.e., drain (D), gate (G), source (S) or bulk (B).

| Symbol                     | Unit             | Description                                                                                                                                 |  |

|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| $A_{\mathrm{GIDL}}$        | $AV^{-3}$        | Gain factor for gate-induced drain leakage current, see Section 4.2                                                                         |  |

| $B_{\rm GIDL}$             | V                | Probability factor for gate-induced drain leakage current, see Section 4.2                                                                  |  |

| Bacc                       | V                | Probability factor for gate tunnelling current in accumulation, see Section 5                                                               |  |

| $B_{ m inv}$               | V                | Probability factor for gate tunnelling current in inversion, see Section 5                                                                  |  |

| $C_{\mathrm{GIDL}}$        | —                | Factor for the lateral field dependence of the gate-induced drain leakage current, see Section 4.2                                          |  |

| $C_{ m GDO}$               | F                | Oxide capacitance for the gate–drain overlap, see Section 6.2                                                                               |  |

| $C_{\rm GSO}$              | F                | Oxide capacitance for the gate-source overlap, see Section 6.2                                                                              |  |

| $C_{\rm OX}$               | F                | Total gate oxide capacitance, $C_{\rm OX} = C_{\rm ox} \cdot W \cdot L$                                                                     |  |

| $C_{\mathrm{b}}$           | F/m <sup>2</sup> | Linearisation factor of $Q_{\rm b}, C_{\rm b} = - \partial Q_{\rm b} / \partial \psi_{\rm s} _{\psi_{\rm s} = \bar{\psi}}$                  |  |

| $C_{g}$                    | F/m <sup>2</sup> | Linearisation factor of $Q_{\rm g}, C_{\rm g} = - \partial Q_{\rm g} / \partial \psi_{\rm s} \big _{\psi_{\rm s} = \bar{\psi}}$             |  |

| $C_{ m ij}$                | F                | Transcapacitance between node $i$ and $j$ , see eq. (6.5)                                                                                   |  |

| $C_{ m inv}$               | F/m <sup>2</sup> | Linearisation factor of $Q_{\rm inv}$ , $C_{\rm inv} = -\partial Q_{\rm inv} / \partial \psi_{\rm s} _{\psi_{\rm s}=\bar{\psi}}$            |  |

| $C_{\rm ox}$               | F/m <sup>2</sup> | Gate oxide capacitance per unit area, $C_{\rm ox} = \epsilon_{\rm ox}/t_{\rm ox}$                                                           |  |

| $\mathcal{E}_{\mathrm{C}}$ | eV               | Energy level of lower edge of conduction band                                                                                               |  |

| $\mathcal{E}_{\mathrm{F}}$ | eV               | Fermi energy level                                                                                                                          |  |

| $\mathcal{E}_{\mathrm{V}}$ | eV               | Energy level of upper edge of valence band                                                                                                  |  |

| $\mathcal{E}_{g}$          | eV               | Energy bandgap between $\mathcal{E}_{C}$ and $\mathcal{E}_{V}$ in silicon, $\mathcal{E}_{g} = 1.12 \text{eV}$ at $T = 300 \text{K}$         |  |

| $E_{\rm Si}$               | V/m              | Transversal electric field at Si/SiO <sub>2</sub> -interface, $E_{Si} = Q_g/\epsilon_{Si}$                                                  |  |

| $E_{\rm eff}$              | V/m              | Effective transversal electric field, see Section 3.3.1                                                                                     |  |

| $E_{\rm ox}$               | V/m              | Transversal electric field in gate oxide, $E_{\rm ox} = Q_{\rm g}/\epsilon_{\rm ox}$                                                        |  |

| $E_{\rm x}$ , $E_{\rm y}$  | V/m              | Lateral $(E_x = -\partial \psi / \partial x)$ and transversal $(E_y = -\partial \psi / \partial y)$ electric field                          |  |

| $G_{R}$                    | _                | Expression for series resistance, see Section 3.4                                                                                           |  |

| $G_{\mathrm{Th}}$          | _                | Expression for self-heating, see Section 3.6.3                                                                                              |  |

| $G_{ m mob}$               | _                | Expression for mobility reduction, see Section 3.3.1                                                                                        |  |

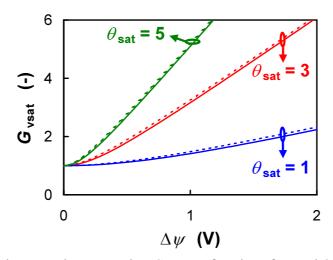

| $G_{\rm vsat}$             | _                | Expression for velocity saturation, see Section 3.3.2                                                                                       |  |

| $G_{\rm tot}$              | _                | Expression for mobility reduction, velocity saturation, series resistance, channel length modulation and self-heating, see Sections 3.3-3.6 |  |

| $G_{\Delta \mathrm{L}}$    | _                | Expression for channel length modulation, see Section 3.6.1                                                                                 |  |

| $I_{\rm GINV}$             | $AV^{-2}$        | Gain factor for intrinsic gate tunnelling current in inversion, see Section 5.1                                                             |  |

| $I_{\text{GACC}}$          | $AV^{-2}$        | Gain factor for intrinsic gate tunnelling current in accumulation, see Section 5.2                                                          |  |

| $I_{\rm GOV}$              | $AV^{-2}$        | Gain factor for source/drain overlap gate tunnelling current, see Section 5.3                                                               |  |

©Koninklijke Philips Electronics N.V. 2003

| Symbol                                            | Unit               | Description                                                                                                                                       |

|---------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{\mathrm{G}_{\mathrm{ov}}}$                    | А                  | Gate current in gate-source $(I_{\text{Gov}_0})$ or gate-drain $(I_{\text{Gov}_L})$ overlap region, see Section 5.3                               |

| $I_{\rm drift}$ , $I_{\rm diff}$                  | А                  | Drift or diffusion component of $I_{\rm DS}$ , $I_{\rm DS} = I_{\rm drift} + I_{\rm diff}$                                                        |

| $I_{\mathrm{i}}$                                  | А                  | Current flowing into node <i>i</i>                                                                                                                |

| $I_{ m ij}$                                       | А                  | Current flowing from node <i>i</i> to node <i>j</i>                                                                                               |

| L                                                 | m                  | Effective channel length                                                                                                                          |

| $L_{\rm mask}$                                    | m                  | Mask or drawn channel length                                                                                                                      |

| $N_{ m FA}$                                       | $V^{-1}m^{-4}$     | First coefficient of the flicker noise, see Section 7.1                                                                                           |

| $N_{ m FB}$                                       | $V^{-1}m^{-2}$     | Second coefficient of the flicker noise, see Section 7.1                                                                                          |

| $N_{\rm FC}$                                      | $V^{-1}$           | Third coefficient of the flicker noise, see Section 7.1                                                                                           |

| $N_{\mathrm{A}}$                                  | $m^{-3}$           | Impurity concentration in bulk                                                                                                                    |

| $N_{\rm OV}$                                      | $m^{-3}$           | Effective impurity concentration in gate-overlapped drain or source extension                                                                     |

| $N_{\mathrm{P}}$                                  | $m^{-3}$           | Impurity concentration in polysilicon gate                                                                                                        |

| $N_{\mathrm{T}}$                                  | J                  | Coefficient of the thermal noise, $N_{\rm T} = 4 \cdot k_{\rm B} \cdot T$                                                                         |

| $Q_{\mathrm{b}}$                                  | C/m <sup>2</sup>   | Bulk charge density formed by accumulation or depletion layer                                                                                     |

| $ar{Q}_{	extsf{b}}$                               | C/m <sup>2</sup>   | Average bulk charge density, $\bar{Q}_{\rm b} = Q_{\rm b}(\psi_{\rm s} = \bar{\psi})$                                                             |

| $Q_{ m g}$                                        | $C/m^2$            | Gate charge density                                                                                                                               |

| $ar{Q}_{	ext{g}}$                                 | $C/m^2$            | Average gate charge density, $\bar{Q}_{\rm g} = Q_{\rm g}(\psi_{\rm s} = \bar{\psi})$                                                             |

| $Q_{ m inv}$                                      | $C/m^2$            | Inversion-layer charge density                                                                                                                    |

| $Q_{\mathrm{inv}_0}, Q_{\mathrm{inv}_\mathrm{I}}$ | $C/m^2$            | Inversion-layer charge density at source or drain side                                                                                            |

| $ar{Q}_{	ext{inv}}$                               | $C/m^2$            | Average inversion-layer charge density, $\bar{Q}_{\rm inv} = Q_{\rm inv}(\psi_{\rm s} = \bar{\psi})$                                              |

| $Q^*_{\mathrm{inv}}$                              | C/m <sup>2</sup>   | Effective inversion-layer charge density, $Q_{\rm inv}^* = Q_{\rm inv} + \phi_{\rm T} \cdot C_{\rm inv}$                                          |

| $ar{Q}^*_{ m inv}$                                | C/m <sup>2</sup>   | Average effective inversion-layer charge density, $\bar{Q}_{inv}^* = Q_{inv}^*(\psi_s = \bar{\psi})$                                              |

| $Q_{ m j}$                                        | С                  | Total nodal charge of node <i>j</i>                                                                                                               |

| $Q_{ m ov}$                                       | C/m <sup>2</sup>   | Charge density in gate-overlapped source/drain extension                                                                                          |

| $Q_{\mathrm{ov}_0}, Q_{\mathrm{ov}_{\mathrm{L}}}$ | C/m <sup>2</sup>   | Charge density in gate-overlapped source or drain extension                                                                                       |

| R <sub>S</sub>                                    | Ω                  | Series resistance                                                                                                                                 |

| $R_{S_0}$                                         | Ω                  | Bias-independent part of series resistance, see Section 3.4                                                                                       |

| $S_{\mathrm{I_D}}, S_{\mathrm{I_G}}$              | A <sup>2</sup> /Hz | Noise spectral density of drain $(S_{I_D})$ and gate $(S_{I_G})$ current                                                                          |

| Т                                                 | Κ                  | Temperature in channel region in MOS transistor                                                                                                   |

| V                                                 | V                  | Electron quasi-Fermi potential                                                                                                                    |

| $V_{\mathrm{DS}_{\mathrm{sat}}}$                  | V                  | Drain-source saturation voltage, see Appendix H                                                                                                   |

| $V_{\mathrm{DS}_{\mathrm{sat}\infty}}$            | V                  | Drain-source saturation voltage for long-channel device, $V_{\text{DS}_{\text{sat}\infty}} = \psi_{\text{sat}} - \phi_{\text{B}} - V_{\text{SB}}$ |

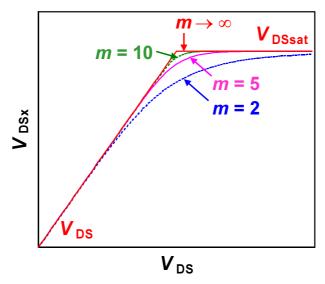

| $V_{\mathrm{DS}_{\mathrm{X}}}$                    | V                  | Ohmic/saturation smoothing function, see Appendix A.2                                                                                             |

| $V_{\rm FB}$                                      | V                  | Flat-band voltage                                                                                                                                 |

Physical Background of MOS Model 11, Level 1101

| Symbol                       | Unit        | Description                                                                                                                 |  |

|------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| $V_{\rm FBov}$               | V           | Flat-band voltage of gate-overlapped source/drain extension                                                                 |  |

| $V_{ m GB}^*$                | V           | Effective gate-bulk bias, $V_{\rm GB}^* = V_{\rm GB} - V_{\rm FB}$                                                          |  |

| $V_{\rm GX}$                 | V           | Gate-source $(X = S)$ or gate-drain $(X = D)$ voltage                                                                       |  |

| $V_{\mathrm{P}}$             | V           | Characteristic voltage of channel length modulation, see Section 3.6.1                                                      |  |

| $V_{\mathrm{T}}$             | V           | Threshold voltage                                                                                                           |  |

| $V_{ m ij}$                  | V           | Voltage between terminal $i$ and $j$                                                                                        |  |

| $V_{ m ov}$                  | V           | Oxide voltage in gate-overlapped source/drain extension, $V_{\rm ov} = -Q_{\rm ov}/C_{\rm ox}$                              |  |

| $V_{\rm ov_0}, V_{\rm ov_L}$ | V           | Oxide voltage in gate-overlapped source or drain extension                                                                  |  |

| $V_{\rm ox}$                 | V           | Oxide voltage in intrinsic channel region, $V_{\rm ox} = Q_{\rm g}/C_{\rm ox}$                                              |  |

| W                            | m           | Effective channel width                                                                                                     |  |

| W <sub>mask</sub>            | m           | Mask or drawn channel width                                                                                                 |  |

| $a_1$                        | _           | Factor of the weak-avalanche current, see Section 4.1                                                                       |  |

| $a_2$                        | V           | Exponent of the weak-avalanche current, see Section 4.1                                                                     |  |

| <i>a</i> <sub>3</sub>        | _           | Factor of the drain–source voltage above which weak–avalanche occurs, see Section 4.1                                       |  |

| f                            | Hz          | Frequency                                                                                                                   |  |

| g                            | A·m/V       | Channel conductance, $g = \mu \cdot W \cdot Q_{inv}$                                                                        |  |

| $g_{ m ds}$                  | A/V         | Output conductance, $g_{\rm ds} = \partial I_{\rm D} / \partial V_{\rm DS}$                                                 |  |

| $g_{ m m}$                   | A/V         | Transconductance, $g_{\rm m} = \partial I_{\rm D} / \partial V_{\rm GS}$                                                    |  |

| $g_{ m mb}$                  | A/V         | Substrate transconductance, $g_{\rm mb} = \partial I_{\rm D} / \partial V_{\rm BS}$                                         |  |

| ħ                            | $J \cdot s$ | Reduced Planck constant, $\hbar = 1.05458 \cdot 10^{-34} \text{J} \cdot \text{s}$                                           |  |

| kB                           | J/K         | Boltzmann constant, $k_{\rm B} = 1.3806226 \cdot 10^{-23}$ J/K                                                              |  |

| $k_0$                        | $V^{1/2}$   | Body-effect factor of bulk, $k_0 = \sqrt{2 \cdot q \cdot \epsilon_{\rm Si} \cdot N_{\rm A}} / C_{\rm ox}$                   |  |

| k <sub>ov</sub>              | $V^{1/2}$   | Body-effect factor of source/drain extension, $k_{ov} = \sqrt{2 \cdot q \cdot \epsilon_{Si} \cdot N_{OV}} / C_{ox}$         |  |

| $k_{\mathrm{P}}$             | $V^{1/2}$   | Body-effect factor of polysilicon gate, $k_{\rm P} = \sqrt{2 \cdot q \cdot \epsilon_{\rm Si} \cdot N_{\rm P}} / C_{\rm ox}$ |  |

| $m_0$                        | _           | Parameter for (short-channel) subthreshold slope, $m_0 = m_S - 1$                                                           |  |

| m <sub>S</sub>               | -           | Parameter for short-channel subthreshold slope, $m_{\rm S} = 1 + m_0$                                                       |  |

| п                            | $m^{-3}$    | Free electron concentration, $n \approx N_{\rm A} \cdot \exp((\psi - \phi_{\rm B} - V)/\phi_{\rm T})$                       |  |

| ni                           | $m^{-3}$    | Intrinsic carrier concentration, $n_i = 1.45 \cdot 10^{+16} \text{m}^{-3}$ at $T = 300 \text{K}$                            |  |

| р                            | $m^{-3}$    | Free hole concentration, $p \approx N_{\rm A} \cdot \exp(-\psi/\phi_{\rm T})$                                               |  |

| q                            | С           | Elementary unit charge, $q = 1.6021918 \cdot 10^{-19}$ C                                                                    |  |

| <i>t</i> <sub>ox</sub>       | m           | Gate oxide thickness, see Fig. 2.1                                                                                          |  |

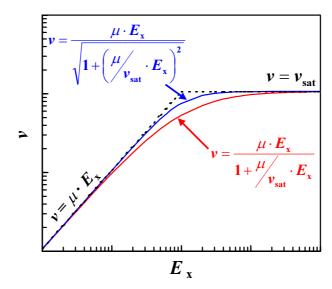

| υ                            | m/s         | Carrier velocity                                                                                                            |  |

| $v_{\rm sat}$                | m/s         | Saturation velocity                                                                                                         |  |

| x , y , z                    | m           | Lateral, transversal and orthogonal coordinates, see Fig. 2.1                                                               |  |

| Symbol                                                 | Unit             | Description                                                                                  |  |

|--------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------|--|

| $\Delta_{ m acc}$                                      | V                | Approximate function for impact of holes in the inversion region, see eq. (2.14)             |  |

| $\Delta Q_{ m inv}$                                    | C/m <sup>2</sup> | Inversion-layer charge density difference, $\Delta Q_{\rm inv} = Q_{\rm inv_L} - Q_{s_0}$    |  |

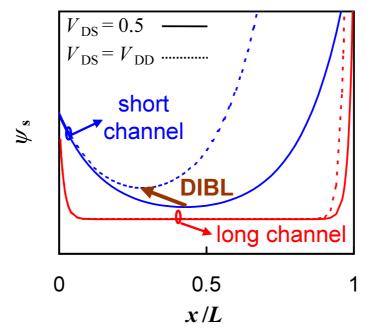

| $\Delta V_{ m G_{dibl}}$                               | V                | Increase in effective gate bias due to DIBL, see Section 3.2                                 |  |

| $\Delta V_{ m G_{sf}}$                                 | V                | Increase in effective gate bias due to static feedback, see Section 3.6.2                    |  |

| $\Delta\psi$                                           | V                | Surface potential difference, $\Delta \psi = \psi_{s_L} - \psi_{s_0}$                        |  |

| α                                                      | _                | Factor of channel length modulation, see Section 3.6.1                                       |  |

| β                                                      | $A/V^2$          | Gain factor, $\beta = \mu_0 \cdot C_{\text{ox}} \cdot W/L$                                   |  |

| $\epsilon_{\mathrm{Si}}$                               | F/m              | Dielectric permittivity of silicon, $\epsilon_{\rm Si} = 1.0447720 \cdot 10^{-10}$ F/m       |  |

| $\epsilon_{\rm ox}$                                    | F/m              | Dielectric permittivity of SiO <sub>2</sub> , $\epsilon_{ox} = 3.4531438 \cdot 10^{-11}$ F/m |  |

| $\eta_{ m mob}$                                        | _                | Effective field parameter for dependence on $Q_{inv}$ and $Q_{dep}$ , see Section 3.3.1      |  |

| $\theta_{\rm R}$                                       | 1/V              | Coefficient of series resistance, $\theta_{\rm R} = 2 \cdot \beta \cdot R_{\rm S_0}$         |  |

| $\theta_{\rm R1}$                                      | V                | Numerator of gate bias dependent part of $R_S$ , see Section 3.4                             |  |

| $\theta_{\rm R2}$                                      | V                | Denominator of gate bias dependent part of $R_S$ , see Section 3.4                           |  |

| $	heta_{\mathrm{Th}}$                                  | $V^{-3}$         | Coefficient of self-heating, see Section 3.6.3                                               |  |

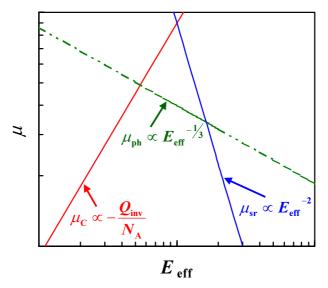

| $	heta_{ m ph}$                                        | $V^{-1}$         | Coefficient of mobility reduction due to phonon scattering, see Section 3.3.1                |  |

| $\theta_{\rm sr}$                                      | $V^{-1}$         | Coefficient of mobility reduction due to surface roughness scattering, see Section 3.3.1     |  |

| $\theta_{\rm sat}$                                     | 1/V              | Velocity saturation parameter, $\theta_{sat} = \mu_0 / (v_{sat} \cdot L)$                    |  |

| $\mu$                                                  | $m^2/V \cdot s$  | Carrier mobility                                                                             |  |

| $\mu_0$                                                | $m^2/V \cdot s$  | Low-field bulk mobility                                                                      |  |

| ν                                                      | _                | Exponent of field dependence of mobility model, see Section 3.3.1                            |  |

| $\phi_{ m B}$                                          | V                | Surface potential at onset of strong inversion, $\phi_{\rm B} = 2 \cdot \phi_{\rm F}$        |  |

| $\phi_{ m F}$                                          | V                | Intrinsic Fermi potential, $\phi_{\rm F} = \phi_{\rm T} \cdot \ln(N_{\rm A}/n_{\rm i})$      |  |

| $\phi_{\mathrm{T}}$                                    | V                | Thermal voltage, $\phi_{\rm T} = k_{\rm B} \cdot T/q$                                        |  |

| $\psi$                                                 | V                | Electrostatic potential with respect to neutral bulk                                         |  |

| $ar{\psi}$                                             | V                | Average surface potential, $\bar{\psi} = (\psi_{s_L} + \psi_{s_0})/2$                        |  |

| $\psi_{ m p}$                                          | V                | Surface potential in polysilicon gate, see Fig. 2.3                                          |  |

| $\psi_{ m s}$                                          | V                | Surface potential, see Fig. 2.3                                                              |  |

| $\psi_{\mathrm{s}_0}$ , $\psi_{\mathrm{s}_\mathrm{L}}$ | V                | Surface potential at source or drain side                                                    |  |

| $\psi_{\mathrm{s}_{\mathrm{ov}}}$                      | V                | Surface potential in gate overlap region, see Fig. 2.6                                       |  |

| $\psi_{ m sat}$                                        | V                | Surface potential in weak inversion, see eq. (3.13)                                          |  |

| $\sigma_{ m dibl}$                                     | $V^{-1/2}$       | Drain-induced barrier-lowering parameter, see Section 3.2                                    |  |

| $\sigma_{ m sf}$                                       | $V^{-1/2}$       | Static-feedback parameter, see Section 3.6.2                                                 |  |

| ω                                                      | rad/s            | Angular frequency, $\omega = 2 \cdot \pi \cdot f$                                            |  |

# Contents

| 1 | Intro | oduction                                               | 1  |

|---|-------|--------------------------------------------------------|----|

|   | 1.1   | $V_{\rm T}$ -Based versus $\psi_{\rm s}$ -Based Models | 1  |

|   | 1.2   | Demands for Analogue and RF Design                     | 2  |

|   | 1.3   | Important Physical Effects:                            | 4  |

|   | 1.4   | Outline of Report                                      | 5  |

| 2 | MO    | SFET Basics                                            | 7  |

|   | 2.1   | Intrinsic Region                                       | 9  |

|   |       | 2.1.1 Surface Potential                                | 9  |

|   |       | 2.1.2 Charge Densities                                 | 12 |

|   | 2.2   | Extrinsic Region                                       | 16 |

|   |       | 2.2.1 Surface Potential                                | 16 |

|   |       | 2.2.2 Charge Densities                                 | 17 |

| 3 | Cha   | nnel Current Modelling                                 | 19 |

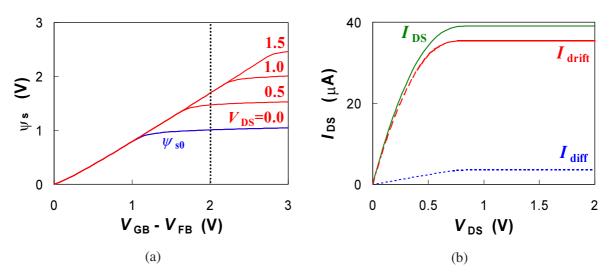

|   | 3.1   | Ideal Channel Current                                  | 19 |

|   | 3.2   | Subthreshold Current                                   | 22 |

|   | 3.3   | Mobility Effects                                       | 25 |

|   |       | 3.3.1 Mobility Reduction                               | 26 |

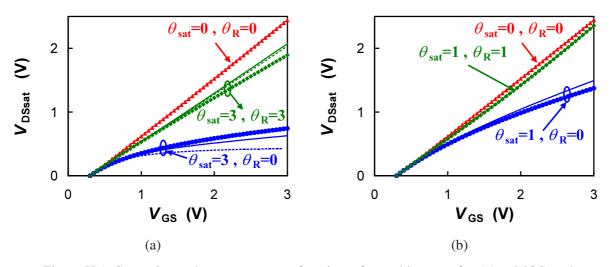

|   |       | 3.3.2 Velocity Saturation                              | 29 |

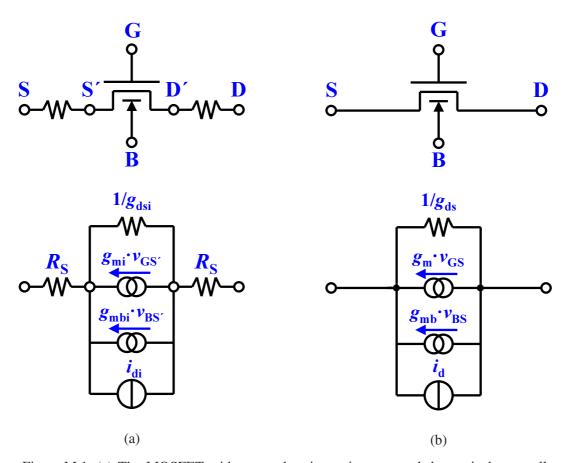

|   | 3.4   | Series Resistance                                      | 32 |

|   | 3.5   | Saturation Voltage                                     | 34 |

|   | 3.6   | Effects on Conductance                                 | 35 |

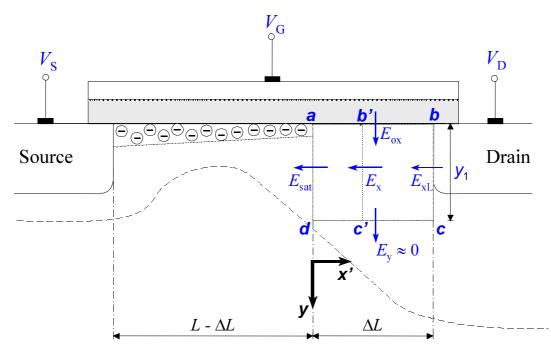

|   |       | 3.6.1 Channel Length Modulation                        | 35 |

|   |       | 3.6.2 Static Feedback                                  | 36 |

|   |       | 3.6.3 Self-Heating                                     | 37 |

|   | 3.7   | Impact of Pocket Implants                              | 38 |

| 4 | Bulk  | x Current Modelling                                    | 41 |

|   | 4.1   | Impact Ionisation                                      | 41 |

|   | 4.2   | Gate-Induced Drain Leakage                             | 43 |

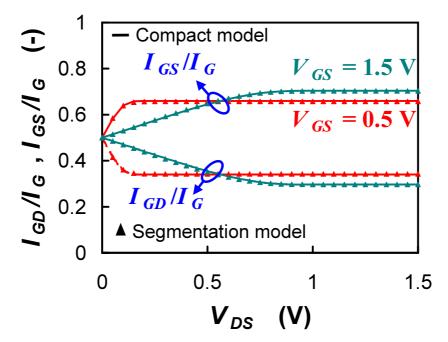

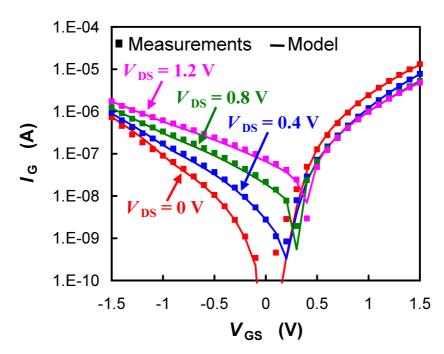

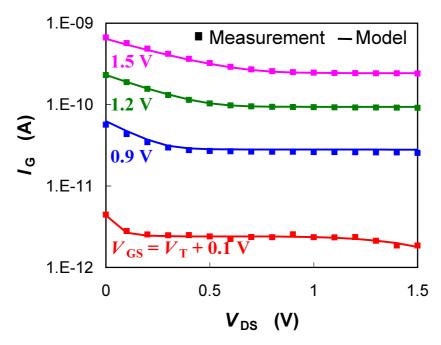

| 5 | Gate  | e Current Modelling                                    | 47 |

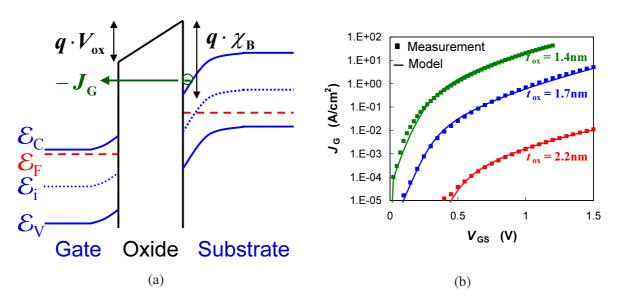

|   | 5.1   | Gate-to-Channel Current                                | 48 |

|   | 5.2   | Gate-to-Bulk Current                                   | 53 |

|   | 5.3   | Gate Overlap Current                                   | 54 |

| H<br>I<br>J | Channel Length Modulation<br>Derivation of Gate-Induced Drain Leakage Equation | 105<br>109 |

|-------------|--------------------------------------------------------------------------------|------------|

|             | Channel Length Modulation                                                      | 105        |

| Η           |                                                                                |            |

|             | Calculation of Saturation Voltage                                              | 101        |

|             | G.2 Impact on Charge Model                                                     | . 98       |

|             | G.1 Impact on Channel Current                                                  | . 97       |

| G           | Implementation of Series Resistance                                            | 97         |

|             | F.2 Impact on Charge Model                                                     | . 94       |

|             | F.1 Impact on Channel Current                                                  | . 93       |

| F           | Impact of Velocity Saturation                                                  | 93         |

|             | E.2 Impact on Charge Model                                                     | . 91       |

|             | E.1 Impact on Channel Current                                                  | . 90       |

| E           | Charge Sheet Approximation and Its Impact                                      | 89         |

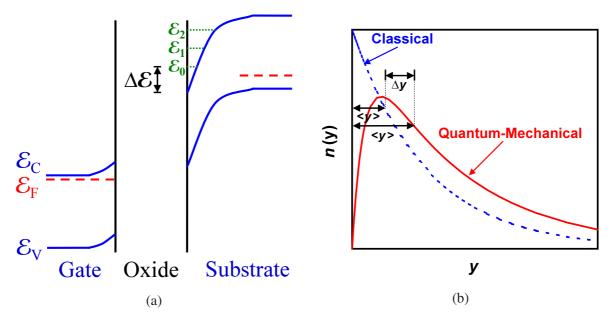

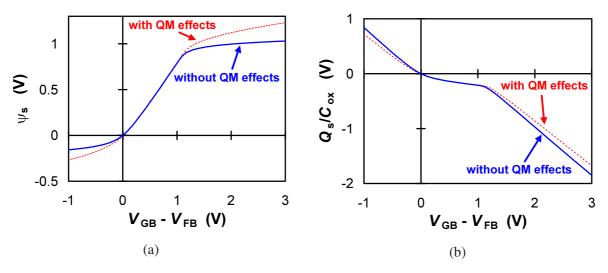

| D           | Quantum-Mechanical Effects                                                     | 85         |

| С           | Explicit Approximation of Surface Potential                                    | 79         |

|             | B.2 Gate Overlap Region                                                        | . 76       |

|             | B.1 Poly-Depletion Effect                                                      | . 75       |

| B           | Calculation of Surface Potential                                               | 75         |

|             | A.2 Ohmic/Saturation Smoothing Function                                        | . 73       |

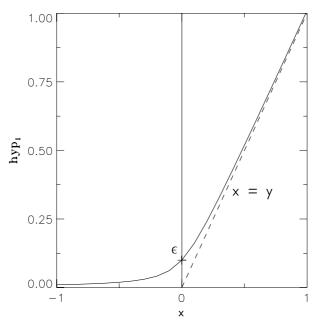

|             | A.1 Hyp Functions                                                              | . 73       |

| A           | Smoothing Functions                                                            | 73         |

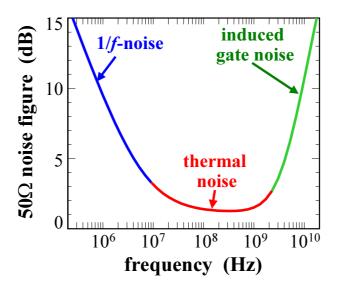

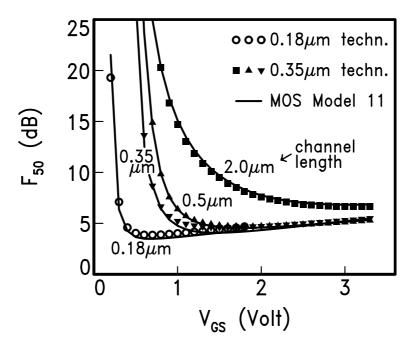

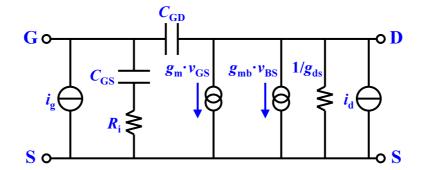

|             | 7.3 Induced Gate Noise Modelling                                               | . 69       |

|             | 7.2 Thermal Noise                                                              | . 66       |

| -           | 7.1 $1/f$ -Noise                                                               |            |

| 7           | Noise Modelling                                                                | 63         |

|             | 6.2 Extrinsic Charges                                                          |            |

|             | 6.1 Intrinsic Charges                                                          | . 57       |

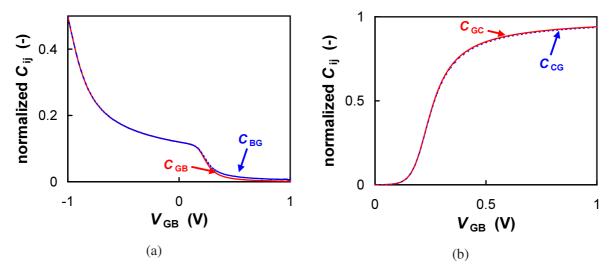

| 6           | Charge modelling                                                               | 57         |

|             | 5.4 Total Gate Current                                                         |            |

| Unclassified Report |                                           | ed Report Physical Background of MOS Model 11                                                 | Physical Background of MOS Model 11, Level 1101 |     | 00239 |

|---------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|-----|-------|

|                     |                                           | General Formula for Gate Current Density<br>General Formula for the Source/Drain Partitioning |                                                 |     |       |

| L                   | Auxi                                      | iliary Derivations for Integration along the Char                                             | nnel                                            |     | 115   |

| Μ                   | M Derivation of Thermal Noise Expressions |                                                                                               |                                                 | 117 |       |

|                     | <b>M</b> .1                               | Derivation of General Thermal Noise                                                           |                                                 |     | 117   |

|                     | M.2                                       | Impact of Series Resistance on Thermal Noise                                                  |                                                 |     | 117   |

|                     |                                           |                                                                                               |                                                 |     |       |

### References

### **1** Introduction

Since its introduction in the 1960s, MOS transistor technology has been subject to a ceaseless decrease in transistor dimensions and resulting progress in performance. The decrease in transistor dimensions has allowed for an exponential increase with time in the number of components per chip and in operation speed. Furthermore, the downscaling of MOS technology has led to the on-going integration of many different functions, both digital and analogue, on a single chip. Nowadays, the realization of very complex and high-speed circuits in CMOS technology is the order of the day. The growth in circuit complexity has made indispensable the use of computer-aided simulation tools which allow the circuit designer to predict and optimize circuit behaviour before the circuit is realized

which allow the circuit designer to predict and optimize circuit behaviour before the circuit is realized in silicon, so-called *circuit simulators*. Circuit simulators contain mathematical models for the quantitative description of the terminal behaviour of the circuit elements as a function of bias conditions, temperature, and device geometry. The above models are often referred to as *compact models*, and they are a critical link in the translation of CMOS process properties into IC performance. Evidently, the benefit of a circuit simulator depends heavily on the accuracy of the compact models used, on the other hand the models should be as simple as possible in order to limit circuit simulation time. Continuity, accuracy, scalability, and simulation performance are basic requirements for such a compact MOSFET model.

Generally three different types of compact models can be distinguished: physics-based models, empirical models and table look-up models. In the first type, the model equations are analytical expressions which have been derived directly from device physics. In the second type, the relations are of a curve fitting nature, and in the last type, the characteristics are reconstructed via tables of measured data. The latter two types offer little physical insight in contrast to the physics-based model, which makes use of physical significant parameters that allow for statistical modelling and that obey well-defined geometrical and temperature scaling rules. As a consequence, most compact MOSFET models in existing circuit simulators are physics-based models. These models include MOS Model 9 (MM9) [1], the BSIM4 model [2] and the EKV model [3].

Within Philips, MM9 has been the compact model of choice since the early 1990s. However, with the continuous downscaling of CMOS technologies, the demands on compact MOS models have become more and more stringent. Modern CMOS technologies are not only suitable for digital and analogue but also for RF applications. A compact model should thus be accurate for RF as well as for digital and analogue design. In addition, new physical effects come into prominence with technology downscaling. The model should accurately describe all the important physical effects of modern and future technologies. Unfortunately all existing models (including MM9) fail to satisfy the above demands, and as a result, a new compact MOS model has been developed over the past years, called MOS Model 11 (MM11) [4]-[17], the successor to MM9. The new MM11 fulfills all of the demands for advanced compact MOS models as discussed in the following Sections.

### **1.1** $V_{\rm T}$ -Based versus $\psi_{\rm s}$ -Based Models

In MOS modelling, the transition region between subthreshold and superthreshold behaviour, often referred to as the *moderate inversion region*, has traditionally received little attention. As the supply voltage is scaled down to lower values with CMOS downscaling, however, this region becomes an increasingly larger fraction of the overall logic swing in digital circuits. Furthermore, in analogue and RF design, MOSFETs are typically biased in this operation region around threshold. An accurate and physical description of the moderate inversion region is thus essential.

Conventional models such as, e.g., BSIM4 and MM9 are based on the formulation of threshold voltage  $V_T$  [1, 2, 18]. These so-called  $V_T$ -based models have been developed using regional approximations which are joined together by suitable smoothing functions over the moderate inversion region,

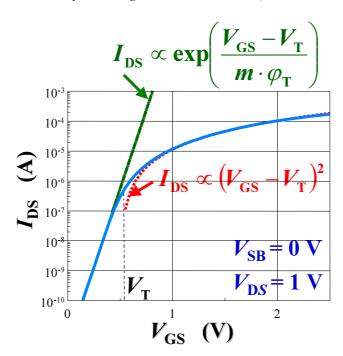

Figure 1.1:  $V_{\rm T}$ -based models such as BSIM4 and MM9 make use of regional approximations for the drain-source channel current  $I_{\rm DS}$  in the subthreshold ( $V_{\rm GS} < V_{\rm T}$ ) and superthreshold region ( $V_{\rm GS} > V_{\rm T}$ ) (dashed lines). These approximations break down around threshold (i.e.,  $V_{\rm GS} = V_{\rm T}$ ). In order to circumvent this problem, the approximations are joined together by suitable smoothing functions over the transition region. These mathematical smoothing functions have no physical basis.

see Fig. 1.1. With the increasing importance of the moderate inversion region, this type of model relies more on the mathematical smoothing functions and less on the physics-based approximations in the subthreshold and the superthreshold region. This has led to the current trend of increasing model complexity and an increasing number of parameters. Some newer models are not based on  $V_{\rm T}$  formulations but on inversion charge  $Q_{\rm inv}$  formulations [3, 19, 20], so-called  $Q_{\rm inv}$ -based models. These models, nevertheless, still use a more or less empirical description of the moderate inversion region.

Over the years, in an attempt to increase the physical content, especially in the moderate inversion region, the focus has gradually shifted from  $V_{\rm T}$ -based (and  $Q_{\rm inv}$ -based) models to charge-sheet models based on the formulation of surface potential  $\psi_s$  [21]-[31]. These so-called  $\psi_s$ -based models are inherently single-piece and give a physics-based and accurate description in all operation regions. Unfortunately, these models require an iterative solution of surface potential, which is generally considered to be computationally expensive. This is undesirable for circuit simulation, and as such it is a drawback of  $\psi_s$ -based models. Nowadays, nevertheless, it is felt that the extra computation time is worth the return in accuracy. New models in the public domain, still under development, such as the HiSIM model [22]-[25] and the SP model [27]-[31] are  $\psi_s$ -based models.

MM11 is based on  $\psi_s$  formulations. In addition, MM11 makes use of a suitable explicit approximation of  $\psi_s$  which reduces computation time and still preserves accuracy [9].

### 1.2 Demands for Analogue and RF Design

Analogue and RF design typically require an accurate description of not only currents and capacitances but also of the small-signal behaviour, the noise behaviour and the distortion behaviour. Espe-

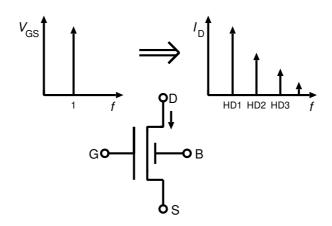

Figure 1.2: In a typical amplifier structure, a sinusoidal input signal  $V_{GS}$  results in a distorted output signal  $I_D$  containing the ground harmonic (HD1) as well as undesired higher-order harmonics (HD2, HD3,...) due to the non-linear dependence of  $I_D$  on  $V_{GS}$ .

cially the latter has received little attention, and is thus a special point of interest. Another point of interest for analogue and RF design is the drain-source symmetry of the MOS model.

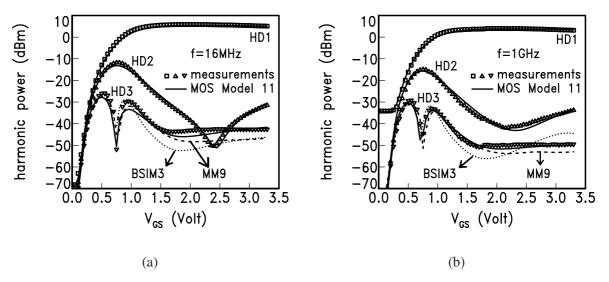

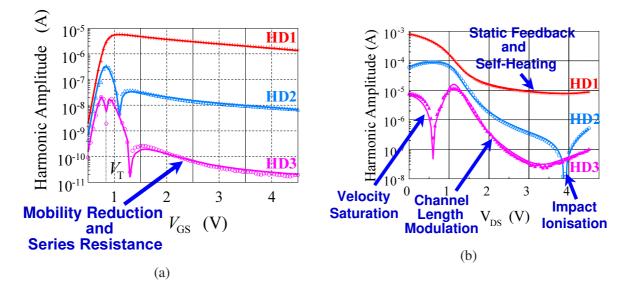

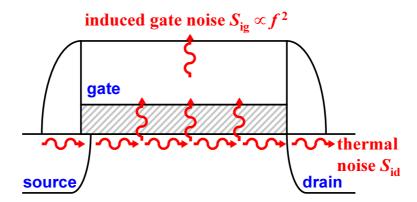

**Distortion Modelling:** The distortion behaviour of a MOSFET in an amplifier structure is illustrated in Fig. 1.2. In circuits using balanced topologies, even-order harmonics can be reduced by about 40dB. As a result, the 3<sup>rd</sup>-order harmonic forms a lower limit for the total distortion [32]. A compact MOS model should thus accurately describe the drain current and its higher-order derivatives (up to at least 3<sup>rd</sup>-order), MM11 has especially been developed for this purpose. As a result, compared to other compact models, MM11 contains improved expressions for mobility reduction [5], velocity saturation and various conductance effects [6, 7]. This improved model gives an accurate description of distortion at both low and high frequencies [10], see Fig. 1.3.

Figure 1.3: Measured and modelled harmonic distortion as a function of dc gate bias  $V_{\text{GS}}$  of a  $16 \times 10/0.35 \,\mu\text{m}$  *n*-type MOSFET in  $0.35 \,\mu\text{m}$  technology at (a) low frequency (f = 16MHz), and (b) high frequency (f = 1GHz). ( $V_{\text{DS}} = 3.3$ V,  $V_{\text{SB}} = 0$ V and  $P_{\text{in}} = -5$ dBm)

**Drain-Source Symmetry:** For applications where the MOSFET is used as a gate-controlled resistor [32], the model should be symmetrical with respect to source and drain at zero drain-source bias

<sup>©</sup>Koninklijke Philips Electronics N.V. 2003

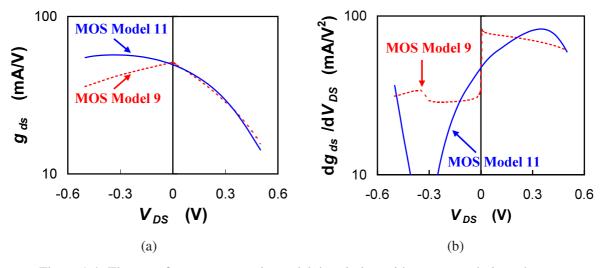

Figure 1.4: The use of a non-symmetric model description with respect to drain and source at  $V_{\rm DS} = 0$ , such as used in conventional models such as MM9 and BSIM4, will result in (a) a kink in the conductance  $g_{\rm ds}$  (i.e.,  $\partial I_{\rm DS}/\partial V_{\rm DS}$ ) and (b) discontinuities in the higher-order derivatives at  $V_{\rm DS} = 0$ . In MM11, care has been taken to preserve symmetry.

(i.e.,  $V_{\rm DS} = 0$ ) in order not to give erroneous results. In most MOS models, the expression for channel current  $I_{\rm DS}$  has been derived for  $V_{\rm DS} \ge 0$ , and source and drain are simply interchanged internally when  $V_{\rm DS} < 0$ . In a typical MOSFET structure, however, the choice of source and drain is arbitrary, in other words, the device is symmetric with respect to source and drain when  $V_{\rm DS} = 0$ . This should be reflected in the channel current expression, i.e., the same expression multiplied by -1 should be obtained if drain and source are interchanged.

Typical  $V_{\rm T}$ -based models are intrinsically asymmetrical since the threshold voltage is defined at the source side only. This asymmetry leads to discontinuities in the higher-order derivatives of channel current at  $V_{\rm DS} = 0$ , see Fig. 1.4, which is undesirable in applications where the MOSFET is used as a gate-bias controlled resistor. Care has to be taken in the derivation of the model expressions to preserve symmetry [6, 26], this has been done in MM11 [6, 7], see Fig. 1.4.

With respect to drain-source symmetry, it should be pointed out here that models are often mistakingly classified as being source-referenced or bulk-referenced [33], where the former is supposed to be aymmetrical and the latter symmetrical. Source-referenced models make use of  $V_{\rm GS}$ ,  $V_{\rm DS}$  and  $V_{\rm SB}$  as independent variables, whereas bulk-referenced models make use of  $V_{\rm GB}$ ,  $V_{\rm DB}$  and  $V_{\rm SB}$ . It will be clear that any bulk-referenced model can be converted to a source-referenced model by replacing  $V_{\rm GB}$  and  $V_{\rm DB}$  by  $V_{\rm GS} + V_{\rm SB}$  and  $V_{\rm DS} + V_{\rm SB}$ , respectively. In other words, all advantages of a body-referenced model (such as, e.g., drain-source symmetry) can be carried over to a corresponding source-referenced model or vice-versa. As a consequence, it is misleading to talk about source-referenced and bulk-referenced models, and it makes more sense to talk about symmetrical and asymmetrical models.

### **1.3 Important Physical Effects:**

The electrical behaviour of realistic MOSFETs deviates considerably from the ideal MOSFET behaviour owing to the influence of various physical effects. These effects have to be accurately taken into account in a compact MOS model. Traditionally, most models incorporate physical effects such as mobility reduction, bias-dependent series resistances, velocity saturation, drain-induced barrier lowering, static feedback, channel length modulation, self-heating and impact ionization. As modern

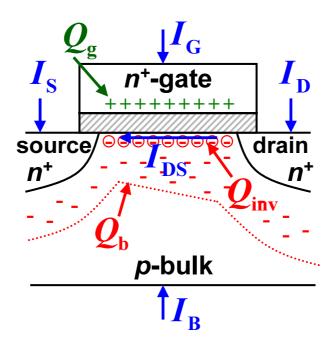

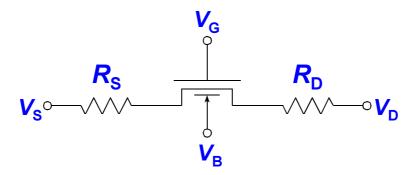

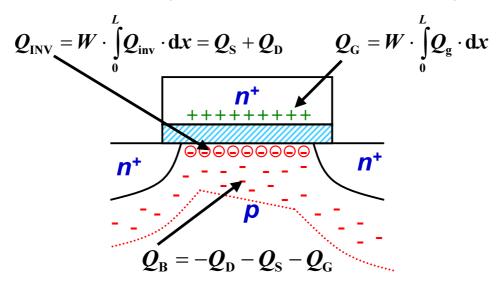

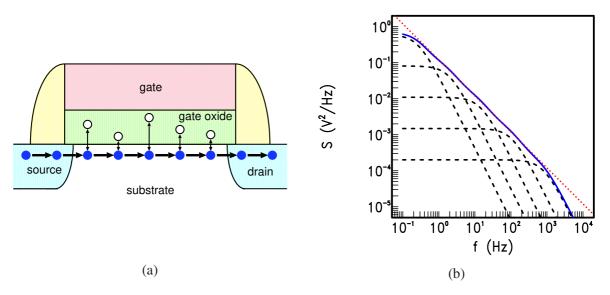

Figure 1.5: Basic structure of an *n*-type MOSFET, where all the most important electrical quantities are indicated: the nodal currents  $(I_D, I_S, I_G \text{ and } I_B)$ , the channel current  $(I_{DS})$  and various charge densities  $(Q_{inv}, Q_b \text{ and } Q_g)$ .

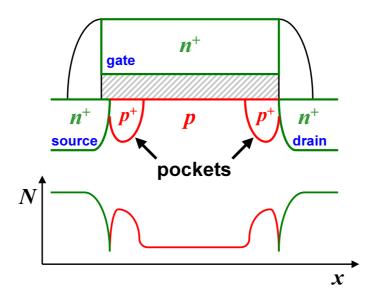

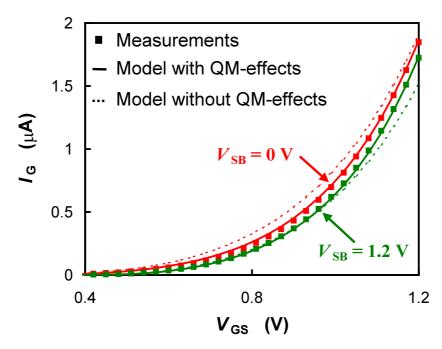

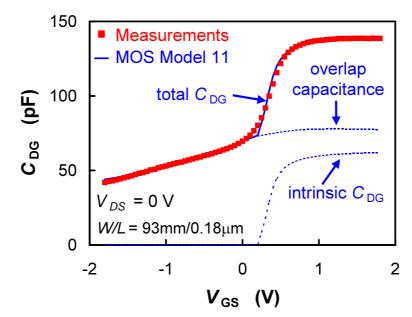

CMOS process technology scales down to sub-100nm dimensions, however, certain physical effects, which did not affect circuit design before, become important. With the downscaling of gate oxide thickness, the gate poly-depletion effect becomes increasingly important. In addition, the gate tunnelling current is no longer negligible, and quantum-mechanical quantisation effects become important. Furthermore, the use of pocket implants in order to reduce short-channel effects does affect the electrical behaviour of MOSFETs. For short-channel devices, the input capacitance is dominated by the overlap capacitances, which are bias-dependent. All of the above effects should be taken into account in an advanced compact model, they have been implemented in MM11 [12, 13, 14].

### **1.4 Outline of Report**

In a MOS transistor, we can distinguish three regions: i) the intrinsic channel region, ii) the gate/source and gate/drain overlap regions, and iii) the drain/bulk and source/bulk junction regions. It should be pointed out that MM11 only provides a model for the intrinsic channel region and the (gate/source and gate/drain) overlap regions. Junction charges, junction leakage currents and interconnect capacitances are not included. They are covered by separate models, which are not treated in this report. This report aims at giving a comprehensive physical derivation of the model equations used in MOS Model 11, Level 1101 [17]. These equations make use of electrical or miniset parameters, which are valid for a device with a specific geometry and a specific temperature. Since most of these parameters scale with geometry and with temperature, the process as a whole is characterised by an enlarged set of scaling parameters, the maxiset. These scaling parameters can be linked to the electrical parameters by physical relations. In practice, however, it is found that the use of semi-empirical scaling rules result in a more accurate and robust description. As a result, in this report, we will only focus on the derivation of the model equations based on miniset parameters. The geometrical and temperature scaling is left out of consideration here.

The MM11 equations give a description of all transistor-action related quantities: nodal currents,

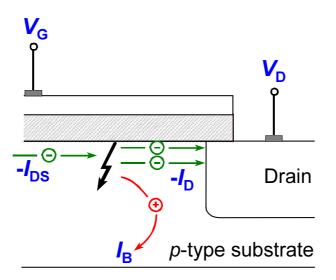

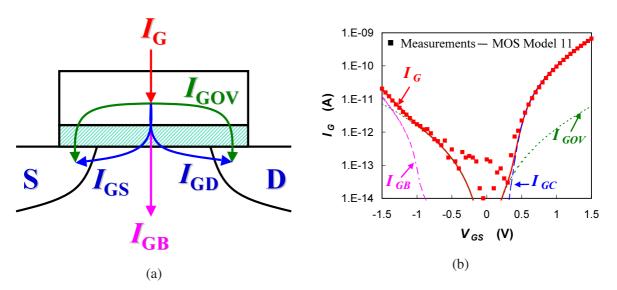

nodal charges and noise-power spectral densities. Before relations can be derived for these quantities, we need to derive expressions for surface potential and important electrical quantities such as charge densities, see Fig. 1.5. This is done in Chapter 2. Next, we focus our attention on the steady-state (or dc) behaviour of MOSFETs. For ideal MOSFET operation, both bulk current and gate current are considered zero, and as a result, the drain-source channel current determines the MOSFET behaviour, see Fig. 1.5. The channel current and all the phenomena that affect it, are discussed in Chapter 3. For realistic devices, however, the bulk and gate current are not zero, and the modelling of these currents is treated in Chapter 4 and 5, respectively. In Chapter 6, we turn our attention towards the dynamic behaviour of MOSFETs, which is described in terms of quasi-static nodal charges. Finally, we derive the expressions for the noise-power spectral densities in Chapter 7.

The treatment of MOS device physics in this report is rather concise in some parts, the interested reader is therefore referred to [34]-[36] for a more in-depth discussion. Furthermore, it will be clear that outlining the physical background of MM11 asks for numerous derivations. In order to keep the report readable, the more elaborate derivations are given in separate Appendices.

### **2 MOSFET Basics**

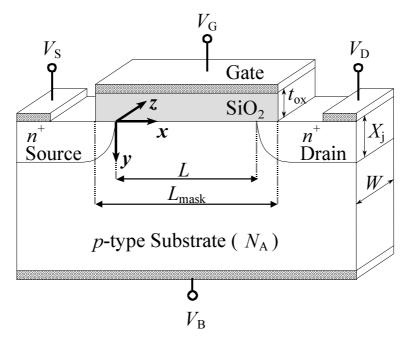

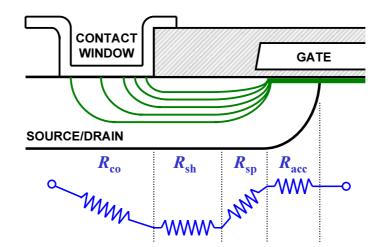

As the name Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) suggests, the MOS transistor consists of a semiconductor substrate on which a thin layer of insulating oxide (SiO<sub>2</sub>) of thickness  $t_{ox}$  is grown. A conducting layer (metal or heavily doped silicided polysilicon) called the gate electrode is deposited on top of the oxide. The basic structure of an *n*-type MOSFET<sup>1</sup> is shown in Fig. 2.1. The *p*-type doped silicon region, commonly referred to as the bulk or substrate, is contacted via the bulk contact. Two heavily *n*-type doped regions of depth  $X_j$ , called the source and the drain, are formed in the substrate on either side of the gate. The gate overlaps slightly with the source and drain regions. The region between the source and drain junctions is called the channel region, which has a length *L* (in the *x*-direction) and a width *W* (in the *z*-direction). Due to the manufacturing tolerances the mask length/width differs slightly from the final gate polysilicon length/width, furthermore the lateral under diffusion of the source and drain junctions also has its effect on the actual channel length/width. As a result, both *L* and *W* may differ from the actual mask dimensions,  $L_{mask}$  and  $W_{mask}$ , and the gate overlaps both the source and drain extensions, the so-called *overlap regions*.

Figure 2.1: The basic structure of an *n*-type MOS transistor.

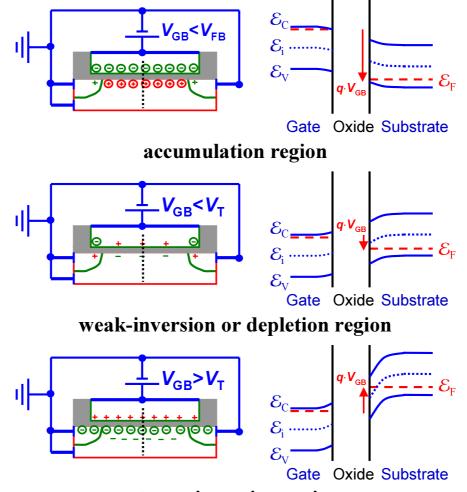

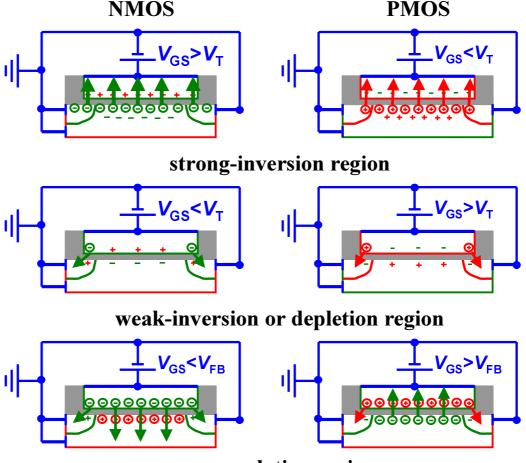

When a voltage  $V_{GB}$  is applied between the gate and the bulk, the band structure near the Si-SiO<sub>2</sub> interface is changed. For the moment, we assume source and drain are grounded ( $V_{SB} = V_{DB} = 0$ ), in this case three different situations can be distinguished (in the channel region): *accumulation*, *depletion* or *weak inversion* and *strong inversion*, as is shown in Fig. 2.2. Note that the gate overlap regions behave differently than the channel region.

For negative or very low gate voltage values, holes are attracted to the surface and a thin layer with a positive charge, a so-called *accumulation layer*, is formed. With increasing gate voltage, the band bending becomes less, until at a distinct gate voltage value no band bending occurs. This is called the flat-band voltage  $V_{\text{FB}}$ .

Beyond this point, the band bending is opposite to the accumulation condition, a negative charge is being built up. In effect, the positive voltage at the gate will repel the holes from the silicon surface

<sup>&</sup>lt;sup>1</sup>With the appropriate change of signs for charge and potential, the following also holds for p-type devices which are fabricated with an n-type doped substrate or a p-type doped substrate with an implanted n-well.

## strong-inversion region

Figure 2.2: The charge distribution and the corresponding energy-band diagram along the indicated dashed line (in *y*-direction) in an *n*-MOSFET for the three operation conditions: *accumulation, depletion* or *weak inversion* and *strong inversion*.

and thus expose the negatively charged (immobile) acceptor ions. This charge is called the depletion charge. Since holes are depleted at the surface, it is referred to as the depletion condition.

When  $V_{GB}$  is increased still more, the downward band bending becomes stronger. In fact, the band bending may cause the midgap energy  $\mathcal{E}_i$  to cross over the constant Fermi level  $\mathcal{E}_F$ , see Fig. 2.2. In this case, the surface behaves like an *n*-type material as opposed to the original *p*-type material, hence the name inversion region. A conducting layer with a negative (mobile) charge  $Q_{inv}$ , a so-called *inversion layer*, is formed. This layer shields the underlying silicon from the gate potential, and as a result the band bending does not extend deeper into the silicon after the (strong) inversion layer has been formed.

The inversion charge can be contacted via the source and drain region, and a current, the so-called *channel current*, will flow through the inverted area when a potential difference  $V_{DS}$  is applied between drain and source. Since the inversion charge depends heavily on the gate potential, the gate can be used to control the current through the channel.

In this chapter the so-called surface potential, on which MM11 is based, will be introduced and treated in depth, and expressions based on surface potential formulations will be derived for the charge densities and other important quantities such as electric fields. Since MM11 not only takes into

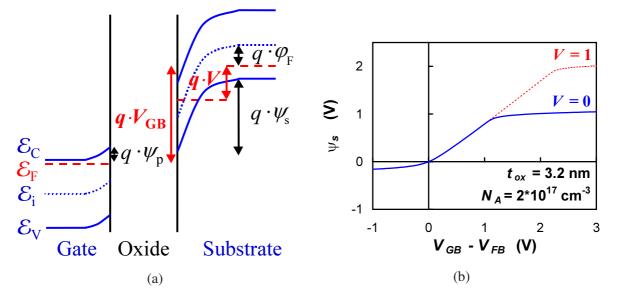

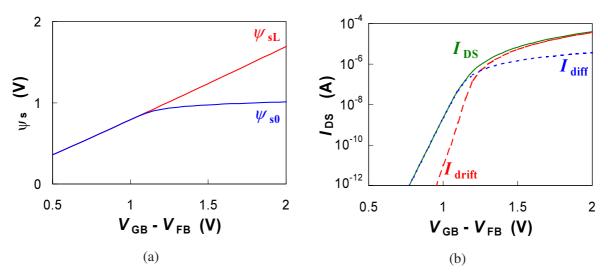

Figure 2.3: (a) The energy-band diagram (in transversal direction) of an *n*-MOSFET for  $V_{\text{GB}} > V_{\text{FB}}$ , where  $\psi_{\text{s}}$  is the surface potential,  $\psi_{\text{p}}$  is the potential drop in the gate due to the poly-depletion effect, *V* is the quasi-Fermi potential and  $\phi_{\text{F}}$  is the intrinsic Fermi-potential ( $\phi_{\text{B}} = 2 \cdot \phi_{\text{F}}$ ). (b) The surface potential as a function of gate bias for different values of quasi-Fermi potential *V* (as calculated from (2.7) with  $m_{\text{S}} = 1$ ).

account the intrinsic MOS region (where the channel is formed) but also the extrinsic MOS regions (i.e., the gate-source and the gate-drain overlap regions), this Chapter is split up in two Sections. First the surface potential and the charge densities in the intrinsic region are treated in Section 2.1, and next the same is done for the extrinsic regions in Section 2.2.

### 2.1 Intrinsic Region

In this Section we will discuss the formulation of surface potential in a typical MOS structure (Section 2.1.1), followed by a description of the various important charge densities and electric fields (Section 2.1.2).

#### 2.1.1 Surface Potential

In order to be able to calculate electrical quantities such as currents, charges and noise, we first start off with the definition of surface potential. The surface potential  $\psi_s$  is defined as the electrostatic potential at the gate oxide/substrate interface with respect to the neutral bulk (due to band bending, see Fig. 2.3 (a)). For the moment, it is assumed that the gate is ideal and no depletion occurs in the polysilicon (i.e.,  $\psi_p = 0$  in Fig. 2.3 (a)). In this case, the surface potential  $\psi_s$  can be calculated using the following derivation.

In the *p*-type substrate, a space charge  $\rho(x, y)$  is present [35]:

$$\rho(x, y) = q \cdot [p(x, y) - n(x, y) - N_{\rm A}]$$

(2.1)

<sup>©</sup>Koninklijke Philips Electronics N.V. 2003

Unclassified Report

where  $N_A$  is the net acceptor doping concentration. The electron and hole density, *n* and *p*, are given by Maxwell-Boltzmann statistics:

$$n(x, y) \approx N_{\rm A} \cdot \exp\left(\frac{\psi(x, y) - V(x) - 2 \cdot \phi_{\rm F}}{\phi_{\rm T}}\right)$$

$$p(x, y) \approx N_{\rm A} \cdot \exp\left(-\frac{\psi(x, y)}{\phi_{\rm T}}\right)$$

(2.2)

where  $\psi$  is the electrostatic potential with respect to the neutral bulk and  $\phi_T (= k_B \cdot T/q)$  is the thermal voltage. The intrinsic Fermi potential  $\phi_F$  (as shown in Fig. 2.3 (a)) is defined by  $\phi_T \cdot \ln(N_A/n_i)$ , and V(x) denotes the electron quasi-Fermi potential, which ranges from  $V_{SB}$  at the source side (x = 0) to  $V_{DB}$  at the drain side (x = L). The Poisson equation for the electrostatic potential  $\psi$  is written as:

$$\nabla^2 \psi = -\frac{\rho(x, y)}{\epsilon_{\rm Si}} \tag{2.3}$$

In order to obtain an approximate analytical solution of (2.3), usually the assumption is made that  $\partial^2 \psi / \partial x^2 \ll \partial^2 \psi / \partial y^2$ . This is called the *gradual channel approximation*, which is valid for long-channel devices. The Poisson equation can now be rewritten as:

$$\frac{\partial^2 \psi}{\partial y^2} \approx \frac{q \cdot N_{\rm A}}{\epsilon_{\rm Si}} \cdot \left[ 1 - \exp\left(-\frac{\psi}{\phi_{\rm T}}\right) + \exp\left(\frac{\psi - V - \phi_{\rm B}}{\phi_{\rm T}}\right) \right]$$

(2.4)

where  $\phi_{\rm B} = 2 \cdot \phi_{\rm F}$ . As boundary conditions both  $\psi$  and  $\partial \psi / \partial y$  are taken to be equal to zero deep in the neutral bulk. Using  $\partial^2 \psi / \partial y^2 = 1/2 \cdot \partial (\partial \psi / \partial y)^2 / \partial y$ , the total charge  $Q_{\rm s}$  per unit area in the semiconductor can be obtained from Gauss' law:

$$Q_{s} = \epsilon_{Si} \cdot \frac{\partial \psi}{\partial y}\Big|_{y=0}$$

$$= \pm k_{0} \cdot C_{ox} \cdot \sqrt{\psi_{s} + \phi_{T} \cdot \left[\exp\left(-\frac{\psi_{s}}{\phi_{T}}\right) - 1\right] + \phi_{T} \cdot \exp\left(-\frac{V + \phi_{B}}{m_{S} \cdot \phi_{T}}\right) \cdot \left[\exp\left(\frac{\psi_{s}}{m_{S} \cdot \phi_{T}}\right) - 1\right]}$$

$$(2.5)$$

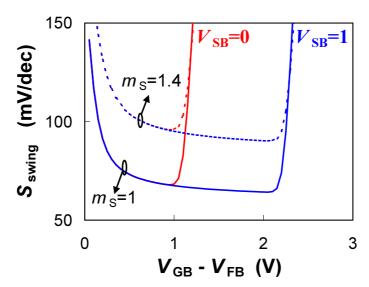

where  $C_{\text{ox}}$  is the gate oxide capacitance per unit area given by  $\epsilon_{\text{ox}}/t_{\text{ox}}$ , and  $k_0$  is the body factor given by  $\sqrt{2 \cdot q \cdot \epsilon_{\text{Si}} \cdot N_{\text{A}}}/C_{\text{ox}}$ . In the above equation, a new parameter  $m_{\text{S}}$  has been introduced in order to take into account short-channel effects as will be discussed in Section 3.2. For the time being,  $m_{\text{S}}$  is taken to be its theoretical value of 1. The charge density  $Q_{\text{s}}$  is negative for  $V_{\text{GB}} > V_{\text{FB}}$  (i.e., inversion) and positive for  $V_{\text{GB}} < V_{\text{FB}}$  (i.e., accumulation).

Applying Gauss' theorem at the oxide interface, the above charge can also be related to the applied gate bias:

$$Q_{\rm s} = -C_{\rm ox} \cdot \left( V_{\rm GB}^* - \psi_{\rm s} \right) \tag{2.6}$$

where the effective gate-bulk bias  $V_{\text{GB}}^*$  is given by  $V_{\text{GB}} - V_{\text{FB}}$ . Equating (2.5) and (2.6), an implicit relation for  $\psi_s(V_{\text{GB}}, V)$  is found:

$$\left(\frac{V_{\rm GB}^* - \psi_{\rm s}}{k_0}\right)^2 = \psi_{\rm s} + \phi_{\rm T} \cdot \left[\exp\left(-\frac{\psi_{\rm s}}{\phi_{\rm T}}\right) - 1\right] + \phi_{\rm T} \cdot \exp\left(-\frac{V + \phi_{\rm B}}{m_{\rm S} \cdot \phi_{\rm T}}\right) \cdot \left[\exp\left(\frac{\psi_{\rm s}}{m_{\rm S} \cdot \phi_{\rm T}}\right) - 1\right] (2.7)$$

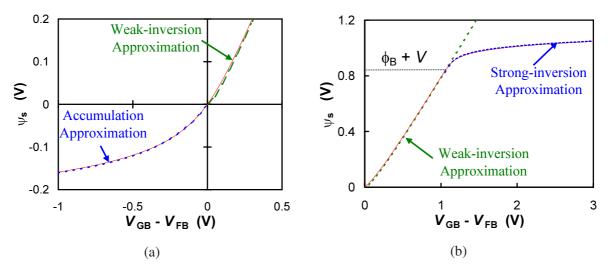

The surface potential  $\psi_s$  cannot be solved analytically from the above relation, and thus it has to be solved iteratively. In Fig. 2.3 (b), the surface potential  $\psi_s$  is given as a function of applied gate bias for different values of quasi-Fermi potential V. Three distinct regions of operation can be observed, the *accumulation region* (i.e.,  $\psi_s < 0$  and  $V_{GB}^* < 0$ ), the *weak-inversion or depletion region* (i.e.,  $0 < \psi_s < \phi_B + V$  and  $0 < V_{GB}^* < \phi_B + V + k_0 \cdot \sqrt{\phi_B + V}$ ) and the *strong-inversion region* (i.e.,  $\psi_s > \phi_B + V$  and  $V_{GB}^* > \phi_B + V + k_0 \cdot \sqrt{\phi_B + V}$ ).

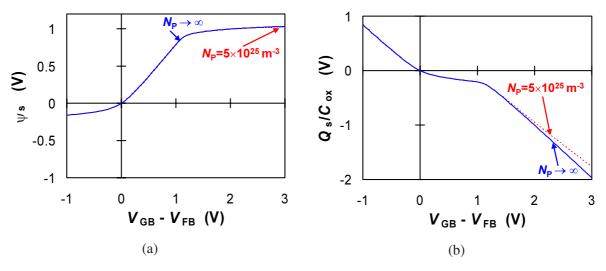

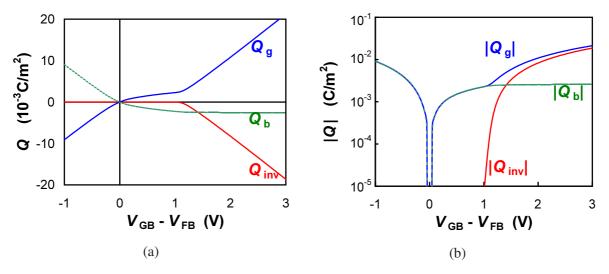

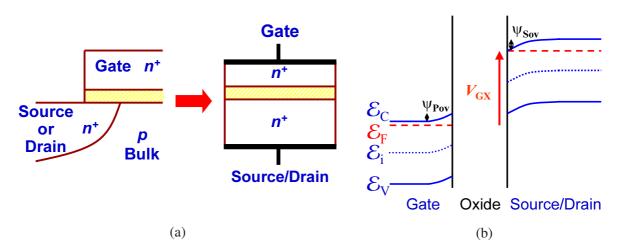

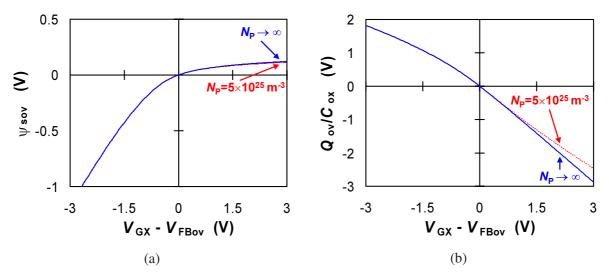

Figure 2.4: (a) The surface potential  $\psi_s$  (as given by (2.10)) and (b) the total charge density  $Q_s$  (as given by (2.8)) as a function of gate bias  $V_{GB}^*$  for an ideal gate, i.e.,  $N_P \rightarrow \infty$  (solid line), and for a polysilicon gate with  $N_P = 5 \times 10^{25} \text{m}^{-3}$  (dashed line). (*n*-MOS, V = 0,  $N_A = 2 \times 10^{23} \text{m}^{-3}$ ,  $t_{ox} = 3.2 \text{nm}$  and  $m_S = 1$ )

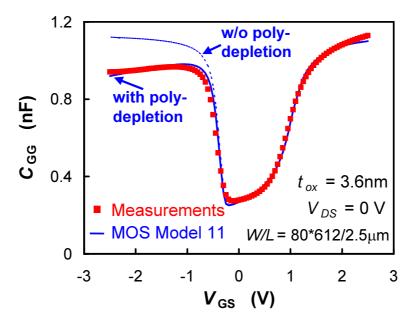

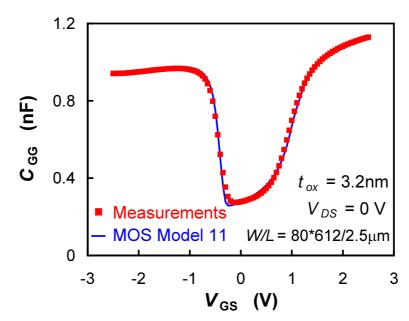

**Poly-Depletion Effect:** In practice, the polysilicon gate is not an ideal conductor. The use of a polysilicon gate in modern technologies results in an unwanted effect, the so-called *poly-depletion effect* [37, 38]. For high values of normal electric field, a depletion layer is not only formed in the silicon substrate but in the polysilicon gate as well, resulting in a potential drop  $\psi_p$  across the polysilicon depletion layer (i.e., the electrostatic potential at the gate/gate-oxide interface with respect to the neutral gate, see Fig. 2.3 (a)). As a consequence, the above-derived relations become inaccurate. The poly-depletion effect particularly affects the MOS *C-V*-characteristics [38], and has to be taken into account. According to Appendix B.1, the total charge density  $Q_s$  becomes:

$$Q_{\rm s} = -C_{\rm ox} \cdot \left( V_{\rm GB}^* - \psi_{\rm s} - \psi_{\rm p} \right) \tag{2.8}$$

where the potential  $\psi_p$  is given by:

$$\psi_{\rm p} = \begin{cases} 0 & \text{for: } V_{\rm GB}^* \le 0 \\ \left( \sqrt{V_{\rm GB}^* - \psi_{\rm s} + k_{\rm P}^2 / 4} - k_{\rm P} / 2 \right)^2 & \text{for: } V_{\rm GB}^* > 0 \end{cases}$$

(2.9)

where  $k_p$  is the gate body factor given by  $\sqrt{2 \cdot q \cdot \epsilon_{Si} \cdot N_P} / C_{ox}$  and  $N_P$  is the net donor doping concentration in the polysilicon gate. Including poly-depletion, the implicit relation for surface potential (2.7) can be rewritten as:

$$\left(\frac{V_{\rm GB}^* - \psi_{\rm s} - \psi_{\rm p}}{k_0}\right)^2 = \psi_{\rm s} + \phi_{\rm T} \cdot \left[\exp\left(-\frac{\psi_{\rm s}}{\phi_{\rm T}}\right) - 1\right]$$

$$+ \phi_{\rm T} \cdot \exp\left(-\frac{V + \phi_{\rm B}}{m_{\rm S} \cdot \phi_{\rm T}}\right) \cdot \left[\exp\left(\frac{\psi_{\rm s}}{m_{\rm S} \cdot \phi_{\rm T}}\right) - 1\right]$$

(2.10)

The influence of poly-depletion can be seen in Fig. 2.4, where the surface potential  $\psi_s$  and the total charge density  $Q_s$  are shown for an ideal metal gate (i.e.,  $N_P \rightarrow \infty$  and consequently  $\psi_p = 0$ ) and

for a typical poly-silicon gate. It is clear that, although it hardly influences the surface potential, poly-depletion reduces the charge density in the strong inversion region and, as a result, it will affect the currents and the capacitances in the MOSFET.

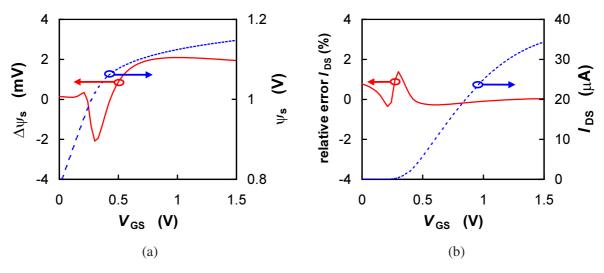

The implicit relation (2.10) for surface potential can only be solved iteratively, which is generally considered to be computationally expensive. This is undesirable for VLSI circuit simulation, and as such it is a drawback of  $\psi_s$ -based models. Nevertheless, these days it is felt that the extra computation time is worth the return in accuracy. Moreover, it is possible to reduce the computation time by using a suitable approximation of  $\psi_s$  [9, 29]. In MM11, an approximate explicit solution of surface potential is used, see Appendix C, resulting in no increase of computation time as compared to MM9.