Received 7 May 2020; revised 8 July 2020; accepted 14 August 2020. Date of publication 21 August 2020; date of current version 22 September 2020. The review of this article was arranged by Editor M. K. Radhakrishnan.

Digital Object Identifier 10.1109/JEDS.2020.3018463

# Physical Modeling of *p*-Type Fluorinated Al-Doped Tin-Oxide Thin Film Transistors

### KADIYAM RAJSHEKAR<sup>® 1</sup>, HSIAO-HSUAN HSU<sup>2</sup>, KOPPOLU UMA MAHENDRA KUMAR<sup>® 3</sup>, P. SATHYANARAYANAN<sup>4</sup>, V. VELMURUGAN<sup>4</sup> (Member, IEEE), CHUN-HU CHENG<sup>®</sup> (Member, IEEE), AND D. KANNADASSAN<sup>® 4</sup>

School of Electronics Engineering, Vellore Institute of Technology, Vellore 632014, India

Department of Materials and Mineral Resources Engineering, National Taipei University of Technology, Taipei 10608, Taiwan

Department of Physics, School of Advanced Sciences, Vellore Institute of Technology, Vellore 632014, India

4 Centre for Nanotechnology Research, Vellore Institute of Technology, Vellore 632014, India

5 Department of Mechatronic Engineering, National Taiwan Normal University, Taipei 10610, Taiwan

CORRESPONDING AUTHORS: D. KANNADASSAN AND C.-H. CHENG (e-mail: dkannadassan@vit.ac.in; chcheng@ntnu.edu.tw)

This work was supported by the Council of Scientific and Industrial Research (CSIR), Government of India under Grant 09/844(0046)/2018-EMR-I.

**ABSTRACT** Fabrication, physical modeling and dynamic response of *p*-type Al-doped SnO<sub>x</sub> active channel thin film transistors (TFTs) are presented for the potential application of ultra-high definition (UHD) displays. After deposition of Al-doped SnO<sub>x</sub> active layer using reactive co-sputtering, the channel was treated with plasma fluorination which improve the device performance of high  $I_{ON}/I_{OFF}$  ratio of > 10<sup>6</sup>, low subtreshold swing of ~100 mV/dec and high field-effect mobility ( $\mu_{FE}$ ) of 4.8  $cm^2V^{-1}s^{-1}$ . To understand the origin of such high performance, physical modeling and numerical simulations were performed using density of state (DOS) model of defects/traps of oxide semiconductor. This model describes the modifications of donor-like tail states and acceptor-like Gaussian defect states due to Al doping on SnO<sub>x</sub> and fluorine treatment. To evaluate the device performance for UHD large scale displays, the dynamic responses of *p*-type TFT pixel circuit for various requirements are simulated with physical models. These results suggest that the Al-doped SnO<sub>x</sub> TFTs are potential candidates for future high-definition displays and many applications in transparent electronics.

**INDEX TERMS** Thin film transistors (TFTs), Al doped  $SnO_x$ , plasma fluorination, density of states (DOS), dynamic response.

#### I. INTRODUCTION

Oxide semiconductors (OSs) have become inevitable commodity in daily life through various electronic gadgets, such as small and large-scale flat panel displays, solar cells and optical sensors [1], [2]. Conventionally, *n*-type OSs were used in development of thin film transistors (TFTs) over the last 40 years, such as  $In_2O_3$ ,  $SnO_2$  and ZnO [3]. In recent times InGaZnO TFTs show high performance for high-speed and high definition large displays [4]. Although *n*-type TFTs are successful, the demand for *p*-type OS has emerged to develop low complexity CMOS circuits. Such CMOS circuits yield high circuit density with low energy consumption. Alternatively, the most of the optoelectronic devices need efficient *p* and *n* type OSs to form *p*-*n* junctions for light emission or detection. On the other hand, ultra-high definition (UHD) displays, such as active matrix LCDs and OLEDs (AMLCDs and AMOLEDs), support high resolutions up to  $8K \times 4K$  ( $7680 \times 4320$  pixels) with frame rates up to 120 Hz [5]. However, higher frame rates, more than 240 Hz, are required for advanced displays, such as 3D displays [6]. In such environments, each pixel has shorter time margin to complete charging cycle of storage capacitors in the sub-pixel unit. N-type a-Si:H and InGaZnO TFTs are often used to meet the design specification [7].

In recent times, few fully oxide CMOS inverters are proposed with p-type  $Cu_2O$  [8] and SnO [9]. It is observed few CMOS configuration such as p-type SnO/ntype InGaZnO and p-type  $Cu_2O/n$ -type InGaZnO show a high voltage gain of > 120 [8], [9]. Recently Chiu *et al.*, demonstrated oxide CMOS inverters for XOR, NAND, XNOR and ring oscillator using large area sputtering process [10]. However, reports on *p*-type TFT pixel circuits are rare. Although significant progress made for p-type TFTs, they hardly yield the performance of n-type TFTs which restrict to enter in the industry market. This is due to few key limitation of p-type OSs: low field-effect mobility, high Off current and high interfacial defects [11]. These gaps can be filled by development of efficient and wideband *p*type OSs. Among the p-type OSs, tin oxide is considerably promising due to its high stability in the air, good uniformity for volume production and high field-effect mobility [11].

Tin oxide shows three crystalline structures, such as SnO<sub>2</sub>, SnO, and Sn<sub>3</sub>O<sub>4</sub>. Amongst these, SnO<sub>2</sub> and SnO are widely studied for transparent electronic applications. SnO exhibits *p*-type conductivity naturally due to the native defects (Sn-rich and O-deficient) [12]. Including our recent findings [13], [14], various reports are available on fabrication of p-type SnO TFTs with field effect mobility of  $\mu_{FE} > 4 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  with  $I_{ON}/I_{OFF}$  ratio > 10<sup>2</sup> [15]. Also, SnO shows a narrow bandgap of 0.9 eV which limits the transparency and  $I_{ON}/I_{OFF}$  ratio. Bandgap of OSs can be widened through various techniques. For instance, doping Al into Cu<sub>2</sub>O results CuAlO<sub>2</sub> delafossite which yields bangap of > 3 eV and stable *p*-type conductivity [16]. Other Cu-based delafossites (CuMO<sub>2</sub>, M = Cr, B, Sc, Y, In, Ga) show *p*-type conductivity with direct or indirect wide bandgap [17], [18], [19].

Metal (M) doped p-type tin oxide TFTs were reported by few research groups [20], [21], [22]. Experimentally, *p*-type conductivity in tin oxide has been reported by doping with Li, Al, Ga, Mg and Ni [20], [23], [24], [25], [26], [27]. Doping Li has been proposed to act as a substitutional dopant in SnO<sub>2</sub>, due to the fact that the ionic radius of Li<sup>I</sup> (0.68 Å) is similar to that of Sn<sup>IV</sup> (0.71 Å) [23]. Therefore, substitution of Sn<sup>4+</sup> ion by Li<sup>1+</sup> ion should cause to form three postive charges (holes) in the valence band. Studies indicate that inversion of polarity from *n*-type to *p*-type occurs only at high Li dopant percentages [23], [28], [29]. Similarly doping with Al, Ga and In were studied for decades for both OSs and gas-sensing applications [22]. Mohaghegh et al., studied the influence of Al doped SnO<sub>2</sub> by varying Al concentration. They found that increase in Al doping up to 8 at%, holes becomes the majority carriers and hence p-type conduction takes place. Below the 8 at%, n-type conductivity dominates [24]. Similarly, Ahmed et al., have tested Al doping levels from 2.31% to 18.56% and found that the Seeback coefficient has changed sign at 12.05% which indicate the transformation from n to p-type [20]. Zhao et al. reported Al doped SnO<sub>2</sub> thin films, annealed at different temperature [21]. It has exhibited a very low resistivity of 0.81  $\Omega$ cm, with a relatively high carrier concentration of 7.2  $\times$  10<sup>18</sup> cm<sup>-3</sup> at 450 °C for 4 hr. However the hall mobility was reduced to 1.1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> from 3.6  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  due to increment in the ionized acceptors. Physical treatment by oxygen, hydrogen or nitrogen has been known to be an effective way to improve the

surfaces properties of OS based optoelectronic devices [30], [31]. Alternatively, fluorine plasma treatment (FPT) yield excellent surface properties for OSs [14], [32], [33]. This process has reduced the channel roughness and passivated the bulk and interface traps, which has improved the  $I_{ON}$ / $I_{OFF}$  ratio, mobility, and subthreshold swing (SS) substantially [14], [32]. FPT on HfO<sub>2</sub> dielectric layer improves the performance of the MOS configuration. This results improvement in C-V hysteresis from 1.1 to 0.045 V due to the elimination of charge trapping phenomena [34]. Our research has demonstrated fabrication of high performance SnO and Al-SnO<sub>x</sub> TFTs with plasma fluorination recently [13], [32].

To understand the enhancement of TFT performance due to plasma treatment and doping of metal, a physics based device modeling may play a major role. This is possible by development of physical model for carrier transport in OS. CAD based numerical simulations can offer such a understanding in device and circuit level. Carrier transport in OS often modeled using density of states (DOS) of defects/traps [35], [36]. Recently, the effects of plasma fluorination in *p*-type SnO TFTs were modeled and simulated by Rajshekar et al., [13]. The model and simulation indicated that the significant improvement in device performance could be attributed to fluorine plasma that has suppressed the interface trap density and reduced the acceptor-like Gaussian states. The change in grain size is related to the lattice strain due to plasma treatment affecting the field-effect mobility and change in the carrier concentration.

Considering the above mentioned facts, the fabrication and FPT of Al doped  $SnO_x$  TFTs are demonstrated and presented in this article. After deposition of Al-doped  $SnO_x$  active layer using reactive co-sputtering, the channel was treated with plasma fluorination which improve the device perfomance of high  $I_{ON}/I_{OFF}$  ratio of > 10<sup>6</sup>, low substhreshold swing of ~100 mV/dec and high field-effect mobility ( $\mu_{FE}$ ) of 4.8  $cm^2V^{-1}s^{-1}$ . Section II presents the fabrication and characterization of fluorinated Al-SnO<sub>x</sub> TFTs. With physical modeling and numerical simulations, the physics and origin of p-type conductivity, TFT performance, effect of fluorine treatment and limitations are investigated in Section III. Using the optimized simulation platform, dynamic response of fluorinated Al-SnO<sub>x</sub> TFTs are simulated and studied the charging and holding performance of p-type TFTs in Section IV.

## II. FABRICATION AND CHARACTERIZATION OF AL-DOPED SNO<sub>X</sub> TFTS

The fabrication of Al-doped  $\text{SnO}_x$  TFTs with bottom gate structure was initiated by growth of a 50 nm HfO<sub>2</sub> thin film on  $n^{++}$  silicon substrate using e-beam evaporation. Here,  $n^{++}$  silicon act as both substrate and gate electrode. To reduce the defects and improve the dielectric quality, this structure was annealed at 400 °C in the presence of nitrogen for 20 min. Using reactive co-sputtering technique, an active layer of 8 nm thick Al-doped  $\text{SnO}_x$  thin film was

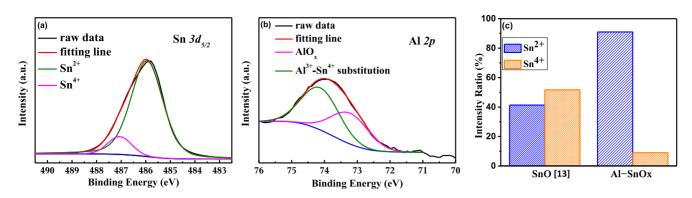

FIGURE 1. (a) Sn  $3d_{5/2}$  photoelectron peaks of XPS spectra of Al doped SnO<sub>x</sub> thin film, (b) Al 2p photoelectron peaks of XPS spectra of Al doped SnO<sub>x</sub> thin films and (c) Relative peak areas corresponding to Sn<sup>2+</sup> and Sn<sup>4+</sup> for Al-SnO<sub>x</sub> and SnO [13].

deposited using Sn and Al targets with RF power 25 W in the presence of oxygen. Later the active layer was annealed at 200 °C for 30 min in nitrogen environment. Fluorine plasma treatment was carried out on the active layers at different plasma powers, i.e., 40, 60 and 80 W for 60 secs using a CF<sub>4</sub> plasma RF unit in a reactive-ion-etching (RIE) system at a pressure of 10 mTorr. Nickel source/drain electrodes were evaporated through shadow mask to form a channel length of 60 µm and width of 520 µm. To study the effect of fluorine treatment, untreated Al-SnO<sub>x</sub> TFTs were fabricated as a control sample. Also, MOS capacitors of same dielectrics with Ni gate electrode of radius 60 µm were fabricated to measure the gate-oxide capacitance and leakage characteristics. Device characterizations, such as voltage-current (V-I) and capacitance-voltage (C-V), were performed using an HP 4156 semiconductor parameter analyzer and Agilent E4980A LCR meter at room temperature. The measured transfer  $I_D - V_G$  and output  $I_D - V_D$  characteristics of Al-doped  $SnO_x$  TFT devices, treated at various fluorine plasma powers, were presented in our earlier report [32]. The untreated and treated Al-doped  $SnO_x$  TFTs exhibit *p*-type conduction with  $I_{ON}/I_{OFF}$  of  $1.7 \times 10^3$  and  $2.6 \times 10^6$  with subthreshold swing of 782 and 174 mV/dec respectively. The calculated fieldeffect mobility ( $\mu_{FE}$ ) ranges from 2.1 to 4.8 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, at gate voltage of -3 V and drain voltages of -0.1 and -0.8 V, for the treated and untreated samples.

To understand the effect of Al doping on  $\text{SnO}_x$ , the XPS analysis was performed. Fig. 1 (a) and (b) presents the Sn  $3d_{5/2}$  and Al 2p spectra in Al-SnO<sub>x</sub> thin film respectively. The peaks of oxidation states  $\text{Sn}^{2+}$  and  $\text{Sn}^{4+}$  are deconvoluted in two sub-peaks by Gaussian fitting method, falls on at 486.0 and 486.7 eV, respectively. Fig. 1(c) shows the calculated relative peak areas corresponding to  $\text{Sn}^{2+}$  and  $\text{Sn}^{4+}$  in Al-SnO<sub>x</sub>. This is also shown for SnO thin film reported earlier [13] for comparison. It is clear that due to Al doping, the  $\text{Sn}^{4+}$  peak decreases with a significant increase in the intensity of the  $\text{Sn}^{2+}$  states. During co-sputtering process, Al atoms replace  $\text{Sn}^{4+}$  in the lattice or Sn interstitials which is clear from the comparison with SnO thin film. This may change in the stoichiometry of the oxide state

$(Sn^{4+} to Sn^{2+})$  which results in reduction of  $Sn^{4+}$  concentration. These changes support the *p*-type characteristics of Al-SnO<sub>x</sub>.

#### III. PHYSICAL MODELING AND NUMERICAL SIMULATION OF AL-SNO<sub>X</sub> TFTS

For the design and optimization of large scale displays, numerical and circuit simulations are important to improve the circuit performance and reduce the cost of fabrication. Numerical simulations also provide the physical insight of device characteristics, such as carrier transport, and give directions to optimize the device structure to show improved device performance. TCAD tools are often used for numerical simulation of semiconductor devices which solves the continuity, Poisson and the charge transport equations.

Simulation of TFTs with Al-doped  $\text{SnO}_x$  active layer is challenging since no detailed reports or physical models are available on *p*-type Al-doped  $\text{SnO}_x$ . In this work, first we have reviewed the physical parameters of Al-doped  $\text{SnO}_x$ , such as bandgap, defect and mobility, based on reports available on first principle simulation and experimental works. These data are used to model the carrier transport of TFTs in the numerical simulation.

#### A. P-TYPE AL DOPED-SNO<sub>X</sub>: PHYSICAL MODELS

The type of conductivity of Tin oxide  $(SnO_x)$  depends on the oxidation state of Sn. It is well known that tin-monoxide (SnO) and tin-oxide  $(SnO_2)$  are *p*-type and *n*-type transparent semiconductors respectively. In general, formation of *p*-type conductivity in OS is rare and difficult due to the dominating nature of O 2*p* states. This state results strong localization of holes and forbids the *p*-type conduction. In *p*-type SnO, the Sn 5*s* level is near to the O 2*p* and hybridized at valence band maximum (VBM) [12]. This reduces the localization of holes, and increases the hole mobility. P-type nature of SnO shows that it has large amount of native acceptors which are due to defects created Sn vacancies and O interstitials. The first principal studies shows that the *p*-type conductivity is due to Sn vacancies [12]. In our earlier report, we have studied the effect of FPT on SnO TFTs and presented DOS model for defect states of SnO [13].

Like SnO, *p*-type Al doped  $SnO_x$  is not studied in detailed. However, few reports are available on p-type Al doped SnO<sub>x</sub> [37]. Perhaps, values of many important parameters, such as bandgap, mobility and effective DOS ( $N_C$  and  $N_V$ ), are not available for Al-doped  $SnO_x$ . Thus, few optimal assumptions are required to start modeling of physical parameters and the numerical simulations. Cu<sub>2</sub>O and SnO are well studied *p*-type oxides due to their more dispersed VBM, which results from the hybridization between the O 2p and Cu 3d (or Sn 5s) orbitals. Though the bandgaps of Cu<sub>2</sub>O and SnO are not same, but these oxides are quite comparable in terms of their electron affinity ( $Cu_2O = 3.2 \text{ eV}$ an SnO = 3.7 eV) and ionization potential ( $Cu_2O = 4.08$  $\sim$ 5.36 and SnO = 4.4 eV) [38], [39]. Several researchers had reported that the *n*-type oxides are found to have high electron affinities and charge neutrality levels lie in midgap or the upper part of their gap, whereas *p*-type oxides have small photoionization potentials and charge neutrality levels lie in the lower gap [1], [40], [41]. In this case since both Cu<sub>2</sub>O and SnO has low ionization potential, which correlates with their *p*-type characteristics.

To increase the bandgap of Cu<sub>2</sub>O, Kawazoe et al. came with the idea of mixing orbitals of appropriate counter cations that have filled energy levels equivalent to O 2p level [16]. They had fabricated copper aluminum oxide  $(CuAlO_{2+x})$  which gives a large bandgap of more than 3.1 eV and electron affinity of  $\sim 2$  eV. This doping has improved the transparancy and electrical performance of TFTs for display applications. Similar characteristics were found when Al doped with  $SnO_2$  [20], [24]. Using these reports, we have speculated that similar modifications might have happend in case of Al doping on SnO. So we have assumed the bandgap of 2 eV (+/- 0.2 eV) for Al-SnO<sub>x</sub> where SnO has 0.9 eV. This also causes the reduction in the electron affinity value for Al-SnO<sub>x</sub> as 2 eV. The hall mobility value is taken as 7.6 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> based on report of Bagheri-Mohagheghi and Shokooh-Saremi [24].

Conductivity in oxide semiconductors is often modeled by defect density model, proposed for amorphous hydrogenated silicon (a-Si:H) was given by Davis and Mott [35]. For Aldoped  $SnO_x$  case, the *p*-type conductivity is modeled using similar defect model which accounts the interface donor and acceptor traps. In this model, the band-tail states include donor-like valance band  $(g_{TD}(E))$  and acceptpr-like conduction band  $(g_{TA}(E))$  with Gaussian mid-gap states include acceptor and donor-like states  $(g_{GD}(E) \text{ and } g_{GA}(E))$ . The total DOS in written as sum of all states:

$$g(E) = g_{TA}(E) + g_{TD}(E) + g_{GA}(E) + g_{GD}(E)$$

(1)

where

$$g_{TA}(E) = N_{TA}(E)exp(E - E_C/W_{TA})$$

$$g_{TD}(E) = N_{TD}(E)exp(E_V - E/W_{TD})$$

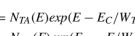

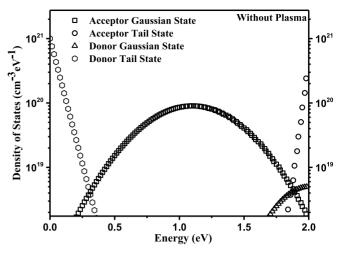

FIGURE 2. Different NGA and WTD without plasma fluorination.

$$g_{GA}(E) = N_{GA}(E)exp\left[-(E_{GA} - E)^2/W_{GA}^2\right]$$

$$g_{GD}(E) = N_{GD}(E)exp\left[-(E - E_{GD})^2/W_{GD}^2\right]$$

(2)

where E is trap energy level. In this model, the magnitude of DOS and the slope are given by N and W respectively. Detailed modeling is described in our earlier report [13].

#### **B. SIMULATION OF AL DOPED SNOX TFTS**

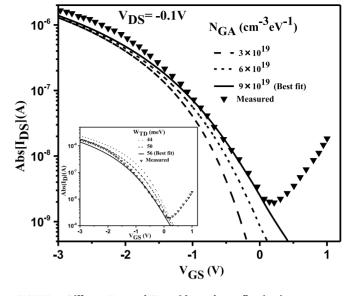

Numerical simulation of Al-SnO<sub>x</sub> TFTs, with and without fluorination, was performed using ATLAS simulator of TCAD Silvaco [42]. A two dimensional bottom gate structure of Al-SnO<sub>x</sub> TFT was constructed, as shown in inset of Fig. 3 (a), to meet the realistic structure of fabricated TFTs with computational simplicity. On the heavily doped Si bottom gate, with workfunction of 4.17 eV, a 50 nm HfO<sub>2</sub> gate oxide and 8 nm Al-doped  $SnO_x$  active layer were placed. A uniform distribution of physical parameters, such as defect, doping etc., is considered over the active of device. Source and drain (S/D) are created by Ni Ohmic contacts with workfuction of 5.1 eV are seperated by a channel length of 60 µm and width of 520 µm with gate-S/D overlap of 10 µm.

In view of accuracy of simulation, a dense meshing has been done near the Al-SnO<sub>x</sub>/HfO<sub>2</sub> interface through out the vertical axis. Important simulation models like Fermi-Dirac model, defect model and field-dependent mobility model are applied in the Al-SnO<sub>x</sub> active layer. The homogeneous Neumann boundary conditions were set at the surface of the channel layer in order to control the carriers flow between S/D contacts during simulation. Apart from the ohmic contact model, other models such as carrier tunneling and thermionic models were included for Nickel S/D. Simulation was performed based on the discrete DOS model which accounts both donor (DON) and acceptor-like (ACC)

**FIGURE 3.** Compatibility of simulated and measured (a) transfer and (b) output characteristics of  $AI-SnO_X$  TFT for without plasma.

trap states of 128 and 128 levels respectively. These simulation settings gives a negligible variation of  $\sim$ 50 nA in ON current.

Numerical simulation of *p*-type Al-SnO<sub>x</sub>TFTs to fit with measured electrical characteristics, several key parameters have to be adjusted. However, few are significantly influencing the *I*-V characteristics, such as  $N_{GA}$ ,  $W_{TD}$  and  $N_{GD}$ . Using ATLAS, the simulations were peformed for various  $N_{GA}$  and  $W_{TD}$ , with major key parameters listed in Table 1. Fig. 2 inset shows the simulated transfer characteristics of Al-SnO<sub>x</sub> TFT for various  $W_{TD}$ , along with measured data. Amongst all,  $W_{TD} = 56$  meV results best fit. This value is nearly 1/3 times more than that of SnO or a-Si:H (for holes) [13], [43]. This may be due to Al doping, which enhances the disorder by change in distribution of coordination number, bond angles and bond length of Al-SnO<sub>x</sub> lattice. Similarly a best fit of simulation and measured has come for  $N_{GA}$  equals to  $9 \times 10^{19} cm^{-3} eV^{-1}$ , shown in Fig. 2.

FIGURE 4. DOS profile for Al-SnO<sub>x</sub> TFT for without plasma.

TABLE 1. Key simulation parameters in DOS model for Al-SnO<sub>X</sub> TFTs with and without fluorination.

| Symbols         | Units              | Al-SnO $_x$ (w/o FPT) | Al-SnO $_x$ (With FPT, 60W) |

|-----------------|--------------------|-----------------------|-----------------------------|

| $N_C$           | $cm^{-3}$          | $2.41\times10^{18}$   | $2.41\times10^{18}$         |

| $N_V$           | $cm^{-3}$          | $9.13 	imes 10^{19}$  | $9.13\times10^{19}$         |

| $N_{TA}$        | $cm^{-3}eV^{-1}$   | $2.43\times10^{20}$   | $2.43\times10^{20}$         |

| $N_{TD}$        | $cm^{-3}eV^{-1}$   | $1 \times 10^{21}$    | $1 \times 10^{21}$          |

| $W_{TA}$        | meV                | 30                    | 30                          |

| $W_{TD}$        | meV                | 56                    | 60                          |

| $E_g$           | eV                 | 2                     | 2                           |

| $\chi_e$        | eV                 | 2                     | 2                           |

| W <sub>GA</sub> | eV                 | 0.45                  | 0.3                         |

| $E_{GA}$        | eV                 | 1.1                   | 1.1                         |

| $E_{GD}$        | eV                 | 2                     | 2                           |

| $W_{GD}$        | eV                 | 0.3                   | 0.3                         |

| N <sub>GD</sub> | $cm^{-3}eV^{-1}$   | $5 \times 10^{18}$    | $4 \times 10^{18}$          |

| N <sub>GA</sub> | $cm^{-3}eV^{-1}$   | $9 \times 10^{19}$    | $2 \times 10^{19}$          |

| $\mu_P$         | $cm^2V^{-1}s^{-1}$ | 7.6                   | 7.6                         |

It is observed that  $N_{GA}$  significantly affects the OFF current. Other parameters of defect model have not impacted much. Fig. 3 (a) and (b) shows the transfer and output characteristics of Al-SnO<sub>x</sub> TFTs without plasma treatment. It shows a high value of SS (782 mV/dec) and low ON/OFF current ratio (~ 2 × 10<sup>3</sup>) due to the presence of traps present at/near the interface. Compare to our earlier report [13], there is an increment in the field-effect mobility ( $\mu_{FE}$ ) value of 3.49 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. This is due to the incorperation of Al into SnO<sub>x</sub> which significantly improves the mobility due to generation of extra hole through Al<sup>3+</sup>-Sn<sup>4+</sup> substitution [44]. Using probe tools of ATLAS, the profile of DOS is extracted at active layer, presented in Fig. 4 and the all optimized parameters are summarized in Table 1.

#### C. EFFECT OF FLUORINE TREATMENT

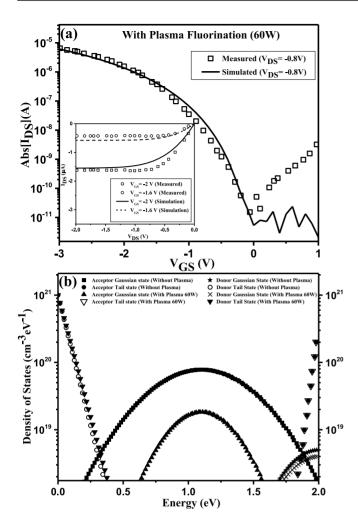

Fig. 5 (a) shows the measured  $I_D$ - $V_G$  and  $I_D$ - $V_D$  of Al-SnO<sub>x</sub> treated with fluorine plasma power of 60 W. It is

**FIGURE 5.** (a) Transfer and output (inset) characteristics of  $AI-SnO_X$  TFT with fluorine plasma treatment of 60W and (b) DOS profile for  $AI-SnO_X$  TFT for both with and without plasma.

observed that a significant reduction in  $I_{ON}$  and  $I_{OFF}$  compare to that of untreated sample. To understand the effect of fluorination a numerical simulation was performed to fit the measured I-V characteristics. A best fit observed for the reduction of acceptor-like Gaussian states ( $N_{GA}$ ) and increase in slope of valence-band tail states ( $W_{TD}$ ). The compatibility of simulated and measured I-V characteristics are presented in Fig. 5 (a). Due to FPT, there are two possible charge dynamic mechanism might have occured:

$$O_o^x + F^{-1} \to F_o^{+1} + e^{-1}$$

(3)

$$V_o^{+2} + 2e^{-1} + F^{-1} \to F_o^{+1} + e^{-1}$$

(4)

According to the first mechanism, equation (3), the fluorine atoms replace the oxygen atoms of Al-SnOx lattice and induces free electron due to the difference in the electronegativity between oxygen ( $O^{2-}$ ) and fluorine ( $F^{1-}$ ). This mechanism helps in filling of acceptor-like traps at/near Al-SnO<sub>x</sub>/HfO<sub>2</sub> interface [33]. This causes reduction in the N<sub>GA</sub> concentration in DOS which results in the decrement in

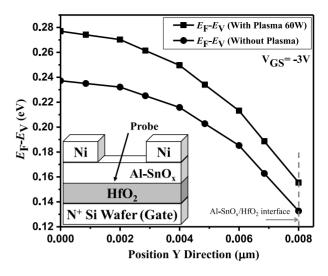

**FIGURE 6.**  $(E_F - E_V)$  Vs Position Y Direction for Vgs = -3V.

the OFF current and improves the SS from 782 mV/dec to 174 mV/dec.

In the second mechanism, refer equation (4), the oxygen vacancies are passivated by fluorine ions. This yield a reduction in oxygen vacancies (donor-like traps) at/near Al-SnO<sub>x</sub> /HfO<sub>2</sub> which reduces the  $N_{GD}$ . However, the effect is minimal. Alternatively, there is a decrement in the ON current and field-effective mobility by an order of  $\sim 1/2$  decade and  $\sim 1.75$  times respectively. This causes increment in the W<sub>TD</sub> to 60 meV. This change is notably small from untreated Al- $SnO_x$  TFT. This concludes the disorder due to fluorination is much lesser than that of Al doping on SnO lattice. Increase in W<sub>TD</sub> affects the ON current, this could be possibly caused by the reduction in hole carrier concentration due to plasma fluorination. This can be well understood based on the Fig. 6 which gives  $E_F$ - $E_V$  Vs Position Y direction. One can observe an increment in the  $E_F$ - $E_V$  from 133 to 157 meV near the interface after fluorination. This increases filled/localized holes near/at the interface which in turn reduces the hole carriers. This is due to the increase in the intensity ratio of  $Sn^{4+}$  in comparison with  $Sn^{2+}$  which captures free holes generated in the Al-SnO<sub>x</sub> thin film [45]. Fig. 5(b) shows the derived DOS of both with and without fluorinated Al- $SnO_x$  channel. The overall DOS parameters for both with and without fluorination is shown in the Table 1. The overall performance of Al-SnO<sub>x</sub> TFT is shown in Table 2.

#### IV. DYNAMIC RESPONSE OF FLUORINATED AL-SNO<sub>X</sub> TFTS

High definition display technologies, like UHD (8K and 4K), suffers with tight requirements of shorter charging time margin ( $t_{CM}$ ) and image flickering. To address these issues dynamic characterization of TFTs for AMLCDs and AMOLEDs are often performed. According to Kaneko *et al.*, this flickering phenomena occurs as a result of shift in the feed through voltage ( $\Delta V_p$ ), which is associated to the parasitics capacitances between source and drain [46]. Likeswise Lee *et al.*, studied the  $\Delta V_p$  and  $t_{CM}$  in details through

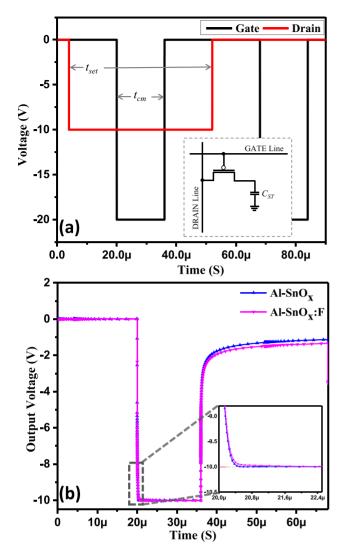

FIGURE 7. (a) Input gate and drain pulses, (b) Output voltage at the source terminal of the Al-SnO<sub>X</sub> and Al-SnO<sub>X</sub>:F TFTs.

| Parameters                   | Without              | With Plasma          |

|------------------------------|----------------------|----------------------|

|                              | Plasma               | Fluorination         |

|                              | Fluorination         | 60W                  |

|                              | (measured)           | (measured)           |

| $V_{th}(V)$                  | -2.2                 | -2.1                 |

| SS (mV/dec)                  | 782                  | 174                  |

| $\mu_{FE}(cm^2V^{-1}s^{-1})$ | 3.49                 | 2.1                  |

| On/Off ratio                 | $\sim 2 \times 10^3$ | $\sim 3 \times 10^6$ |

| N <sub>it</sub> [32]         | $2.3 	imes 10^{13}$  | $3.7 	imes 10^{12}$  |

TABLE 2. Overall Al-SnO<sub>x</sub> TFT performance.

dynamic response of a-Si:H [47]. Recently, Yu *et al.* have studied the dynamic characterization of InGaZnO TFTs for UHD display requirements, considering the pixel densities and time margins [7]. It was found that InGaZnO TFTs show faster and stable charging response while comparing normal/recessed gate a-Si:H TFTs. It is due to the high effective mobility of InGaZnO TFT which is 9.1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>

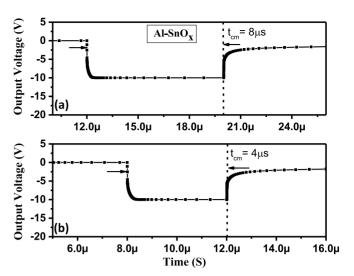

**FIGURE 8.** Output voltage at the source terminal for tcm (a) 8  $\mu$ s and (b) 4  $\mu$ s.

and better SS of ~0.13 V/dec. All these studies were demostrated for *n*-type TFTs and rare reports are available for *p*-type [48], [49]. By considering the above facts, we presented a detailed report on the dynamic characteristics of Al-SnO<sub>x</sub> TFTs and the effect of plasma fluorination. In order to give a detailed analysis on charging and holding process, we have also simulated the SnO TFTs and compared with the performance of Al-SnO<sub>x</sub> TFTs for the requirements of UHDs.

A simple pixel circuit with one TFT and one storage capacitor ( $C_{ST}$ ) is considered in this work, as shown in inset of Fig. 7(a). For each frame, a fixed DRAIN pulse of amplitude  $V_{DH}$  (DRAIN voltage high) applied at DRAIN line as drain bias to set the charging process, shown in Fig. 7(a). This pulse returns to low DRAIN voltage  $V_{DL}$  to reset the frame. The set/reset period ( $t_{set}$ ) is often calculated based on the charging-time margin ( $t_{cm}$ ) of the GATE pulse of each frame. To estimate the  $t_{cm}$ , we have adopted the expression from [50]:

$$t_{cm} = \frac{1}{FR \times N_{RL}} \tag{5}$$

where *FR* is frame rate and  $N_{RL}$  is number of row-lines in the diplay panel. Considering the display specifications of UHD technologies [5], the full HD and 4K displays need  $t_{cm}$  of 16 and 8  $\mu s$  respectively. Assuming  $t_{set} = 3 \times t_{cm}$ , each GATE pulse will be arrived at  $1 \times t_{cm}$  just after the rise of set/reset select pulse. The rising and falling edge times  $(t_r \text{ and } t_f)$  of gate pulse may vary from 1 to 100 ns which significantly affect the voltage holding process of storage capacitor. However, GATE and DRAIN lines of large scale AMLCDs show a delay due to RC parasitics which impacts on the requirements of  $t_{cm}$  which is not considered in this work.

Transient simulation of pixel circuit, having TFT with different *p*-type oxide semiconductor properties, with various time margins are performed using mixed mode tools of

**TABLE 3.** Calculated time constants for pixel circuits with Al-SnO<sub>X</sub> and Al-SnO<sub>X</sub>: F TFTs.

| TFTs:                       | Al-SnO $_x$ | Al-SnO <sub><math>x</math></sub> :F |

|-----------------------------|-------------|-------------------------------------|

| $\tau$ (µs) from eq. 7      | 0.64        | 1.06                                |

| $\tau$ (µs) from simulation | 0.52        | 0.95                                |

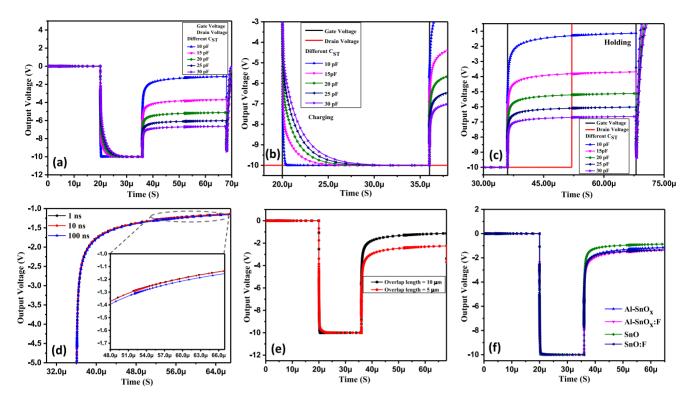

ATLAS. TFTs are considered with Fermi-Dirac and defect models whose steady-state analysis were initiate with twostage Newton method [42]. In this simulation, both GATE and DRAIN pulses are rising and falling in exponential scale to avoid the convergence issues in the numerical simulation. In this regard, the  $t_r$  and  $t_f$  are taken as 10 ns and minimum simulation time-step of 1 ns. For all simulations, the amplitude of GATE pulse is set to high  $V_{GH} = -20$  V and reset low of  $V_{GL} = 0$  V. On the other hand, the DRAIN pulse is excited with  $V_{DH} = -10$  V and  $V_{DL} = 0$  V for set and reset of charging process respectively.  $C_{ST}$  of 10 pF is considered to maximixe the charging delay to evaluate the perfomance of *p*-type TFTs. For Al-SnO<sub>x</sub> and flourinated Al-SnO<sub>x</sub> (Al-SnO<sub>x</sub>:F) TFTs of channel length 60  $\mu$ m, channel thickness 8 nm and S/D overlap length 10  $\mu$ m and device width of 60  $\mu$ m, the simulation of dynamic response is perfored for full HD displays ( $t_{cm}$  of 16  $\mu s$ ). The output votage  $(V_{OUT})$  accross the storage capacitor during the application of GATE and DRAIN pulses for the pixel circuit, with Al-SnO<sub>x</sub> and Al-SnO<sub>x</sub>:F TFT cases, are presented in Fig. 7(b). One can observe that both the TFTs are capable of charging the  $C_{ST}$  to  $V_{DH}$  within 16  $\mu s$ .

To quantify the charging characteristics, an exponential fit of time constant ( $\tau$ ) for output voltage inside GATE pulse using simple parallel RC model. Therefore the output voltage can be expressed as:

$$C_{ST}\frac{dV_{OUT}}{dt} = \frac{\mu_{FE}C_{ox}W}{L}(V_G - V_{OUT} - V_{th})(V_D - V_{OUT})$$

(6)

This equation yields the time required to charge the  $C_{ST}$  [7],

$$t_{ch} = \frac{C_{ST}L}{\mu_{FE}C_{ox}W} \frac{1}{(V_{GH} - V_{DH} - V_{th})} \\ \times \ln \frac{(V_{GH} - V_{out} - V_{th})V_{DH}}{(V_{GH} - V_{th})(V_{DH} - V_{out})}$$

(7)

An approximate value of time constant can be calculated from the above expression by substituting  $V_{OUT} = 0.63V_{DH}$ . From this calculation, we found the time constants for both the TFT cases and listed in Table 3. Similarly, the time constant is also calculated from simulation results for time required to charge 6.3 V from  $V_{DL} = 0$  which is also listed in the table. It is clear that the time constant is lowest for Al-SnO<sub>x</sub> without fluorination. This is due to the high mobility of Al-SnO<sub>x</sub> which makes time constant low since it is inversely proportion which considerabily reduces the resistivity of the TFT which helps in fast charging. After fluorination, the mobility decreases due to increase in disorder in the material, which can be seen in the increment of the  $W_{TD}$  value. We have also simulated the dynamic response of device at channal length of 60  $\mu$ m for t<sub>cm</sub> = 8 and 4  $\mu$ s to evaluate the requirements for UHD displays and beyond. It is found that all TFTs are able to charge the C<sub>ST</sub> in less than 1  $\mu$ s.

In AMLCDs, the image flickering is due to sudden reduction of output voltage when GATE pulse is falling from  $V_{GH}$ to  $V_{GL}$ . This reduction of  $V_{OUT}$  is refered as feedthough voltage,  $\Delta V_P$ , shown in Fig. 7(b). From earlier studies of AMLCDs [46], [51], [52], the feedthrough voltage is expressed analytically as,

$$\Delta V_P = \frac{C_{GS}}{C_{GS} + C_{ST}} (V_{th} + V_{SH} - V_{GL}) \tag{8}$$

Here,  $C_{GS}$  is the parasitic capacitance between gate and source of TFT which is due to gate-source overlap. This indicate that the  $\Delta V_P$  is inversely proportional to  $C_{ST}$  and directly proportional to gate-source overlap length ( $L_{OVGS}$ ).

Shown in the Fig. 7(b), Al-SnO<sub>x</sub> and Al-SnO<sub>x</sub>:F TFTs are overlayed. Though Al-SnO<sub>x</sub> TFT shows better performance in terms of charging time, but its  $\Delta V_P$  value is slightly more in comparison with  $Al-SnO_x$ :F. This is due to their difference in the V<sub>th</sub> voltage of  $\sim 0.1$  V. Equation (8) also suggests that the value of  $C_{ST}$  also affect the  $\Delta V_P$ . Figure 9 (a) shows the simulated dynamic response of  $Al-SnO_x$  TFT pixel circuit for different  $C_{ST}$  values from 10 to 30 pF. We can observe that for the larger value of C<sub>ST</sub> results higher charging time and lower  $\Delta V_P$ . For the time margin of  $t_{cm} = 16$  $\mu$ s, the difference in charging time is minimal and only noticeable in the Fig. 9 (b). It is observed that the time constant increases from 0.52 to 1.9  $\mu$ s for C<sub>ST</sub> from 10 to 30 pF. From Fig. 9 (c), the extracted  $\Delta V_P$  are 8.7, 6.2, 4.8, 3.91 and 3.3 V for C<sub>ST</sub> values of 10, 15, 20, 25 and 30 pF respectively. This improvement in  $\Delta V_P$  is due to inversely proportional relationship with  $C_{ST}$ . To further reduce the  $\Delta V_P$ , a larger value of  $C_{ST}$  can be implemented based on the aspect ratio of the AMLCD pixel. To study the influence of falling edge time  $(t_f)$  of GATE pulse on  $\Delta V_P$ , we have simulated Al-SnO<sub>x</sub> TFT for three different  $t_f$  values, i.e., 1 ns, 10 ns, and 100 ns. The output voltage is shown in the Figure 9 (d), found that  $\Delta V_P$  reduced slightly for  $t_f = 100$ ns. For lower  $t_f$ , the GATE pulse is falling at faster rate. In such situation, the excess residual charges in the channel are not drained as the transist time of device is higher than 1  $\mu$ s. This results a feedback path through gate which impacts output voltage even after the GATE pulse reached low. For higher  $t_f$ , this phenomena slows down and yields low  $\Delta V_P$ . One can further reduce  $\Delta V_P$  by controlling the  $t_f$ which is subject to the technology requirement. In a similar manner we have observed the effect of S/D over lap length on  $\Delta V_P$ . For  $L_{OVGS}$  of 5 and 10  $\mu$ m, the output voltage are exracted and shown in the Figure 9 (e). Ultimately decrease in the overlap length will cause a reduction in the  $C_{GS}$  value, directly proportional to  $\Delta V_P$ , resulting lower  $\Delta V_P$ .

FIGURE 9. Dynamic Response of Al-SnO TFTs for various (a) C<sub>ST</sub> (b) Charging capacitor (c) Holding, (d) Different Overlap length, (e) Different t<sub>FE</sub> of V<sub>GH</sub> and (f) Output voltages of SnO, SnO:F, Al-SnO<sub>x</sub> and Al-SnO<sub>x</sub>:F TFTs.

To the compare the Al-SnO<sub>x</sub> performance, we have incorporated the dynamic responce of SnO TFT for both with and without fluorination [13] shown in the Fig. 9 (f). From the figure we can see Al-SnO<sub>x</sub> shows better performance in terms of charging time. This is due to the high mobility value compare to all other TFTs. Clearly Al-doping on SnO<sub>x</sub> has improved the performance of TFT which is due to the generation of extra holes through Al<sup>3+</sup>-Sn<sup>4+</sup>. Plasma fluorination has improved the holding mechanism of the capacitor which ultimately gives less  $\Delta V_P$

#### A. CONCLUSION

In this work, we have presented the detailed study of the effect of Al-doping on  $SnO_x$  and fluorine plasma treatment. The origin of improvement in device performance is studied through physical modeling of fluorinated Al-SnO<sub>x</sub>. Based on numerical simulation and fitting the transfer and output characteristics of Al-SnO<sub>x</sub> TFTs for both with and without fluorine plasma treatments, and simulation of dynamic response, following conclusions are made:

1) The Al-doping on SnO active layer significantly improved the device performance, such as high  $I_{ON}/I_{OFF}$  ratio of > 10<sup>6</sup> and low subthreshold swing of ~100 mV/dec and field-effect mobility ( $\mu_{FE}$ ) of 4.8  $cm^2V^{-1}s^{-1}$  due to modification of band structure and DOS. The Al doping also enhances the disorder in bond angles and bond length in the lattice of SnO which reduces the acceptor-like Gaussian defect states ( $N_{GA}$ ) and increases the slope of donor-like tail states ( $W_{TD}$ ).

- 2) Plasma fluorination treatment of Al-SnO<sub>x</sub> channel layer results the oxidation state of Sn from  $Sn^{2+}$ to  $Sn^{4+}$  which significantly reduces the acceptorlike Gaussian states ( $N_{GA}$ ) and enhances the device performance. At higher plasma power (60 W), the fluorine atoms take the interstitial sites of Al-SnO<sub>x</sub> lattice which leads to the disorder in the channel and modifies the donor-like tail states ( $W_{TD}$ ). This excess fluorination reduces the  $I_{ON}$  current.

- 3) The simulated dynamic responses reveals that the switching characteristics of  $Al-SnO_x$  TFT is superior while comparing the performances of SnO and a-Si:H TFTs. This is due to high mobility of low SS due to Al doping and fluorination. With a time-constant of 0.64  $\mu$ s, the p-type TFT pixel circuit is capable of charging the 10 pF storage capacitors within the charging time-margin requirements for Full HD and UHD displays. This suggests that the TFTs are also suitable for large displays where high storage capacitance is used.

#### ACKNOWLEDGMENT

The authors would like to thank the Editor and anonymous reviewers for the useful comments and insights.

#### REFERENCES

[1] D. Ginley, H. Hosono, and D. Paine, *Handbook of Transparent Conductors*. New York, NY, USA: Springer, 2010.

- [2] T. Kamiya, H. Hiramatsu, K. Nomura, and H. Hosono, "Device applications of transparent oxide semiconductors: Excitonic blue led and transparent flexible TFT," *J. Electroceram.*, vol. 17, nos. 2–4, pp. 267–275, 2006.

- [3] J. Wager, B. Yeh, R. Hoffman, and D. Keszler, "An amorphous oxide semiconductor thin-film transistor route to oxide electronics," *Current Opinion Solid-State Mater. Sci.*, vol. 18, no. 2, pp. 53–61, 2014.

- [4] E. Fortunato, P. Barquinha, and R. Martins, "Oxide semiconductor thin-film transistors: A review of recent advances," *Adv. Mater.*, vol. 24, no. 22, pp. 2945–2986, 2012.

- [5] "Parameter values for ultra-high definition television systems for production and international programme exchange," Int. Telecommun. Union, Geneva, Switzerland, ITU-Recommendation BT.2020-1, 2014.

- [6] S. Kim, B. You, H. Choi, B. Berkeley, D. Kim, and N. Kim, "31.1: Invited paper: World's first 240hz TFT-LCD technology for full-HD LCD-TV and its application to 3D display," in *Soc. Inf. Display Int. Symp. Dig. Tech. Papers*, vol. 40, 2009, pp. 424–427.

- [7] E. K. Yu, R. Zhang, L. Bie, A. Kuo, and J. Kanicki, "Dynamic response of a-InGaZnO and amorphous silicon thin-film transistors for ultra-high definition active-matrix liquid crystal displays," *J. Display Technol.*, vol. 11, no. 5, pp. 471–479, May 2015.

- [8] A. Dindar, J. B. Kim, C. Fuentes-Hernandez, and B. Kippelen, "Metaloxide complementary inverters with a vertical geometry fabricated on flexible substrates," *Appl. Phys. Lett.*, vol. 99, no. 17, pp. 1–4, 2011.

- [9] Y. Li and D. J. Singh, "First principles based screen for identification of transparent conductors," *J. Mater. Chem. C*, vol. 7, pp. 2436–2442, Feb. 2019.

- [10] I.-C. Chiu, Y.-S. Li, M.-S. Tu, and I.-C. Cheng, "Complementary oxide–semiconductor-based circuits with n-channel ZnO and p-Channel SnO thin-film transistors," *IEEE Electron Device Lett.*, vol. 35, no. 12, pp. 1263–1265, Dec. 2014.

- [11] Z. W. Shang, H. H. Hsu, Z. W. Zheng, and C. H. Cheng, "Progress and challenges in p-type oxide-based thin film transistors," *Nanotechnol. Rev.*, vol. 8, no. 1, pp. 422–443, 2019.

- [12] A. Togo, F. Oba, I. Tanaka, and K. Tatsumi, "First-principles calculations of native defects in tin monoxide," *Phys. Rev. B, Condens. Matter Mater. Phys.*, vol. 74, no. 19, Nov. 2006, Art. no. 195128.

- [13] K. Rajshekar *et al.*, "Effect of plasma fluorination in p-type SnO TFTs: Experiments, modeling, and simulation," *IEEE Trans. Electron Devices*, vol. 66, no. 3, pp. 1314–1321, Mar. 2019.

- [14] P.-C. Chen, Y.-C. Chiu, Z.-W. Zheng, C.-H. Cheng, and Y.-H. Wu, "Influence of plasma fluorination on p-type channel tin-oxide thin film transistors," *J. Alloys Compd.*, vol. 707, pp. 162–166, Jun. 2017.

- [15] J. Caraveo-Frescas, P. Nayak, H. Al-Jawhari, D. Granato, U. Schwingenschlögl, and H. Alshareef, "Record mobility in transparent p-type tin monoxide films and devices by phase engineering," *ACS Nano*, vol. 7, no. 6, pp. 5160–5167, May 2013.

- [16] H. Kawazoe, M. Yasukawa, H. Hyodo, M. Kurita, H. Yanagi, and H. Hosono, "P-type electrical conduction in transparent thin films of CuAlO<sub>2</sub>," *Nature*, vol. 389, no. 6654, pp. 939–942, 1997.

- [17] D. O. Scanlon, A. Walsh, B. J. Morgan, G. W. Watson, D. J. Payne, and R. G. Egdell, "Effect of Cr substitution on the electronic structure of CuAl<sub>1-x</sub>Cr<sub>x</sub>O<sub>2</sub>," *Phys. Rev. B, Condens. Matter Mater. Phys.*, vol. 79, Jan. 2009, Art. no. 035101.

- [18] K. Ueda *et al.*, "Epitaxial growth of transparent p-type conducting CuGaO<sub>2</sub> thin films on sapphire (001) substrates by pulsed laser deposition," *J. Appl. Phys.*, vol. 89, pp. 1790–1793, Feb. 2001.

- [19] H. Yanagi, T. Hase, S. Ibuki, K. Ueda, and H. Hosono, "Bipolarity in electrical conduction of transparent oxide semiconductor CuInO<sub>2</sub> with delafossite structure," *Appl. Phys. Lett.*, vol. 78, no. 11, pp. 1583–1585, 2001.

- [20] S. Ahmed, S. Khan, P. Ghosh, M. Mitra, and K. Chattopadhyay, "Effect of Al doping on the conductivity type inversion and electro-optical properties of SnO<sub>2</sub> thin films synthesized by sol-gel technique," *J. Sol-Gel Sci. Technol.*, vol. 39, no. 3, pp. 241–247, 2006.

- [21] J. Zhao, X. J. Zhao, J. M. Ni, and H. Z. Tao, "Structural, electrical and optical properties of p-type transparent conducting SnO<sub>2</sub>:Al film derived from thermal diffusion of Al/ SnO<sub>2</sub> Al multilayer thin films," *Acta Materialia*, vol. 58, pp. 6243–6248, Nov. 2010.

- [22] A. Tiburcio-Silver and A. Sánchez-Juárez, "SnO<sub>2</sub>:Ga thin films as oxygen gas sensor," *Mater. Sci. Eng. B, Solid-State Mater. Adv. Technol.*, vol. 110, pp. 268–271, Jul. 2004.

- [23] M. M. Bagheri-Mohagheghi and M. Shokooh-Saremi, "Electrical, optical and structural properties of Li-doped SnO<sub>2</sub> transparent conducting films deposited by the spray pyrolysis technique: A carrier-type conversion study," *Semicond. Sci. Technol.*, vol. 19, pp. 764–769, Jun. 2004.

- [24] M.-M. Bagheri-Mohagheghi and M. Shokooh-Saremi, "The influence of Al doping on the electrical, optical and structural properties of SnO<sub>2</sub> transparent conducting films deposited by the spray pyrolysis technique," *J. Phys. D, Appl. Phys.*, vol. 37, no. 8, pp. 1248–1253, 2004.

- [25] H. I. Bang, E. J. Yun, and B. S. Bae, "Effects of the post-annealing treatment on the properties of Ga-doped SnO<sub>x</sub> thin films," *J. Korean Phys. Soc.*, vol. 75, no. 8, pp. 561–568, 2019.

- [26] H. He, Z. Xie, Q. Li, J. Li, and Q. Zhang, "Novel p-type conductivity in SnO<sub>2</sub> thin films by Mg doping," *J. Alloys Compd.*, vol. 714, pp. 258–262, Aug. 2017.

- [27] F. E. Ghodsi and J. Mazloom, "Optical, electrical, and electrochemical behavior of p-type nanostructured SnO<sub>2</sub>:Ni (NTO) thin films," *J. Solid-State Electrochem.*, vol. 22, pp. 2375–2384, Mar. 2018.

- [28] A. Chaparadza and S. B. Rananavare, "Towards p-type conductivity in SnO<sub>2</sub> nanocrystals through Li doping," *Nanotechnology*, vol. 21, no. 3, 2010, Art. no. 035708.

- [29] D. P. Joseph, P. Renugambal, M. Saravanan, S. P. Raja, and C. Venkateswaran, "Effect of Li doping on the structural, optical and electrical properties of spray deposited SnO<sub>2</sub> thin films," *Thin Solid Films*, vol. 517, pp. 6129–6136, Sep. 2009.

- [30] J. S. Kim, R. H. Friend, and F. Cacialli, "Improved operational stability of polyfluorene-based organic light-emitting diodes with plasma-treated indium-tin-oxide anodes," *Appl. Phys. Lett.*, vol. 74, pp. 3084–3086, May 1999.

- [31] C. C. Wu, C. I. Wu, J. C. Sturm, and A. Kahn, "Surface modification of indium tin oxide by plasma treatment: An effective method to improve the efficiency, brightness, and reliability of organic light emitting devices," *Appl. Phys. Lett.*, vol. 70, pp. 1348–1350, Mar. 1997.

- [32] P.-C. Chen, Y.-C. Chiu, G.-L. Liou, Z.-W. Zheng, C.-H. Cheng, and Y.-H. Wu, "Performance enhancements in p-type Al-doped tinoxide thin film transistors by using fluorine plasma treatment," *IEEE Electron Device Lett.*, vol. 38, no. 2, pp. 210–212, Feb. 2017.

- [33] L. X. Qian and P. T. Lai, "Fluorinated InGaZnO thin-film transistor with HfLaO gate dielectric," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 363–365, Mar. 2014.

- [34] W. Wu, C. Lai, J. Wang, J. Chen, M. Ma, and T. Chao, "Highperformance HfO<sub>2</sub> gate dielectrics fluorinated by postdeposition CF<sub>4</sub> plasma treatment," *J. Electrochem. Soc.*, vol. 154, no. 7, pp. H561–H565, May 2007.

- [35] E. Davis and N. Mott, "Conduction in non-crystalline systems v. conductivity, optical absorption and photoconductivity in amorphous semiconductors," *Philos. Mag.*, vol. 22, no. 179, pp. 903–922, 1970.

- [36] T.-C. Fung *et al.*, "Two-dimensional numerical simulation of radio frequency sputter amorphous In-Ga-Zn-O thin-film transistors," *J. Appl. Phys.*, vol. 106, no. 8, Oct. 2009, Art. no. 084511.

- [37] A. H. T. Nguyen, M. C. Nguyen, J. Choi, S. Han, J. Kim, and R. Choi, "Electrical performance enhancement of p-type tin oxide channel thin film transistor using aluminum doping," *Thin Solid Films*, vol. 641, pp. 24–27, Nov. 2017.

- [38] N. Quackenbush *et al.*, "Origin of the bipolar doping behavior of SnO from X-ray spectroscopy and density functional theory," *Chem. Mater.*, vol. 25, no. 15, pp. 3114–3123, Jul. 2013.

- [39] A. Walsh and K. Butler, "Prediction of electron energies in metal oxides," Accounts Chem. Res., vol. 47, no. 2, pp. 364–372, 2014.

- [40] J. Robertson and S. J. Clark, "Limits to doping in oxides," *Phys. Rev. B, Condens. Matter Mater. Phys.*, vol. 83, no. 7, pp. 1–7, 2011.

- [41] S. B. Zhang, S.-H. Wei, and A. Zunger, "A phenomenological model for systematization and prediction of doping limits in II-VI and I-III-VI<sub>2</sub> compounds," *J. Appl. Phys.*, vol. 83, no. 6, p. 3192, 2012.

- [42] ATLAS Device Simulation Software User's Manual, Silvaco, Santa Clara, CA, USA, 2005.

- [43] K. Winer, "Defects in hydrogenated amorphous silicon," Annu. Rev. Mater. Sci., vol. 21, no. 1, pp. 1–21, Aug. 1991.

- [44] P.-M. Lee, Y.-S. Liu, L. Villamagua, A. Stashans, M. Carini, and C.-Y. Liu, "Experimental observation and computer simulation of Al/Sn substitution in p-type aluminum nitride-doped tin oxide thin film," J. Phys. Chem. C, vol. 120, no. 8, pp. 4211–4218, 2016.

- [45] H. Luo, L. Y. Liang, H. T. Cao, Z. M. Liu, and F. Zhuge, "Structural, chemical, optical, and electrical evolution of SnOx films deposited by reactive RF magnetron sputtering," ACS Appl. Mater. Interfaces, vol. 4, no. 10, pp. 5673–5677, 2012.

- [46] Y. Kaneko, Y. Tanaka, and T. Tsukada, "A new address scheme to improve the display quality of a-Si TFT/LCD panels," *IEEE Trans. Electron Devices*, vol. 36, no. 12, pp. 2949–2952, Dec. 1989.

- [47] H. Lee, C.-S. Chiang, and J. Kanicki, "Dynamic response of normal and corbino a-Si:H TFTs for AM-OLEDs," *IEEE Trans. Electron Devices*, vol. 55, no. 9, pp. 2338–2347, Sep. 2008.

- [48] Y. Kim, Y. Kim, and H. Lee, "A novel p-type LTPS TFT pixel circuit compensating for threshold voltage and mobility variations," J. Display Technol., vol. 10, no. 12, pp. 995–1000, Dec. 2014.

- [49] C.-L. Lin, C.-C. Hung, W.-Y. Chang, M.-H. Cheng, P.-Y. Kuo, and Y.-C. Chen, "Voltage driving scheme using three TFTs and one capacitor for active-matrix organic light-emitting diode pixel circuits," *J. Display Technol.*, vol. 8, no. 10, pp. 602–608, Oct. 2012.

- [50] B.-D. Choi and O.-K. Kwon, "Line time extension driving method for a-Si TFT-LCDs and its application to high definition televisions," *IEEE Trans. Consum. Electron.*, vol. 50, no. 1, pp. 33–38, Feb. 2004.

- [51] M. Takabatake, M. Tsumura, and Y. Nagae, "Consideration of feed-through voltage in Amorphous-Si TFT's," *IEEE Trans. Electron Devices*, vol. 40, no. 10, pp. 1866–1870, Oct. 1993.

- [52] H. Aoki, "Dynamic characterization of a-Si TFT-LCD pixels," *IEEE Trans. Electron Devices*, vol. 43, no. 1, pp. 31–39, Jan. 1996.

**KADIYAM RAJSHEKAR** received the M.Tech. degree in VLSI design from the Vellore Institute of Technology, Vellore, India, in 2011, where he is currently pursuing the Ph.D. degree in electronics engineering. He is also a recipient of Senior Research Fellowship from Council of Scientific and Industrial Research, Government of India. His research includes thin film transistor and semiconductor device modeling.

HSIAO-HSUAN HSU received the B.S. degree from the Department of Material Science and Engineering, National Chiao Tung University (NCTU), Taiwan, and the M.S./Ph.D. degrees from the Department of Electronics Engineering, NCTU. She was with the Green Energy and Environment Research Laboratory, Industrial Technology Research Institute and Taiwan Semiconductor Manufacturing Company Ltd., Taiwan, from 2008 to 2016. She is currently an Assistant Professor with the Department of

Materials and Mineral Resources Engineering, National Taipei University of Technology, Taiwan. She has published 30 journal papers, 24 conference papers, and nine patents. Her research is focus on metal-oxide semiconductors and thin-film transistors, thermoelectric, and ferroelectric/resistive materials and devices.

**P. SATHYANARAYANAN** received the Ph.D. degree in physics from the Nanostructured Physics Group, Hasselt University, Belgium. He works as an Assistant Professor with the Centre for Nanotechnology Research, VIT University (Vellore Campus), Vellore. He had been working as a Postdoctoral Researcher on nanofabrication of molecular structures through nano-chemistry with the University of Lille, France. He has an expertise on ultrafast synthesis of nearly mono-disperse well-ordered and well separated inorganic nanos-

tructures. He has published more than ten papers in reputed journals, which includes Angewandte Chemie, Nanoscale, ACS Applied Materials and Interfaces, Journal of Materials Chemistry C, Advanced Materials Interfaces.

**V. VELMURUGAN** (Member, IEEE) is an Associate Professor with the Centre for Nanotechnology Research, VIT University, Vellore, and has 15 years of teaching and research experience in the field of Nanotechnology. His research interests include optical interference lithography for sub-wavelength structures, nanomaterials for environmental applications, modeling, simulation of MEMS, and nanosensors.

**CHUN-HU CHENG** (Member, IEEE) received the Ph.D. degree from the Department of Electronics Engineering, National Tsing Hua University. He is currently an Associate Professor with the Department of Mechatronic Engineering, National Taiwan Normal University. His current research interests include the low-power CMOS devices (NCFET, GAA FET), fast low-power NVMs (RRAM, FeRAM) and high-mobility metal-oxide TFTs. He has published ten articles in IEEE IEDM and VLSI conferences, focused on novel

device technology developments of RRAM, FeRAM, and NCFET. He has published 136 journals and 101 conference papers.

**KOPPOLU UMA MAHENDRA KUMAR** received the Ph.D. degree from the University of Hyderabad, India. His postdoctoral work is comprised of EXAFS of metalloenzymes with the University of Gerogia, USA. He is an Assistant Professor with the Departtment of Physics, Vellore Institute of Technology, India. To his credit there are 9 research papers. His current research interest is in core level spectroscopy of soft condensed matter and biochemistry.

**D. KANNADASSAN** received the Ph.D. degree from the School of Electronics Engineering, Vellore Institute of Technology, Vellore, where he is an Associate Professor with the Centre for Nanotechnology Research. He has published 12 articles in reputed journals, a book chapter and five conference papers in microelectronics and microwave resonators. His current research interests are transparent TFTs and graphene FETs for future technologies.