# Physical Parameter-Based SPICE Models for InGaZnO Thin-Film Transistors Applicable to Process Optimization and Robust Circuit Design

Dae Hwan Kim, *Member, IEEE*, Yong Woo Jeon, Sungchul Kim, Yongsik Kim, Yun Seop Yu, *Member, IEEE*, Dong Myong Kim, *Member, IEEE*, and Hyuck-In Kwon

Abstract—In this letter, we show that the physics-based equation that was derived for amorphous oxide semiconductor (AOS) thin-film transistors (TFTs) in our previous work can be successfully incorporated into the SPICE model via Verilog-A. The proposed model and extracted SPICE parameters successfully reproduce the measured current-voltage characteristics of amorphous indium-gallium-zinc-oxide (a-IGZO) TFTs and the load line diagram of a-IGZO TFT inverters. The main advantage of our model is that each parameter has its physical meaning and most of them can be related with the fabrication conditions of AOS TFTs. To show the advantage of the proposed models and extracted SPICE parameters more clearly, we investigate the effect of ionized donor concentration  $(N_{\mathrm{D}}^+)$  on the inverter circuit operation and determine the optimum value of  $N_{\rm D}^+$  and device dimensions considering the tradeoff between the power consumption and the output swing in a-IGZO inverters. The proposed physics-based SPICE model via Verilog-A is expected to play a significant role in the process optimization and circuit design with AOS TFTs.

*Index Terms*—Amorphous indium–gallium–zinc-oxide (a-IGZO), amorphous oxide semiconductor (AOS), inverter, SPICE, thin-film transistor (TFT), Verilog-A.

#### I. INTRODUCTION

**D** EMONSTRATION OF amorphous indium–gallium– zinc-oxide (a-IGZO) thin-film transistor (TFT)-based analog and digital circuits has been extensively documented in recent years [1], [2]. This activity reflects the level of maturity achieved in the a-IGZO TFT fabrication technology. In most of previous works [1], [2], to simulate the circuit operation with a SPICE tool, the Rensselaer Polytechnic Institute (RPI) TFT model [3], [4] was used with the parameters extracted from the current–voltage (I-V) characteristics of a-IGZO TFTs. The

Manuscript received September 22, 2011; accepted October 7, 2011. Date of publication November 8, 2011; date of current version December 23, 2011. This work was supported by MEST through the Mid-career Researcher Program under NRF Grants 2010-0000828 and 2011-0016971. The CAD software was supported by the IC Design Education Center. The review of this letter was arranged by Editor A. Nathan.

D. H. Kim, Y. W. Jeon, S. Kim, Y. Kim, and D. M. Kim are with the School of Electrical Engineering, Kookmin University, Seoul 136-702, Korea.

Y. S. Yu is with the Department of Information and Control Engineering, Electronic Technology Institute, Hankyong National University, Anseong 456-749, Korea.

H.-I. Kwon is with the School of Electrical and Electronics Engineering, Chung-Ang University, Seoul 156-756, Korea (e-mail: hyuckin@cau.ac.kr).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2011.2172184

RPI TFT model and extracted parameters have shown that they are useful in the prediction of a-IGZO TFT-based circuit behaviors. Although the RPI model is a powerful model based on the parameters with a physical meaning, it can be insufficient in simulating the unusual characteristics of amorphous oxide semiconductor (AOS) TFTs considering that it has been mainly derived from the amorphous silicon (a-Si) TFT. In this letter, we show that the physical parameter-based equation that was derived for AOS TFTs in our previous paper [5] can be successfully incorporated into the SPICE model via Verilog-A. We have shown that the proposed model can simulate the operational behavior of AOS TFTs in various bias conditions and reflect the peculiar electrical characteristics of AOS TFTs including the active layer thickness dependence of the electrical behaviors [5]. Based on the SPICE simulation with physicsbased and process-controlled parameters, the ionized donor concentration dependence of the a-IGZO TFT inverter behavior is predicted for the first time.

#### II. PHYSICS-BASED I-V MODEL FOR AOS TFTs

In our previous work [5], we proposed the physics-based I-V model for AOS TFTs with concrete techniques for parameter extraction as

$$I_{DS} = q\mu_{Band} \frac{W}{L}$$

$$\times \int_{V_S}^{V_S+V_D} \int_{\phi_B}^{\phi_S} \frac{Q_{\text{free}}(\phi, V_{CH}(y))}{Q_{\text{free}}(\phi, V_{CH}(y)) + Q_{loc}(\phi, V_{CH}(y))}$$

$$\times \frac{n_{\text{free}}(\phi, V_{CH}(y))}{E_{AOS}(\phi, V_{CH}(y))} d\phi dV_{CH}(y) \quad (1)$$

where q is the electronic charge,  $\mu_{\text{Band}}$  is the conduction band mobility, W is the channel width, L is the channel length,  $V_{\text{S}}$  is the source voltage,  $V_{\text{D}}$  is the drain voltage,  $\phi_{\text{S}}$  is the surface potential,  $\phi_{\text{B}}$  is the back potential,  $Q_{\text{free}}$  is the free charge density per unit area,  $Q_{\text{loc}}$  is the localized charge density per unit area which can be obtained from the extracted acceptorlike and donorlike density of states (DOS),  $n_{\text{free}}$  is the free electron density, and  $E_{\text{AOS}}$  is the surface electric field. Recently, Lee *et al.* [6] have reported the percolation conduction as a dominant conduction mechanism at high gate-to-source voltages ( $V_{\text{GS}}$ s) in AOS TFTs. However, the trap-limited

| parameter                                               | value              |                      |                                       | value              |                    |                                                                         |                    |                                           |                    |

|---------------------------------------------------------|--------------------|----------------------|---------------------------------------|--------------------|--------------------|-------------------------------------------------------------------------|--------------------|-------------------------------------------|--------------------|

|                                                         | Load               | Driver               | parameter                             | Load               | Driver             | parameter                                                               | value              | parameter                                 | value              |

| N <sub>TA</sub><br>[eV <sup>-1</sup> cm <sup>-3</sup> ] | 8×10 <sup>18</sup> | 7.5×10 <sup>18</sup> | N <sub>D</sub><br>[cm <sup>-3</sup> ] | 5×10 <sup>16</sup> | 5×10 <sup>16</sup> | $\begin{bmatrix} N_{\rm TD} \\ [\rm eV^{-1} \rm cm^{-3}] \end{bmatrix}$ | 1×10 <sup>20</sup> | N <sub>C</sub><br>[cm <sup>-3</sup> ]     | 6×10 <sup>18</sup> |

| kT <sub>TA</sub><br>[eV]                                | 0.067              | 0.08                 | V <sub>FB</sub><br>[V]                | 0.13               | 0.067              | kT <sub>TD</sub><br>[eV]                                                | 0.06               | $\mu_{\text{Band}}$ [cm <sup>2</sup> /Vs] | 23.5               |

| $[eV^{-1}cm^{-3}]$                                      | 5×10 <sup>16</sup> | 3×10 <sup>16</sup>   | W<br>[µm]                             | 50                 | 175                | $[eV^{-1}cm^{-3}]$                                                      | 1×10 <sup>18</sup> | T <sub>OX</sub><br>[nm]                   | 100                |

| kT <sub>DA</sub><br>[eV]                                | 0.8                | 0.8                  | <i>L</i><br>[μm]                      | 30                 | 30                 | kT <sub>DD</sub><br>[eV]                                                | 0.55               | T <sub>IGZO</sub><br>[nm]                 | 50                 |

$\begin{array}{c} \text{TABLE} \quad \text{I} \\ \text{SPICE Model Parameters of the Load and Driver TFTs} \end{array}$

conduction was assumed because of the low  $V_{\rm GS}$ 's in our model, and it showed good agreement with the measured results. Compared with the previously reported a-Si TFT models, the proposed model was proved to be more effective in reproducing the electrical characteristics of AOS TFTs where the free carrier charge can be comparable with or larger than the localized one out of the induced charge.

## III. EXPERIMENTS, RESULTS, AND DISCUSSIONS

For this research, the enhancement load-type a-IGZO TFTbased inverter was integrated on a highly doped silicon substrate with a staggered bottom gate structure. The device structure and detailed process sequences are the same as that in [5]. The pads of all nodes in two TFTs were prepared in the inverter layout in order to separately extract the model parameters of the load and driver TFTs.

Table I summarizes the extracted parameters for the SPICE simulation in each TFT of the inverter based on the physical parameter-based equation for AOS TFTs. The parameters of  $T_{\text{ox}}$ ,  $T_{\text{IGZO}}$ ,  $N_{\text{TA}}$ ,  $kT_{\text{TA}}$ ,  $N_{\text{DA}}$ ,  $kT_{\text{DA}}$ ,  $N_{\text{TD}}$ ,  $kT_{\text{TD}}$ ,  $N_{\text{DD}}$ ,  $kT_{\rm DD}$ ,  $V_{\rm FB}$ ,  $N_{\rm C}$ , and  $N_{\rm D}^+$  in Table I represent the thickness of the gate oxide, thickness of a-IGZO active thin film, intercept density at the conduction band edge  $(E_{\rm C})$  of the acceptorlike exponential tail states, characteristic decay energy of the acceptorlike exponential tail states, intercept density at  $E_{\rm C}$  of the acceptorlike exponential deep states, characteristic decay energy of the acceptorlike exponential deep states, intercept density at the valance band edge  $(E_V)$  of the donorlike exponential tail states, characteristic decay energy of the donorlike exponential tail states, intercept density at  $E_{\rm V}$  of the donorlike exponential deep states, characteristic decay energy of the donorlike exponential deep states, flat-band voltage, conduction band effective DOS, and ionized donor concentration, respectively.

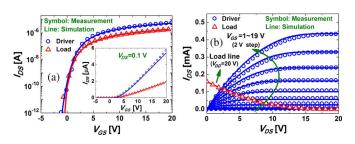

Fig. 1(a) and (b) depict the transfer curves and the load line diagram obtained from the measured and SPICE-simulated data in both TFTs. The results show that the SPICE-simulated transfer curves and the load line diagram are in good agreement with the measured ones, which verifies that the proposed physics-based model and the extracted model parameters are reasonable and very efficient in predicting the behavior of the a-IGZO TFT-based circuits.

To show the usefulness of the proposed models and extracted SPICE parameters more clearly, we investigate the effect of  $N_{\rm D}^+$  on the inverter operation and determine the optimum value of  $N_{\rm D}^+$  and  $W_{\rm load}/W_{\rm driver}$  considering the tradeoff between the

Fig. 1. (a) Transfer curves and (b) load line diagram obtained from the measured and SPICE-simulated data in both TFTs of the a-IGZO inverter. The inset of Fig. 1(a) shows the transfer characteristic in the linear scale.

power consumption and the output swing in a-IGZO inverters. The ionized donor concentration  $(N_D^+)$  is one of the most important physical parameter which can be managed by controlling the magnitude of oxygen vacancy  $(V_o)$  in amorphous oxide materials. Unlike the fitting parameter-based models, each parameter in our model has its physical meaning, which is the important advantage of our model. For example, the  $N_D^+$  can be increased by reducing the partial pressure of oxygen during the deposition process of amorphous oxide thin films in AOS TFTs. Therefore, by using the proposed models and extracted SPICE parameters, we can easily predict the effect of TFT-fabrication conditions on the AOS TFT-based circuit behaviors.

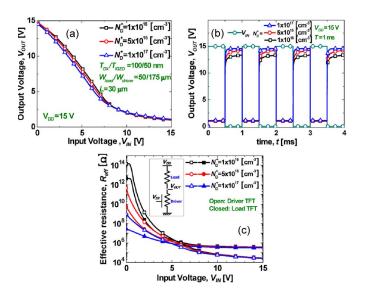

Fig. 2(a) and (b) shows the voltage transfer curves (VTCs) and time transient characteristics of the a-IGZO inverter simulated using the extracted SPICE parameters with various values of  $N_{\rm D}^+$ . The results show that the variation of  $N_{\rm D}^+$  much affects the inverter behaviors. As the value of  $N_{\rm D}^+$  increases, the output voltage  $(V_{OUT})$  decreases at low input voltages  $(V_{IN}$ 's) in the VTC, and the output peak-to-peak voltage  $(V_{OUT,P-P})$ increases in the transient characteristics. This phenomenon can be explained based on the modulation of channel resistance with a variation of  $N_{\rm D}^+$  in both TFTs. As well known, the increase of  $N_{\rm D}^+$  or  $V_{\rm o}$  causes the negative shift of the threshold voltage in AOS TFTs, so the channel resistance decreases in both TFTs with an increase of  $N_{\rm D}^+$ . In Fig. 2(a), the high  $V_{\rm OUT}$ is close to the supply voltage  $(V_{DD})$  in all circuits, which is due to the nonnegligible subthreshold current of the load TFT. Because  $\phi_{\rm S}$  is calculated by the numerical integration along the channel depth in our model, it can reflect the residual channel current due to the undepleted back surface in AOS TFTs [5].

Fig. 2(c) depicts the simulated channel resistance of both TFTs with various values of  $N_{\rm D}^+$ . As expected, the channel resistance decreases with an increase of  $N_{\rm D}^+$  in both TFTs.

Fig. 2. Simulated  $N_{\rm D}^+$ -dependences of (a) VTC, (b) transient characteristics, and (c) effective channel resistance of load and driver TFTs in inverters.

Fig. 2(c) also shows that the degree of the channel resistance decrease is more prominent in the driver TFTs and at low  $V_{\rm IN}$ 's. Considering that the decrease of the channel resistance in the driver TFT causes the improvement of the pull-down characteristics of the inverter and the reduction of resistance–capacitance delay in the pull-down path, the decrease of  $V_{\rm OUT}$  at low  $V_{\rm in}$ 's in the VTC and the increase of  $V_{\rm OUT,P-P}$  in the transient characteristics with an increase of  $N_{\rm D}^+$  can be considered as a reasonable result. During the transient simulation, we included a constant capacitance of 13.9 pF in the output node, which was calculated considering all the capacitances from the load TFT, driver TFT, and the external loads. The capacitance from the external load is included to imitate the real operation condition of the inverter circuits.

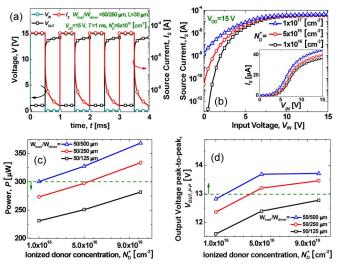

Although the result in Fig. 2 shows the effect of  $N_{\rm D}^+$  on the inverter operation, we also have to consider the power consumption  $(P_{\text{total}})$  for the circuit optimization. Fig. 3(a) shows the  $V_{\rm IN}$ ,  $V_{\rm OUT}$ , and the short circuit current  $(I_{\rm S})$  in the transient characteristics of the a-IGZO TFT inverter, and Fig. 3(b) depicts the  $N_{\rm D}^+$ -dependence of  $I_{\rm S}$  as a function of  $V_{\rm IN}$ . The result in Fig. 3(b) clearly shows that  $I_{\rm S}$  increases with an increase of  $N_{\rm D}^+$ , which represents that the higher power consumption is required in the inverter circuits with higher  $N_{\rm D}^+$ -TFTs. If we compare this result with that of Fig. 2(b), we get to know that there is a tradeoff between the magnitude of  $V_{\rm OUT,P-P}$  and the power consumption regarding the  $N_{\rm D}^+$ , so it is necessary to find out the optimum value of  $N_{\rm D}^+$ . Fig. 3(c) and (d) shows the simulated values of  $P_{\text{total}}$  and  $V_{\text{OUT,P-P}}$  in the a-IGZO inverters with various values of  $N_{\rm D}^+$  and  $W_{\rm load}/W_{\rm driver}$ . If we assume the figure-of-merit (FOM) of the a-IGZO inverter as  $P_{\rm total} < 300 \ \mu W$  and  $V_{\rm OUT,P-P} > 13$  V, the results in Fig. 3(c) and (d) show that the value of  $N_{\rm D}^+$  and  $W_{\rm load}/W_{\rm driver}$  should be decided to be  $4.0 \times 10^{16} < N_{\rm D}^+ < 5.5 \times 10^{16} \ {\rm cm}^{-3}$ and 50/250  $\mu$ m to fulfill the requirement. The procedures and results in Figs. 2 and 3 confirm the usefulness of our model and parameters in the process optimization as well as the circuit design with AOS TFTs.

Fig. 3. (a) Simulated  $V_{\rm IN}$ ,  $V_{\rm OUT}$ , and  $I_{\rm S}$  of transient characteristics and (b)  $N_{\rm D}^+$ -dependent short circuit current  $I_{\rm S}$  as the function of  $V_{\rm IN}$  in a-IGZO inverter. (c) Calculated  $P_{\rm total}$  with the change of  $N_{\rm D}^+$  and/or  $W_{\rm load}/W_{\rm driver}$  and (d) simulated  $V_{\rm OUT,P-P}$  with the change of  $N_{\rm D}^+$  and/or  $W_{\rm load}/W_{\rm driver}$  in the inverter.

## IV. CONCLUSION

In this letter, we show that the physics-based equation that was derived for AOS TFTs in our previous paper [5] can be successfully incorporated into the SPICE model via Verilog-A. The derived equation shows good compatibility with the SPICE model. To confirm the usefulness of the model in a systematic optimization of the process/circuit design parameters in AOS TFTs more clearly, we simulate the effect of  $N_{\rm D}^+$  on the inverter operation and determine the optimum value of  $N_{\rm D}^+$  and  $W_{\rm load}/W_{\rm driver}$  considering the tradeoff between the power consumption and the output swing in a-IGZO inverters. We expect that the proposed SPICE model will be very useful in the circuit design for innovative AOS TFT-based applications.

### REFERENCES

- C. Chen, K. Abe, T.-C. Fung, H. Kumomi, and J. Kanicki, "Amorphous In-Ga-Zn-O thin-film transistor current-scaling pixel electrode circuit for active-matrix organic light-emitting displays," *Jpn. J. Appl. Phys.*, vol. 48, no. 3, pp. 03B 025-1–03B 025-7, Mar. 2009.

- [2] A. Jamshidi-Roudbari, S. A. Khan, and M. K. Hatalis, "High-frequency half-bit shift register with amorphous-oxide TFT," *IEEE Electron Device Lett.*, vol. 31, no. 4, pp. 320–322, Apr. 2010.

- [3] M. S. Shur, H. C. Slade, M. D. Jacunski, A. A. Owasu, and T. Ytterdal, "SPICE models for amorphous silicon and polysilicon thin film transistors," *J. Electrochem. Soc.*, vol. 144, no. 8, pp. 2833–2839, Aug. 1997.

- [4] A. Cerdeira, M. Estrada, R. Garcia, A. O.-Conde, and F. J. G. Sanchez, "New procedure for the extraction of basic a-Si:H TFT model parameters in the linear and saturation regions," *Solid-State Electron.*, vol. 45, no. 7, pp. 1077–1080, Jul. 2001.

- [5] Y. W. Jeon, S. Kim, S. Lee, D. M. Kim, D. H. Kim, J. Park, C. J. Kim, I. Song, Y. Park, U.-I. Chung, J.-H. Lee, B. D. Ahn, S. Y. Park, J.-H. Park, and J. H. Kim, "Subgap density of states-based amorphous oxide thin film transistor simulator (DeAOTS)," *IEEE Trans. Electron Devices*, vol. 57, no. 11, pp. 2988–3000, Nov. 2010.

- [6] S. Lee, K. Ghaffarzadeh, A. Nathan, J. Robertson, S. Jeon, C. Kim, I.-H. Song, and U.-I. Chung, "Trap-limited and percolation conduction mechanisms in amorphous oxide semiconductor thin film transistors," *Appl. Phys. Lett.*, vol. 98, no. 20, pp. 203 508-1–203 508-3, May 2011.