# Physical unbiased generation of random numbers with coupled resistive switching devices

S. Balatti, *Student Member, IEEE*, S. Ambrogio, *Student Member, IEEE*, R. Carboni, V. Milo, Z.-Q. Wang, A. Calderoni, N. Ramaswamy, *Senior Member, IEEE*, and D. Ielmini, *Senior Member, IEEE*

*Abstract*—Resistive switching memory (RRAM) is currently under consideration for fast nonvolatile memory thanks to its relatively low cost and high performance. A key concern for RRAM reliability is stochastic switching, which impacts the operation of the digital memory due to distribution broadening. On the other hand, stochastic behaviors are enabling mechanisms for some computing tasks, such as physical unclonable functions (PUF) and random number generation (RNG). Here we present new circuit blocks for physical RNG, based on the coupling of 2 RRAM devices. The 2-resistance (2R) scheme allows to overcome the need of probability tracking, where the operation voltage must be tuned to adjust the generation probabilities of 0 and 1. Probability tests are proven successful for one of the 3 proposed schemes.

Keywords: Resistive switching memory (RRAM), Random number generation (RNG), memory reliability.

#### I. INTRODUCTION

Random number generation is essential for generating random encryption keys for secure transmission protocols [1]. The pervasiveness of internet-based communication and the need to protect data from eavesdropping, raises the need for compact random number generator (RNG) circuits capable of generating true random numbers with high entropy quality and high throughput. To generate true random numbers, which do not rely on deterministic algorithms and are totally unpredictable, it is important to identify a convenient onchip entropy source and design the corresponding circuit for generating the random bit stream with high throughput and stability. Previous approaches to true/physical RNG include random telegraph noise (RTN) in dielectrics [2] or in resistive switching memory (RRAM) [3]. RTN appears as a random fluctuation of current, or resistance, between 2 or more levels, as a result of the random charging/discharging of a bistable defects [4]. However, RTN is difficult to control in terms

S. Balatti was with the Dipartimento di Elettronica e Informazione and Italian Universities Nanoelectronics Team (IU.NET), Politecnico di Milano, piazza L. da Vinci 32, 20133 Milano, Italy (E-mail: simone.balatti@polimi.it). He is now with Intermolecular Inc., 3011 North First Street, San Jose, CA 95134, USA (E-mail: simone.balatti@intermolecular.com)

S. Ambrogio, R. Carboni, V. Milo, Z.-Q. Wang and D. Ielmini are with the Dipartimento di Elettronica, Informazione e Bioingegneria and Italian Universities Nanoelectronics Team (IU.NET), Politecnico di Milano, piazza L. da Vinci 32, 20133 Milano, Italy. (E-mail: stefano.ambrogio@polimi.it, roberto.carboni@polimi.it, valerio.milo@polimi.it, zhongqiang.wang@polimi.it and daniele.ielmini@polimi.it)

A. Calderoni and N. Ramaswamy are with Micron Technology Inc., Boise, ID 83707 USA (E-mail: acaldero@micron.com and dramaswamy@micron.com)

This work was supported in part by the ERC Consolidator Grant No. 648635 "Resistive-switch computing Beyond CMOS". of both amplitude and frequency, thus raising the need for dedicated techniques for RTN initiation. Also, RTN has been shown to be unstable in RRAM, where the current fluctuation at a given bias can show unpredictable onset and interruption [5]. Other schemes relying on physical fluctuation phenomena are therefore under scrutiny for efficient and stable RNG.

Recently, novel RNG concepts based on the switching variability in low-voltage memory technologies such as spintransfer-torque (STT) magnetic memory (MRAM) [6], [7] and RRAM [8], [9] have been proposed. Switching variation in RRAM was similarly applied to developed physical unclonable function (PUF) [10] and to enhance learning in neuromorphic circuits [11]. For RNG, one can take advantage of the stochastic variation of a switching parameter, such as the voltage  $V_{set}$  for the set transition from high to low resistance [12]. Application of a voltage close to the median value in the distribution of V<sub>set</sub> statistically results in a random set transition occurring randomly only in a fraction of attempts. A key problem in this approach, however, is the need for a careful tracking of the applied voltage, which must be exactly centered in the median of the  $V_{set}$  distribution to ensure perfect balance between 0s and 1s [12]. For this purpose, real-time voltage tracking techniques must be used for compensating 0 and 1 probabilities [7].

This work presents new solutions for RRAM-based unbiased RNGs overcoming the need for probability tracking. These novel approaches rely on stochastic switching in 2 coupled RRAM devices, driven by the same voltage pulse and having different (*e.g.*, parallel or series) configurations. Unbiased RNG relies on either a comparison between the resistance levels after independent switching, or on alternative switching in series/parallel RRAM, similar to the operation of RRAM logic gates [13]. The new RNG schemes are finally supported by presenting and discussing randomness tests.

#### II. RRAM SWITCHING CHARACTERISTICS

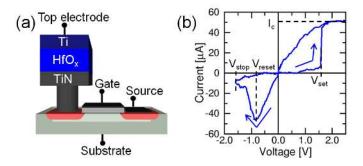

Devices used in our RNG circuits were bipolar RRAMs consisting of a Si-doped  $HfO_2$  switching layer with TiN bottom electrode (BE) and Ti top electrode (TE), acting as oxygen exchange layer for defect generation at the TE side [4], [14]. Fig. 1 shows the RRAM device stack (a) and the corresponding I-V characteristics (b). One-transistor/one-resistor (1T1R) structures were used for proper control of the resistance level by limiting the current of the integrated select transistor [15]. Application of a positive voltage causes set transition from high-resistance state (HRS) to low-resistance

Fig. 1. Schematic of the 1T1R structure used in this work (a) and corresponding I-V curve providing definition of the set voltage  $V_{set}$ , the compliance current  $I_C$ , the reset voltage  $V_{reset}$ , and the stop voltage  $V_{stop}$  (b). The RRAM stack includes a Si-doped HfO<sub>x</sub> switching layer, a Ti top electrode and a TiN bottom electrode.

state (LRS) in correspondence of  $V_{set}$ , while application of a negative voltage causes the reset transition from LRS to HRS starting at a reset voltage  $V_{reset}$ . A compliance current  $I_C = 50 \ \mu$ A was used during the set transition by applying a relatively small gate voltage. A maximum negative voltage  $V_{stop}$  was applied during the reset sweep. Triangular pulses of width  $t_P = 1$  ms width were used for set and reset in Fig. 1 and throughout this work. The relatively long pulse was needed to overcome the parasitic capacitance inducing delays in the custom board used for experimental verification. We applied a suitably low voltage for set and reset to avoid any degradation in the device during cycling.

# III. RRAM-BASED RNG CIRCUITS

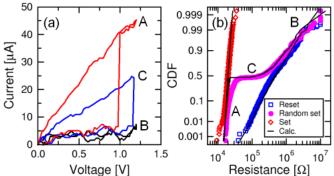

RRAM is affected by stochastic switching, where the switching parameters randomly change from cycle to cycle [16], [17]. The resistance R in both HRS and LRS, the set voltage Vset, and the reset voltage Vreset were shown to vary during cycling depending on the compliance current  $I_C$  [18] and the stop voltage  $V_{stop}$  [17]. These statistical fluctuations were explained by the random formation and rupture of the conductive filament (CF) and the varying number of defects within the CF in both HRS and LRS [18]. While variability is a considerable concern for digital memory applications, where distinct set/reset distributions should be ensured, random variations of V<sub>set</sub> were previously used to generate random bits [12]. In fact, the application of a voltage  $V_A$ close to the median value of V<sub>set</sub> to HRS results in random set as shown in Fig. 2(a). The device undergoes set transition if  $V_A > V_{set}$  (case A in Fig. 2(a)), while no change is seen if  $V_A < V_{set}$  (case B). This leads to a bimodal distribution of R measured after random set as shown in Fig. 2(b). Between the HRS and LRS sub-sets in the bimodal distribution, there is an intermediate case C in Fig. 2(a) where set transition took place only partially due to insufficient time to complete the CF formation [12]. Simulation results are provided in Fig. 2(b). The LRS distribution is modeled by a lognormal distribution of resistance with median value 20 k $\Omega$  and a relatively small standard deviation  $\sigma(\log R) = 8.64 \times 10^{-2}$ . The HRS distribution is modeled as the sum of a LRS resistance and a lognormal distribution with median 480 k $\Omega$  and standard deviation  $\sigma(\log R) = 0.82$ . The series combination of LRS and

Fig. 2. Measured I-V characteristics during random set operation (a) and cumulative distributions of resistance after reset, after set and after random set at  $V_A = 1.2$  V. Random-set operation can results in either set transition (A) or no transition (B). Partial set transition (C) can also be observed.

HRS allows to better describe the low-resistance portion of the HRS distribution, where the resistance of the incompletelydissolved filament and of the top and bottom interface resistances cannot be neglected. The random set distribution was obtained by combining randomly selected HRS and LRS resistance with equal probabilities of 50%, resulting in the bimodal distribution in Fig. 2(b). The random set operation on HRS can be used as entropy source for true RNG, however achieving an unbiased RNG with equal probabilities of 0 and 1 in Fig. 2(b) requires careful adjustment of the voltage  $V_A$ in correspondence of the median of the Vset distribution. This can be obtained by real-time probability tracking techniques [7], however at the expense of a higher circuit and algorithm complexity. Also, Vset might decrease during cycling due to degradation and wear out of the CF region in the RRAM device [19], which further supports the need for voltage tracking techniques. To avoid this issue, we redesign RNG blocks based on random switching in 2 coupled RRAM devices, with the purpose of compensating the unbalanced generation and achieve unbiased RNG. RRAM devices can be coupled in either series or parallel configurations, while the source of entropy is the variability of either set or reset transitions. As a result, 3 RNG schemes with coupled RRAMs are developed, as detailed in the following.

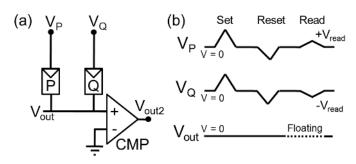

## A. Parallel reset

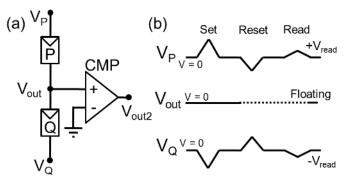

Fig. 3(a) shows the parallel-reset RNG circuit, where two RRAM cells (P and Q) are connected in parallel. 1T1R structures were used for P and Q during the experimental demonstration of the RNG operation. Fig. 3(b) shows the waveforms for the TE voltage  $V_P$  of device P, the TE voltage of device Q, and the voltage  $V_{out}$  of the common node between P and Q in Fig. 3(a). The RNG cycle consists of 3 phases, namely (i) application of a positive voltage across P and Q to induce set transition, (ii) application of a negative voltage to induce reset transition, and (iii) read, where the voltage divider of P and Q is evaluated by probing the potential  $V_{out}$  with  $V_P = +V_{read}$  and  $V_Q = -V_{read}$ . Triangular pulses with 1 ms duration were applied for set, reset and read. Note that voltages across devices P and Q are independently applied during set and reset with no interaction between the two cells,

Fig. 3. Parallel reset circuit (a) and sequence of applied signals (b). Starting from P and Q in HRS, cells are firstly independent set, then reset and finally read using voltage-divider configuration. The analogical comparator (CMP) is used to digitally regenerate  $V_{out}$ .

Fig. 4. Cumulative distributions of resistance after set and after reset for cells P and Q (a), corresponding distributions of  $V_{out}$  and  $V_{out2}$  with and without comparator (b), measured  $V_{out}$  and  $V_{out2}$  as a function of RNG cycle (c) and corresponding PDF (d).

thus set and reset transitions both occur independently in this scheme. As a result of the relatively large statistical variation of HRS resistance [14], [17],  $V_{out}$  randomly varies from cycle to cycle, thus serving as the output bit value in the RNG. HRS resistance variation serves as the entropy source in this scheme.

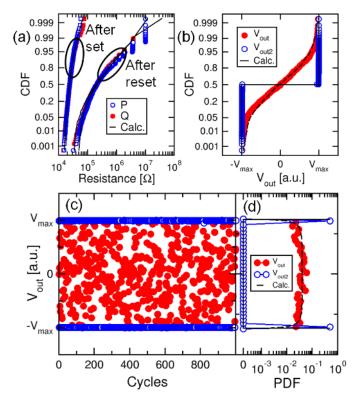

Fig. 4(a) shows the cumulative distributions of P resistance  $R_P$  and Q resistance  $R_Q$ , measured after set and reset, together with calculated results obtained as in Fig. 2(b). RNG was tested along 1000 cycles which provides sufficient statistical accuracy with negligible device degradation. Distributions  $R_P$  and  $R_Q$  are almost identical in both LRS and HRS, which is a key to achieve true and unbiased RNG. Fig. 4(b) shows

the resulting experimental and calculated distributions of  $V_{out}$ obtained during read, indicating a bimodal shape with 50% transition probability. The bimodal distribution was improved in our experimental setup by introducing an analog comparator (CMP) in Fig. 3(a). The CMP can be replaced by one or more integrated CMOS inverters in an integrated circuit to decrease the occupied area on the chip [12]. The distribution of the CMP output voltage Vout2 shows a bimodal distribution with abrupt transition at 50%. Fig. 4(c) shows the measured  $V_{out}$ and Vout2 along 1000 cycles during RNG operation, while Fig. 4(d) shows the corresponding probability density function (PDF) of Vout and Vout2. Simulation results show a uniform distribution of Vout, in line with data. No probability tracking is needed thanks to natural matching of HRS distributions in cells P and Q (Fig. 4(a)). This was possible because the cycleto-cycle variability was significantly larger than the cell-to-cell variability in our devices.

# B. Serial reset

Fig. 5(a) shows the serial reset scheme for the RNG where the cells P and Q are connected in series between voltage supplies  $V_P$  and  $V_Q$ . As in the parallel reset case, 1T1R devices were used for cells P and Q for the experimental demonstration. Fig. 5(b) shows the RNG cycle consisting of (i) independent set of P and Q, (ii) conditional reset of P and Q, and (iii) read of the voltage  $V_{out}$  of the common node between P and Q. During random reset, a negative voltage  $V_P$  - $V_Q$  < 0 is applied across P and Q while the intermediate

Fig. 5. Series reset circuit (a) and sequence of applied signals (b). Starting from HRS, the cells are first independently set, then subjected to random reset where only one cell can reset, and finally read in voltage-divider configuration.

Fig. 6. Schematic illustration of time evolution of the I-V curves of cells P and Q during random reset causing the transition of P (a) and measured voltage across P and Q (b).

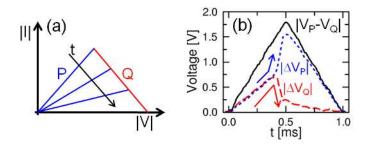

node between P and Q is left floating. The total applied voltage is  $|V_P - V_Q| > 2V_{reset}$ , thus sufficient to trigger reset in at least one device. Once the reset transition is initiated in either device, the voltage across it increases because of the voltage divider configuration, thus causing the voltage across the other cell to reduce. This is illustrated in Fig. 6(a), schematically showing the I-V curve of P with Q acting as load resistance: after the onset of the reset transition in P, the voltage drop across P increases, thus accelerating reset transition in P, while the voltage drop across Q decreases, thus preventing reset transition in Q. Fig. 6(b) shows the experimentally measured voltage  $V_P$ - $V_Q$  applied across the 2 RRAM devices, the voltage  $\Delta V_P$  across P and the voltage  $\Delta V_Q$  across Q, showing the reset transition after about 0.4 ms along the rising edge of the pulse. This self-accelerated random reset scheme results in the reset transition being randomly carried out in one device only, namely the one featuring the smallest  $V_{reset}$  as a result of LRS variability [17]. The variation of V<sub>reset</sub> thus serves as the entropy source in this scheme. A similar scheme was used to perform material implication in RRAM logic, where the 2 devices were deliberately prepared in different LRS to avoid the unpredictable random reset in Figs. 5 and 6 [13].

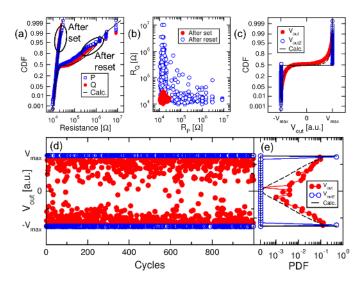

After random reset, the potential of the intermediate node between P and Q is read while a voltage  $2V_{read}$  is applied across the 2 cells. Fig. 7(a) shows the cumulative distribution of resistance R of P and Q after either set or reset in Fig. 5(b). After reset, both P and Q show equal bimodal distributions with 50% transition point, demonstrating unbiased true RNG without probability tracking. The calculated distributions after random reset were obtained by randomly moving 50% of samples from the LRS distribution to the HRS distribution. Fig. 7(b) shows the correlation plot of  $R_Q$  as a function of  $R_P$  after either set or reset. After reset, the devices show complementary state, namely, if one device shows LRS, then the other shows HRS, and vice versa. This is the result of

Fig. 7. Cumulative distribution of R after set and after reset of cells P and Q (a), correlation plot of  $R_Q$  as a function of  $R_P$  (b), cumulative distribution of measured  $V_{out}$  and  $V_{out2}$  (c) measured  $V_{out}$  and  $V_{out2}$  as a function of RNG cycles (d) and their corresponding PDF (e).

the random reset process in Fig. 6, where the voltage division after the onset of the reset transition accelerates or prevents the reset process in one RRAM or the other. Fig. 7(c) shows the resulting experimental and calculated bimodal distribution of Vout with transition point at 50% probability. Voltage regeneration is possible by introducing a CMP (or digital inverter), resulting in the bimodal abrupt distribution of  $V_{out2}$ in Fig. 7(c). Fig. 7(d) shows the cycling evolution of  $V_{out}$ and  $V_{out2}$  during repetition of the RNG sequence in Fig. 5(b), completed by a final unconditional reset pulse, with amplitude larger than the total voltage applied during the random reset pulse  $|V_P - V_Q|$ , to ensure that the first set pulse is applied to equal states in P and Q. Fig. 7(e) shows the corresponding PDF of Vout and Vout2 for data and calculations. These results demonstrate unbiased true RNG with no probability tracking, taking advantage of random reset in the 2 coupled RRAM devices. Note that this RNG scheme is particularly suited to devices with relatively low V<sub>reset</sub>, since the applied voltage 2V<sub>reset</sub> is finally dropping almost totally across the HRS cell. This might cause early failure of the RRAM device, since endurance exponentially decreases with  $V_{stop}$ , i.e., the maximum voltage during reset, in RRAM [14].

## C. Parallel set

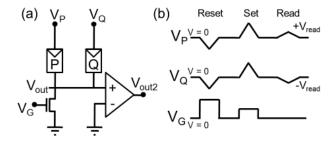

Fig. 8 shows the parallel set scheme for RNG (a) and the corresponding voltage pulse sequence (b). The 2 RRAM devices are connected to ground via a transistor controlled by a gate voltage  $V_G$ . The pulse sequence includes (i) independent reset of P and Q, (ii) random set of P and Q, and (iii) read by application of a voltage  $2V_{read}$  across the 2 devices while the

Fig. 8. Parallel set circuit (a) and sequence of applied signals (b). Starting from LRS, the cells are first independently reset, then subjected to parallel set, and finally read with voltage-divider configuration.

Fig. 9. Schematic illustration of the I-V curves of P and Q during a parallel set operation in the circuit of Fig. 8(a). As the set transition starts to occur in the cell with smaller  $V_{set}$  (P in the figure) the voltage across both cells drops thus inhibiting set transition in the other cell (Q in the figure).

#### TABLE I

Randomness test results for a sequence of more than 2 Mbits generated by the parallel-reset scheme of Fig. 3(a) divided in 55 segments before and after Von Neumann correction. Tests are passed if P-value<sub>T</sub> ( $X^2$ ) > 0.0001 and Proportion > 0.945454. The RRAM scheme passes all tests after Von Neumann correction, except for the Non Overlapping Template Matching test which was passed in 143 sequences over 148, namely about 96.6%.

|                                | Output                       |             | After Von Neumann correction |             |

|--------------------------------|------------------------------|-------------|------------------------------|-------------|

| Test                           | P-value <sub>T</sub> $(X^2)$ | Proportion  | P-value <sub>T</sub> $(X^2)$ | Proportion  |

| Frequency                      | 0.000000                     | 0.109091    | 0.514124                     | 1.000000    |

| Block Frequency                | 0.000000                     | 0.000000    | 0.637119                     | 1.000000    |

| Cumulative Sums (forward)      | 0.000000                     | 0.036364    | 0.595549                     | 1.000000    |

| Cumulative Sums (reverse)      | 0.000000                     | 0.072727    | 0.401199                     | 1.000000    |

| Runs                           | 0.000000                     | 0.018182    | 0.437274                     | 1.000000    |

| Longest Run of Ones            | 0.000000                     | 0.145455    | 0.275709                     | 1.000000    |

| FFT                            | 0.000000                     | 0.545455    | 0.000184                     | 0.981818    |

| Non Overlapping                | 55/148                       | 1/148       | All test                     | 143/148     |

| Template Matching              | test passed                  | test passed | passed                       | test passed |

| Serial (P-value <sub>1</sub> ) | 0.000000                     | 0.018182    | 0.595549                     | 0.981818    |

| Serial (P-value <sub>2</sub> ) | 0.000000                     | 0.290909    | 0.129620                     | 0.981818    |

| Approximate Entropy            | 0.000000                     | 0.036364    | 0.798139                     | 0.981818    |

transistor is in the off state. This RNG scheme takes advantage of the dynamic voltage divider in the 1-transistor/2-resistor (1T2R) structure during set: as the voltage across the 2 RRAM increases, set transition eventually takes place randomly in one device, while the consequent voltage decrease across P and Q inhibits the other device to undergo set transition. This finally leads to a random set transition, similar to the random reset transition in the scheme of Figs. 5-7. The variation of V<sub>set</sub> serves as the entropy source in the scheme, similar to the 1-RRAM scheme described in Fig. 2. Clearly, no probability tracking is needed in Fig. 8, since set transition is naturally occurring in one device only in each cycle.

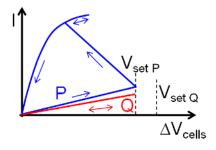

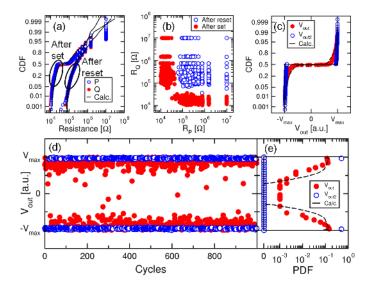

Fig. 9(a) schematically shows the I-V characteristics of P and Q during the set pulse: as set transition takes place in P because of  $V_{set,P} < V_{set,Q}$ , the voltage across both devices drops thus preventing any set transition in Q. Fig. 10(a) shows the resulting bimodal distribution of R for P and Q,

Fig. 10. Cumulative distributions of R after reset and after set for P and Q (a), correlation plot of  $R_Q$  as a function of  $R_P$  after set and reset(b), cumulative distributions of  $V_{out}$  and  $V_{out2}$  (c), measured  $V_{out}$  and  $V_{out2}$  as a function of RNG cycles (d) and their corresponding PDF (e).

showing a bimodal distribution with a HRS/LRS transition at 50%. Calculations were performed by randomly moving 50% samples from the HRS distribution to the LRS distribution. Fig. 10(b) shows the correlation plot of  $R_Q$  as a function of  $R_P$ , indicating complementary states, namely P is always in HRS if Q is in LRS, and vice versa. Fig. 10(c) shows the cumulative distributions of  $V_{out}$  and  $V_{out2}$ , the latter being the output of the regenerative CMP. Nice bimodal distributions with smooth and abrupt transitions are shown by  $V_{out}$  and  $V_{out2}$ , respectively. Figs. 10(d) and (e) show  $V_{out}$  and  $V_{out2}$  as a function of the RNG cycle (d) and the corresponding PDF (e). Calculations are provided for Figs. 10(c) and (e), showing a good agreement with data.

Note that the parallel set RNG shows a better performance based on the bimodal distributions of R (Fig. 10(a)) and  $V_{out}$ (Figs. 10(c) and (e)) compared to the parallel reset in Fig. 7(a). This can be understood by the abrupt set transition in the parallel set approach as opposed to the more gradual reset transition in the parallel reset scheme, as also visible from the I-V characteristics of the individual RRAM device in Fig. 1(b) and explained by the different microscopic processes of filament growth and gap depletion during set and reset, respectively [20].

#### **IV. RANDOMNESS ANALYSIS**

To assess the performance of any true RNG, randomness test is mandatory. For this purpose, we evaluated randomness on one of our schemes, using the standard set of statistical tests developed by the National Institute of Standards and Technology (NIST) [21]. The serial reset and the parallel set schemes showed less excellent performance against the NIST test, which we attribute to the stronger impact of cell-cell variability of  $V_{reset}$  and  $V_{set}$ , respectively. Therefore, we focussed on the parallel reset scheme in the following NIST test.

Each random bit was generated in 6 ms, including set, reset and read pulses of 1 ms width, each followed by a 1 ms wait time. The generation rate is therefore about 0.16 kHz, although we estimate that much faster generation can be achieved (*e.g.*, around 1 GHz) by taking advantage of the sub-1 ns switching time of HfO<sub>x</sub> RRAM [22]. The RNG output was taken at  $V_{out2}$  in the scheme of Fig. 3(a).

Randomness was tested on a generated sequence of about 2,280,000 random bits. According to the NIST guidelines, we divided the entire sequence in 55 segments and we applied the 9 different tests reported in Tab. I. Each test returned 2 parameters, P-value<sub>T</sub>(X<sup>2</sup>) and Proportion. If P-value<sub>T</sub>(X<sup>2</sup>)  $\geq$  0.0001, then the sequence can be considered to be uniformly distributed, while, for the Proportion, the minimum pass rate for each statistical test is 0.945454.

Tab. I shows pass/fail results for both the raw bit data, and that obtained after Von Neumann correction, namely a standard post-process analysis which removes all the 0 and 1 bias from a pseudo random sequence [7]. Results indicate that all tests applied to raw bits failed, while application of the Von Neumann correction allows our scheme to pass all tests except one, namely the Non Overlapping Template Matching test where pass rate was 143 over 148. Note that Von Neumann is a standard tool to improve randomness of RNG, although it introduces additional complexity in terms of controller logic of the RNG circuit. These results appear promising for hardwarebased, true unbiased RNG using RRAM technology.

## V. CONCLUSIONS

We presented 3 new concepts for unbiased RNG relying on switching variability in RRAM. All concepts adopt 2 coupled RRAM devices to provide 50% probability of 0s and 1s by self-compensation schemes, as opposed to complicated probability tracking proposed before. The concepts include (i) a parallel reset configuration based on HRS resistance variation, (ii) a serial reset configuration based on V<sub>reset</sub> variation, and (iii) a parallel set configuration based on V<sub>set</sub> variation. In all cases, bimodal distributions of high/low voltage were obtained with low-to-high transition at 50%. RNG was improved by adding digital regeneration. The results of the randomness tests for the parallel reset scheme with/without the Von Neumann correction support the 2-RRAM scheme for future on-chip RNG, thus enlarging the pool of potential application for RRAM technology.

#### REFERENCES

- [1] S. K. Mathew, S. Srinivasan, M. A. Anders, H. Kaul, S. K. Hsu, F. Sheikh, A. Agarwal, S. Satpathy, and R. K. Krishnamurthy, "2.4 Gbps, 7 mW all-digital PVT-variation tolerant true random number generator for 45 nm CMOS high-performance microprocessors," *IEEE J. Solid-State Circ.*, vol. 47, no. 11, pp. 2807–2821, 2012.

- [2] R. Brederlow, R. Prakash, C. Paulus, and R. Thewes, "A low-power true random number generator using random telegraph noise of single oxide-traps," *ISSCC Tech. Dig.*, no. 1666, 2006.

- [3] C.-Y. Huang, W. C. Shen, Y.-H. Tseng, Y.-C. King, and C.-J. Lin, "A contact-resistive random-access-memory-based true random number generator," *IEEE Electron Device Lett.*, vol. 8, no. 33, pp. 1108–1110, Aug. 2012.

- [4] S. Ambrogio, S. Balatti, A. Cubeta, A. Calderoni, N. Ramaswamy, and D. Ielmini, "Statistical fluctuations in *HfO<sub>x</sub>* resistive-switching memory (RRAM): Part II - Random telegraph noise," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2920–2927, Aug. 2014.

- [5] S. Ambrogio, S. Balatti, V. McCaffrey, D. Wang, and D. Ielmini, "Noiseinduced resistance broadening in resistive switching memory (RRAM) -Part II: Array statistics," *IEEE Trans. Electron Devices*, vol. 62, no. 11, pp. 3812–3819, Nov. 2015.

- [6] A. Fukushima, T. Seki, K. Yakushiji, H. Kubota, H. Imamura, S. Yuasa, and K. Ando, "Spin dice: A scalable truly random number generator based on spintronics," *Appl. Phys. Express.*, no. 7, p. 083001, 2014.

- [7] W. Choi, L. Yang, K. Jongyeon, A. Deshpande, K. Gyuseong, J.-P. Wang, and C. Kim, "A magnetic tunnel junction based true random number generator with conditional perturb and real-time output probability tracking," *Electron Devices Meeting (IEDM)*, 2014 IEEE International, pp. 315–318, 2014.

- [8] S. Gaba, P. Sheridan, J. Zhou, S. Choi, and W. Lu, "Stochastic memristive devices for computing and neuromorphic applications," in *Nanoscale*, no. 5, 2013, pp. 5872–5878.

- [9] Y. Wang, W. Wen, M. Hu, and H. Li, "A novel true random number generator design leveraging emerging memristor technology," *Great Lakes Symposium on VLSI*, pp. 271–276, 2015.

- [10] A. Chen, "Utilizing the variability of resistive random access memory to implement reconfigurable physical unclonable functions," *Electron Device Letters, IEEE*, vol. 36, no. 2, pp. 138–140, Feb. 2015.

- [11] S. Yu, "Orientation classification by a winner-take-all network with oxide rram based synaptic devices," *Circuits and Systems (ISCAS), 2014 IEEE International Symposium on*, pp. 1058–1061, 2014.

- [12] S. Balatti, S. Ambrogio, Z.-Q. Wang, and D. Ielmini, "True random number generation by variability of resistive switching in oxide-based devices," in *IEEE Journal on Emerging and Selected Topics in Circuits* and Systems, vol. 5, no. 2, June 2015, pp. 214–221.

- [13] S. Balatti, S. Ambrogio, and D. Ielmini, "Normally-off logic based on resistive switches-Part I: Logic gates," in *IEEE Trans. Electron Devices*, vol. 62, no. 6, June 2015, pp. 1831–1838.

- [14] S. Balatti, S. Ambrogio, Z.-Q.Wang, S. Sills, A. Calderoni, N. Ramaswamy, and D. Ielmini, "Voltage-controlled cycling endurance of HfO<sub>x</sub>-based resistive-switching memory (RRAM)," *IEEE Trans. Electron Devices*, vol. 62, no. 10, pp. 3365–3372, Oct. 2015.

- [15] D. Ielmini, "Modeling the universal set/reset characteristics of bipolar RRAM by field- and temperature-driven filament growth," *IEEE Trans. Electron Devices*, vol. 58, pp. 4309–4317, Dec. 2011.

- [16] S. Yu, X. Guan, and H.-S. P. Wong, "On the stochastic nature of resistive switching in metal oxide RRAM: Physical modeling, monte carlo simulation, and experimental characterization," *IEDM Tech. Dig.*, pp. 275–278, 2011.

- [17] S. Ambrogio, S. Balatti, A. Cubeta, A. Calderoni, N. Ramaswamy, and D. Ielmini, "Statistical fluctuations in  $HfO_x$  resistive-switching memory (RRAM): Part I - Set/Reset variability," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2912–2919, Aug. 2014.

- [18] A. Fantini, L. Goux, R. Degraeve, D. J. Wouters, N. Raghavan, G. Kar, A. Belmonte, Y.-Y. Chen, B. Govoreanu, and M. Jurczak, "Intrinsic switching variability in *HfO*<sub>2</sub> RRAM," *International Memory Workshop IMW*, pp. 30–33, 2013.

- [19] Z.-Q. Wang, S. Ambrogio, S. Balatti, S. Sills, A. Calderoni, N. Ramaswamy, and D. Ielmini, "Cycling-induced degradation of metal-oxide resistive switching memory (RRAM)," *IEDM Tech. Dig.*, pp. 173–176, 2015.

- [20] S. Larentis, F. Nardi, S. Balatti, D. C. Gilmer, and D. Ielmini, "Resistive switching by voltage-driven ion migration in bipolar RRAM - Part II: Modeling," *IEEE Trans. Electron Devices*, vol. 59, no. 9, pp. 2468–2475, Sept. 2012.

- [21] A. Rukhin, J. Soto, J. Nechvatal, M. Smid, E. Barker, S. Leigh, M. Levenson, M. Vangel, D. Banks, A. Heckert, J. Dray, and S. Vo, "A statistical test suite for random and pseudorandom number generators for cryptographic applications," *NIST Special Publications*, no. 800-22, 2010.

- [22] H. Y. Lee, Y. S. Chen, P. S. Chen, P. Y. Gu, Y. Y. Hsu, S. M. Wang, W. H. Liu, C. H. Tsai, S. S. Sheu, P. C. Chiang, W. P. Lin, C. H. Lin, W. S. Chen, F. T. Chen, C. H. Lien, and M. Tsai, "Evidence and solution of over-reset problem for HfO<sub>x</sub> based resistive memory with sub-ns switching speed and high endurance," in *IEDM Tech. Dig.*, 2010, pp. 460–463.

Simone Balatti (S'12) received B.S., M.S. degrees and Ph.D. in Electrical Engineering from Politecnico di Milano, Italy, in 2009, 2011 and 2015, respectively. He is now working as Device Engineer at Intermolecular Inc., CA, USA. His research interests include the study of novel devices for memory applications.

Alessandro Calderoni received the Laurea (cum laude) degree in electrical engineering from Politecnico di Milano, Milano, Italy, in 2006. He is currently with the Emerging Memory Cell Technology Team, Micron Technology, Boise, ID, USA, as a Senior Device Engineer. His current research interests include the characterization of various emerging memory devices and selectors for high-density applications.

**Stefano Ambrogio** (S'14) received the M.S. (cum laude) degree in Electrical Engineering from Politecnico di Milano, Italy, in 2012. He is currently working toward his Ph.D. at Politecnico di Milano in the group of Prof. Ielmini. His main research interests are electrical characterization, modeling and neuromorphic applications of resistive switching and ECM memories.

**Roberto Carboni** received the B.S. degree in electrical engineering from Politecnico di Milano, Milano, Italy, in 2013, where he is currently pursuing the M.S. degree in electrical engineering. His current research interests include the characterization and modeling of resistive switching and magnetoresistive memories.

Nirmal Ramaswamy (M'07-SM'09) received the bachelor's degree in metallurgical engineering from IIT Madras, Chennai, India, and the M.S. and Ph.D. degrees in material science and engineering from Arizona State University, Phoenix, AZ, USA. He has been with Micron Technology, Boise, ID, USA, since 2002, where he is currently the Manager of Emerging Memory Cell Technology Team. His current research interests include various emerging memory technologies for high-density applications.

**Valerio Milo** received the B.S. and M.S. degrees in Electrical Engineering from Politecnico di Milano, Milan, Italy, in 2012 and 2015, respectively. Since November 2015, he is a PhD student in Electrical Engineering at Politecnico di Milano in the group of Prof. Ielmini. His main research interests are modeling and neuromorphic applications of resistive switching and phase change memories.

**Daniele Ielmini** received a Ph.D. in 2000 from Politecnico di Milano in 2000. He joined the Dipartimento di Elettronica, Informazione, e Bioingegneria of Politecnico di Milano as an Assistant Professor in 2002 and Associate Professor in 2010. He conducts research on emerging nanoelectronic devices, such as phase change memory (PCM) and resistive switching memory (RRAM). He received the Intel Outstanding Researcher Award in 2013 and the ERC Consolidator Grant in 2014.

**Zhongqiang Wang** was born in Hebei, China, in 1984. He received the B.S. and Ph.D. degrees in condensed matter physics from Northeast Normal University, Changchun, China, in 2008 and 2013, respectively. He is currently a postdoc researcher of the DEIB of the Politecnico di Milano. His research interests mainly involve device fabrication, electrical characterization and neuromorphic applications of resistive switching resistive switching and conductive bridge memories.