# **Aalborg Universitet**

# Physics-Based Modeling of Parasitic Capacitance in Medium-Voltage Filter Inductors

Zhao, Hongbo; Dalal, Dipen Narendra; Jørgensen, Asger Bjørn; Jørgensen, Jannick Kjær; Wang, Xiongfei; Beczkowski, Szymon Michal; Munk-Nielsen, Stig; Uhrenfeldt, Christian Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2020.3003157

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, H., Dalal, D. N., Jørgensen, A. B., Jørgensen, J. K., Wang, X., Beczkowski, S. M., Munk-Nielsen, S., & Uhrenfeldt, C. (2021). Physics-Based Modeling of Parasitic Capacitance in Medium-Voltage Filter Inductors. *I E E Transactions on Power Electronics*, *36*(1), 829-843. [9119860]. https://doi.org/10.1109/TPEL.2020.3003157

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: August 28, 2022

# Physics-Based Modeling of Parasitic Capacitance in Medium-Voltage Filter Inductors

Hongbo Zhao, *Student Member, IEEE*, Dipen Narendra Dalal, *Student Member, IEEE*, Asger Bjørn Jørgensen, Jannick Kjær Jørgensen, Xiongfei Wang, *Senior Member, IEEE*, Szymon Beczkowski, Stig Munk-Nielsen, *Member, IEEE*, and Christian Uhrenfeldt, *Member, IEEE*.

Abstract- This paper proposes a general physics-based model for identifying the parasitic capacitance in medium-voltage (MV) filter inductors, which can provide analytical calculations without using empirical equations and is not restricted by the geometrical structures of inductors. The elementary capacitances of the MV inductor are identified, then the equivalent capacitances between the two terminals of the inductor are derived under different voltage potential on the core. Further, a three-terminal equivalent circuit, instead of the conventional two-terminal equivalent circuit, is proposed by using the derived capacitances. Thus, the parasitic equivalent capacitance between the terminals and core are explicitly quantified. Experimental measurements for parasitic capacitances show a good agreement with the theoretical calculations.

Index terms- Physics-based modeling, parasitic capacitance, medium-voltage, filter inductors, three-terminal equivalent circuit.

#### I. INTRODUCTION

With the recent advancements of the Silicon Carbide (SiC) technology, the blocking voltage of SiC Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) devices has been increased to 10 kV and 15 kV [1], which brings several benefits to the medium-voltage (MV) power converters, such as a simpler circuit topology [2], [3], and lower turn-on and turn-off switching energy dissipation than in Si devices [4].

Due to the faster switching behavior (higher dv/dt) of SiC MOSFET devices, the parasitic capacitances of MV converter systems are of significant concern [5]. The adverse effects of parasitic capacitances on the converter operation are recently revealed, e.g., the transient heatsink-grounding current [6], the drain current oscillations caused by power modules [7]-[9], and the common-mode current in the gate drivers [10], [11]. It has been shown that the parasitic capacitance of MV filter inductors can bring large spikes to the drain current and the load current [12], [13], which can be three times larger than the nominal load current [13], and consequently deteriorate electromagnetic interference issues [14] and accelerate the aging of power modules [15].

The modeling and analysis of parasitic capacitances in the MV converter filters have also attracted increasing attention. The physics-based modeling methods, which are based on the

This work is supported by MV-BASIC project (https://www.mvbasic.et.aau.dk/), which is co-funded by the Department of Energy Technology of Aalborg University, KK wind solutions and Siemens Gamesa. (Corresponding author: Xiongfei Wang)

H. Zhao, D. Dalal, A. Jørgensen, J. Jørgensen, X. Wang, S. Beczkowski, S. Munk-Nielsen, and C. Uhrenfeldt are with the Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark (e-mail: hzh@et.aau.dk; xwa@et.aau.dk; smn@et.aau.dk)

geometrical structures of inductors, are widely applied to calculate the parasitic capacitance of filter inductors. Those methods can be broadly categorized into two groups: i) Finite element methods (FEM); ii) Analytical modeling methods.

The FEM models have better accuracy than the analytical models. In those models, the commonly used FEM-based software, e.g., ANSYS and COMSOL, are first used to extract the parasitic electrical parameters of components by means of a 2-dimensional or a 3-dimensional computer-aided design (CAD) tool [16], and then, the RLC matrix can be exported at certain frequencies [17]. Although convenient, this method has two restrictions: 1) it is time-consuming if the components have complex structures; 2) it is hard to derive design-oriented insights that can map the geometrical parameters to parasitic RLC parameters.

It is therefore of interest to develop the analytical modeling methods for calculating the parasitic capacitance of inductors, which is computationally more efficient and applicable for the model-based design and optimization when compared to the FEM-based alternatives [18]. Analytical modeling methods are capable of fully characterizing the capacitive couplings in inductors. Two approaches have been reported to derive the analytical models.

The first approach is based on the energy-conservation modeling [18]-[22], which is developed by assuming the equal voltage drops across the windings and using the energy-conservation law. A relative capacitance of the two adjacent planes between the two terminals of inductors can be derived, which is, however, dependent on the capacitance when the two adjacent planes are completely disconnected [19]. The empirical equations are therefore widely used for deriving the capacitance when the two adjacent planes are disconnected [19]-[22]. Yet, the empirical equations are not precise when the geometrical structure of inductors is complex, and hence it is important to compensate for the errors. For that purpose, an improved model with equivalent relative permittivity is recently reported in [18]. However, the improved model is still not a general modeling method for inductors with complex geometric structure

The second method is based on the lumped-circuit modeling which is, in theory, based on the charge-conservation law and the equivalent circuit network [23]-[28]. The circuit network is composed by multiple capacitances, where each capacitance can be theoretically calculated based on the charge-conservation law and the geometrical structure [23]. Although intuitive, the computation burden of this approach increases

with the rising complexity of the equivalent circuit network. In case that the geometrical structure of the inductor winding is simple, the explicit analytical equation of overall capacitance between the two terminals of the inductor can be readily derived, based on the symmetry of the circuit without considering inductive effects [23]. However, when the geometrical structure is complex, or the inductive effects are considered, it is difficult to simplify the circuit network into the explicit analytical equations. It is therefore necessary to solve the circuit by using matrix-based calculators [27] and circuit-based simulators [28].

A common restriction of the previous analytical models is the two-terminal circuit assumption, which is merely valid for calculating the parasitic capacitance of inductors with a floating core. Yet, the same does not apply to inductors with a grounded core, since the inductor should be represented by a threeterminal equivalent circuit. The IEEE Std. C57.12.01 requires to ground the frame and core of high-power dry-type transformers [29] such that the extra common-mode current injection can be observed [30], and thus the couplings between terminals and core cannot be neglected. Although there are no specific standards on the grounding requirements for highpower filter inductors, their frame and core are usually grounded in practice due to the safety requirements. Especially for the MV inductors, the potential of the core can float with high value if not grounded, due to the high voltages at the dc link and ac grid side.

Two major challenges can therefore be identified from the prior art, which are summarized as follows

- The energy-conservation modeling is constrained by the accuracy of the used empirical equations, while the lumped-circuit modeling is limited by the computation burden.

- The two-terminal equivalent circuit is inadequate for modeling inductors with grounded cores, where the capacitive couplings between two terminals and the ground cannot be overlooked.

To address these challenges, this paper proposes a physicsbased modeling approach, where instead of directly using empirical equations as in [19], the inductor is modeled first as a circuit network of elementary capacitances, which are then lumped as total capacitances between inductor terminals by using the energy-conservation principle. Thus, a more general and computationally efficient modeling procedure than the conventional approaches is obtained. Further, based on the lumped capacitances of inductors, a three-terminal equivalent circuit, considering three different core potentials, is developed, which not only enables to characterize the capacitive couplings between terminals and ground when the core is grounded, but can also be readily adapted to inductors with floating cores. The calculations of parasitic capacitance of the researched inductor by using the proposed modeling method have been verified experimentally.

## II. CAPACITIVE COUPLINGS IN MV INDUCTORS

A MV filter inductor is given as an example in this paper. The MV inductor is designed for a 5 kHz 2-level voltage source

converter based on SiC MOSFETs with 4.16 kV line-to-line voltage and 6 kV dc-link voltage.

Two U-type amorphous cores are used for the magnetic loop with a 2 mm air gap in between. Due to the high inductance of the required filter inductor, the dual windings are designed with a 3-layer structure, which can increase the power density of the filter inductor. There is 63 turns in each layer. With 189 turns of a single winding, a 30 mH inductance is achieved with the dual windings. The inductor is designed to the rated RMS current of 8 A.

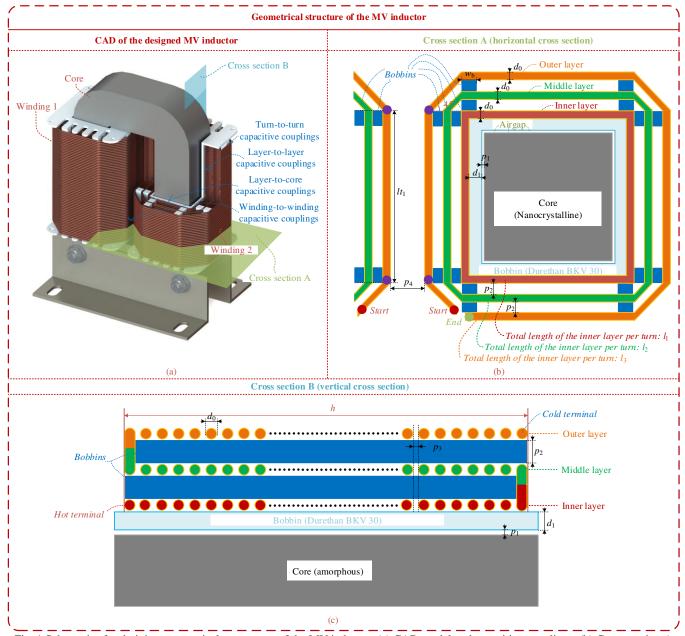

Three schematics of the MV inductor are shown in Fig. 1 to illustrate the physical structure. Fig. 1 (a) is the CAD model of the designed MV 30 mH inductor. Fig. 1(b) is the horizontal cross-section view of the designed inductor. Fig. 1(c) is the vertical cross-section view of one of the dual windings of the designed inductor. As can be seen, some spacers are added between two adjacent layers to provide an extra distance for reducing the equivalent parasitic layer-to-layer capacitance. Bobbins are added between the inner layer and core for insulating the core and windings. The key parameters of the physical structure of the inductor are listed in Table I.

Table I. Key parameters of the MV inductor

| Description                               | Symbol                | Value    |

|-------------------------------------------|-----------------------|----------|

| Diameter of the cable                     | $d_0$                 | 1.4 mm   |

| Length of the air gap between the bobbin  | <i>p</i> <sub>1</sub> | 0.75 mm  |

| and core                                  |                       |          |

| Thickness of the bobbins between the      | $d_1$                 | 2 mm     |

| inner layer and core                      |                       |          |

| Length of the air gap between two         | $p_2$                 | 5.7 mm   |

| adjacent layers                           |                       |          |

| Average length of the air gap between     | рз                    | 0.45 mm  |

| two turns in the same layer               |                       |          |

| Height of the windings                    | h                     | 11.9 cm  |

| Width of the spacers between two          | Wb                    | 4.8 mm   |

| adjacent layers                           |                       |          |

| Length of the outer layer per turn        | $l_1$                 | 24.7 cm  |

| Length of the middle layer per turn       | $l_2$                 | 22.2 cm  |

| Length of the inner layer per turn        | $l_3$                 | 19.7 cm  |

| Average length of per turn for three      | l                     | 22.2 cm  |

| layers                                    |                       |          |

| Average length of the air gap between the | <i>p</i> <sub>4</sub> | 3 mm     |

| two windings                              |                       |          |

| Number of turns of per layers             | n                     | 63       |

| Number of layers                          | m                     | 3        |

| Number of the winding                     | w                     | 2        |

| Total inductance                          | L                     | 30 mH    |

| Equivalent inductance per turn            | $L_1$                 | 0.079 mH |

The values for the relative permittivity of the materials are listed in Table II, which are identified from the datasheet.

The cables for windings are selected as DAMID 200 [31]. The coating material of the cables is THEIC-modified polyester. The bobbins are selected as UI/120/41 for c-type cores [32]. The material of bobbin is Durethan BKV 30 H3, which is based

Fig. 1 Schematics for deriving geometrical parameters of the MV inductor. (a) CAD model and capacitive couplings. (b) Cross section A (horizontal cross section) . (c) Cross section B (vertical cross section).

on polyamide 6 with 30% glass-reinforced [33]. The spacers between two adjacent layers are manufactured by using the same material as bobbins. The relative permittivity of polyester is between 2.8-4.5 [34]. Therefore, the average value 3.7 is used in this paper.

TABLE II. RELATIVE PERMITTIVITY OF THE MATERIAL

| Description                          | Symbol Value               |                            |

|--------------------------------------|----------------------------|----------------------------|

| The permittivity of the bobbins [33] | $\mathcal{E}_{b}$          | 4.0                        |

| The permittivity of the coating of   | $\mathcal{E}_{\mathrm{r}}$ | 3.7                        |

| cables [34]                          |                            | (average value)            |

| The permittivity of vacuum [35]      | £0                         | 8.82×10 <sup>-12</sup> F/m |

The capacitive couplings in this inductor are identified as follows:

- The turn-to-turn capacitive coupling contributed by the voltage potential difference between two neighbor turns in the same layer.

- The layer-to-layer capacitive coupling resulted from the voltage potential difference between two neighbor turns at different layers.

- The layer-to-core capacitive coupling caused by the voltage potential differences between the inner layer and the core.

The winding-to-winding capacitive coupling resulted from the voltage potential differences between the two windings.

#### III. CONVENTIONAL ANALYTICAL MODELING METHODS

This section reviews two commonly used analytical modeling methods, and the constraints for calculating the parasitic capacitance of the researched MV filter inductor are highlighted.

## A. Lumped-circuit modeling method

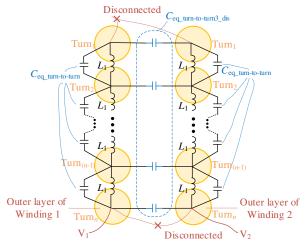

Based on [23]-[26], the lumped-circuit modeling method is used for characterizing the parasitic capacitance of the researched inductor.

The turn-to-turn, layer-to-layer, and winding-to-winding capacitive couplings can be decomposed into elementary turn-to-turn capacitances, since all of them can be represented by the voltage potential difference between the two turns. The bobbins (spacers) can be used between two adjacent layers, and hence, the elementary turn-to-turn capacitance with and without bobbins needs to be considered, respectively. In contrast, the layer-to-core capacitive coupling is composed of multiple elementary turn-to-core capacitances. Since the bobbins are always used in high-power inductors, only the elementary turn-to-core capacitance with bobbins is derived.

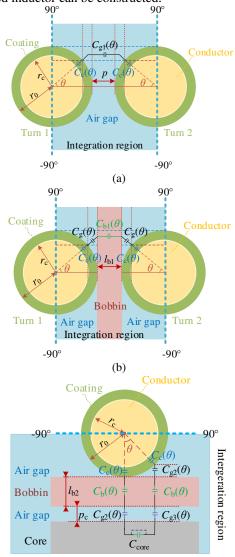

Therefore, three elementary capacitances of the researched MV inductor are developed, which are given in Fig. 2.  $r_c$  and  $r_0$  are the radii of the conductor, and turn including coating. p and  $p_c$  are the lengths of the air gap between two turns for calculating elementary turn-to-turn and turn-to-core capacitance.  $l_{b1}$  and  $l_{b2}$  are the thickness of the two different bobbins.  $\Theta$  is the elementary angle.

In Fig. 2,  $C_c(\theta)$  is the elementary coating capacitance,  $C_{g1}(\theta)$ ,  $C_{g2}(\theta)$ , and  $C_{g3}(\theta)$  are the elementary air capacitances.  $C_{b1}(\theta)$  and  $C_{b2}(\theta)$  are the elementary bobbin capacitances,  $C_{core}$  is the elementary core capacitance.

The derived equations for representing the elementary turn-to-turn capacitances without bobbins  $C_{\text{ele\_turn-to-turn}}$  of Fig .2(a) are shown in (1).  $\varepsilon_0$  and  $\varepsilon_r$  are the permittivity of vacuum and coating, respectively.

$$dC_{c}(\theta) = \frac{\varepsilon_{r}\varepsilon_{0}}{\ln \frac{r_{0}}{r_{c}}} d\theta$$

$$dC_{g1}(\theta) = \frac{\varepsilon_{0}r_{0}}{p + 2r_{0}(1 - \cos \theta)} d\theta$$

$$\frac{1}{dC_{ele\_turn-to-turn}(\theta)} = \frac{1}{dC_{c}(\theta)} + \frac{1}{dC_{g1}(\theta)} + \frac{1}{dC_{c}(\theta)}$$

(1)

Therefore, the integrated elementary capacitance  $C'_{\text{ele\_turn-to-turn}}$  between two neighbor turns in Fig. 1(a) can be represented as (2), where the integrated angle is from  $[-\pi/2, \pi/2]$  [24].

$$C'_{\text{ele\_turn-to-turn}} = \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} dC_{\text{ele\_turn-to-turn}}(\theta)$$

(2)

Similarly, the integrated elementary turn-to-turn capacitance with bobbins  $C'_{\text{ele\_turn-to-turn\_wb}}$  and turn-to-core capacitance  $C'_{\text{ele\_turn-to-core\_wb}}$  are derived.

By using the integrated elementary capacitance, the equivalent circuit of the parasitic capacitive couplings of the researched inductor can be constructed.

Fig. 2 Elementary capacitances of the researched inductor. a) Turn-to-turn capacitance without bobbins; b) Turn-to-turn capacitance with bobbins; c) Turn-to-core capacitance.

(c)

$$\begin{cases} \frac{1}{dC_{\text{ele\_turn-to-turn\_wb}}} = \frac{2}{dC_{\text{c}}(\theta)} + \frac{2}{dC_{\text{g2}}(\theta)} + \frac{1}{dC_{\text{b1}}(\theta)} \\ C'_{\text{ele\_turn-to-turn\_wb}} = \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} dC_{\text{ele\_turn-to-turn\_wb}}(\theta) \\ \begin{cases} \frac{1}{dC_{\text{ele\_turn-to-core\_wb}}} = \frac{1}{dC_{\text{c}}(\theta)} + \frac{1}{dC_{\text{g2}}(\theta)} + \frac{1}{dC_{\text{b2}}(\theta)} + \frac{1}{dC_{\text{g3}}(\theta)} \\ C'_{\text{ele\_turn-to-core\_wb}} = \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} dC_{\text{ele\_turn-to-core\_wb}}(\theta) \end{cases}$$

$$(3)$$

However, the explicit analytical equation of parasitic capacitance cannot be identified in this application, since the mathematical induction methods reported in [23]-[25] are only valid for the inductors with simple geometrical structures, where the researched MV inductor has a three-layer and double-winding structure.

#### B. Energy-conservation modeling method

The parasitic capacitance between two adjacent planes can also be described by using the stored electrical-field energy [18]-[22]. The voltage potential on the plane is assumed to be linearly distributed.

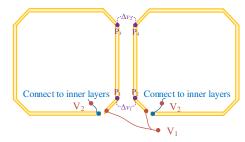

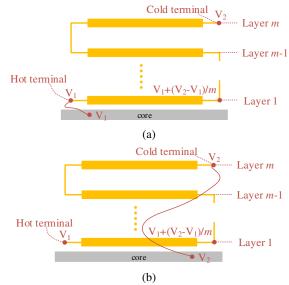

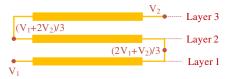

With using this theory, the lumped turn-to-turn capacitance of m-layer cable with n-turns per layer, which is presented in Fig. 3, can be derived as (5) for two windings.  $V_1$  is the voltage potential at the first turn, where  $V_2$  is the voltage potential at the last turn. n is the number of turns in one layer, m is the number of layers.

Fig. 3 Schematic of multiple turns within a winding

$$C_{\text{eq\_turn-to-turn}} = 2 \times \frac{nm-1}{(nm)^2} \times C_{\text{eq\_turn-to-turn\_dis}}$$

(5)

where  $C_{\text{eq\_turn-to-turn\_dis}}$  is the capacitance between two adjacent turns when disconnected. The detailed derivations are attached in Appendix a).

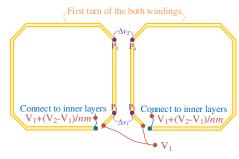

In Fig. 4, the lumped winding-to-winding capacitance is addressed, where the equation is presented in (6). In this case, only the region within  $P_1P_2P_3P_4$  is assumed to store the electrical field energy between the two windings.

Fig. 4 Schematic of the two windings

$$C_{\rm eq\_winding\_to\_winding} = \frac{(\Delta v_1^2 + \Delta v_2^2 + \Delta v_1 \Delta v_2)}{3nm(V_2 - V_1)^2} C_{\rm eq\_winding\_to\_winding\_dis}$$

where  $C_{\text{eq\_winding-to-winding\_dis}}$  is the capacitance between the two adjacent windings of  $P_1P_3$  and  $P_2P_4$  when disconnected. The voltage potential between P1 and P2 is  $\Delta \nu_1$ , where the voltage potential between P3 and P4 is  $\Delta \nu_2$ . The detailed derivations are attached in Appendix b).

Similarly, the lumped layer-to-layer capacitance shown in Fig. 5 is derived as (7).

$$C_{\text{eq\_layer-to-layer}} = \frac{4(m-1)}{3m} \times C_{\text{eq\_layer-to-layer\_dis}}$$

(7)

where  $C_{\text{eq\_layer-to-layer\_dis}}$  is the capacitance between the two adjacent layers when disconnected. The detailed deviations are attached in Appendix c).

Lastly, the lumped layer-to-core capacitance between the inner layer and core shown in Fig. 5 is calculated as (8) for two windings, where the core is assumed to be floating in this case.

$$C_{\text{eq\_layer-to-core}1} = \frac{1}{12m^2} \times C_{\text{eq\_layer-to-core\_dis}}$$

(8)

where  $C_{\text{eq\_layer-to-core\_dis}}$  is the intermediate capacitance between the inner layer and core. The detailed derivations are attached in Appendix d).

Fig. 5 Schematic of multiple layers and a core within a winding

The total lumped capacitance can be calculated as the sum of (5)-(8). Generally, the intermediate capacitance  $C_{\rm eq\_turn-to-turn\_dis}$ ,  $C_{\rm eq\_winding\_to-winding\_dis}$ ,  $C_{\rm eq\_layer-to-layer\_dis}$ , and  $C_{\rm eq\_layer-to-core\_dis}$  can be derived by using the empirical equations in [19].

However, the empirical equations will introduce significant errors when the geometrical structure of inductors is complex since it is not a general solution for deriving the intermediate capacitances. Besides, this method is derived based on the assumption that the core is floating. Therefore, it can not characterize the parasitic coupling between terminals and ground when the core is grounded.

#### IV. PROPOSED ANALYTICAL MODELING METHOD

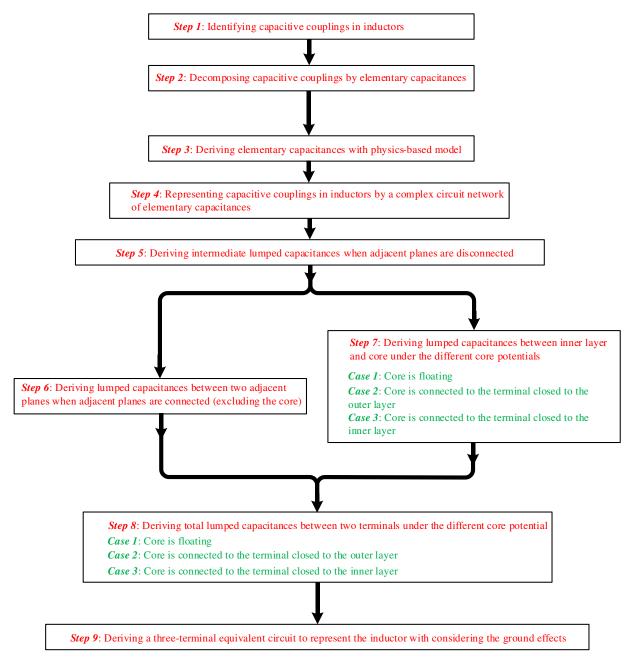

The step-by-step modeling processes of the proposed analytical modeling method are given in Fig. 6.

In Fig. 6, Step 1) - 4) can be obtained by using the previous modeling methods introduced in Section III. The processes of Step 5) - 9) are given in detail as follows.

# A. Step 5) Deriving the intermediate lumped capacitances when adjacent planes are disconnected

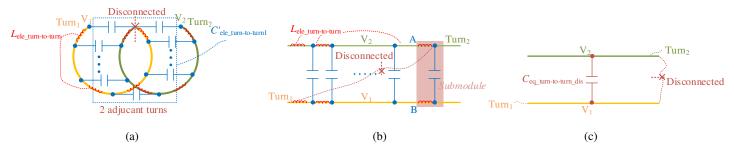

Fig. 7(a) is the equivalent circuit of the capacitive coupling between two neighbor turns with elementary capacitance and inductance, where the two neighbor turns are assumed to be disconnected. The equivalent circuit in Fig. 7(a) is simplified as Fig. 7(b). The impedance of the submodule is given as (9).

$$Z_{AB} = j\omega L_{\text{ele\_turn-to-turn}} + \frac{1}{j\omega C_{\text{eq\_turn-to-turn\_wb\_dis}}}$$

(9)

For frequencies much smaller than the characteristic frequency, the submodule is simplified into a single capacitor, which is given as (10).

Fig. 6 A flowchart for the proposed physics-based modeling method

Fig. 7 Parasitic capacitance between two neighbor turns. a) Equivalent circuit; b) A simplification of the equivalent circuit; c) Equivalent circuit when frequency is much smaller than the characteristic frequency

$$Z_{\rm AB} \approx \frac{1}{j\omega C_{\rm eq\_turm-to-turm\_wb\_dis}},$$

$$f \ll \frac{1}{2\pi\sqrt{2L_{\rm eq\_turm-to-turm}C_{\rm eq\_turm-to-turm\_wb\_dis}}}$$

(10)

Therefore, the equivalent circuit can be simplified as Fig. 7(c), which is represented by a single capacitor. Then the intermediate lumped capacitance between two neighbor turns when disconnected can be presented as

$$C_{\text{eq\_turn-to-turn\_dis}} = n \times C_{\text{eq\_turn-to-turn\_wb\_dis}}$$

$$= l_{\text{turn}} \times C'_{\text{ele turn-to-turn1}}$$

(11)

where  $l_{\text{turn}}$  is the length of a single turn.

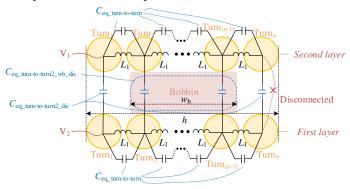

The equivalent circuit between two neighbor layers is presented in Fig. 8, where partial layers (red region in Fig. 8) are inserted with bobbins in between. The width of the bobbin is labeled as  $w_b$ , where the width of a layer is labeled as h.  $L_1$  is the equivalent inductance per turn.

Fig. 8 Equivalent circuit of the parasitic capacitance between two layers

The equivalent capacitances per turn with and without layers are given as (12). Where, x is the ratio of turns that have bobbins between the adjacent layers, and y is the ratio of turns that only have air between the adjacent layers.

$$C_{\text{eq\_turn-to-turn2\_dis}} = C'_{\text{ele\_turn-to-turn2}} \times l_{\text{turn}} \times x$$

$$C_{\text{ea turn-to-turn2 wb dis}} = C'_{\text{ele turn-to-turn2 wb}} \times l_{\text{turn}} \times y$$

(12)

Here  $x = w_b/h$  and  $y = 1-w_b/h$ .

Similarly, the intermediate lumped capacitance between the two layers when disconnected is obtained as (13) when the frequency is much smaller than the characteristic frequency.

$$C_{\rm eq\_layer-to-layer\_dis} = n \times (C_{\rm eq\_turn-to-turn2\_dis} + C_{\rm eq\_turn-to-turn2\_wb\_dis}),$$

$$f \ll \min \left[ \frac{1}{2\pi \sqrt{L_1 C_{\text{eq\_turn-to-turn2\_dis}}}}, \frac{1}{2\pi \sqrt{L_1 C_{\text{ele\_turn-to-turn2\_wb\_dis}}}} \right], \frac{1}{2\pi \sqrt{L_1 C_{\text{eq\_turn-to-turn2\_dis}}}}$$

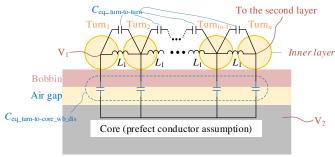

The equivalent circuit between the inner layer and the core is presented in Fig. 9. The equivalent capacitance per turn between the inner layer and core is presented as (14).

$$C_{\text{eq turn-to-core wb dis}} = C'_{\text{ele turn-to-core wb}} \times l_{\text{turn}}$$

(14)

Fig. 9 Equivalent circuit of the parasitic capacitance between the inner layer and core

The intermediate lumped capacitance between the inner layer and core when disconnected is obtained as (15) when the frequency is much smaller than the characteristic frequency.

$$C_{\text{eq\_layer-to-core\_dis}} = n \times C_{\text{eq\_turn-to-core\_wb\_dis}},$$

$$f \ll \min \left[ \frac{1}{2\pi \sqrt{L_1 C_{\text{eq\_turn-to-turn\_dis}}}}, \frac{1}{2\pi \sqrt{L_1 C_{\text{eq\_turn-to-core\_wb}}}} \right]$$

(15)

The equivalent circuit between the two windings is presented in Fig. 10. The equivalent capacitance per turn between the two windings is presented as (16).

$$C_{\text{eq\_turn-to-turn3\_dis}} = C'_{\text{ele\_turn-to-turn3}} \times l_{\text{turn}}$$

(16)

The intermediate capacitance between the two windings when disconnected is presented as (17) when the frequency is much smaller than the characteristic frequency.

$$\begin{split} &C_{\rm eq\_wingding-to-winding\_dis} = n \times C_{\rm eq\_turn-to-turn3\_dis}\,, \\ & \text{for} \, f \, \ll \min \left[ \frac{1}{2\pi \sqrt{L_1 C_{\rm eq\_turn-to-turn3\_dis}}}, \frac{1}{2\pi \sqrt{L_1 C_{\rm eq\_turn-to-turn3\_dis}}} \right] \end{split}$$

The obtained intermediate capacitances will be further used in the following derivations.

Fig. 10 Equivalent circuit of the parasitic capacitance between two windings

B. Step 6) Deriving lumped capacitances between two adjacent planes when adjacent planes are connected (excluding the core)

In this step, the adjacent planes are connected, and thus the voltage potential on each plane is assumed to be linearly distributed. With the intermediate lumped capacitance obtained in *Step 5*), the energy stored in the electric field of two connected adjacent planes can be derived, which is then used to calculate the lumped capacitance seen from terminals of planes, based on the former derivations by using the energy-conservation law.

- The total lumped turn-to-turn capacitance is calculated in (5) by substituting (11).

- The total lumped winding-to-winding capacitance is given in (6) by substituting (17). This method is also adapted to the inductors with multiple windings.

- The total lumped layer-to-layer capacitance is given in (7) by substituting (13).

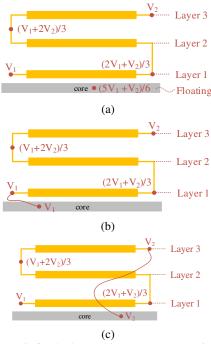

# C. Step 7) Deriving lumped capacitance between the inner layer and core under different core potentials

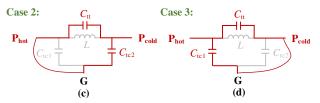

Three cases of the inductor with three different voltage potentials on the core are analyzed.

In this step, it is assumed that the voltage potential on the core is distributed equally. For the inductors with multi-layer winding structure, the terminal at the outer layer has less capacitive couplings to the core due to larger coupling distance, and hence the terminals at the inner layer and outer layer are characterized separately. The hot terminal and cold terminal are defined here, where the terminal closest to the inner layer is named as hot terminal, and the terminal closest to the outer layer is named as cold terminal. The voltage potential of the hot terminal is defined as  $V_1$ , while the voltage potential of the cold terminal is defined as  $V_2$ .

The lumped capacitances between the inner layer and core are discussed in three cases below:

- Case 1: The core is assumed to be floating. Then, the voltage potential on the core is equal and assumed to be the average value of the potential in the inner layer. The derived capacitance is already given as (8).

- Case 2: The core is connected to the hot terminal, which is presented as Fig. 11(a). Since the voltage potential of the hot terminal is V<sub>1</sub>, the potential on the core is equal and clamped to V<sub>1</sub>. The derived equation is presented as (18).

$$C_{\text{eq\_layer-to-core 2}} = 2 \times \frac{1}{3m^2} \times C_{\text{eq\_layer-to-core\_dis}}$$

(18)

Case 3: The core is connected to the cold terminal, which is presented as Fig. 11(b). Since the voltage potential of the cold terminal is V<sub>2</sub>, the potential on the core is equal and clamped to V<sub>2</sub>. The derived equation is given as (19).

$$C_{\text{eq\_layer-to-core3}} = 2 \times \frac{3m^2 - 3m + 1}{3m^2} \times C_{\text{eq\_layer-to-core\_dis}}$$

(19)

(18) and (19) can be solved by substituting (15). The detailed derivation process of (18) and (19) is attached in Appendix d.

Fig. 11 Schematic of the inner layer and core with different configurations. a) Case 2: core is clamped to the hot terminal; b) core is clamped to the cold terminal

# D. Step 8) Deriving total lumped capacitance between two terminals under different core potential

Based on the energy-conservation law, the total lumped capacitances represent the total electrical field energy stored in the inductor, which is composed of the electric field energy stored in between neighbor turns, neighbor layers, neighbor windings, and the inner layer to core. Therefore, the total lumped capacitances  $C_{\text{total1}}$ ,  $C_{\text{total2}}$ , and  $C_{\text{total3}}$  between the two terminals of the inductor in the three cases are calculated as (20), which is a sum of the derived lumped turn-to-turn, layer-to-layer, winding-to-winding, and layer-to-core capacitances.

In (20), for the inductors with single-layer windings, the calculated total capacitances  $C_{\text{total2}}$  and  $C_{\text{total3}}$  should be the same due to the symmetrical structure. However, for the inductors with multi-layer windings,  $C_{\text{total2}}$  and  $C_{\text{total3}}$  are different due to the voltage potential difference between the inner layer and core, respectively.

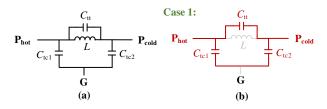

# E. Step 9) Deriving total lumped capacitance between two terminals under different core potential

Since the lumped total capacitance is dependent on three different core potentials, it is still not straightforward to understand the capacitive couplings between the two terminals and core, especially when the core is grounded. Therefore, a three-terminal equivalent circuit presented in Fig. 12(a) is

Case 1: The core is floating

$$C_{\text{total1}} = C_{\text{eq\_turn-to-turn}} + C_{\text{eq\_layer\_to\_layer}} + C_{\text{eq\_layer\_to\_core1}} + C_{\text{eq\_winding\_to\_winding}}$$

Case 2: The core is clamped to  $V_1$

$$C_{\text{total2}} = C_{\text{eq\_turn-to-turn}} + C_{\text{eq\_layer\_to\_layer}} + C_{\text{eq\_layer\_to\_core2}} + C_{\text{eq\_winding\_to\_winding}}$$

(20) Case 3: The core is clamped to  $V_2$

$$C_{\text{total3}} = C_{\text{eq\_turn-to-turn}} + C_{\text{eq\_layer\_to\_layer}} + C_{\text{eq\_layer\_to\_core3}} + C_{\text{eq\_winding\_to\_winding}}$$

Fig. 12 Derivation of the three-terminal equivalent circuit schematic. (a) is the schematic. (b), (c) and (d) are the representation of three cases with different terminal connections.

introduced to account for the couplings, which is based on the derived total lumped capacitances in three different cases.

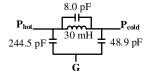

In the three-terminal equivalent circuit, the cold terminal of the inductor is represented by  $P_{cold}$ , the hot terminal is represented by  $P_{hot}$ , and the ground point of the frame/core is represented by G.  $L_1$  is the equivalent inductance.  $C_{tt}$  represents the coupling capacitance between  $P_{cold}$  and  $P_{hot}$ .  $C_{tc1}$  represents the coupling capacitance between  $P_{hot}$  and  $P_{hot}$ .  $P_{tc2}$  represents the coupling capacitance between  $P_{cold}$  and  $P_{tc2}$  represents the coupling capacitance between  $P_{cold}$  and  $P_{tc2}$ .

The mathematical transformation can be formulated by mapping the three cases to a practical three-terminal equivalent circuit in the low-frequency range:

- Case 1 is represented by the equivalent circuit in Fig. 12(b), where the ground point and the core are floating as well.

- Case 2 is modeled as the equivalent circuit in Fig. 12(c), where the ground point is connected to the hot terminal, which means  $C_{tc1}$  is shorted in this case.

- Case 3 is modeled as the equivalent circuit in Fig. 12(d), where the ground point is connected to the cold terminal, implying that  $C_{\rm tc2}$  is shorted in this case.

Consequently, the total equivalent capacitances can be obtained as below

$$\begin{cases}

C_{\text{total1}} = C_{\text{tt}} + (C_{\text{tc1}} / / C_{\text{tc2}}) \\

C_{\text{total2}} = C_{\text{tt}} + C_{\text{tc2}} \\

C_{\text{total3}} = C_{\text{tt}} + C_{\text{tc1}}

\end{cases}$$

(21)

For the inductors with multi-layer windings,  $C_{tc1}$  and  $C_{tc2}$  are not equal, due to the different value  $C_{total2}$  and  $C_{total3}$  of inductors

with a multi-layer structure. Therefore, the capacitances of equivalent circuits are unbalanced in cases of the inductor with multi-layer windings. It is worth mentioning that the three-terminal equivalent circuit is obtained mathematically, where a negative capacitance may result in the calculation.

#### V. MODEL VALIDATIONS

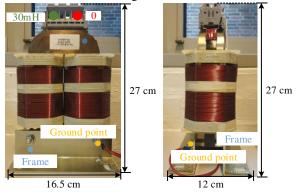

By using the explicit equations derived from the proposed physics-based modeling method, the parasitic capacitances of a 30 mH MV filter inductor are calculated theoretically based on the geometrical structure and material information of the researched inductor. The pictures of the researched 30 mH MV filter inductor are shown in Fig. 13.

Fig. 13 Pictures of the researched MV inductor

#### A. Theoretical calculations

Based on the derived equations (1)-(21) and physical parameters, the lumped turn-to-turn, layer-to-layer, layer-to-core, and winding-to-winding capacitance, and total lumped capacitances for three cases are calculated, which are listed in Table III. It is worth to mention that the electrical field energy stored between two windings is zero since the voltage potential on  $P_1P_3$  and  $P_2P_4$  are the same in this case.

By using the calculated values of the three capacitances for three cases presented in Table III, the three-terminal equivalent circuit is derived based on (21), which is given in Fig. 14. It is worth to mention that the equivalent capacitance between the  $P_{\text{hot}}$  and G is different from the equivalent capacitance between the  $P_{\text{cold}}$  and G.

The valid frequency range of the designed MV inductors for using the proposed physical-based lumped-parameter model is calculated as (22) based on the minimum characteristic frequency given in (10), (13), (15) and (17).

Table III Total parasitic equivalent capacitance for the three different cases

| Case      | Description           | Equivalent turn-to- | Equivalent layer-to- | Equivalent layer-to- | Equivalent winding-to- | Total       |

|-----------|-----------------------|---------------------|----------------------|----------------------|------------------------|-------------|

|           | Description           | turn capacitance    | layer capacitance    | core capacitance     | winding capacitance    | capacitance |

| Case1     | G is floating         |                     |                      | 2.72 pF              |                        | 48.76 pF    |

| Case2 G i | G is connected to the | o the               |                      | 98 pF 10.86 pF       |                        | 56.90 pF    |

|           | $P_{cold}$            | 0.06 pF             | 45.98 pF             |                      | 0 pF                   |             |

| Case3     | G is connected to the |                     |                      | 206.5 pF             |                        | 252.54 pF   |

|           | Phot                  |                     |                      | 200.5 pr             |                        | 232.34 pr   |

## $f \ll 6.8 \text{ MHz}$ (22)

Fig. 14 Three-terminal equivalent circuit for the researched MV inductor

# B. Experimental verifications

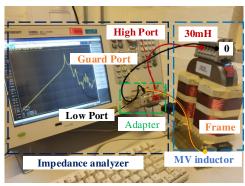

In order to verify the calculated parasitic capacitances of the designed inductor, the experimental results are carried out in this section. The parasitic capacitances of the three different cases are measured directly or indirectly by using a Keysight E4990A impedance analyzer and its adapter 16047. The measurement principle is based on the auto-balancing bridge method [36]. Both measurement methods with and without guarding technology are utilized to validate the theoretical analysis, where the setup is shown in Fig. 15. The principles and measurement processes for these two measurement methods are well described in [36].

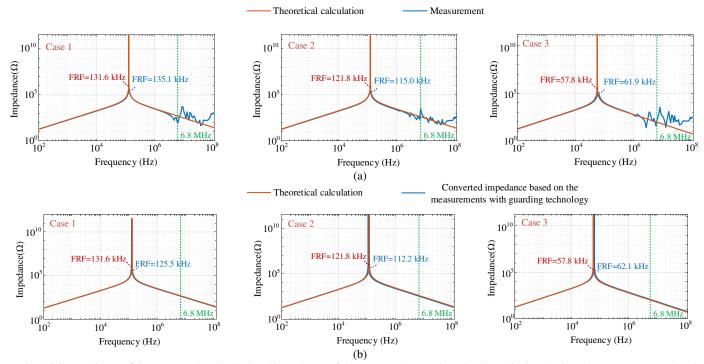

Fig. 16 shows the comparisons between the impedance measurement using the traditional measurement method, the guarding technology, and the theoretically obtained impedance, which is derived with the known value of designed inductance (30mH) paralleled with the calculated parasitic capacitance. The measured parasitic capacitance is obtained with fitting by using an equivalent circuit in the impedance analyzer. Fig. 16(a) is the comparison between the measured impedance and theoretically calculated impedance.

Fig. 15 The impedance measurement setup by using the Keysight E4990A and its adapter 16047

Since the guarding technology is a three-terminal measurement method, where each impedance of the equivalent three-terminal circuit is measured directly and individually. The measured three different capacitances are converted into the total equivalent capacitances Case1, Case 2, and Case 3 by following (20). The calculated impedance shows good agreement with measured impedance at the resonant point before the calculated valid frequency range. Fig. 16(b) is the comparison between the theoretically calculated impedance and converted impedance based on the measurements with the guarding method. In Fig. 16, since the damping resistances are not modeled in the theoretical calculations and converted impedance, both of them have an infinte magnitude at the first resonant frequency (FRF).

The valid frequency range should be much smaller than 6.8 MHz, which is verified in Fig. 16 as well. The unbalanced terminal-to-ground capacitances of inductors with multiple

Fig. 16 Comparisons of the measured and calculated impedance of three cases. a) Based on the theoretical analysis and measurement methods without using guarding technology. b) Based on the theoretical analysis and calculations by measurements with the guarding technology

Table IV Numerical comparisons of parasitic capacitances between the measurements and calculations

| Case                              | Calculations<br>(Proposed method)                                       | Calculations<br>(method [19]) | Calculations<br>(method [18]) | Measured capacitance<br>(Normal measurements)      | Converted capacitance based on the measurements with guarding method |

|-----------------------------------|-------------------------------------------------------------------------|-------------------------------|-------------------------------|----------------------------------------------------|----------------------------------------------------------------------|

| Case 1                            | 48.76 pF (C <sub>total1</sub> )                                         | 27.63 pF                      | 43.22 pF                      | 49.9 pF                                            | 53.6 pF                                                              |

| Case 2                            | 56.90 pF (C <sub>total2</sub> )                                         | Not valid                     | Not valid                     | 63.0 pF                                            | 67.1 pF                                                              |

| Case 3                            | 252.54 pF (C <sub>total3</sub> )                                        | Not valid                     | Not valid                     | 230.1 pF                                           | 218.9 pF                                                             |

| Two-terminal equivalent circuit   | 48.76 pF Phot Pcold 30 mH                                               | 27.63 pF Phot Pcold 30 mH     | 43.22 pF Phot 30 mH Pcold     | 49.9 pF Phot The Pcold                             | Phot 30 mH Pcold                                                     |

| Three-terminal equivalent circuit | P <sub>hot</sub> P <sub>cold</sub> P <sub>cold</sub> 244.5 pF G 48.9 pF | Not valid                     | Not valid                     | P <sub>hot</sub> 6.5 pF P <sub>cold</sub> 212.4 pF | P <sub>hot</sub> 1.2 pF P <sub>cold</sub> 228.9 pF 30 mH 61.8 pF     |

layers are also predicted by the proposed modeling method according to Fig. 16 since the FRF in Case 2 and Case 3 are not equal.

#### C. Comparisons and error analysis

The results calculated by using the proposed modeling method and the other two analytical energy-conservation based modeling methods are compared with the measurements in Table IV.

It can be found that the two typical modeling methods are only valid in Case 1, where the proposed modeling method has the least error ts around 2% using the normal measurements and 15% using the guarding technology. As expected, [18] and [19] can only characterize a two-terminal equivalent circuit for the inductors.

In Case 2 and 3, the calculations of using the proposed modeling method are close to the measurement results, where the maximum errors are 10% with using the normal measurements and 15% with using the guarding technology. It is worth noticing that the calculations are based on purely geometrical input and material parameter estimates and thus are not fitted to any measurements. Therefore, the errors are acceptable since the absolute value is still in the pF level. Multiple reasons might be responsible for the errors:

- The value of relative permittivity bobbin and coating material has a direct impact on results.

- Geometrical errors might arise from deviations of the idealized winding structure in Fig. 1 relative to the practical inductor.

- The assumptions made for simplifying the modeling will influence the final results. For example, the voltage potential is assumed to be distributed linearly on the conductor, which might not be realistic. However, these assumptions are compromises between the complexity and accuracy of models.

- The measurement methods can introduce errors to themselves. As can be seen from Table IV, the maximum error between two different measurement results is up to 5%.

#### VI. CONCLUSIONS

This paper has discussed a physics-based modeling method for calculating parasitic capacitances in inductors with considering the ground effects. Instead of using empirical equations, a computationally efficient approach to calculating the lumped capacitances between the adjacent layers, turns, windings, as well as the inner layer and core, has been introduced. Furthermore, a three-terminal equivalent circuit has been developed, which enables to characterize the capacitive couplings between two terminals of inductors and the capacitive couplings between the terminal and core. The measurements on a commercial MV filter inductor have been shown. The results verified the correctness of the proposed modeling method, where the unbalanced capacitances between the terminals and ground of inductors are revealed.

#### APPENDIX

Derivation of the lumped capacitance when the adjacent planes are connected

# a) Lumped turn-to-turn capacitance

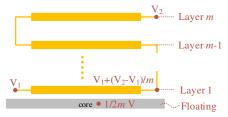

Using a winding with three turns as an example in Fig. a1, the voltage potential at  $P_0$ ,  $P_1$ ,  $P_2$ , and  $P_3$  are  $V_1$ ,  $(2V_1+V_2)/3$ ,  $(V_1+2V_2)/3$ , and  $V_2$ , respectively.

Fig. a1 Schematic for the lumped turn-to-turn capacitance of three turns (example) with linear voltage potential distribution. The lumped turn-to-turn capacitance is derived according to (a1).

Fig. b1 Schematic for the equivalent lumped capacitance of dual windings with linear voltage potential distribution

$$\begin{split} W_{\text{E-field}} &= \frac{1}{2} C_{\text{eq\_turn-to-turn}} (V_2 - V_1)^2 \\ W_{\text{E-field}} &= \frac{C_{\text{eq\_turn-to-turn\_dis}}}{6} \left( (\frac{2V_1 + V_2}{3} - V_1)^2 + (\frac{2V_1 + V_2}{3} - V_1) \times \right. \\ &\left. (\frac{V_1 + 2V_2}{3} - \frac{2V_1 + V_2}{3}) + (\frac{V_1 + 2V_2}{3} - \frac{2V_1 + V_2}{3})^2 \right) + \\ &\left. \frac{C_{\text{eq\_turn-to-turn\_dis}}}{6} \left( (\frac{V_1 + 2V_2}{3} - \frac{2V_1 + V_2}{3})^2 + \right. \right. \\ &\left. (\frac{V_1 + 2V_2}{3} - \frac{2V_1 + V_2}{3}) \times (V_2 - \frac{V_1 + 2V_2}{3}) + \right. \\ &\left. (V_2 - \frac{V_1 + 2V_2}{3})^2 \right) \\ &= \frac{C_{\text{eq\_turn-to-turn\_dis}} (V_2 - V_1)^2}{9} \\ &C_{\text{eq\_turn-to-turn\_dis}} \left( \frac{V_2 - V_1}{3} \right)^2 \end{split}$$

For general cases considering the winding with  $m \times n$  turns, the lumped capacitance contributed by turns is presented as

$$C_{\text{eq\_turn-to-turn}} = \frac{nm-1}{(nm)^2} C_{\text{eq\_turn-to-turn\_dis}}$$

(a3)

#### b) Lumped winding-to-winding capacitance

The lumped winding-to-winding capacitance is represented by the electrical field energy stored in between the two windings. Fig. b1 gives an example to illustrate it. It is found that the lumped capacitance is determined by the potential difference between the two windings in the efficient area.

However, the potential is fully determined by the winding layout. It is assumed that the potential difference between  $P_1$  and  $P_2$  is  $\Delta v_1$ , and the potential difference between the  $P_3$  and  $P_4$  is  $\Delta v_2$ . n is the number of total turns.  $(x_1 - x_2)$  is equal to  $(y_1 - y_2)$  because the voltage potential is distributed evenly in the winding.

The total electrical-field energy stored between the two windings are presented as (b1).

Therefore, the lumped winding-to-winding capacitance is obtained according to (b1).

$$W_{\text{E-field}} = \frac{1}{2} C_{\text{eq\_winding\_to\_winding}} (V_2 - V_1)^2$$

$$W_{\text{E-field}} = \frac{C_{\text{winding-to-winding}}}{6} \left( \left( \frac{\Delta v_1}{n} \right)^2 + \left( \frac{\Delta v_1}{n} \right) \right)$$

$$\times \left( \frac{\Delta v_2}{n} \right) + \left( \frac{\Delta v_2}{n} \right)^2 \right) \times \frac{n}{m}$$

(b1)

$$C_{\text{eq\_winding\_to\_winding}} = \frac{(\Delta v_1^2 + \Delta v_2^2 + \Delta v_1 \Delta v_2)}{3nm(V_2 - V_1)^2} C_{\text{eq\_winding\_to\_winding\_dis}}$$

(b2)

If both  $\Delta v_1$  and  $\Delta v_2$  are equal to zero, then  $C_{\text{eq\_winding\_to\_winding}}$  is zero.

#### c) Lumped layer-to-layer capacitance

The variations of the core potential have impacts on the electrical-field energy stored between two adjacent layers since the potential of the winding is assumed to be distributed evenly.

By using the same schematic shown in Fig. c1 as an example, the total electrical-field energy between two adjacent layers is presented as (c1).

Fig. c1 Schematic for the lumped layer-to-layer capacitance of three conducted layers with linear voltage potage distribution

$$\begin{split} W_{\text{E-field}} &= \frac{1}{2} C_{\text{eq\_layer-to-layer}} (V_2 - V_1)^2 \\ W_{\text{E-field}} &= \frac{C_{\text{eq\_layer-to-layer\_dis}}}{6} \left( \left( \frac{(V_1 + 2V_2)}{3} - V_1 \right)^2 + \frac{(V_1 + 2V_2)}{3} - V_1 \right) \times 0 + 0^2 \right) + \frac{C_{\text{eq\_layer-to-layer\_dis}}}{6} \times \\ &\left( V_2 - \frac{(2V_1 + V_2)}{3} \right)^2 + (V_2 - \frac{(2V_1 + V_2)}{3}) \times 0 + 0^2 \right) \\ &= \frac{4C_{\text{eq\_layer-to-layer\_dis}} V_1^2}{27} \end{split}$$

The lumped layer-to-layer capacitance is derived according to (c2).

$$C_{\text{eq\_turn-to-turn}} = \frac{8}{27} C_{\text{eq\_turn-to-turn\_dis}}$$

(c2)

For general cases considering the winding with  $m \times n$  turns, the lumped capacitance contributed by turns is presented as

$$C_{\text{eq\_turn-to-turn}} = \frac{4(m-1)}{3m^2} C_{\text{eq\_turn-to-turn\_dis}}$$

(c3)

# d) Lumped layer-to-core capacitance

By using a winding with three layers as an example, the schematic of the winding is shown in Fig. d1. The potential at the hot terminal is assumed to be  $V_1$ , and the potential at the

cold terminal is assumed to be  $V_2$ . Three different cases with different voltage potential of core are as follows:

Case 1: The core is floating. In this case, the core is closer to the inner winding, thus the potential of the core is an approach to  $(0+V_1/3)/2$ .

Case 2: The core is connected to the start point. Therefore, the potential of the core is clamped to  $V_1$ .

Case 3: The core is connected to the end point. Therefore, the potential of the core is clamped to  $V_2$ .

The lumped layer-to-core capacitance of the three cases is different because of the potential difference between the inner layer and core.

#### Case 1:

The electrical-field energy stored between the inner layer and core for Case 1 shown in Fig. d1(a) is presented as (d1).

Fig. d1 Schematic for the lumped layer-to-core capacitance of three layers with linear voltage potential distribution on each layer and different voltage potential on core. a) Core is floating (core potential is  $(5V_1+V_2)/6$ ). b) Core is clamped to the hot terminal with  $V_1$ . c) Core is clamped to the cold terminal with  $V_2$ .

$$\begin{split} W_{\text{E-field}} &= \frac{1}{2} C_{\text{eq\_layer\_to\_core1}} (V_2 - V_1)^2 \\ W_{\text{E-field}} &= \frac{C_{\text{layer-to-core}}}{6} \left( (V_1 - \frac{(5V_1 + V_2)}{6})^2 + (V_1 - \frac{(5V_1 + V_2)}{6}) \right) \\ &\times (\frac{2V_1 + V_2}{3} - \frac{(5V_1 + V_2)}{6}) + (\frac{2V_1 + V_2}{3} - \frac{(5V_1 + V_2)}{6})^2 \right) \end{split} \tag{d1}$$

$$&= \frac{C_{\text{layer-to-core}} (V_2 - V_1)^2}{216}$$

By solving (d1), the lumped layer-to-core capacitance is presented as

$$C_{\text{eq\_layer\_to\_corel}} = \frac{1}{108} C_{\text{layer-to-core}}$$

(d2)

For general cases of a winding with m layers, the lumped layer-to-core capacitance in Case 1 is presented as

$$C_{\text{eq\_layer\_to\_corel}} = \frac{1}{12m^2} C_{\text{layer-to-core}}$$

(d3)

Case 2:

The total electrical-field energy stored between the inner layer and core for Case 2 shown in Fig. d1(b) is presented as (d4).

By solving the (d4), the lumped layer-to-core capacitance is presented as (d5).

For general cases of a winding with *m* layers, the lumped layer-to-core capacitance in Case 2 is presented as (d6).

$$W_{\text{E-field}} = \frac{1}{2} C_{\text{eq\_layer\_to\_core2}} (V_2 - V_1)^2$$

$$W_{\text{E-field}} = \frac{C_{\text{layer-to-core}}}{6} \left( (V_1 - V_1)^2 + (V_1 - V_1) \times (\frac{(2V_1 + V_2)}{3} - V_1) + (\frac{(2V_1 + V_2)}{3} - V_1)^2 \right)$$

$$= \frac{C_{\text{layer-to-core}} (V_2 - V_1)^2}{54}$$

(d4)

$$C_{\text{eq\_layer\_to\_core2}} = \frac{1}{27} C_{\text{layer-to-core}}$$

(d5)

$$C_{\text{eq\_layer\_to\_core2}} = \frac{1}{3m^2} C_{\text{layer-to-core}}$$

(d6)

Case 3:

The electrical-field energy stored between the inner layer and core for Case 3 shown in Fig. d1(c) is presented as

$$\begin{split} W_{\text{E-field}} &= \frac{1}{2} C_{\text{eq\_layer\_to\_core3}} (V_2 - V_1)^2 \\ W_{\text{E-field}} &= \frac{C_{\text{layer-to-core}}}{6} \left( (V_1 - V_2)^2 + (V_1 - V_2) \times (\frac{(2V_1 + V_2)}{3} - V_2) \right. \\ &\left. + (\frac{(2V_1 + V_2)}{3} - V_2)^2 \right) \\ &= \frac{19C_{\text{layer-to-core}} (V_2 - V_1)^2}{54} \end{split}$$

$$(d7)$$

By solving the (d7), the lumped layer-to-core capacitance is presented as

$$C_{\text{eq\_layer\_to\_core3}} = \frac{19}{27} C_{\text{layer-to-core}}$$

(d8)

For general cases of a winding with *m* layers, the lumped layer-to-core capacitance in Case 3 is presented as

$$C_{\text{eq\_layer\_to\_core3}} = \frac{3m^2 - 3m + 1}{3m^2} C_{\text{layer-to-core}}$$

(d9)

# REFERENCES

J. Casady, V. Pala, D. Lichtenwalner, E. Brunt, B. Hull and et al., "New generation 10 kV SiC power MOSFET and diodes for Industrial

- Applications," in Proc. Proceedings of PCIM Europe 2015, May 2015, pp. 96-103.

- [2] D. Rothmund, T. Guillod, D. Bortis and J. W. Kolar, "99% efficient 10 kV SiC-Based 7 kV/400 V DC transformer for future data centers," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 2, pp. 753-767, Jun. 2019.

- [3] J. Wang, R. Burgos, D. Boroyevich and Z. Liu, "Design and testing of 1 kV H-bridge power electronics building block based on 1.7 kV SiC MOSFET module," in Proc. 2018 International Power Electronics Conference, May 2018, pp. 3749-3756.

- [4] J. Casarin, P. Ladoux and P. Lasserre, "10kV SiC MOSFETs versus 6.5kV Si-IGBTs for medium frequency transformer application in railway traction," in Proc. 2015 International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles, Aachen, 2015, pp. 1-6.

- [5] B. Hu, X. Lyu, D. Xing, D. Ma, H. Brothers, R. Na and J. Wang, "A survey on recent advances of medium voltage silicon carbide power devices," in Proc. 2018 IEEE Energy Conversion Congress and Exposition, Sep. 2018, pp. 2420-2427.

- [6] N. Christensen, A. Jørgensen, D. Dalal, S. Sonderskov, S. Bęczkowski, C. Uhrenfeldt and S. Munk-Nielsen, "Common-mode current mitigation for medium voltage half-bridge SiC modules," in Proc. 2017 19th European Conference on Power Electronics and Applications, Sep. 2017, pp. 1-8.

- [7] T. Huber, A. Kleimajer and R. Kennel, "Ultra-low inductive power module design with integrated common-mode noise shielding," in Proc. 2017 19th European Conference on Power Electronics and Applications, Sep. 2017, pp. 1-9.

- [8] D. Dalal, N. Christensen, A. Jørgensen, J. Jørgensen, S. Bęczkowski, C. Uhrenfeldt and S. Munk-Nielsen, "Impact of power module parasitic capacitances on medium voltage SiC MOSFETs switching transients," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Early access, doi: 10.1109/JESTPE.2019.2939644.

- [9] C. DiMarino, B. Mouawad, C. Johnson, M. Wang, Y. Tan, G. Lu, D. Boroyevich and R. Burgos, "Design and experimental validation of a wire-bond-less 10 kV SiC MOSFET power module," *IEEE Journal of Emerging and Selected Topics in Power Electronics, Early access*, doi: 10.1109/JESTPE.2019.2944138.

- [10] A. Anurag, S. Acharya and S. Bhattacharya, "Gate drivers for high-frequency application of silicon-carbide MOSFETs: design considerations for faster growth of LV and MV applications," *IEEE Power Electronics Magazine*, vol. 6, no. 3, pp. 18-31, Sep. 2019.

- [11] X. Zhang, H. Li, J. Brothers, L. Fu, M. Perales, J. Wu and J. Wang, "A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15-kV SiC MOSFET," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 946-955, Sep. 2016.

- [12] H. Zhao, D. Dalal, J. Jørgensen, X. Wang, M. Bech, A. Jørgensen, S. Bęczkowski, C. Uhrenfeldt and S. Munk-Nielsen, "Behavioral modeling of ground current in filter inductors of medium-voltage SiC-MOSFET-based converters," in Proc. IEEE Applies Power Electronics Conference, Mar. 2020, accepted.

- [13] S. Acharya, A. Anurag, Y. Prabowo, and S. Bhattacharya, "Practical design considerations for MV LCL filter under high dv/dt conditions considering the effects of parasitic elements," in Proc. 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems, Jun. 2018, pp. 1-7.

- [14] Z. Ouyang and M. Andersen, "Overview of planar magnetic technology-fundamental properties," *IEEE Transactions on Power Electronics*, vol. 29, no. 9, pp. 4888-4900, Sep. 2014.

- [15] A. Anurag, S. Acharya, S. Bhattacharya and T. Weatherford, "Thermal performance and reliability analysis of a medium voltage three-phase inverter considering the influence of high dv/dt on parasitic filter elements," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Early access, doi: 10.1109/JESTPE.2019.2952570.

- [16] ANSYS, Inc., "ANSYS Q3D Extractor." [Online]. Available: http://www.ansys.com/products/electronics/ansys-q3d-extractor. Accessed on: Apr.19, 2018.

- [17] A. B. Jørgensen, S. Bęczkowski, C. Uhrenfeldt, N. H. Petersen, S. Jørgensen and S. Munk-Nielsen, "A fast-switching integrated full-bridge power module based on GaN eHEMT devices," *IEEE Transactions on Power Electronics*, vol. 34, no. 3, pp. 2494-2504, Mar. 2019.

- [18] Z. Shen, H. Wang, Y. Shen, Z. Qin and F. Blaabjerg, "An improved stray capacitance model for inductors," *IEEE Transactions on Power Electronics*, vol. 34, no. 11, pp. 11153-11170, Nov. 2019.

- [19] E. Snelling, SoftFerrites: Properties and Applications. London, U.K.: Iliffe Books Ltd., 1988.

- [20] P. Thummala, H. Schneider, Z. Zhang and M. Andersen, "Investigation of transformer winding architectures for high voltage (2.5 kV) capacitor charging and discharging applications," *IEEE Transactions on Power Electronics*, vol. 31, no. 8, pp. 5786-5796, Aug. 2016.

- [21] M. Zdanowski, K. Kostov, J. Rabkowski, R. Barlik and H. Nee, "Design and Evaluation of Reduced Self-Capacitance Inductor in DC/DC Converters with Fast-Switching SiC Transistors," *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2492-2499, May 2014.

- [22] J. Biela and J. W. Kolar, "Using transformer parasitics for resonant converters—A review of the calculation of the stray capacitance of transformers," *IEEE Transactions on Industry Applications*, vol. 44, no. 1, pp. 223-233, Jan.-Feb. 2008.

- [23] A. Massarini and M. K. Kazimierczuk, "Self-capacitance of inductors," IEEE Trans. Power Electron., vol. 12, no. 4, pp. 671–676, Jul. 1997.

- [24] A. Ayachit and K. Kazimierczuk, "Self-capacitance of single-layer inductors with separation between conductor turns," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 5, pp. 1642–1645, Sep. 2017.

- [25] G. Grandi, M. K. Kazimierczuk, A. Massarini and U. Reggiani, "Stray capacitances of single-layer solenoid air-core inductors," *IEEE Transactions on Industry Applications*, vol. 35, no. 5, pp. 1162-1168, Sept.-Oct. 1999.

- [26] S. Zhu, X. Yuan and P. Mellor, "Modelling of high-frequency effects of laminated iron-core power inductors and reduction of parasitic capacitance," *IECON 2017 - 43rd Annual Conference of the IEEE Industrial Electronics Society*, Beijing, 2017, pp. 1299-1306.

- [27] L. F. de Freitas Gutierres and G. Cardoso, "Analytical technique for evaluating stray capacitances in multiconductor systems: single-layer aircore inductors," *IEEE Transactions on Power Electronics*, vol. 33, no. 7, pp. 6147-6158, July 2018.

- [28] N. B. Chagas and T. B. Marchesan, "Analytical Calculation of Static Capacitance for High-Frequency Inductors and Transformers," *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1672-1682, Feb. 2010

- [29] IEEE standard for general requirements for dry-type distribution and power transformers, IEEE Standard C57.12.01-2015, 2015.

- [30] T. Guillod, F. Krismer, and J. W. Kolar, "Electrical shielding of MV/MF transformers subjected to high dv/dt PWM voltages," in Proc. IEEE Applied Power Electronics Conf. and Expo. (APEC), 2017, pp. 2502–2510.

- [31] LWW group, "Techincal data for winding wire," Jul., 2016. [Online]. Available: http://www.lww.se/wp-content/uploads/2017/06/LWW-brochure-2016.pdf

- [32] MICHAEL-KUNSTSTOFFETCHNIK, "Bobbins for cores: type for c-core," Nov., 2019. [Online]. Available: https://www.michael-kunststofftechnik.com/spulenkoerper-fuer-kerne-produkte.php?fthid=198

- [33] , LANXESS, "DURETHAN BKV 30 H-polyamide 6", May 2005. [Online]. Available: https://techcenter.lanxess.com/scp/americas/en/docguard/PIB\_Durethan\_BKV30H.pdf?docId=76997

- [34] The engineering toolbox, "Relative permittivity-the dielectric constant", Nov., 2019. [Online]. Available: <a href="https://www.engineeringtoolbox.com/relative-permittivity-d-1660.html">https://www.engineeringtoolbox.com/relative-permittivity-d-1660.html</a>

- [35] Wikipedia, "Vacuum permittivity", Sep. 2019. [Online]. Available: https://en.wikipedia.org/wiki/Vacuum\_permittivity

- [36] Keysight Technologies, "Keysight Technologies Impedance measurement handbook" [Online], Available: https://literature.cdn.keysight.com/litweb/pdf/5950-3000.pdf

Hongbo Zhao (S'16) received the B.S. degree in electrical engineering and its automation from Southwest Jiaotong University, Chengdu, China in 2015. He is currently working toward the Ph.D degree with Aalborg University, Aalborg, Denmark.

His research interests include mediumvoltage converters and their filters utilized by wide band-gap power devices.

power converters.

**Dipen Dalal** (S'19) received the M.Sc. degree in Energy Engineering with specialization in Power Electronics and Drivers from Aalborg University, Aalborg, Denmark in 2016. He is currently working towards the PhD degree at the Department of Energy Technology, Aalborg University.

His current research interests include wide band-gap power semiconductor devices and medium voltage high

**Asger Bjørn Jørgensen** received the M.Sc. and Ph.D. degrees in energy engineering from Aalborg University, Denmark, in 2016 and 2019, respectively.

He is currently working as a Postdoc at the Department of Energy Technology, Aalborg University. His research interests include power module packaging, wide bandgap power semiconductors and multi-physics finite element analysis within power electronic applications.

power modules.

Jannick Kjær Jørgensen received his M.Sc. degree in Nanotechnology with specialization in Nanomaterials and Nanophysics from Aalborg University, Aalborg, Denmark in 2018. He is currently working as a research assistant at the Department of Energy Technology, Aalborg university.

His research interests include packaging and modeling of wide-bandgap power semiconductor devices, and medium voltage

Xiongfei Wang (S'10-M'13-SM'17) received the B.S. degree from Yanshan University, Qinhuangdao, China, in 2006, the M.S. degree from Harbin Institute of Technology, Harbin, China, in 2008, both in electrical engineering, and the Ph.D. degree in energy technology from Aalborg University, Aalborg, Denmark, in 2013. Since 2009, he has been with the Department of Energy Technology, Aalborg

University, where he became an Assistant

Professor in 2014, an Associate Professor in 2016, a Professor and Research Program Leader for Electronic Power Grid (eGrid) in 2018, and the Director of Aalborg University-Huawei Energy Innovation Center in 2020. His current research interests include modeling and control of grid-interactive power converters, stability and power quality of converter-based power systems, active and passive filters.

Dr. Wang was selected into Aalborg University Strategic Talent Management Program in 2016. He has received six IEEE Prize Paper Awards, the 2016 Outstanding Reviewer Award of IEEE TRANSACTIONS ON POWER ELECTRONICS, the 2018 IEEE PELS Richard M. Bass Outstanding Young Power Electronics Engineer Award, the 2019 IEEE PELS Sustainable Energy Systems Technical Achievement Award, and the 2019 Highly Cited Researcher by Clarivate Analytics (former Thomson Reuters). He serves as a Member at Large for Administrative Committee of IEEE Power Electronics Society in 2020-2022, and as an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, and the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS.

**Szymon Bęczkowski** received the M.Sc. degree in electrical engineering from the Warsaw University of Technology, Poland, in 2007. In 2012, he received the Ph.D. degree from Aalborg University, Aalborg, Denmark.

He is currently working as Associate Professor at the Department of Energy Technology, Aalborg University. His research interests include optimization of power electronic converters, power module

packaging and SiC technology.

**Stig Munk-Nielsen** (S'92–M'97) received the M.Sc. and Ph.D. degrees from Aalborg University, Aalborg, Denmark, in 1991 and 1997, respectively.

He is currently Professor at the Department of Energy Technology, Aalborg University. His research interests include LV and MV Si, SiC and GaN converters, packaging of power electronic devices, electrical monitoring apparatus for IGBTs, failure modes and device test systems. In the last

ten years, he has been involved or has managed 10 research projects. Published 221 international power electronic papers being co-author or author.

Christian Uhrenfeldt received his M.Sc. in Physics from Aalborg University in 2004. In 2008 he received the Ph.D. degree in the field of semiconductor material science from Aarhus University. He is currently working as Associate professor at the Department of Energy Technology at Aalborg University on power electronics packaging and materials. His research interests include packaging of power modules, physics based modelling of

power electronic components and semiconductor diagnostics in power electronics.