# PHYSICS-BASED RELIABLITY ASSESSMENT OF EMBEDDED PASSIVES

A Dissertation

Presented to

The Academic Faculty

By

Manoj Kumar Damani

In Partial Fulfillment

Of the Requirements for the Degree

Masters of Science in Mechanical Engineering

Georgia Institute of Technology

July 2004

Copyright © 2004 by Manoj Kumar Damani

# PHYSICS-BASED RELIABLITY ASSESSMENT OF EMBEDDED PASSIVES

Approved by:

Dr. Suresh K. Sitaraman, Chair

Dr. Peter Hesketh

Dr. Manos Tentzeris

Dr. Swapan Bhattacharya.

July 12, 2004

## ACKNOWLEDGEMENTS

I would like to thank my advisor Dr. Suresh K. Sitaraman for his encouragement and support throughout my Master's program. His advice has helped me advance both academically and professionally. I would also like to thank Dr. Tentzeris, Dr. Hesketh and Dr. Bhattacharya for agreeing to be on my thesis committee.

I would like to thank Dr. Bhattacharya for his support and his insight throughout the project. His knowledge of passives was very helpful in helping me complete this project. In addition, I would like to thank Dr. Pucha for helping me on various aspects of my project. Some other CASPaR members I would like to thank are Jamie Ahmad, Andy Perkins, Krishna Tunga and Shashikant Hegde. Their detailed knowledge in many subjects helped me learn a lot about packaging. I would also like to thank PRC for their support in this project.

Finally I would like to thank my Dad and Mom for believing in me and encouraging me throughout the project. I would also like to thank my Sister, Pallavi and Brother-in-Law Nishant for their good wishes. I would like to dedicate this thesis to them.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSiii                                  |

|------------------------------------------------------|

| LIST OF FIGURESix                                    |

| LIST OF TABLESxii                                    |

| GLOSSARYxiii                                         |

| SUMMARYxvi                                           |

| CHAPTER I INTRODUCTION 1                             |

| SOP Concept                                          |

| Thermo-Mechanical Reliability of Integral Passives   |

| CHAPTER II BACKGROUND ON PERFORMANCE AND RELIABILITY |

| Electrical Performance                               |

| Modeling Capacitors                                  |

| Modeling Inductors                                   |

| Modeling Resistors                                   |

| Fabrication Of Passives15                            |

| Capacitors                                           |

| Physical Vapor deposition (PVD)16                    |

| Chemical Vapor Deposition (CVD)17                    |

| Anodization                                          |

| Solution-Based: Physical 20                          |

| Spin Coating                                         |

| Meniscus Coating                                                  | 21 |

|-------------------------------------------------------------------|----|

| Solution-Based - Chemical                                         | 22 |

| Sol-Gel Deposition                                                | 22 |

| Hydrothermal Deposition                                           | 23 |

| Photolithography                                                  | 24 |

| Commercialized Dielectric Materials for Capacitors                | 25 |

| DuPont Interra <sup>TM</sup>                                      | 26 |

| 3M C-Ply <sup>TM</sup>                                            | 27 |

| Resistors                                                         | 27 |

| Sputtering                                                        | 28 |

| Screen Printing                                                   | 28 |

| Ink Jet Deposition                                                | 29 |

| Commercialized Processes for Resistors                            | 30 |

| $Ohmega-Ply^{TM}$                                                 | 30 |

| DuPont Interra <sup>TM</sup>                                      | 30 |

| Shipley InSite <sup>TM</sup>                                      | 30 |

| Reliability Experiments                                           | 31 |

| Literature Review on passing qualifications for Embedded Passives | 33 |

| Literature Review on Qualification Tests of Embedded Passives     | 35 |

| Reliability Modeling                                              | 36 |

| Chapter III OBJECTIVES                                            | 38 |

| Gaps in Existing Research                                         | 39 |

| Chapter IV DESCRIPTION OF TEST VEHICLE      | 41 |

|---------------------------------------------|----|

| Test Vehicle Details                        | 41 |

| Fabrication Steps and Processing Conditions |    |

| Metal 1 Layer                               |    |

| Dielectric Layer                            |    |

| Metal 2 Layer                               |    |

| Resistor Layer                              | 50 |

| Solder Mask                                 | 51 |

| CHAPTER V MODELING OF INTEGRAL PASSIVES     | 54 |

| Material Modeling                           | 55 |

| Copper                                      | 55 |

| FR4                                         |    |

| DynaVia                                     |    |

| ViaLux <sup>TM</sup> 81                     | 60 |

| Modeling of Capacitors                      | 61 |

| Geometric Modeling                          | 61 |

| Parametric Modeling                         | 65 |

| Fabrication Process Modeling                | 65 |

| Electromagnetic Modeling                    |    |

| Modeling of Inductors                       | 71 |

| Geometric Modeling                          | 71 |

| Parametric Modeling                         | 73 |

| Electromagnetic Model74                                    |

|------------------------------------------------------------|

| CHAPTER VI THERMO-MECHANICAL MODELING OF INTEGRAI          |

| PASSIVES                                                   |

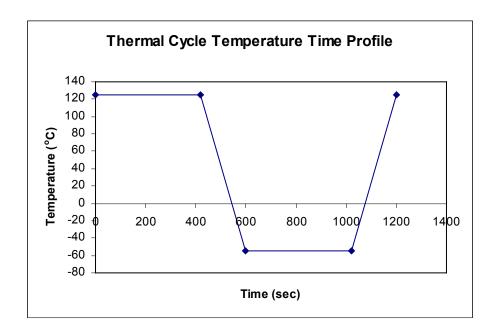

| Thermo-Mechanical Loading Conditions76                     |

| Thermal Cycling76                                          |

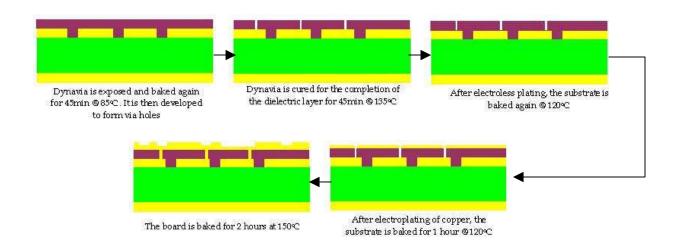

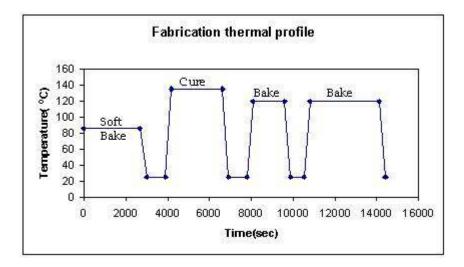

| Fabrication Process Profile72                              |

| FEA Methodology79                                          |

| Fabrication Process Methodology79                          |

| Thermal Cycling                                            |

| Thermal Cycling of Capacitors                              |

| Original Model                                             |

| Parametric Model                                           |

| Fabrication Process Deformation In Capacitors              |

| Thermal Cycling of Inductors                               |

| Parametric Model                                           |

| Effect of Materials on the Board                           |

| CHAPTER VII RELIABILITY EXPERIMENTS                        |

| Moisture Effect                                            |

| Air-to-Air Thermal Cycling92                               |

| Humidity Testing                                           |

| CHAPTER VIII PERFORMANCE OF INTEGRAL PASSIVES DURING FIELD |

| USE                                                        |

| Low Pass Filter                        |  |

|----------------------------------------|--|

| Experimental Results                   |  |

| FEA Results                            |  |

| Amplifier                              |  |

| Thermal Cycling                        |  |

| Humidity Testing                       |  |

| CHAPTER IX CONCLUSIONS AND FUTURE WORK |  |

| Conclusions                            |  |

| Contributions                          |  |

| Future Work                            |  |

| REFERENCES                             |  |

# LIST OF FIGURES

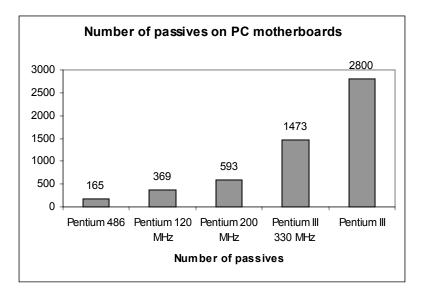

| Figure 1.1 Number of passives on PC motherboards                      | 2  |

|-----------------------------------------------------------------------|----|

| Figure 1.2. PRC's SOP Test vehicle                                    | 6  |

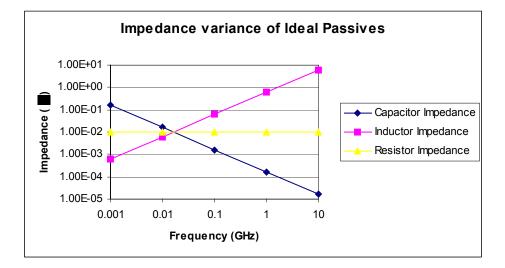

| Figure 2.1. Impedance variance of Ideal Passives with frequency       | 9  |

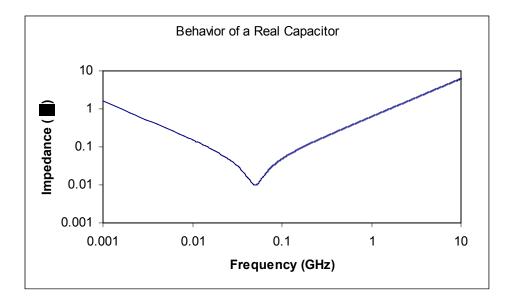

| Figure 2.2. Behavior of a real capacitor                              | 12 |

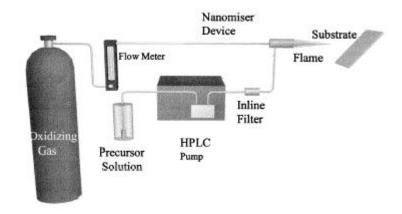

| Figure 2.3. Schematic of CCVD                                         | 18 |

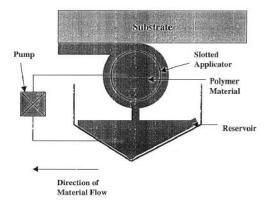

| Figure 2.4. Schematic of Meniscus coating                             | 21 |

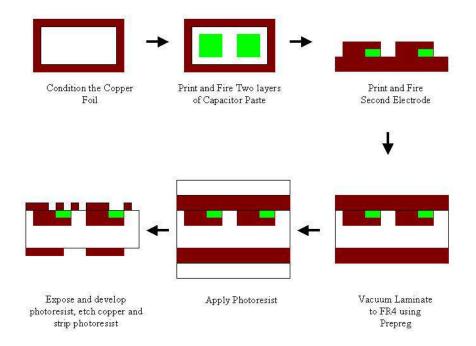

| Figure 2.5. Dupont Interra <sup>TM</sup> process                      | 27 |

| Figure 2.6. Droplets on Demand Ink Jet deposition                     | 29 |

| Figure 2.8. Shipley InSite <sup>TM</sup> process                      | 31 |

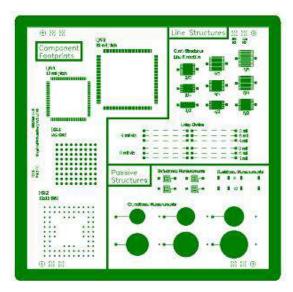

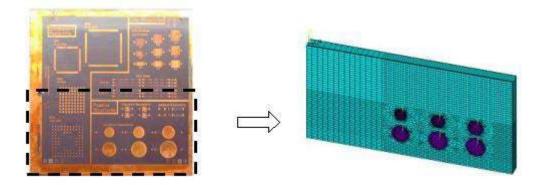

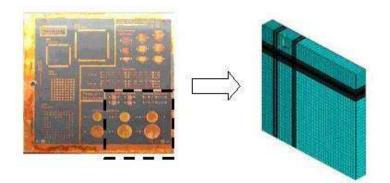

| Figure 4.1. Picture of the Test Board                                 | 42 |

| Figure 4.2. Bottom Metal Mask                                         | 45 |

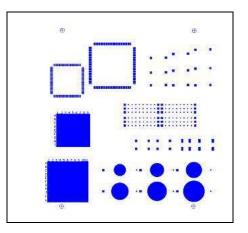

| Figure 4.3. Via Mask                                                  | 46 |

| Figure 4.4. Top Metal Mask                                            | 49 |

| Figure 4.5. Resistor Mask                                             | 51 |

| Figure 4.6. Solder Mask mask                                          | 52 |

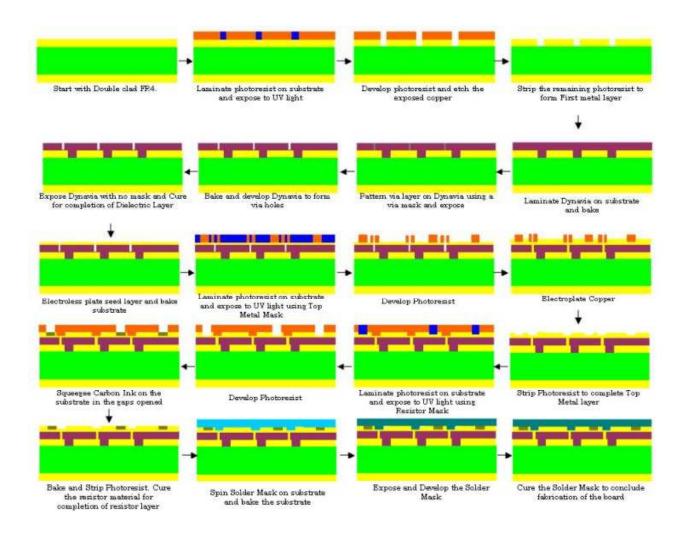

| Figure 4.7. Fabrication process of passives                           | 53 |

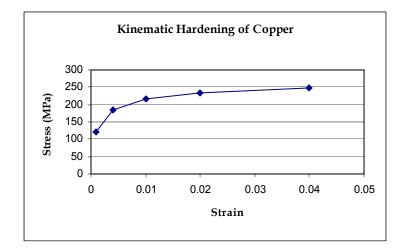

| Figure 5.1. Kinematic Hardening of Copper                             | 57 |

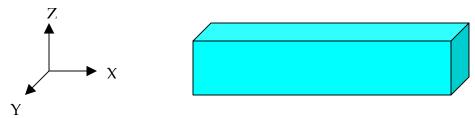

| Figure 5.2. Co-ordinate axis in ANSYS™                                | 57 |

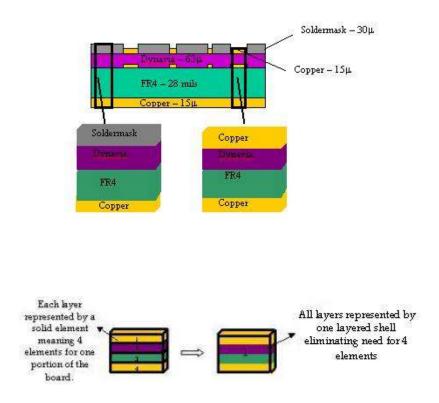

| Figure 5.3 Schematic of the board and an explanation of layered shell | 62 |

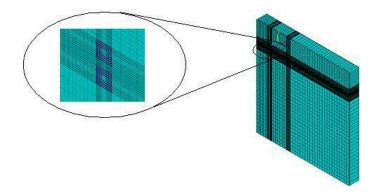

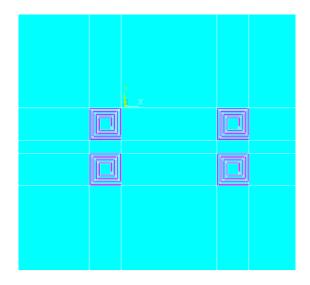

| Figure 5.4 FEA representations of capacitors                          | 63 |

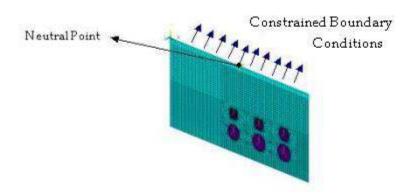

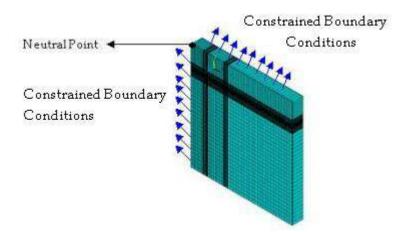

| Figure 5.5 Symmetry boundary conditions applied on the board.         | 63 |

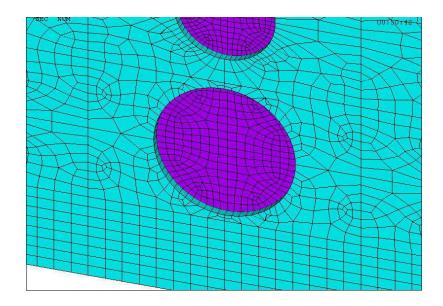

| Figure 5.6. Close up on the capacitors                                    | 64      |

|---------------------------------------------------------------------------|---------|

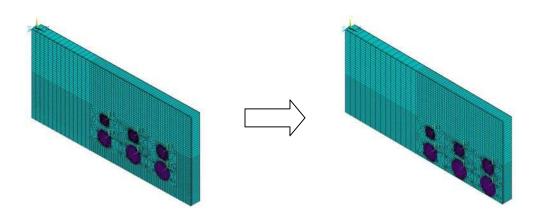

| Figure 5.7. Capacitor mesh moved through parameters                       | 65      |

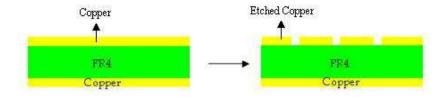

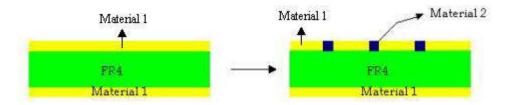

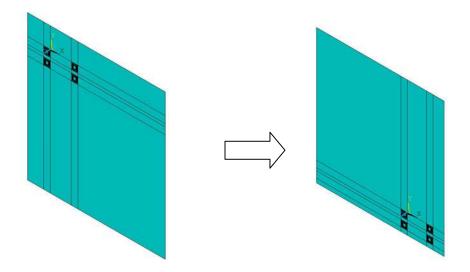

| Figure 5.8 (a). Etching away of copper during fabrication                 | 67      |

| Figure 5.8 (b). Etching away of copper represented in ANSYS <sup>TM</sup> | 67      |

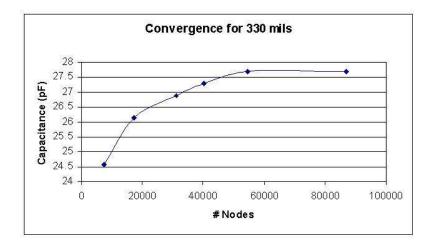

| Figure 5.8. Capacitance Convergence for 330 mils (8.25mm)                 | 70      |

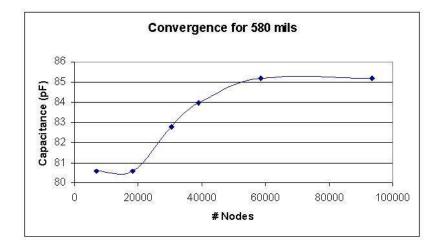

| Figure 5.9. Capacitance Convergence for 580 mils (14.5mm)                 | 70      |

| Figure 5.10. FEA representation of inductors                              | 72      |

| Figure 5.11. Zoomed view of the inductors on the board                    | 72      |

| Figure 5.12. Inductors as present on the board                            | 72      |

| Figure 5.13. Boundary Conditions on inductor model                        | 73      |

| Figure 5.14. Parametric models for inductors                              | 74      |

| Figure 5.15. Model of the Inductor in ANSYS <sup>TM</sup>                 | 75      |

| Figure 6.1. Load step used in thermal cycling of passives                 | 77      |

| Figure 6.2. Schematic of a part of the fabrication process in capacitors  | 78      |

| Figure 6.3. Thermal profile between the curing of the dielectric and plat | ting of |

| top metal layer                                                           | 79      |

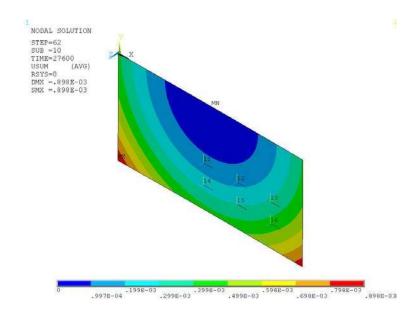

| Figure 6.4. Deformation in board after thermal cycling with capacitors    | 82      |

| Figure 6.5. Deformed capacitor furthest from the neutral point            | 82      |

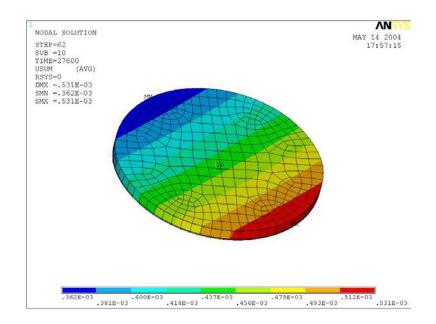

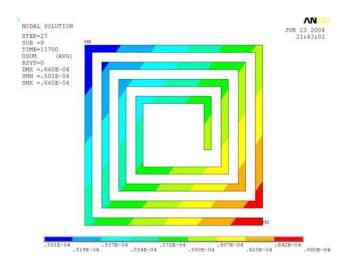

| Figure 6.6. Deformed Inductor after thermal cycling                       | 86      |

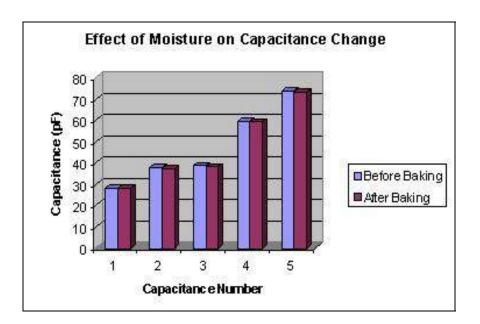

| Figure 7.1. Capacitance values after baking the board                     | 90      |

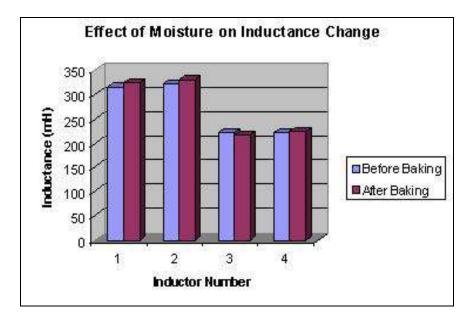

| Figure 7.2. Inductance values after baking the board                      | 91      |

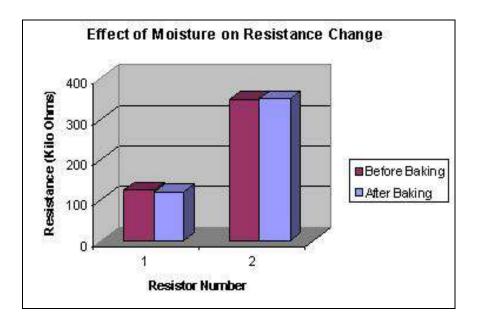

| Figure 7.3. Resistance values after baking the board                      | 91      |

| Figure 7.3. Picture of the Thermal Chamber used                   | 93            |

|-------------------------------------------------------------------|---------------|

| Figure 7.5. Change in capacitance after 1000 thermal cycles       | 94            |

| Figure 7.6. Change in inductance after 1000 thermal cycles        | 94            |

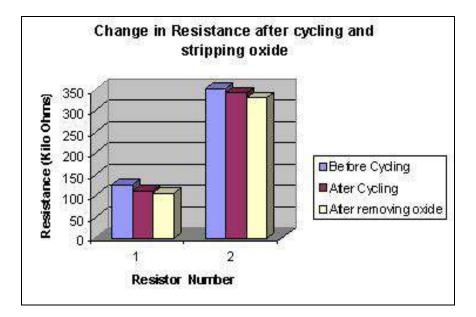

| Figure 7.7. Change in resistance after 1000 thermal cycles        | 95            |

| Figure 7.7. Humidity Chamber used                                 | 96            |

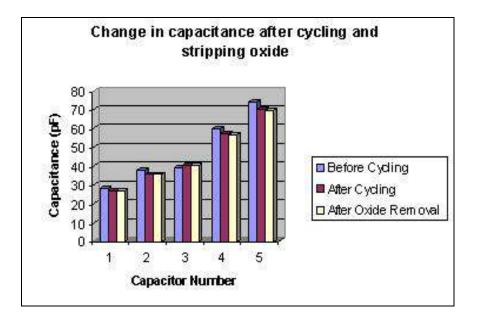

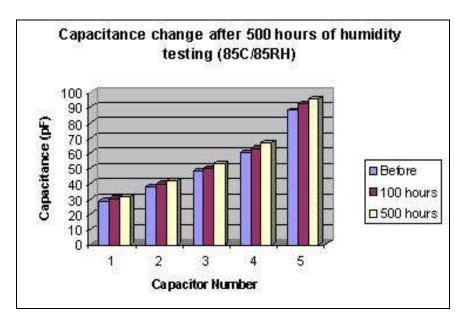

| Figure 7.9. Capacitance change after humidity testing             | 96            |

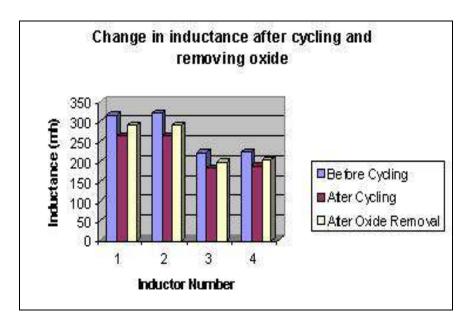

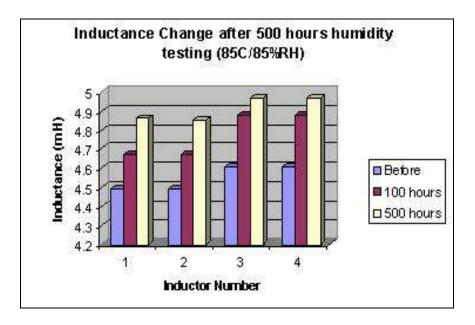

| Figure 7.10. Inductance change after humidity testing             | 97            |

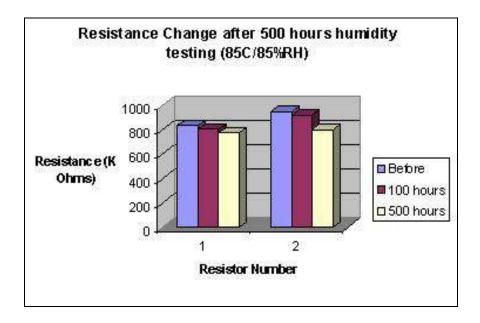

| Figure 7.11. Resistance change after humidity testing             | 97            |

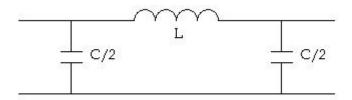

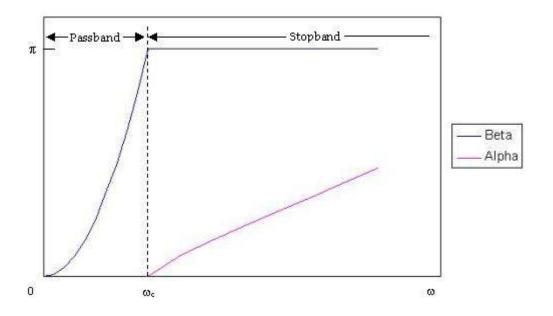

| Figure 8.1. Schematic of a low pass filter                        | 99            |

| Figure 8.2. Low pass filter characteristics                       | 100           |

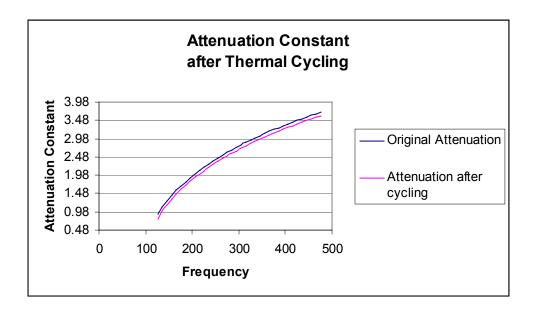

| Figure 8.3. Change in Attenuation constant after thermal cycling  | of the filter |

|                                                                   | 101           |

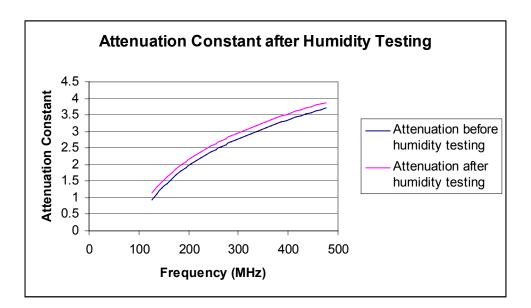

| Figure 8.4. Change in Attenuation constant after humidity testing | 102           |

|                                                                   |               |

| Figure 8.5. GaAs FET in the common source configuration | 104 |

|---------------------------------------------------------|-----|

|---------------------------------------------------------|-----|

# LIST OF TABLES

| Table 2.1. EIA temperature codes for dielectrics                     | . 34 |

|----------------------------------------------------------------------|------|

| Table 4.1. Materials used in the test board                          | . 42 |

| Table 4.2. Details of the capacitors                                 | . 43 |

| Table 5.1 Dependence of modulus on temperature [31]                  | 56   |

| Table 5.2 Kinematic Behavior of copper                               | 56   |

| Table 5.3. Properties of FR4 at 30°C                                 | 58   |

| Table 5.4. Viscoelastic Prony Parameters for DynaVia 2000            | 59   |

| Table 5.5. Viscoelastic Prony Parameters for ViaLux 81 <sup>TM</sup> | 60   |

| Table 5.6. Capacitance Convergence for 330 mils (8.25mm)             | 69   |

| Table 5.7. Comparison with simulated, actual and theoretical values  | of   |

| capacitance                                                          | . 71 |

| Table 6.1. Results from thermal cycling of capacitors                | 83   |

| Table 6.2. Change in parametrically further capacitors               | . 84 |

| Table 6.3. Results from the fabrication process simulation           | . 85 |

| Table 6.4. Results from the thermal cycling of inductors             | . 87 |

| Table 6.5. Results from the parametric modeling of inductors         | . 87 |

# GLOSSARY

Abbreviations

- CTE Coefficient of Thermal Expansion

- CVD Chemical Vapor Deposition

- DIP- Dual In line Package

- DNP Distance From Neutral Point

- FEA- Finite Element Analysis

- FEM Finite Element Model

- HDW High Density Wiring

- IC Integrated Circuits

- LTCC Low Temperature Co-fired Ceramic

- MCM Multi-chip module

- PC Personal Computer

- RF Radio Frequency

- RH Relative Humidity

- SMT Surface Mount Technology

- SOP System On Package

- TCC Temperature Coefficient of Capacitance

- TCR Temperature Coefficient of Resistance

- WLP Wafer Level Package

## Symbols

- °C Degrees Celsius

- C Capacitance

- E Elastic Modulus

- f frequency

- F Farad (unit of capacitance)

- nF Nano Farad (10<sup>-9</sup> Farad)

- pF Pico Farad (10<sup>-12</sup> Farad)

- G Shear Modulus

- GPa Giga Pascals (unit of stress)

- H Henry (unit of inductance)

- $\mu$ H Micro Henry (10<sup>-6</sup> H)

- k dielectric constant

- L Inductance

- mm millimeter

- MPa Mega Pascal (unit of stress)

- $\mu$  micro meter (10<sup>-6</sup> m)

- $\Omega$  Ohm (unit of resistance)

- $k\Omega$  Kilo Ohm (10<sup>3</sup> Ohms)

- Q factor Quality Factor

- R Resistance

- $\mu_r$  Relative Permeability

$T_{\rm g}$  – Glass Transition Temperature

## SUMMARY

Multilayer embedded passives (resistors, inductors, and capacitors) on a printed wiring board can help to meet high performance requirements at a low cost and at a smaller size. Such an integration of embedded passives has new challenges with respect to design, materials, manufacturing, thermal management and reliability. As the area of integral passives on printed circuit boards is relatively new, there is inadequate literature on the thermo-mechanical reliability of integral passives. Therefore, there is a compelling need to understand the thermo-mechanical reliability of integral passives through the development of physics-based models as well as through experiments, and this thesis aims to develop such an experimental and theoretical program to study the thermo-mechanical reliability of integral passives..

As integral passives are often composite layers with dissimilar material properties compared to the other layers in the integral substrate, it is essential to ensure that RLC characteristics of the embedded passives do not deteriorate with thermal cycling due to thermo-mechanical deformations. This thesis aims to study the changes in the passive characteristics due to the thermally-induced deformations. Embedded capacitors and inductors have been looked at specifically in this research. Multi-field physics-based models have been constructed to determine the change in electrical parameters after thermal cycling. The thermo-mechanical models assume direction-dependent material properties for the board substrate and interconnect copper layers and temperature-dependent properties for interlayer dielectric and passive layers. Using the deformed geometry, the electrical characteristics have been determined at low frequency. In parallel to the models, test vehicle substrates have been subjected to 1000 thermal cycles between -55°C to 125°C and high humidity and temperature conditions at 85°C/85RH for 500 hours, and it has been observed that there are significant changes in the electrical parameters. The results obtained from the physics-based simulations have been validated against the measured electrical characteristics from the fabricated functional test boards that have been thermal cycled.

# CHAPTER I

# INTRODUCTION

The past four decades have seen tremendous progress in the field of system level packaging with IC packaging technology progressing from the dualin-line package (DIPs) to the wafer-level-package (WLPs). However, there is another area in packaging that has not received that much attention as IC's. This is the group of passive elements and the advancements have been comparatively marginal in size and density. As a result, the passive elements occupy more space and make up most of the weight in electronic packages. Passive elements are very important to the functioning of the microelectronic circuit and perform functions like filtering, decoupling, bias etc. The number of passive components in hand-held devices and computers have been growing through the years and now stand at 80% of the total part counts [1]. Figure 1.1 shows the growth of passives in PC motherboards over the years [2]. The worldwide market of passives is \$1.1 Billion with the increased use of cell phones and wireless technologies, passive components are going to play an important role in the development of next generation microlectronics devices.

Figure 1.1 Number of passives on PC motherboards

Passives can be categorized into three distinct categories:

- Discrete Passive: A single passive element in its own leaded or surface mount technology (SMT) package. The most commonly used size is 0402 (1×0.5 mm), 0201 (0.5×0.25 mm) is the smallest size available. [3]

- 2) Integrated Passive: This applies to many passive components grouped together into one package.

- 3) Embedded Passive: This type of passive is embedded in the interconnect substrate.

Discrete and Integrated passives have been used in the industry for many years now. Up until 1995, almost all passive components were discrete. However, in 1998, 55 Billion SMT Capacitors and Resistors were replaced by Integrated passives devices. 95% of the current 900 billion passive components are Discrete and integrated passives and about 3% are used in the embedded form [4].

Even with its wide use, Discrete passives have an inherent number of disadvantages associated with them. They are:

- i) Real Estate Consumption: Discrete passives take up a large amount of real estate area. Since the IC's have been reducing in size much faster than the passives, the total IC package including the discrete passives is typically 6-8 times the size of the IC itself [5].

- **ii) Poor Electrical Performance**: Discrete passives have high parasitics due to the presence of solder joints in the package, particularly the parasitic inductance in capacitors.

- **iii)** Low Reliability: The presence of solder joints results in reliability problems as the solder joints fail through thermo-mechanical fatigue after prolonged use. In a typical board, passives account for 25% of the solder joints.

- iv) Inflexible Design: Discrete passives are available in limited sizes and ranges making them difficult for customization according to the customer's needs.

Given these shortcomings, there is a need to overcome these problems to improve the overall performance of the microelectronics system. Integral Passives can overcome these limitations due to the following aspects:

- i) Reduced footprint, mass and volume: Since the passives are integrated in the interconnecting substrate, the Integral passives will have lower mass and occupy less real estate area than the corresponding Discrete passive.

- **ii) Better Electrical Performance**: The elimination of solder joints improves the parasitics of the Integral passives.

- **iii) Increased Design Flexibility**: The Integral Passives can be designed with respect to electrical characteristics to any value.

- **iv) Improved Reliability**: The elimination of solder joints leads to improved reliability. A detailed discussion is presented after this subsection.

- v) Better Yield: Integral Passives are fabricated with the interconnecting substrate and no additional work is required on the substrate after fabrication. In contrast, discrete passives have to be assembled on the substrate after fabrication resulting in lower yield and higher costs.

However, there are many concerns with Integral passives related to manufacturing and materials that will be addressed in the next section.

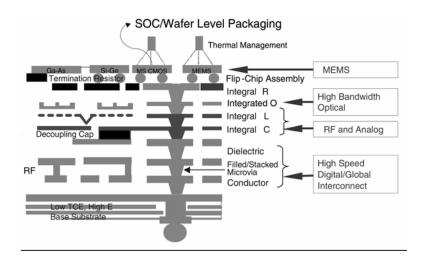

#### SOP Concept

The SOP (System On Package) paradigm integrates various functionalities such as RF, Optical and Digital into one module. This module promises to provide low cost, reliable and faster to market approach to Microsystems packaging. This is in sharp contrast to the System on Chip (SOC) approach, which will be severely limited by expense and lithography technology by the year 2007. Integral passives form an important part of the SOP package and play an important part in the RF module of the SOP. The RF passives will be critical in the miniaturization and cost effectiveness of the SOP approach. There has been tremendous demand for mobile and wireless applications such as RF Identification, local multipoint distribution systems (LMDS) and wireless Local Area Networks (WLAN) operating at frequencies in the millimeter range. This has been implemented by the SOP approach that integrates antennas, filters, resonators, baluns and other RF components in an advanced LTCC based MCM module. In addition, high Quality factor inductors have been integrated in the multiplayer organic package [6]. Decoupling capacitors will also be essential in providing noise free supply to the different modules in the SOP package. Figure 1.2 shows the SOP test vehicle currently being implemented in the Packaging Research Center (PRC) [7].

Figure 1.2. PRC's SOP Test vehicle

# **Thermo-Mechanical Reliability of Integral Passives**

The elimination of solder joints in Integral passives means that Integral passives will have higher reliability than the Discrete passives. However integration into the substrate can give rise to new concerns with respect to reliability of the Integral passives. The primary concern arises from the use of new materials and new fabrication processes. With respect to reliability, the two failure modes are:

- 1) Mechanical Failure: This failure is characterized by the delamination of the different layers in the interconnecting substrate containing the Integral passives, or cracks propagating in the passive. Also cracking of the traces could lead to electrical opens.

- 2) Electrical Failure: This failure stems from the change in electrical parameters above a certain tolerance value. The tolerance value

depends on the application of the passive component. The change occurs due to the thermo-mechanical deformation of the passive component and with the change in the electrical properties of the dielectric material with time/temperature/age/bias. The change in the electrical parameters influences the functioning of the module or the system level functionality of the device.

With the use of different materials in a High Density Substrate (HDW), the difference in Coefficient of Thermal Expansion (CTE) between the different layers in the substrate can give rise to interlaminar stresses that can cause deformation, delamination or crack propagation. The induced stresses depend on the thickness of the layers, the difference in properties of the layers, the curing temperature and the reliability tests conducted. However, it is important to note that electrical failure may occur prior to mechanical failure making it important to analyze the potential for electrical failure before determining the mechanical integrity of the system. In short, just because the system does not exhibit signs of mechanical failure doesn't imply that it has full electrical functionality.

This thesis looks at the change in the electrical parameters of embedded passives with thermal cycling and its impact on the performance of the passive. Test vehicles have been fabricated and subjected to thermal cycles and extreme temperature and humidity conditions. These results will be validated against Finite Element Analysis to determine the change in electrical parameters with adverse conditions.

# **CHAPTER II**

# BACKGROUND ON PERFORMANCE AND RELIABILITY

#### **Electrical Performance**

In order to accurately represent the electrical performance of embedded passives, the electrical model needs to consider the pure value of the ideal component and the parasitics associated with the passive. For example, this would mean considering the inductive and resistive effects of an embedded capacitor. Currently the discrete passives manufactured have specification sheets detailing its electrical performance. The parasitics of passives should always be taken into account while modeling the electrical performance. Ideal passives are represented by a single number and are characteristic of the passive being used. The impedance of an ideal resistor is a flat line with frequency whereas the impedance of an ideal capacitor decreases linearly with frequency and the impedance of an ideal inductor increases linearly with frequency. In an ideal capacitor, the voltage lags the current by 90° and in an inductor, the current lags the voltage by 90°. In an ideal resistor, both the current and the voltage are perfectly in phase.

The impedance or reactance of each passive is given by,

#### Resistor – R

Capacitance -

$$\frac{1}{2\pi f C}$$

where R = resistance

C = Capacitance

L = Inductance

Figure 2.1. Impedance variance of Ideal Passives with frequency

The following sections talk about different electrical parameters used to describe the electrical performance of embedded passives and the modeling of real passives.

## **Modeling** Capacitors

A capacitor stores energy in the form of an electric field. The most important constant of the capacitor is the dielectric constant. Another way of representing the dielectric property of a capacitor is to use the capacitance density or specific capacitance. This is the capacitance per unit area and higher values mean higher dielectric constant. The capacitance density can be calculated by the dielectric constant and the dielectric thickness by

Capacitance density

$$\left(\frac{nF}{cm^2}\right) = 0.885 \frac{k}{d}$$

Where k = dielectric constant

d = distance between the plates in  $\mu$ m.

Another important parameter is the dissipation factor. This is the measure of how much energy is lost in the dielectric during the AC operation. The inability of the mobile charges to respond to changes in the electric field or the inductive and resistive losses in the capacitor can cause the dissipation factor to increase. The reciprocal of the dissipation factor is known as the quality factor. A dissipation factor of 0.1% is considered very good and is generally hard to obtain for high k dielectrics.

The dependence of capacitance on temperature is called the Temperature Coefficient of Capacitance (TCC). It is calculated by

$$TCC = \frac{1}{C} \frac{\partial C}{\partial T} = \frac{1}{C_{T_{1}}} \frac{C_{T_{2}} - C_{T_{1}}}{T_{2} - T_{1}}$$

A TCC of around 200 ppm / °C (parts per million) is considered low and the dielectric is very stable with temperature. Thus in order to find the change in capacitance from -55 °C to 125 °C, the change will be the TCC times the temperature change (180 °C). For a TCC of 200 ppm / °C, this will mean a change of 3.6% over this temperature range.

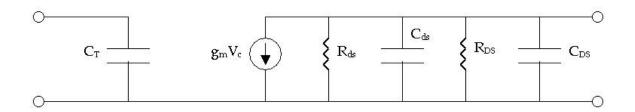

A capacitor has two parasitics associated with it called the ESR (Equivalent Series Resistance) and the ESL (Equivalent Series Inductance). The ESR is due to the inherent resistivity of the conductor plates and the leads of the capacitors. The ESL is due to the coupling between the conductor plates and the ground plane. Ideally both the ESR and the ESL should be zero. As mentioned in the section before, the capacitive reactance decreases with frequency and the inductive reactance increases with frequency. In the case of a capacitor, the inductive reactance or the ESL increases with frequency and at a particular frequency balances out the capacitive reactance. At this frequency, the current and voltage are in phase and the only impedance present is due to the resistive reactance. This point is known as the self-resonating frequency or simply the resonance frequency. Beyond the resonating frequency, the capacitor turns into an inductor and the impedance increases with frequency. Figure 2.2 shows the behavior of an actual capacitor and the lowest point is the resonance frequency where the only impedance comes form the resistive reactance.

Figure 2.2. Behavior of a real capacitor

The parasitic inductance of a capacitor is proportional to the distance between the plates. Closer plates mean higher capacitance and lower parasitic inductance but difficult manufacturability and distant plates mean lower capacitance with higher parasitic inductance but easier manufacturability. Embedded capacitors don't suffer from the high parasitic inductance as discrete passives do due to the absence of leads and the lower height difference between the interconnects and the embedded capacitor.

## **Modeling Inductors**

Inductors store energy in the form of magnetic energy. The most important property is that of magnetic permeability. Magnetic permeability is defined in terms of the magnetic field

$$\vec{B} = \mu \vec{H}$$

where B is the magnetic flux density vector, m is the magnetic permeability and H is the auxiliary magnetic field or the magnetic field vector. In addition,

$$\mu = \mu_0(1 + \chi_m)$$

where  $\mu_0$  is the magnetic permeability of free space and  $\chi_m$  is the magnetic susceptibility. The relative permeability is given by the ratio of the magnetic permeability of the material to the free space permeability.

A very common parameter used to measure the performance of an inductor is the Quality factor. This is the ratio of the Imaginary impedance to Real Impedance. The Quality factor in inductors can be improved by a variety of methods. This includes reducing the ESR, using high resistivity and low k substrates.

$$Q = \frac{Z_{im}}{Z_{re}} = 2\pi \frac{peak \text{ magnetic energy} - peak \text{ electric energy}}{energy \text{ loss in one cycle}}$$

Magnetic fields generated in the inductors interact with other materials in the substrate which gives rise to eddy currents. These eddy currents oppose the original change in magnetic field and cause loss in the inductors. The most important factor related to eddy current effects is skin depth. The skin depth measures the level of penetration of the electric current and magnetic flux into the conductor. The skin depth is given by

$$\delta = \sqrt{\frac{1}{\pi \,\mu \sigma \, f}}$$

where  $\delta$  is the skin depth,  $\mu$  is the permeability and  $\sigma$  is the conductivity of the material and f is the frequency. At high frequencies, the skin effect goes up and hence the current only flows on the surface of the conductor. The eddy current losses are minimal if the skin depth is greater than the thickness of the conductor.

## **Modeling Resistors**

Resistors dissipate electrical energy in the form of heat. For a perfect resistor, the resistance is given by

$$R = \frac{\rho L}{Wt}$$

where R is the resistance in W

$\rho$  = resistivity of the material

L = length of the strip

W = width of the strip

t = thickness of the strip

Another way of describing the resistance is by sheet resistance. The sheet resistance is equal to the resistance of a square of the material. The resistance of a resistor can be broken down into little squares and by knowledge of the resistance of each square and the number of squares, the resistance of the entire resistor can be calculated. The sheet resistance is given by

$$R = \left(\frac{\rho}{W}\right) \left(\frac{L}{W}\right) = R_s N_s$$

where R<sub>s</sub> is the sheet resistance

$N_s$  is the number of squares = L/W

Like the capacitors, the dependence of resistors on temperature is determined by Temperature Coefficient of Resistance (TCR). In some applications like thermistors, resistors with large TCR's can be used to measure changes in temperature. In addition, a positive TCC for the capacitor can be countered with a negative TCR for the resistor to maintain a constant RC time constant.

### **Fabrication Of Passives**

#### Capacitors

This section deals with the various methods of fabricating integrated capacitors. Given the wide variety of processing options for fabricating integrated capacitors, only the most commonly used are considered in this section. It is important to note that certain processes have inherent disadvantages over others and can be used only for specific materials. Most of these processes are applicable to organic boards and hence the maximum processing temperature is 250°C. All the processes may be divided into four basic categories. They are

Physical Vapor deposition (PVD), Chemical Vapor Deposition (CVD), solution based physical methods and photolithography.

#### Physical Vapor deposition (PVD)

Sputtering: Sputtering involves bombing a secondary object with energetic positive ions. The positive ions on hitting the secondary object lose their energy ejecting particles towards the substrate to be coated [8]. Sputtering is used usually to deposit thin films of metals but is also used to deposit resistor materials and dielectrics such as Tantalum Oxide, Titanium Oxide, Barium Titanate, Alumina etc. Sputtering can be performed at low temperatures which makes it a favorable process for temperature sensitive materials but its requirement of a vacuum and its uneven material deposition can be disadvantageous. In addition, thin sputtered films can show high dispersion loss at low frequencies [9]. It is also very important that the bottom electrode of the capacitor on which the deposition is taking place be smooth or the coating will not be even on the steep slopes of the bottom metal plate [10]. As a result obtaining high yields on rough substrate materials such as Kapton and Alumina is very hard [11][12]. In addition, many ferroelectrics such as Barium Titanate have to be annealed at 300°C to obtain a higher dielectric constant than obtained from direct sputtering [13]. Some materials such as Tantalum Oxide may require temperatures as high as 550°C. Such annealing requirements for ferroelectrics have limited the commercialization of sputtering in industry. In addition, the slow deposition rate of the dielectric can limit formation of thick films in paraelectrics. The maximum film thickness that can be obtained from sputtering is limited to a few micrometers.

#### <u>Chemical Vapor Deposition (CVD)</u>

In Chemical Vapor Deposition, the substance to be deposited is introduced as a vapor in a chamber containing the substrate. In order to deposit the dielectric on the surface, energy needs to be supplied for this endothermic reaction. This is done by either heating the substrate or using the electron energy of plasma. However the difficulty of vaporizing metallic dielectrics has led to use of metallo - organic CVD's (MOCVD) which can be used at low temperatures. CVD can be used to deposit specific dielectrics that cannot be deposited with many other processes. One such example is Diamond-like carbon (DLC), which has high hardness and low friction coefficient [14]. The MOCVD is a promising technology but is limited by its cost and rigid processing conditions.

One emerging chemical vapor deposition process is Combustion Chemical Vapor Deposition (CCVD). Figure 2.3 shows a schematic of the process [15].

Figure 2.3. Schematic of CCVD

This process entails mixing the dielectric with a combustible solvent and atomizing it to submicron droplets. The combustion of these droplets provides the energy required to evaporate the droplets and cause the dielectric to react and vapor deposit on the substrate. This process doesn't require a vacuum to be realized and can be done in ambient conditions and temperature with appropriate filters [16]. All these features combine to make CCVD a lower cost process than sputtering. CCVD can be used with a variety of materials such as cerium oxide, yttria stabilized zirconia, strontium titanate, Tantalum, Hf oxide, Shipley<sup>TM</sup> Insite etc.

#### Anodization

Anodization refers to electrochemical process used in forming dielectric oxides on the metal surface. The tendency of metals to form a metal oxide when exposed to moisture or oxygen can be exploited to form an oxide on the metal surface. The resultant oxide will have residual compressive stresses giving it excellent mechanical properties and stability. The primary materials used in anodization are Tantalum and Aluminum. Barium Titanate has also been made but the process requires an alkaline solution and the resultant film comparatively poor dielectric properties [17].

The procedure for anodization is quite similar as a typical electrochemical cell. The anode is the metal to be oxidized and the cathode is a noble metal (metal such as gold which is highly resistant to oxidation and corrosion). One of the typical electrolytes used is that of tartaric acid and ammonium hydroxide [18]. The anode and cathode are connected by a DC power source, which should be capable of providing around 150V and 1 mA per cm<sup>2</sup> of area to be anodized. The amount of oxide formed on the anode can be determined by Faraday's law:

$$\frac{dz_{ox}}{dt} = \frac{i}{nF} \frac{M_{ox}}{\rho_{ox}}$$

$z_{ox}$  = oxide thickness, cm

t = time, sec

- $i = \text{current density}, \text{A/cm}^2$

- *n* = number of electrons given off in the half reaction at the anode

- *F* = Faraday's constant (96500 coulombs/mole of electrons)

- $M_{ox}$  = molecular weight of the oxide, gms/mole

- $\rho_{ox}$  = density of the oxide, gms/cm<sup>3</sup>

Anodization is an excellent process for making capacitor dielectrics for a multitude of reasons. It is very easy to achieve uniform defect free films with this process and in addition the final thickness is a function of cell voltage and not affected by processing time, electrolyte used, temperature and current. Also anodization is not affected by the thickness of the bottom electrode since the amount of dielectric grown can be easily determined by the above equation. The apparatus is inexpensive, easy to use and is non-toxic.

#### Solution-Based: Physical

# Spin Coating

In spin coating, the liquid dielectric to be coated is put in the middle of the substrate and the substrate is rotated at a high speed. The dielectric then spreads over the substrate due to centrifugal force. The thickness of the dielectric depends on the angular velocity at which the substrate is rotated, the viscosity of the dielectric and surface tension of the dielectric. Hence it is very easy to control the thickness of the films produced by determining the required angular speed. However spin coating has its inherent disadvantages as well, the biggest being the wastage of material, which can drive up the costs. In addition, the ability to form thick films is limited in spin coating as the uniformity is not constant.

Polyimide is the most commonly used material in spin coating. Thickness of 0.95µm in polyimide has been achieved using spin coating. The dielectric showed changes within a range of 10% with increasing frequency and decreased with decreasing thickness [19].

# Meniscus Coating

In Meniscus coating, the dielectric to be coated is pumped through an applicator tube from one end. When the horizontally held tube is full, the material pours out from the slot back into the reservoir. The meniscus that is formed on the upper surface of the tube is made in contact with the substrate held upside down by a vacuum. The tube traverses the entire length of the substrate depositing a thin layer of dielectric on the substrate surface. The thickness of the dielectric deposited is a function of the viscosity of the dielectric, the applicator speed and environmental conditions. Figure 2.4 shows a schematic of the process [20].

Figure 2.4. Schematic of Meniscus coating

At PRC at Georgia Tech, Meniscus coating has been successfully used to coat a variety of dielectrics such as Ciba<sup>TM</sup> 7081, Shipley<sup>TM</sup> XP9500CC, Dupont<sup>TM</sup> P12611, Dow<sup>TM</sup> Benzocyclobutene etc. Uniform thicknesses of 3-25µm have been obtained using the meniscus coater. Unlike Spin coating, Meniscus coating has achieved minimal material wastage, high throughput, high planarity, minimal defect density and uniform thickness over a large area. This simple to implement technology is an important aspect of achieving a high density, low cost SOP substrate with excellent mechanical and electrical properties.

### Solution-Based - Chemical

### Sol-Gel Deposition

In Sol-Gel deposition, a thin layer of a liquid-phase metallo-organic compound is thermally cured to remove the organic portion forming a metal inorganic oxide. Sol-gel processes allow for deposition of films with high degree of homogeneity at low temperatures.

The process starts by dissolving organometallic compounds such as metal alkoxides in alcohol to give a homogenous solution. This solution or "sol' is then gelated by a hydrolysis reaction with water or by exposure to atmosphere. Important factors affecting the gelation are the pH and concentration of the catalyst, the amount and composition of the solvent and the sequence of mixing. The gel is amorphous and is mechanically weak because it has continuous pores and trapped organics, water and hydroxyl groups. Heat treatment and densification of the film form the final film. The high surface area of the dried gels results in very high reactivity, which results in a relatively low-temperature process as compared to ceramic deposition.

Sol-gel can be used for low cost processing of high k dielectrics since it requires less equipment and no vacuum. However the temperatures required to form high dielectric crystalline films are around 500°C. For example, films of Barium Strontium Titanate have to be annealed from 500°C to 700°C to achieve the crystalline structure and yield high dielectric constants in the range of 100-250 but the dielectric constant changes dramatically with the film thickness [21]. One promising material is Lead Zirconate Titanate (PZT) ,which at a film thickness of 0.5µm, gives a capacitance density of 2000 nF/cm<sup>2</sup> with a very high breakdown voltage of 1.3 MV/cm. Other materials that can be processed with Sol-Gel are Barium Titanate (formed from Barium Hydroxide), PZT (formed by lead acetate) etc.

# Hydrothermal Deposition

Hydrothermal deposition involves the dissolution of reactants and precipitation of crystalline compounds in hot, pressurized water. It is a standard technique to form crystalline powders in hot, pressurized water. The raw materials used are similar to that in the sol-gel process. A subsequent hydrothermal treatment of the sol can assist in the formation of thin films at lower temperatures. The reactions are carried out in closed vessels typically under strong alkali conditions. Hydrothermal processing can achieve crystalline ceramics at temperatures lower than 100°C.

At PRC at Georgia Tech, Barium Titanate has been deposited on Titanium coated glass slides or thin foils laminated on FR4. It was found that the specific capacitance was very high but so was the dielectric loss. By treatment with oxygen plasma, the dielectric loss was reduced but as the same time the specific capacitance went down as well. It is uncertain why the oxygen plasma had a significant effect on the dielectric properties of Barium Titanate. Another post hydrothermal method of improving the properties was to use polymer infiltration. The fabricated Barium Titanate films can be integrated on low cost substrate via standard build up processes.

### Photolithography

Photolithography is the most important process in industry right now that is used to assemble and package PWB's. It can be used to get resolutions of upto  $2\mu m$ , which is far larger than the widths currently used in the semiconductor industry. The pattern to be realized on the substrate is generated on a CAD or a similar system and is transferred to a photographic film or photomask. The pattern is made by a computer-controlled photoplotter or an electron beam. In order to transfer the pattern from the photomask to the substrate a thin layer of photosensitive material known as photoresist is applied on the substrate surface. The photoresist is then exposed to UV light or other type of light source with the photomask on top of it. The photoresist can be positive in which light breaks the molecules in the polymer making the photoresist easier to dissolve or negative in which light causes crosslinking in the polymer making the illuminated portion harder to dissolve.

### Commercialized Dielectric Materials for Capacitors

In this section, the different types of dielectrics and commercially used dielectrics are discussed. Given the tremendous amount of development going on in the choice of dielectric materials, there are three mechanisms for polarization in dielectric when an electric field is applied. They are electronic, atomic and ionic polarization. Each occurs by a different mechanism and the dielectric constant produced by each of these mechanisms varies. There are two types of dielectrics that are used in embedded passives. They are paraelectric and ferroelectric dielectrics. They display each of the polarizations but the difference is that when the electric field is removed, ferroelectric materials do not lose all of their ionic polarization unlike paralectrics. An example of a ferroelectric is Barium Titanate which below its Curie temperature a asymmetric tetragonal with unequal side lengths giving the crystal a residual polarization. This residual polarization can give the ferroelectric a dielectric constant in the thousands and hence gives ferroelectrics dielectric constants that are quite large as compared to paraelectrics. Also unlike paralectrics, ferroelectrics are heavily influenced by temperature, frequency, bias, thickness of the film and aging. In addition, the process used to fabricate the paraelectric can have a significant effect on the final dielectric constant of the dielectric. Following are some of the commercialized materials:

### DuPont Interra<sup>TM</sup>

DuPont has developed a high-k integrated capacitor process called Interra<sup>TM</sup> that involves the firing of a screen-printed ferroelectric paste on one side of the Cu foil at 900°C and then firing a Cu-based paste on that to form a top plate and flipping the stack onto the FR4. The foil is then patterned to form separate capacitors and the electrical connections to the capacitors. The dielectric is fired two times in order to eliminate pinholes. The dielectric used is doped Barium Titanate plus a glass that is compatible with board-level etching processes. The dielectric has excellent properties with the dielectric constant in excess of a 1000 with a capacitance density of 44 nF/cm<sup>2</sup> and a breakdown voltage of 0.8 MV/cm. Figure 2.5 depicts the process flow for the Interra<sup>TM</sup> integrated capacitor [22].

Figure 2.5. Dupont Interra<sup>TM</sup> process

3M C-Ply<sup>TM</sup>

This dielectric is a Barium Titanate filled epoxy, which is sandwiched between two layers of Cu foil. It has a capacitance density of 1.6nF/cm<sup>2</sup> with a very low dissipation factor of 0.45%. Based on these performance parameters, the dielectric has been used for decoupling application and has been found to reduce switching noise by three times [23].

## Resistors

The following section talks about fabrication processes for resistors and materials that are currently being developed for embedded resistors. Some of the processes for fabricating resistors have been discussed in the capacitor fabrication section and hence will be only briefly revisited.

#### **Sputtering**

Sputtering is the most commonly used process to deposit thin film integrated resistors. Tantalum Nitride (TaN<sub>x</sub>) has been deposited in a nitrogen rich environment and depending on the concentration of nitrogen, the resistivity increases with increasing nitrogen and the Temperature Coefficient of Resistance (TCR) decreases with increasing nitrogen. Tantalum Nitride films with resistivity of 250 $\Omega$ -cm have been fabricated. Tantalum Oxy-Nitride (TaN<sub>x</sub>O<sub>y</sub>) is another material that is deposited by sputtering and resistivities of 5000 $\Omega$ /square have been demonstrated. Semiconductors like Silicon can be used as resistors but their highly temperature and impurities dependent. Silicon is sputtered on organic substrates.

### Screen Printing

Polymer Thick Film (PTF) materials are primarily processed using screenprinting. These materials consist of epoxy-based polymers that have carbon fillers in the polymer. These are the conducting particles and the conduction mechanism is due to the bridging of these particles. PTF materials have low temperature processing and are usually cured at temperatures below 200°C. Screen-printing is a very simple and inexpensive process but it suffers from tolerance problems, reliability issues and delamination between the resistor material and the copper pad resulting in open circuits. In addition, swelling due to moisture and cracking of the polymer material due to CTE mismatch are causes of failure. Finally Screen-printing may be a little cumbersome process and requires very careful process control for good tolerance. The achievable sheet resistances cover a very wide range of 1 to  $10^7 \Omega$ /square.

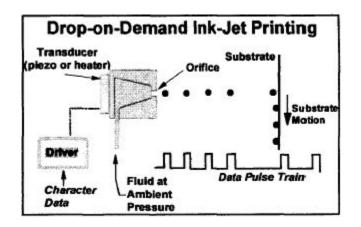

### Ink Jet Deposition

This process is very similar to ink jet printers and is used to deposit curable resin polymers and solder. Good tolerances, flexibility in resistor values, ease of use and reworkability make ink jet deposition an attractive process. Epoxy resins have been deposited using the above method. Figure 2.6 shows a Figure of the process [24].

Figure 2.6. Droplets on Demand Ink Jet deposition

#### Commercialized Processes for Resistors

This section discusses some commercialized processes in resistors that are currently being used or show great promise.

# Ohmega-Ply<sup>TM</sup>

Ohmega-Ply<sup>TM</sup> is an embedded resistor technology developed by Ohmega and is meant primarily for organic substrates or laminates. The resistor used is Nickel Phosphide (NiP), which is on one side of a copper foil. Using various process steps, copper interconnects can be formed to define the final resistor structure and value. The thickness of NiP varies between 0.1µm and 0.4µm and the sheet resistance can be as high as  $250\Omega$ /square.

#### DuPont Interra<sup>TM</sup>

The process is the same as discussed earlier in the capacitor fabrication section with the exception of Lanthanum Boride being used as the resistor material. Lanthanum Boride is stable and highly reliable resistor material. The minimum thickness of the resistor lines is 10µm and issues relating to the separation of the resistor termination interface surfaced.

#### Shipley InSite<sup>TM</sup>

The resistor material used in embedded resistor is a thin film of doped platinum deposited on copper foil by CCVD. The process produces high values of sheet resistivity ( $1000\Omega$ /square) and a TCR of 100ppm. The process consists of

a copper foil of  $\frac{1}{2}$  oz or 1 oz thickness, which is coated with the InSite resistor material, laminated with the resistor film against the prepreg. Figure 2.8 shows a schematic of the process [25].

Figure 2.8. Shipley InSite<sup>TM</sup> process

# **Reliability Experiments**

This section addresses the previous research done in the field of reliability of embedded passives. Since embedded passives are still an emerging technology, research in the thermo-mechanical reliability of passives is very limited. Schatzel has studied the thermo-mechanical reliability of capacitors made from Tantalum Oxide (Ta<sub>2</sub>O<sub>5</sub>) and Benzocyclobutene (BCB) [26]. The capacitors were fabricated on silicon as compared to industry standard FR4 and the capacitance values were measured at low frequency. The changes in capacitance after assembly process and 20 thermal cycles between -55°C and

100°C were measured. The mean change in capacitance was 0.61% but since only 20 thermal cycles were performed, it is inconclusive as far as long-term reliability goes. Borland et al. have reviewed the reliability of the Dupont Interra<sup>TM</sup> process as outlined in the capacitor and resistor fabrication section above [27]. The ceramic embedded capacitors and resistors were cycled between -45°C and 125°C and kept at 85°C/85%RH. The resistors showed an extremely small change 0.3% and capacitors showed a maximum change of 5% after 1000 cycles. The change in resistors after the high humidity and temperature conditions are less than 2%. However the resistors and capacitors were ceramic which have a much lower CTE and hence the thermo-mechanical deformation experienced will be much less than the deformation experienced in organic polymer dielectrics. Strydom et al. have looked at the reliability of embedded inductors from a delamination standpoint [28]. The inductors are subjected to thermal cycling and then the interfacial peel strength was measured at the end of subsequent thermal cycles to see the potential site of delamination. In addition, the change in capacitance was measured after 2000 tests. Lots of other literature on reliability of passives was found but they were of discrete passives and generally did not involve any thermal cycling. In addition, the change in electrical parameters was also not considered as a mode of failure. Fairchild et al. have looked at the thermal cycling of flexible thin-film embedded resistors and noticed a change of 2% after 300 thermal cycles. The resistor material used was Chromium Silicate (CrSi) with copper as the metalization [29]. Zhou et al. have subjected embedded resistors and capacitors to 1000 thermal cycles between −40 °C and 125 °C and observed a change of -0.3% and -3.10% respectively. The resistor used is Dupont<sup>TM</sup> ceramic resistor material and the capacitor dielectric is 3M C-Ply<sup>TM</sup> [30].

# Literature Review on passing qualifications for Embedded Passives

Failure qualifications in traditional reliability experiments have been very specific and easy to determine. For example, in an IC, the failure of the solder joint occurs when a crack propagates through the entire length of the solder joint and hence current cannot flow through the solder joint. In thermo-mechanical failure of passives however, the failure is not clearly quantified and different applications of passives might carry different ranges of failure. For example, the tolerance in a decoupling capacitor is not extremely important and a change of about 5% is not considered to be high. On the other hand, analog functions such as filters, A/D conversion require tight tolerances and even a change of 5% is too high.

Though there is no standard for embedded passives, the Electronics Industry Association (EIA) has classified discrete capacitor dielectrics by the change in dielectric constant with temperature. Currently there is no code for embedded passives but a similar system may be implemented in the future. The system consists of a alphanumeric code; the first alphabet is used to describe the low temperature, the second number represents the high temperature and the third alphabet is the %change seen in the dielectric. For example, X7R represents a maximum change of  $\pm 15\%$  between  $-55^{\circ}$ C and  $125^{\circ}$ C. Table 2.1 shows the EIA codes used for classifying different dielectric materials.

| Low Temperature |            | High | High Temperature |   | % Change     |  |

|-----------------|------------|------|------------------|---|--------------|--|

| Ζ               | +10 deg. C | 2    | +45 deg. C       | А | 1.00%        |  |

| Y               | -30 deg. C | 4    | +65 deg. C       | В | $\pm 1.5\%$  |  |

| X               | -55 deg. C | 5    | +85 deg. C       | С | ± 2.2%       |  |

|                 |            | 6    | +105 deg. C      | D | ± 3.3%       |  |

|                 |            | 7    | +125 deg. C      | Е | $\pm 4.7\%$  |  |

|                 |            |      |                  | F | ±7.5%        |  |

|                 |            |      |                  | Р | $\pm 10.0\%$ |  |

|                 |            |      |                  | R | ±15.0%       |  |

|                 |            |      |                  | S | ± 22.0%      |  |

|                 |            |      |                  | Т | +22%, -33%   |  |

|                 |            |      |                  | U | +22%, -56%   |  |

|                 |            |      |                  | V | +22%, -82%   |  |

Table 2.1. EIA temperature codes for dielectrics

In addition, the EIA has also classified dielectrics according to their dielectric constant and the stability with temperature. The three classes are:

- Class 1: These dielectrics usually have a k less than 100 and change no more than 30ppm between temperature range of 125°C and -55°C. If adapted for embedded passives, this category would go to paraelectrics for dielectric constant and stability.

- ii) Class 2: These dielectrics usually have a k in the range of 2000-5000 and a stability of upto  $\pm 15.0\%$ .

- iii) Class 3: These dielectrics have a k in the range of 4000-20000 and stability in the range of +22% to -82%. Both Class 2 and 3 belong to the category of ferroelectrics.

In the near future with the widespread use of embedded passives, some sort of code will be used to describe the changes in electrical parameters in passives with changes in temperature, voltage, bias, aging etc.

# Literature Review on Qualification Tests of Embedded Passives

The reliability of passives has been determined using some of the techniques mentioned below.

Air-to-air accelerated reliability testing: Air to air thermal stress testing is a standard methodology in the electronic packaging industry to assess the reliability of the components. It is also called the MIL-STD-883 Method or IPC-SM-785 test. Components are subjected to a temperature range from -55°C to

125°C in a cycle. Each cycle has a period of 20 minutes with 10 minutes dwell at extreme temperatures.

Standard Steady State Humidity Life Test: Very commonly used to determine the reliability of microelectronics packages, this test places the test substrate at high temperature and relative humidity of 85°C/85% RH. Sometimes the substrate is also subjected to a bias to determine the electrical performance of the test vehicle in adverse conditions. The test is also referred sometimes as the HAST test (Highly Accelerated Stress Test).

# **<u>Reliability Modeling</u>**

It is clear that research into the thermo-mechanical reliability of organic dielectrics on FR4 substrates is lacking and more work needs to understand the physics of passive reliability. In addition, very limited literature was found on the Finite Element Analysis validation of the results obtained from various experiments. Most of the research found published the results without any Finite Element Evaluation of the reason behind the changes in electrical parameters. No attempts are made to explain the reason for the changes in electrical parameters and the physics behind the change of the parameters.

Lee et al. have looked at the temperature distribution in integrated passive modules and determined the thermo-mechanical stress distribution in the module [31]. The temperature distribution was validated using an Infra Red camera and the Von Mises stress distribution was found to influenced by the in plane stresses. The stress distribution was not validated by any means.

# **Chapter III**

# **OBJECTIVES**

Embedded passives will play a critical role in high performance low cost microelectronics packages of the future. Everything from the fabrication process to the materials to be used is still under research and there is no consensus on each of the issues. In addition, the reliability research in embedded passives is lacking and there is no standard developed right now to qualify the reliability of passives. With the strong consumer drive to wireless applications, it is necessary to have design guidelines to fabricate reliable passives structures.

The primary objective of this research is to see the effect of thermomechanical deformation on the electrical parameters of the embedded passive structures. In order to perform reliability experiments, test boards are fabricated in a class 1000 clean room and then subjected to various reliability tests. The results from the experimental studies are correlated with the results obtained from the Finite Element Simulations.

The specific objectives of this work are:

- Develop theoretical models and to conduct experiments to study the reliability of embedded passives.

- The theoretical program aims:

- To develop physics based models that simulate the board deformation during thermal cycling.

- To develop electrostatic models that find the electrical parameters of the deformed model.

- Develop parametric models to see the effect of passive distance from neutral point and material selection on passive reliability.

- To develop physics based models to predict the change in electrical parameters based on the thermal loading experienced in fabrication processes.

- The experimental program aims:

- To fabricate test vehicles with embedded passives using photolithography process on standard FR4 substrate.

- To subject the test vehicles to various reliability tests and observe the change in electrical parameters.

- To validate the results from the theoretical program with the experimental data.

# Gaps in Existing Research

As observed in the literature survey, there is a severe shortage of research performed in thermo-mechanical reliability of embedded passives. Most of the research in the reliability of passives has been performed on either discrete passives or ceramic passives. Very limited literature takes a look at the reliability of standard photolithography process on conventional substrates. In addition, no Finite Element Analysis is performed in most of the published work to correlate the results with the experimental results obtained. There has been no attempt to understand the reason for the change in electrical parameters after the reliability experiments. No combined experimental and theoretical program exists for understanding the reliability of embedded passives. While material selection based on cost and electrical performance is widely considered, selection based on mechanical performance is very limited. No design guidelines exist for designing passives for optimal electrical and mechanical performance. Finally, there is limited research in understanding the effect of fabrication process on the change in electrical parameters. It has been generally observed in literature that obtaining a tolerance higher than 5% after fabrication is difficult. No literature could be found on effects on fabrication process on the performance of passives. In addition, the focus of most of the published work is limited to one type of passive instead of looking at all three.

# Chapter IV

# **DESCRIPTION OF TEST VEHICLE**

This chapter focuses on the steps to fabricate a multi-layered substrate with embedded passives. The first section discusses the test vehicle and the various passives structures in it. The next section looks at the processing conditions required to fabricate the test vehicle.

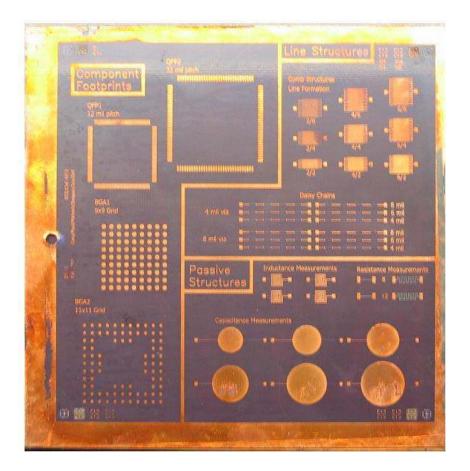

# **Test Vehicle Details**

The test vehicle fabricated has five layers of material on it. It is fabricated using a photolithography process on a FR4 substrate. The different materials used in the substrate and their thickness are listed in table 4.1. Figure 4.1 shows a picture of the test board and the passives embedded in the test board. The test board has 6 parallel circular plate capacitors, 4 spiral inductors and 2 meander resistors. The 6 capacitors have varying electrode diameters but same dielectric thickness between the electrodes. Table 4.2 shows the diameter of the capacitors and the capacitance value.

| Material              | Function                                           | Thickness |

|-----------------------|----------------------------------------------------|-----------|

| Copper                | Traces, Pads, Inductor traces,<br>Capacitor Plates | 15µm      |

| Shipley Dynavia 2000™ | Dielectric                                         | 63.5μ m   |

| Carbon Ink            | Resistor                                           | 15µ m     |

| FR4                   | Base material                                      | 700µ m    |

| Vialux 81             | Solder Mask                                        | 30µ m     |

# Table 4.1. Materials used in the test board

Figure 4.1. Picture of the Test Board

| Passive     | Diameter | Value    |

|-------------|----------|----------|

| Capacitor 1 | 330 mils | 29.53 pF |

| Capacitor 2 | 380 mils | 39.16 pF |

| Capacitor 3 | 430 mils | 50.14 pF |

| Capacitor 4 | 480 mils | 62.48 pF |

| Capacitor 5 | 530 mils | 76.18 pF |

| Capacitor 6 | 580 mils | 91.23 pF |

Table 4.2. Details of the capacitors

The other passives on the board are inductors and resistors. The value of inductance for all the inductors is 4.9  $\mu$ H and the resistance for the 8 mil thick resistor is 350K $\Omega$  and for the 12 mil thick resistor is 125 K $\Omega$ .

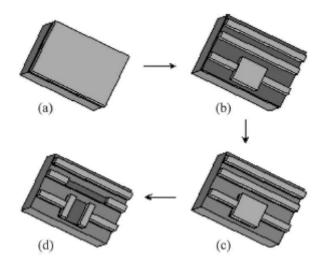

# **Fabrication Steps and Processing Conditions**

There are five layers in the fabrication. They are metal 1 (or the bottom metal layer), dielectric, metal 2 (or the top metal layer), soldermask and resistor layer. The photoresist used in the process is Dupont<sup>TM</sup> Riston 206, which is a negative defined dry film photoresist. The fabrication process starts with a double clad FR4 board. Prior to fabrication, the board is cleaned and the thin oxide formed on the copper is removed. This is done by dipping the board in Acetone, Methanol and Propanol to remove the dirt from the copper. It is then

dipped in deionized water and placed in sulphuric acid for 1 min. The board is finally baked at the end of the process to remove the accumulated moisture.

#### Metal 1 Layer

The photoresist is taken out of the refrigerator and allowed to warm up to room temperature. A 5.375" square is cut out from the photoresist and placed on the board. The protective coating on the side of the substrate is removed prior to the placement on the board. The photoresist is then vacuum laminated at 105 °C for 60 seconds and at 4 atmospheres for 30 seconds respectively. After the photoresist has been laminated, the laminator drawer is opened and the substrate is cooled down to room temperature.

The photoresist is now exposed for 15 seconds using the under the bottom metal mask shown in Figure 4.2. Photolithography is based on the principle that the exposed region is going to be harder to remove due to cross-linking under UV light. Hence when the photoresist is developed, the unexposed areas will etch away and the exposed areas will prevent the underneath materials from etching or other processes. The exposed photoresist is developed using a much stronger solvent. In case of the negative acting Riston 206, the unexposed photoresist is developed using Sodium Carbonate solution heated upto 35 °C. Before developing, the protective coating on the top side of the photoresist is removed and the substrate is placed in the solution for 60 seconds. The substrate is then rinsed in deionized water and dried with an air gun. The substrate is inspected under a microscope to make sure no residue of the exposed photoresist is left on the board.

Figure 4.2. Bottom Metal Mask

Now that the photoresist is removed from the board, the exposed copper, which was under the unexposed photoresist, is etched away using a 30% Ferric Chloride solution. The substrate is rinsed and dried and inspected for any copper residue and feature sharpness. Having formed the bottom metal layer, the remaining developed photoresist is removed using 1% Sodium Hydroxide solution heated to 53 °C. Any residue of photoresist or copper means that the stripping should go on till no residue is left and all features on the board are visible. Finally the substrate is baked to remove any accumulated moisture in the substrate. After the metal 1 layer, the Dielectric layer is fabricated.

# **Dielectric Layer**

Shipley DynaVia 2000<sup>TM</sup> is the dielectric material used as the dielectric. It is a negative acting dry film dielectric. The dielectric is laminated on the substrate in the same manner as the photoresist. However the lamination takes place at 60 °C instead of 105 °C. Once the dielectric has been laminated, the substrate is baked at 85 °C for 45 minutes and allowed to cool down to room temperature. The DynaVia<sup>TM</sup> is exposed using the via mask. The vias mask used is shown in Figure 4.3. In order to align the mask properly with the board, orientation structures called fiducials are matched with the fiducials formed on the bottom metal layer. It is important to align the masks properly or the vias will be unable to connect the bottom layer with the top metal layer. This mask allows the formation of vias in the dielectric and connects the bottom metal layer with the top metal layer. The substrate is baked after exposure for 45 minutes at 85 °C.

Figure 4.3. Via Mask

The Dynavia is then developed using a 98% solution of GBL (Gammabutyroacetone) for 31/2 minutes to form the via holes. Following the developing, the substrate is placed in a solution of propanol for 1-2 minutes and dried with an air gun. The substrate is inspected under a microscope to ensure that the vias have opened up and if that is not the case, the dielectric is developed again. The Dynavia is now exposed without any mask and subsequently cured at 135 °C for 45 minutes to cross link the dielectric. The substrate is removed from the oven and allowed to cool down to room temperature. Following the fabrication of the dielectric layer, the top metal layer is formed next.

### Metal 2 Layer

In order to form copper on the substrate, copper needs to be electroplated on the substrate. However electroplating requires a conducting medium on the surface of the substrate and Dynavia, being a dielectric, is not one. So a thin seed layer of copper is deposited to electroplate thicker layer of copper later. The seed layer has a thickness of around 5µm and is deposited by electroless plating. Following are the steps followed in order to do electroless plating on the substrate:

- The substrate is swelled in order to make etching easier. This is done by using a solution containing the solvents diethylene glycol and nbutyl ether.

- ii) The substrate is rinsed in deionized water and put in a permanganate etch solution. This allows for better adhesion of the material.

- iii) The board is rinsed in deionized water for 2 minutes and then neutralized for 2 minutes at room temperature using a solution of ptoulene, sulphuric acid and hydrogen peroxide to remove any excess chemicals.

- iv) The board is rinsed in deionized water and conditioned using weak sulphuric acid to prepare the board for microetching.

- v) The board is then microetched to prepare the substrate for the activator and rinsed for 2 minutes.

- vi) The board is pretreated for 1 minute before dipping in the activator. The pretreatment solution consists of sodium bisulfate and carbamidic acid. The activator bath triggers the insulating surface to provide metal seeds and provide better copper deposition. The activator solution consists of hydrochloric acid, palladium chloride and tin chloride.

- vii) The board is rinsed and put in a reducer solution for 5 minutes. The reducer allows for reduction of metal cations at the substrate surface, a plating reaction, to occur. The reducing agent used is Formaldehyde.

- viii) The board is rinsed and electroless plating is performed on the board for 6 minutes.

- ix) The board is rinsed and microetched for 1 minute.

- x) The board is rinsed and dipped in an antitarnish solution to remove any oxide from the freshly formed copper surface.

- xi) The board is rinsed and baked at 65 °C for 2 minutes to remove excess moisture from the board.

Figure 4.4. Top Metal Mask

With the formation of the seed layer, electroplating can now be carried out. However, in order to pattern the top metal, copper only needs to be deposited in certain areas. Hence in order to develop that pattern, photoresist is laminated on the top surface of the substrate, aligned with the top metal mask and exposed. The photoresist is then developed to expose only the areas that need to be electroplated. The board is then microetched to remove the oxide layer on copper before electroplating. The following steps are followed for the electroplating of copper.

- i) The board is dipped in sulphuric acid for 1 minute to remove the oxide.

- ii) The board is clipped into place and placed in the electroplating bath for 10 minutes.

- iii) After 10 minutes, rotate the substrate to perform even coating over the coated surface.

- iv) After all 4 sides of the board have been rotated; place the board in a 3%Sodium Hydroxide solution to remove the remaining photoresist.

- v) Rinse the board and dry it.

- vi) The board is microetched for 40 seconds and rinsed and dried. The board is inspected to ensure uniform coating.

- vii) The board is baked to remove any moisture.

# **Resistor Layer**

With the completion of the top metal layer, resistors are fabricated by opening gaps between copper pads and depositing resistor material with a squeegee in the gaps. The process starts by laminating photoresist on the substrate and exposing it using the resistor mask.

Figure 4.5. Resistor Mask

The photoresist is developed and then rinsed in deionized water. The resistor material is then squeegeed into the gaps in the substrate. The substrate is then baked for 30 minutes at 85°C and for 15 minutes at 110°C. The photoresist then stripped off to complete the liftoff process. The resistor is then cured at 150°C for 2 hours to make the resistor permanent. After the resistor layer, the final layer of solder mask is fabricated.

# Solder Mask

The solder mask is fabricated by first making the solder mask. The solder mask consists of a thinner, hardener and thinner. After the mixture is made, the solder mask is spun coat on the substrate by spinning it for 30 seconds at 300 rpm and for 30 seconds at 1200 rpm. The substrate is then baked for 15 minutes at 60 °C and for 45 minutes for 85 °C. The solder mask is then exposed using the solder mask mask.

Figure 4.6. Solder Mask mask

The solder mask is then developed in a 1% Sodium Carbonate solution and cured for 1 hour at 150 °C. With the completion of the solder mask layer, the fabrication of the board is concluded. Figure 4.7 shows a schematic of the fabrication process.